# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-VQFN Exposed Pad                                       |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0831qh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

## xvi

| Table 119. | Flash Memory Electrical Characteristics and Timing 192                |

|------------|-----------------------------------------------------------------------|

| Table 120. | Watchdog Timer Electrical Characteristics and Timing 192              |

| Table 121. | Nonvolatile Data Storage                                              |

| Table 122. | Analog-to-Digital Converter Electrical Characteristics and Timing 193 |

| Table 123. | Comparator Electrical Characteristics                                 |

| Table 124. | GPIO Port Input Timing                                                |

| Table 125. | GPIO Port Output Timing 196                                           |

| Table 126. | On-Chip Debugger Timing 197                                           |

| Table 127. | Power Consumption Reference Table                                     |

| Table 128. | Z8 Encore! XP F0830 Series Ordering Matrix 200                        |

| Table 129. | Package and Pin Count Description 207                                 |

| Table 130. | Timer 0 High Byte Register (T0H) 208                                  |

| Table 131. | Timer 0 Low Byte Register (T0L) 209                                   |

| Table 132. | Timer 0 Reload High Byte Register (T0RH) 209                          |

| Table 133. | Timer 0 Reload Low Byte Register (T0RL)                               |

| Table 134. | Timer 0 PWM High Byte Register (T0PWMH) 209                           |

| Table 135. | Timer 0 PWM Low Byte Register (T0PWML) 210                            |

| Table 136. | Timer 0 Control Register 0 (T0CTL0)                                   |

| Table 137. | Timer 0 Control Register 1 (T0CTL1)                                   |

| Table 138. | Timer 1 High Byte Register (T1H) 210                                  |

| Table 139. | Timer 1 Low Byte Register (T1L) 211                                   |

| Table 140. | Timer 1 Reload High Byte Register (T1RH) 211                          |

| Table 141. | Timer 1 Reload Low Byte Register (T1RL)                               |

| Table 142. | Timer 1 PWM High Byte Register (T1PWMH) 211                           |

| Table 143. | Timer 1 PWM Low Byte Register (T1PWML)                                |

| Table 144. | Timer 1 Control Register 0 (T1CTL0)                                   |

| Table 145. | Timer 1 Control Register 1 (T1CTL1)                                   |

| Table 146. | ADC Control Register 0 (ADCCTL0)                                      |

| Table 147. | ADC Data High Byte Register (ADCD_H) 214                              |

| Table 148. | ADC Data Low Bits Register (ADCD_L) 214                               |

#### 1

# **Overview**

Zilog's Z8 Encore! MCU family of products are the first in a line of Zilog microcontroller products based on the 8-bit eZ8 CPU. The Z8 Encore! F0830 Series products expand on Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward-compatible with existing Z8 CPU instructions. The rich peripheral set of Z8 Encore! F0830 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices and sensors.

## **Features**

The key features of Z8 Encore! F0830 Series MCU include:

- 20MHz eZ8 CPU

- Up to 12KB Flash memory with in-circuit programming capability

- Up to 256B register RAM

- 64B Nonvolatile Data Storage (NVDS)

- Up to 25 I/O pins depending upon package

- Internal Precision Oscillator (IPO)

- External crystal oscillator

- Two enhanced 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Single-pin, On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-chip analog comparator

- Up to 17 interrupt sources

- Voltage Brown-Out (VBO) protection

- Power-On Reset (POR)

- 2.7V to 3.6V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 20- and 28-pin packages

- 0°C to +70°C standard temperature range and -40°C to +105°C extended temperature operating ranges

# **Address Space**

The eZ8 CPU can access the following three distinct address spaces:

- The register file addresses access for the general purpose registers and the eZ8 CPU, peripheral and general purpose I/O port control registers

- The program memory addresses access for all of the memory locations having executable code and/or data

- The data memory addresses access for all of the memory locations containing only the data

The following sections describe these three address spaces. For more information about the eZ8 CPU and its address space, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download at <u>www.zilog.com</u>.

# **Register File**

The register file address space in the Z8 Encore! MCU is 4KB (4096 bytes). The register file consists of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as *source* are read and registers defined as *destinations* are written. The architecture of the eZ8 CPU allows all general purpose registers to function as accumulators, address pointers, index registers, stack areas or scratch pad memory.

The upper 256 bytes of the 4KB register file address space are reserved for controlling the eZ8 CPU, on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256B Control Register section are reserved (unavailable). Reading from a reserved register file address returns an undefined value. Writing to reserved register file addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the register file address space. The Z8 Encore! F0830 Series devices contain up to 256B of on-chip RAM. Reading from register file addresses outside the available RAM addresses (and not within the Control Register address space), returns an undefined value. Writing to these register file addresses has no effect.

#### 32

**Note:** This register is only reset during a Power-On Reset sequence. Other system reset events do not affect it.

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                | 6                                     | 5   | 4   | 3        | 2        | 1    | 0        |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|-----|----------|----------|------|----------|--|

| Field       |                                                                                                                                                                                                                                                                                                                                                                  | Reserved                              |     | VBO | Reserved | Reserved | COMP | Reserved |  |

| RESET       | 1                                                                                                                                                                                                                                                                                                                                                                | 0                                     | 0   | 0   | 1        | 0        | 0    | 0        |  |

| R/W         | R/W                                                                                                                                                                                                                                                                                                                                                              | R/W                                   | R/W | R/W | R/W      | R/W      | R/W  | R/W      |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                  | ·                                     |     | F8  | 80H      |          |      | ·        |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                       | n                                     |     |     |          |          |      |          |  |

| [7:5]       | Reserved<br>These registers are reserved and must be programmed to 000.                                                                                                                                                                                                                                                                                          |                                       |     |     |          |          |      |          |  |

| [4]<br>VBO  | Voltage Brown-Out detector disable<br>This bit takes only effect when the VBO_AO Flash option bit is disabled. In STOP Mode, VBO<br>is always disabled when the VBO_AO Flash option bit is disabled. To learn more about the<br>VBO_AO Flash option bit function, see the <u>Flash Option Bits</u> chapter on page 124.<br>0 = VBO enabled.<br>1 = VBO disabled. |                                       |     |     |          |          |      |          |  |

| [3]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                             |                                       |     |     |          |          |      |          |  |

| [2]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                             |                                       |     |     |          |          |      |          |  |

| [1]<br>COMP | Comparator Disable<br>0 = Comparator is enabled.<br>1 = Comparator is disabled.                                                                                                                                                                                                                                                                                  |                                       |     |     |          |          |      |          |  |

| [0]         | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                       | · · · · · · · · · · · · · · · · · · · |     |     |          |          |      |          |  |

#### Table 14. Power Control Register 0 (PWRCTL0)

>

| Port                | Pin | Mnemonic         | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------|--------------------------------|-----------------------------------------|

| Port B <sup>2</sup> | PB0 | Reserved         |                                | AFS1[0]: 0                              |

|                     |     | ANA0             | ADC analog input               | AFS1[0]: 1                              |

|                     | PB1 | Reserved         |                                | AFS1[1]: 0                              |

|                     |     | ANA1             | ADC analog input               | AFS1[1]: 1                              |

|                     | PB2 | Reserved         |                                | AFS1[2]: 0                              |

|                     |     | ANA2             | ADC analog input               | AFS1[2]: 1                              |

|                     | PB3 | CLKIN            | External input clock           | AFS1[3]: 0                              |

|                     |     | ANA3             | ADC analog input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved         |                                | AFS1[4]: 0                              |

|                     |     | ANA7             | ADC analog input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved         |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> | ADC reference voltage          | AFS1[5]: 1                              |

|                     | PB6 | Reserved         |                                | AFS1[6]: 0                              |

|                     |     | Reserved         |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved         |                                | AFS1[7]: 0                              |

|                     |     | Reserved         |                                | AFS1[7]: 1                              |

#### Table 16. Port Alternate Function Mapping (Continued)

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

# Port A–D Address Registers

The Port A–D Address registers select the GPIO port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO port controls; see Tables 18 and 19.

| <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W | Bit     | 7                      | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------------|---------|------------------------|-----------------------------|---|---|---|---|---|---|

| <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W | Field   |                        | PADDR[7:0]                  |   |   |   |   |   |   |

|                                        | RESET   | 00H                    |                             |   |   |   |   |   |   |

| Address FD0H, FD4H, FD8H, FDCH         | R/W     | R/W                    | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

|                                        | Address | FD0H, FD4H, FD8H, FDCH |                             |   |   |   |   |   |   |

### Table 18. Port A–D GPIO Address Registers (PxADDR)

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The port address selects one of the subregisters accessible through the Port Control Register. |

### Table 19. Port Control Subregister Access

| PADDR[7:0] | Port Control Subregister accessible using the Port A–D Control registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental port reconfiguration. |

| 01H        | Data Direction                                                                 |

| 02H        | Alternate Function                                                             |

| 03H        | Output Control (open-drain)                                                    |

| 04H        | High Drive Enable                                                              |

| 05H        | Stop Mode Recovery Source Enable                                               |

| 06H        | Pull-Up Enable                                                                 |

| 07H        | Alternate Function Set 1                                                       |

| 08H        | Alternate Function Set 2                                                       |

| 09H–FFH    | No function                                                                    |

• Writing 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (disable interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the Interrupt Controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction Trap

- Primary oscillator fail trap

- Watchdog Oscillator fail trap

## **Interrupt Vectors and Priority**

The Interrupt Controller supports three levels of interrupt priority. Level 3 is the highest priority, level 2 is the second highest priority and level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 54. Level 3 interrupts are always assigned higher priority than level 2 interrupts and level 2 interrupts are assigned higher priority than level 1 interrupts. Within each interrupt priority level (level 1, level 2 or level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), primary oscillator fail trap, Watchdog Oscillator fail trap and illegal instruction trap always have highest (level 3) priority.

## **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the interrupt request register is cleared. Writing 0 to the corresponding bit in the interrupt request register clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

# **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit                  | 7                                                                                                                                  | 6             | 5             | 4         | 3    | 2    | 1    | 0    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-----------|------|------|------|------|

| Field                |                                                                                                                                    | Rese          | erved         |           | PC3I | PC2I | PC1I | PC0I |

| RESET                | 0                                                                                                                                  | 0             | 0             | 0         | 0    | 0    | 0    | 0    |

| R/W                  | R/W                                                                                                                                | R/W           | R/W           | R/W       | R/W  | R/W  | R/W  | R/W  |

| Address              |                                                                                                                                    |               |               | FC        | 6H   |      |      |      |

| Bit                  | Description                                                                                                                        |               |               |           |      |      |      |      |

| [7:4]                | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000.                                                    |               |               |           |      |      |      |      |

| [3]<br>PC <i>x</i> l | PCxI0 = No interrupt request is pending for GPIO Port C pin x.1 = An interrupt request from GPIO Port C pin x is awaiting service. |               |               |           |      |      |      |      |

| Note: x in           | dicates the sp                                                                                                                     | ecific GPIO p | ort pin numbe | ər (3–0). |      |      |      |      |

#### Table 37. Interrupt Request 2 Register (IRQ2)

# **IRQ0 Enable High and Low Bit Registers**

Table 38 lists the priority control values for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling service for interrupts in the Interrupt Request 0 Register. Priority is generated by setting the bits in each register.

| IRQ0EN  | IH[x]                                                 | IRQ0ENL[x] | Priority | Description |  |  |  |

|---------|-------------------------------------------------------|------------|----------|-------------|--|--|--|

| C       | )                                                     | 0          | Disabled | Disabled    |  |  |  |

| C       | )                                                     | 1          | Level 1  | Low         |  |  |  |

| 1       |                                                       | 0          | Level 2  | Nominal     |  |  |  |

| 1       |                                                       | 1          | Level 3  | High        |  |  |  |

| Note: x | te: $x$ indicates the register bits in the range 7–0. |            |          |             |  |  |  |

Table 38. IRQ0 Enable and Priority Encoding

## 73

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer reload in COMPARATOR COUNTER Mode, counting always begins at the reset value 0001H. Generally, in COMPARATOR COUNTER Mode, the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions is calculated with the following equation:

Comparator Output Transitions = Current Count Value – Start Value

### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a pulse width modulated (PWM) output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to 16-bit PWM match value stored in the timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the timer output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the timer output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The timer output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the timer output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The timer output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps for configuring a timer for PWM SINGLE OUTPUT Mode and for initiating PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This value only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the timer output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

# Sample Settling Time Register

The <u>Sample Settling</u> Time Register, shown in Table 66, is used to program a delay after the <u>SAMPLE/HOLD</u> signal is asserted and before the START signal is asserted; an ADC conversion then begins. The number of clock cycles required for settling will vary from system to system depending on the system clock period used. The system designer should program this register to contain the number of clocks required to meet a  $0.5 \mu s$  minimum settling time.

| Bit     | 7        | 6 | 5 | 4 | 3            | 2  | 1 | 0 |

|---------|----------|---|---|---|--------------|----|---|---|

| Field   | Reserved |   |   |   | Reserved SST |    |   |   |

| RESET   | 0        |   |   |   | 1            | 1  | 1 | 1 |

| R/W     | R        |   |   |   |              | R/ | W |   |

| Address | F74H     |   |   |   |              |    |   |   |

### Table 66. Sample Settling Time (ADCSST)

| Bit          | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                  |

| [3:0]<br>SST | 0h–Fh = Sample settling time in number of system clock periods to meet 0.5 $\mu$ s minimum. |

# Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

# Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

### Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

- The Flash Sector Protect Register is ignored for programming and Erase operations.

- Programming operations are not limited to the page selected in the page select register.

- Bits in the Flash Sector Protect Register can be written to one or zero.

- The second write of the page select register to unlock the Flash Controller is not necessary.

- The page select register can be written when the Flash Controller is unlocked.

- The mass erase command is enabled through the Flash Control Register

**Caution:** For security reasons, Flash Controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the Flash Controller must go through the unlock sequence again to select another page.

# **NVDS Operational Requirements**

The device uses a 12KB Flash memory space, despite the maximum specified Flash size of 8KB (with the exception of 12KB mode with non-NVDS). User code accesses the lower 8KB of Flash, leaving the upper 4KB for proprietary (for Zilog-only) memory. The NVDS is implemented by using this proprietary memory space for special-purpose routines and for the data required by these routines, which are factory-programmed and cannot be altered by the user. The NVDS operation is described in detail in *the* <u>Nonvolatile</u> <u>Data Storage</u> *chapter on page 134*.

The NVDS routines are triggered by a user code: CALL into proprietary memory. Code executing from this proprietary memory must be able to read and write other locations within proprietary memory. User code must not be able to read or write proprietary memory.

# **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 119

Flash Status Register: see page 120

Flash Page Select Register: see page 121

Flash Sector Protect Register: see page 122

Flash Frequency High and Low Byte Registers: see page 123

# **On-Chip Debugger**

The Z8 Encore! devices contain an integrated On-Chip Debugger (OCD) that provides the following advanced debugging features:

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

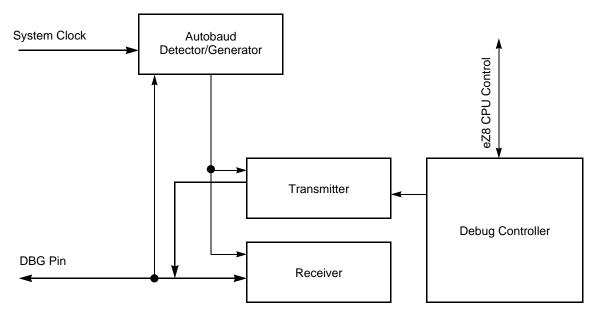

# Architecture

The On-Chip Debugger consists of four primary functional blocks: transmitter, receiver, autobaud detector/generator and debug controller. Figure 20 displays the architecture of the On-Chip Debugger.

Figure 20. On-Chip Debugger Block Diagram

# **Runtime Counter**

The OCD contains a 16-bit runtime counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash read protect option bit (FRP). The FRP prevents the code in memory from being read out of the Z8 Encore! F0830 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 95 summarizes the On-Chip Debugger commands. This table indicates the commands that operate when the device is not in DEBUG Mode (normal operation) and the commands that are disabled by programming the FRP.

| Debug Command              | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                                     |

|----------------------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                | -                                                                                                                                                                                |

| Reserved                   | 01H             | _                                  | _                                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                                | _                                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                                  | -                                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                                | Cannot clear DBGMODE bit                                                                                                                                                         |

| Read OCD Control Register  | 05H             | Yes                                | _                                                                                                                                                                                |

| Write Program Counter      | 06H             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Counter       | 07H             | _                                  | Disabled                                                                                                                                                                         |

| Write Register             | 08H             | _                                  | Only writes of the Flash Memory Con-<br>trol registers are allowed. Additionally,<br>only the Mass Erase command is<br>allowed to be written to the Flash Con-<br>trol register. |

| Read Register              | 09H             | _                                  | Disabled                                                                                                                                                                         |

| Write Program Memory       | 0AH             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Memory        | 0BH             | _                                  | Disabled                                                                                                                                                                         |

| Write Data Memory          | 0CH             | _                                  | Yes                                                                                                                                                                              |

| Read Data Memory           | 0DH             | _                                  | _                                                                                                                                                                                |

#### Table 95. On-Chip Debugger Command Summary

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! F0830 Series device ceases functioning and can only be recovered by power-on-reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

Figure 24 displays the oscillator control clock switching flow. See <u>Table 117</u> on page 189 to review the waiting times of various oscillator circuits.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2   | 1      | 0   |  |  |

|---------|-------|-------|-------|-------|-------|-----|--------|-----|--|--|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN |     | SCKSEL |     |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0   | 0      | 0   |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W | R/W    | R/W |  |  |

| Address | F86H  |       |       |       |       |     |        |     |  |  |

| Table 99 | . Oscillator | <b>Control Register</b> | (OSCCTL) |

|----------|--------------|-------------------------|----------|

|----------|--------------|-------------------------|----------|

| Bit   | Description                                                       |

|-------|-------------------------------------------------------------------|

| [7]   | Internal Precision Oscillator Enable                              |

| INTEN | 1 = Internal Precision Oscillator is enabled.                     |

|       | 0 = Internal Precision Oscillator is disabled.                    |

| [6]   | Crystal Oscillator Enable                                         |

| XTLEN | This setting overrides the GPIO register control for PA0 and PA1. |

|       | 1 = Crystal oscillator is enabled.                                |

|       | 0 = Crystal oscillator is disabled.                               |

| [5]   | Watchdog Timer Oscillator Enable                                  |

| WDTEN | 1 = Watchdog Timer Oscillator is enabled.                         |

|       | 0 = Watchdog Timer Oscillator is disabled.                        |

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

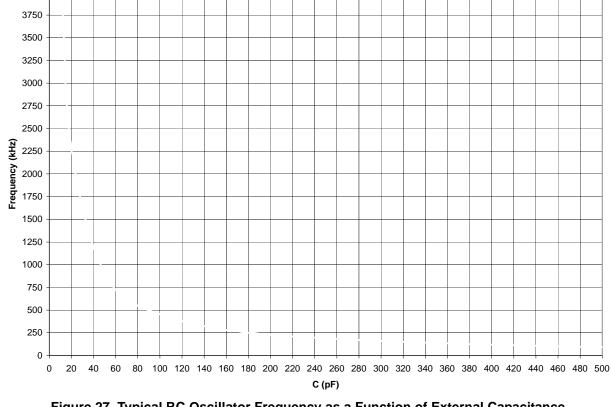

Figure 27. Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$  Resistor

**Caution:** When using the external RC OSCILLATOR Mode, the oscillator can stop oscillating if the power supply drops below 2.7V but before it drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7V.

160

4000

|                   |                                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = -40°C to<br>+105°C |                  |     |       |                                                             |  |

|-------------------|-------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|-----|-------|-------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                 | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max | Units | Conditions                                                  |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>disabled                              |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>enabled                               |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                                            |                               |     |     | _                                   | 10               | _   | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to gen<br>erate a Reset. |  |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to<br>transition from $V_{SS}$<br>to $V_{POR}$ to ensure<br>valid Reset |                               |     |     | 0.10                                | _                | 100 | ms    |                                                             |  |

## Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

ance only and are not tested in production.

# Packaging

Zilog's F0830 Series of MCUs includes the Z8F0130, Z8F0131, Z8F0230, Z8F0231, Z8F1232 and Z8F1233 devices, which are available in the following packages:

- 20-Pin Quad Flat No-Lead Package (QFN)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Plastic Dual-Inline Package (PDIP)

- 20-pin Small Shrink Outline Package (SSOP)

- 28-Pin Quad Flat No-Lead Package (QFN)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Shrink Outline Package (SSOP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

## Hex Addresses: FC9–FCC

This address range is reserved.

### Hex Address: FCD

#### Table 166. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|--|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |  |  |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |  |

| Address | FCDH |      |      |      |      |      |      |      |  |  |  |

### Hex Address: FCE

#### Table 167. Shared Interrupt Select Register (IRQSS)

| Bit     | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|----------|-------|----------|-----|-----|-----|-----|-----|--|--|--|

| Field   | Reserved | PA6CS | Reserved |     |     |     |     |     |  |  |  |

| RESET   | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address | FCEH     |       |          |     |     |     |     |     |  |  |  |

## Hex Address: FCF

#### Table 168. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------|----------|---|---|---|---|---|---|--|--|--|

| Field   | IRQE | Reserved |   |   |   |   |   |   |  |  |  |

| RESET   | 0    | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| R/W     | R/W  | R        | R | R | R | R | R | R |  |  |  |

| Address | FCFH |          |   |   |   |   |   |   |  |  |  |