Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 12KB (12K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1232hj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Reset Controller**

The Z8 Encore! F0830 Series products are reset using any one of the following: the RESET pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP Mode exit or Voltage Brown-Out (VBO) warning signal. The RESET pin is bidirectional; i.e., it functions as a reset source as well as a reset indicator.

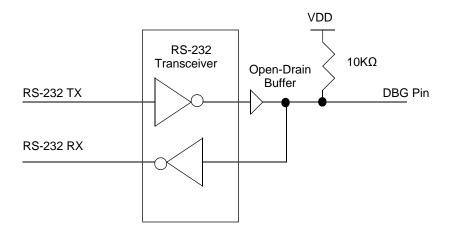

# **On-Chip Debugger**

The Z8 Encore! F0830 Series products feature an integrated On-Chip Debugger (OCD). The OCD provides a rich set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. The OCD uses one single-pin interface for communication with an external host.

# **Acronyms and Expansions**

This document references a number of acronyms; each is expanded in Table 2 for the reader's understanding.

| Acronyms | Expansions                       |

|----------|----------------------------------|

| ADC      | Analog-to-Digital Converter      |

| NVDS     | Nonvolatile Data Storage         |

| WDT      | Watchdog Timer                   |

| GPIO     | General-Purpose Input/Output     |

| OCD      | On-Chip Debugger                 |

| POR      | Power-On Reset                   |

| VBO      | Voltage Brown-Out                |

| IPO      | Internal Precision Oscillator    |

| PDIP     | Plastic Dual Inline Package      |

| SOIC     | Small Outline Integrated Circuit |

| SSOP     | Small Shrink Outline Package     |

| QFN      | Quad Flat No Lead                |

| IRQ      | Interrupt request                |

| ISR      | Interrupt service routine        |

| MSB      | Most significant byte            |

| LSB      | Least significant byte           |

| PWM      | Pulse Width Modulation           |

| SAR      | Successive Approximation Regis-  |

|          |                                  |

#### Table 2. Acronyms and Expansions

# **Address Space**

The eZ8 CPU can access the following three distinct address spaces:

- The register file addresses access for the general purpose registers and the eZ8 CPU, peripheral and general purpose I/O port control registers

- The program memory addresses access for all of the memory locations having executable code and/or data

- The data memory addresses access for all of the memory locations containing only the data

The following sections describe these three address spaces. For more information about the eZ8 CPU and its address space, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download at <u>www.zilog.com</u>.

# **Register File**

The register file address space in the Z8 Encore! MCU is 4KB (4096 bytes). The register file consists of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as *source* are read and registers defined as *destinations* are written. The architecture of the eZ8 CPU allows all general purpose registers to function as accumulators, address pointers, index registers, stack areas or scratch pad memory.

The upper 256 bytes of the 4KB register file address space are reserved for controlling the eZ8 CPU, on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256B Control Register section are reserved (unavailable). Reading from a reserved register file address returns an undefined value. Writing to reserved register file addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the register file address space. The Z8 Encore! F0830 Series devices contain up to 256B of on-chip RAM. Reading from register file addresses outside the available RAM addresses (and not within the Control Register address space), returns an undefined value. Writing to these register file addresses has no effect.

| Port                | Pin | Mnemonic         | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------|--------------------------------|-----------------------------------------|

| Port B <sup>2</sup> | PB0 | Reserved         |                                | AFS1[0]: 0                              |

|                     |     | ANA0             | ADC analog input               | AFS1[0]: 1                              |

|                     | PB1 | Reserved         |                                | AFS1[1]: 0                              |

|                     |     | ANA1             | ADC analog input               | AFS1[1]: 1                              |

|                     | PB2 | Reserved         |                                | AFS1[2]: 0                              |

|                     |     | ANA2             | ADC analog input               | AFS1[2]: 1                              |

|                     | PB3 | CLKIN            | External input clock           | AFS1[3]: 0                              |

|                     |     | ANA3             | ADC analog input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved         |                                | AFS1[4]: 0                              |

|                     |     | ANA7             | ADC analog input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved         |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> | ADC reference voltage          | AFS1[5]: 1                              |

|                     | PB6 | Reserved         |                                | AFS1[6]: 0                              |

|                     |     | Reserved         |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved         |                                | AFS1[7]: 0                              |

|                     |     | Reserved         |                                | AFS1[7]: 1                              |

#### Table 16. Port Alternate Function Mapping (Continued)

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

# Interrupt Controller

The Interrupt Controller on the Z8 Encore!<sup>®</sup> F0830 Series products prioritize the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the Interrupt Controller include:

- Seventeen interrupt sources using sixteen unique interrupt vectors:

- Twelve GPIO port pin interrupt sources

- Five on-chip peripheral interrupt sources (Comparator Output interrupt shares one interrupt vector with PA6)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt m

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the Interrupt Controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU User Manual (UM0128)</u>, which is available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 34 lists the interrupts available in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even program memory address and the least significant byte (LSB) at the odd program memory address.

**Note:** Some port interrupts are not available on the 20-pin and 28-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

# **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) Register, shown in Table 36, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ1 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 Register to determine if any interrupt requests are pending.

| Bit     | 7          | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------------|-------|------|------|------|------|------|------|

| Field   | PA7I       | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET   | 0          | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W        | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |            | FC3H  |      |      |      |      |      |      |

| Bit     | Descriptio | n     |      |      |      |      |      |      |

#### Table 36. Interrupt Request 1 Register (IRQ1)

| Bit   | Description                                                            |  |

|-------|------------------------------------------------------------------------|--|

| [7]   | Port A7                                                                |  |

| PA7I  | 0 = No interrupt request is pending for GPIO Port A.                   |  |

|       | 1 = An interrupt request from GPIO Port A.                             |  |

| [6]   | Port A6 or Comparator Interrupt Request                                |  |

| PA6CI | 0 = No interrupt request is pending for GPIO Port A or comparator.     |  |

|       | 1 = An interrupt request from GPIO Port A or comparator.               |  |

| [5]   | Port A Pin <i>x</i> Interrupt Request                                  |  |

| PAxI  | 0 = No interrupt request is pending for GPIO Port A pin x.             |  |

|       | 1 = An interrupt request from GPIO Port A pin $x$ is awaiting service. |  |

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$$

### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the capture occurs on a rising edge or a falling edge of the timer input signal.

When the capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in the TxCTL1 Register is set to indicate the timer interrupt because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in the TxCTL1 Register clears, indicating that the timer interrupt has not occurred because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the timer PWM High and Low Byte registers to 0000H. Clearing these registers allows user software to determine if interrupts were generated either by a capture event or by a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt were generated by a reload.

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The compare time can be calculated by the following equation:

Compare Mode Time (s) =  $\frac{(Compare Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **GATED Mode**

In GATED Mode, the timer counts only when the timer input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the timer input signal is asserted, counting begins. A timer interrupt is generated when the timer input signal is deasserted or a timer reload occurs. To determine whether the timer input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the timer input signal remains asserted). Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps for configuring a timer for GATED Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deasser-

| Bit    | Description (Continued)                                                                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0]    | Input Capture Event                                                                                                                                                        |

| INPCAP | This bit indicates whether the most recent timer interrupt is caused by a timer input capture event.                                                                       |

|        | <ul> <li>0 = Previous timer interrupt is not caused by timer input capture event.</li> <li>1 = Previous timer interrupt is caused by timer input capture event.</li> </ul> |

## Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

| Bit     | 7          | 6    | 5   | 4    | 3   | 2   | 1     | 0   |

|---------|------------|------|-----|------|-----|-----|-------|-----|

| Field   | TEN        | TPOL |     | PRES |     |     | TMODE |     |

| RESET   | 0          | 0    | 0   | 0    | 0   | 0   | 0     | 0   |

| R/W     | R/W        | R/W  | R/W | R/W  | R/W | R/W | R/W   | R/W |

| Address | F07H, F0FH |      |     |      |     |     |       |     |

| Bit | Description                                           |

|-----|-------------------------------------------------------|

| [7] | Timer Enable                                          |

| TEN | 0 = Timer is disabled.<br>1 = Timer enabled to count. |

### 96

# Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 60 through 62, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. This 24-bit value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate reload value; reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                         |      |      |      | WD   | TU   |      |      |      |

| RESET                                                                                         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W                                                                                           | R/W* |

| Address                                                                                       | FF1H |      |      |      |      |      |      |      |

| Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |      |

#### Table 60. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

| Bit         | 7              | 6            | 5             | 4               | 3                 | 2              | 1    | 0    |

|-------------|----------------|--------------|---------------|-----------------|-------------------|----------------|------|------|

| Field       |                |              |               | WD              | TH                |                |      |      |

| RESET       | 0              | 0            | 0             | 0               | 0                 | 1              | 0    | 0    |

| R/W         | R/W*           | R/W*         | R/W*          | R/W*            | R/W*              | R/W*           | R/W* | R/W* |

| Address     |                |              |               | FF              | 2H                |                |      |      |

| Note: *A re | ead returns th | e current WD | T count value | e; a write sets | the appropriation | ate reload val | ue.  |      |

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte, bits[15:8] of the 24-bit WDT reload value. |

# ADC Data High Byte Register

The ADC Data High Byte Register, listed in Table 64, contains the upper eight bits of the ADC output. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

#### Table 64. ADC Data High Byte Register (ADCD\_H)

| Bit     | 7 | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

|---------|---|---|---|-----|-----|---|---|---|

| Field   |   |   |   | ADO | CDH |   |   |   |

| RESET   |   |   |   | )   | K   |   |   |   |

| R/W     |   |   |   | F   | २   |   |   |   |

| Address |   |   |   | F7  | 2H  |   |   |   |

|         |   |   |   |     |     |   |   |   |

| Bit   | Description                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------|

| [7:0] | ADC High Byte                                                                                                       |

| ADCDH | 00h–FFh = The last conversion output is held in the data registers until the next ADC conver-<br>sion is completed. |

# ADC Data Low Bits Register

The ADC Data Low Bits Register, shown in Table 65, contains the lower bits of the ADC output. Access to the ADC Data Low Bits Register is read-only. Reading the ADC Data High Byte Register latches lower bits of the ADC in the ADC Data Low Bits Register.

| Bit     | 7   | 6   | 5 | 4  | 3    | 2     | 1 | 0 |  |

|---------|-----|-----|---|----|------|-------|---|---|--|

| Field   | ADO | CDL |   |    | Rese | erved |   |   |  |

| RESET   | )   | Х   |   | Х  |      |       |   |   |  |

| R/W     | F   | २   |   |    | F    | र     |   |   |  |

| Address |     |     |   | F7 | 3H   |       |   |   |  |

| Table 65. | ADC Data L | ow Bits R | Register (A | ADCD_L) |

|-----------|------------|-----------|-------------|---------|

|-----------|------------|-----------|-------------|---------|

| Bit            | Description                                                                                                                                                                                                                                  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]<br>ADCDL | ADC Low Bits<br>00–11b = These bits are the two least-significant bits of the 10-bit ADC output. These bits are<br>undefined after a reset. The low bits are latched into this register whenever the ADC Data High<br>Byte Register is read. |

| [5:0]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                 |

# Flash Option Bits

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! F0830 Series operation. The feature configuration data is stored in the Flash program memory and read during reset. The features available for control through the Flash option bits are:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer enabled at reset

- The ability to prevent unwanted read access to user code in program memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in program memory

- Voltage Brown-Out configuration always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- OSCILLATOR Mode selection for high, medium and low power crystal oscillators or external RC oscillator

- Factory trimming information for the Internal Precision Oscillator and VBO voltage

# Operation

This section describes the type and configuration of the programmable Flash option bits.

# **Option Bit Configuration by Reset**

Each time the Flash option bits are programmed or erased, the device must be reset for the change to be effective. During any Reset operation (system reset or Stop Mode Recovery), the Flash option bits are automatically read from Flash program memory and written to the Option Configuration registers, which control Z8 Encore! F0830 Series device operation. Option bit control is established before the device exits reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the register file and are not accessible for read or write access.

| Bit     | 7   | 6   | 5   | 4         | 3           | 2   | 1   | 0   |

|---------|-----|-----|-----|-----------|-------------|-----|-----|-----|

| Field   |     |     |     | TRMDR: Tr | im Bit Data |     |     |     |

| RESET   | 0   | 0   | 0   | 0         | 0           | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W       | R/W         | R/W | R/W | R/W |

| Address |     |     |     | FF        | 7H          |     |     |     |

#### Table 80. Trim Bit Data Register (TRMDR)

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits. See Tables 81 and 82.

| Bit                             | 7                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                                                | 4                                                        | 3                                                            | 2                                                           | 1                                                                                 | 0                                |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------|

| Field                           | WDT_RES                                                                                                                                           | WDT_AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OSC_S                                                                                                                            | SEL[1:0]                                                 | VBO_AO                                                       | FRP                                                         | Reserved                                                                          | FWP                              |

| RESET                           | U                                                                                                                                                 | U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U                                                                                                                                | U                                                        | U                                                            | U                                                           | U                                                                                 | U                                |

| R/W                             | R/W                                                                                                                                               | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W                                                                                                                              | R/W                                                      | R/W                                                          | R/W                                                         | R/W                                                                               | R/W                              |

| Address                         |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Р                                                                                                                                | rogram Mer                                               | nory 0000H                                                   |                                                             |                                                                                   |                                  |

| Note: U =                       | Unchanged by                                                                                                                                      | Reset. R/W :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | = Read/Write                                                                                                                     | •                                                        |                                                              |                                                             |                                                                                   |                                  |

| Bit                             | Descriptio                                                                                                                                        | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |                                                          |                                                              |                                                             |                                                                                   |                                  |

| [7]<br>WDT_RES<br>[6]<br>WDT_AO | <ul> <li>0 = Watch<br/>enable</li> <li>1 = Watch<br/>gramm</li> <li>Watchdog</li> <li>0 = On ap<br/>Timer</li> <li>1 = Watch<br/>Watch</li> </ul> | ed for the eZ<br>dog Timer ti<br>ned (erased<br>g Timer Alw<br>plication of s<br>cannot be d<br>dog Timer is<br>dog Timer o                                                                                                                                                                                                                                                                                                                                                                                                     | me-out gen<br>8 CPU to ad<br>me-out caus<br>) Flash.<br><b>rays On</b><br>system pow<br>isabled.<br>s enabled or<br>an only be o | cknowledge<br>ses a syster<br>er, Watchdo<br>n execution | the interrup<br>m reset. This<br>og Timer is a<br>of the WDT | t request.<br>s is the defa<br>utomatically<br>instruction. | ots must be g<br>ault setting fo<br>y enabled. W<br>Once enabl<br>ault setting fo | or unpro-<br>/atchdog<br>ed, the |

| [5:4]<br>OSC_SEL                | OSCILLA<br>00 = On-c<br>01 = Minin<br>10 = Medin<br>to 5.0<br>11 = Maxir                                                                          | <ul> <li>grammed (erased) Flash.</li> <li>OSCILLATOR Mode Selection</li> <li>00 = On-chip oscillator configured for use with external RC networks (&lt;4MHz).</li> <li>01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0MHz).</li> <li>10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MH to 5.0MHz).</li> <li>11 = Maximum power for use with high frequency crystals (5.0MHz to 20.0MHz). This is the default setting for unprogrammed (erased) Flash.</li> </ul> |                                                                                                                                  |                                                          |                                                              |                                                             | s (0.5MHz                                                                         |                                  |

Table 81. Flash Option Bits at Program Memory Address 0000H

Figure 22. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

# **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates, unless the device is in STOP Mode

- All enabled on-chip peripherals operate, unless the device is in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

### **Entering DEBUG Mode**

- The device enters DEBUG Mode after the eZ8 CPU executes a Breakpoint (BRK) instruction

- If the DBG pin is held low during the most recent clock cycle of system reset, the device enters DEBUG Mode on exiting system reset

### **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

149

### Table 96. OCD Control Register (OCDCTL)

| Bit           | 7                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                            | 4                                                              | 3                                                          | 2                                                     | 1                                           | 0                        |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|--------------------------|

| Field         | DBGMODE                                                                                                                                                                                                                                                                                                                                             | BRKEN                                                                                                                                                                                                                                                                                                                                                                                                                             | DBGACK                                                       |                                                                | Res                                                        | erved                                                 |                                             | RST                      |

| RESET         | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                            | 0                                                              | 0                                                          | 0                                                     | 0                                           | 0                        |

| R/W           | R/W                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                                                          | R                                                              | R                                                          | R                                                     | R                                           | R/W                      |

| Bit           | Descriptio                                                                                                                                                                                                                                                                                                                                          | on                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                              |                                                                |                                                            |                                                       |                                             |                          |

| [7]<br>DBGMOD | stops fetch<br>automatica<br>Flash read<br>cannot be<br>0 = The Z8                                                                                                                                                                                                                                                                                  | e enters DE<br>ning new ins<br>ally set whe<br>protect option<br>written to 0<br>B Encore! F(                                                                                                                                                                                                                                                                                                                                     | 0830 Series                                                  | learing this<br>ruction is de<br>bled, this bit<br>device is o | bit causes t<br>ecoded and<br>can only be<br>perating in N | he eZ8 CPU<br>breakpoints<br>e cleared by<br>NORMAL M | J to restart.<br>are enable<br>resetting th | This bit is<br>d. If the |

| [6]<br>BRKEN  | This bit co<br>are disable<br>when a BR<br>cally set to                                                                                                                                                                                                                                                                                             | 1 = The Z8 Encore! F0830 Series device is in DEBUG Mode.<br><b>Breakpoint Enable</b><br>This bit controls the behavior of the BRK instruction (opcode 00H). By default, breakpoints<br>are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1<br>when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automati-<br>cally set to 1.<br>0 = Breakpoints are disabled. |                                                              |                                                                |                                                            |                                                       |                                             | s bit is 1               |

| [5]<br>DBGACK | This bit en<br>Debug ack<br>0 = Debug                                                                                                                                                                                                                                                                                                               | nowledge o<br>acknowled                                                                                                                                                                                                                                                                                                                                                                                                           | ebug acknow<br>character (F<br>ge is disable<br>ge is enable | FH) to the h<br>ed.                                            |                                                            |                                                       |                                             | ends a                   |

| [4:1]         | Reserved<br>These bits                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                              |                                                                |                                                            |                                                       |                                             |                          |

| [0]<br>RST    | Reset         Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal Power-On Reset sequence with the exception that the On-Chip Debugger is not reset. Th bit is automatically cleared to 0 at the end of the reset sequence.         0 = No effect.         1 = Reset the Flash read protect option bit device. |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                              |                                                                |                                                            |                                                       |                                             |                          |

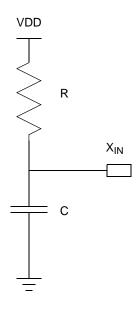

# **Oscillator Operation with an External RC Network**

Figure 26 displays a recommended configuration for connection with an external resistorcapacitor (RC) network.

#### Figure 26. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of  $45 \text{ k}\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is  $40 \text{ k}\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (R in k $\Omega$ ) and capacitor (C in pF) elements using the following equation:

Oscillator Frequency (kHz) =  $\frac{1 \times 10^{6}}{(0.4 \times R \times C) + (4 \times C)}$

Figure 27 displays the typical (3.3V and 25°C) oscillator frequency as a function of the capacitor (C in pF) employed in the RC network assuming a 45 k $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator X<sub>IN</sub> pin and the printed circuit board should be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20pF are recommended. 159

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit manipulation

- Block transfer

- CPU control

- Load

- Logical

- Program control

- Rotate and shift

Tables 105 through 112 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instructions can be considered as a subset of more than one category. Within these tables, the source operand is identified as *src*, the destination operand is *dst* and a condition code is *cc*.

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| CPX      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

### 170

## Table 112. Rotate and Shift Instructions (Continued)

| RRdstRotate RightRRCdstRotate Right through CarrySRAdstShift Right ArithmeticSRLdstShift Right LogicalSWAPdstSwap Nibbles | Mnemonic | Operands | Instruction                |

|---------------------------------------------------------------------------------------------------------------------------|----------|----------|----------------------------|

| SRAdstShift Right ArithmeticSRLdstShift Right Logical                                                                     | RR       | dst      | Rotate Right               |

| SRL dst Shift Right Logical                                                                                               | RRC      | dst      | Rotate Right through Carry |

|                                                                                                                           | SRA      | dst      | Shift Right Arithmetic     |

| SWAP dst Swap Nibbles                                                                                                     | SRL      | dst      | Shift Right Logical        |

|                                                                                                                           | SWAP     | dst      | Swap Nibbles               |

| Abbreviation | Description                             | Abbreviation                                      | Description            |

|--------------|-----------------------------------------|---------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                               | Indirect Register Pair |

| CC           | Condition code                          | р                                                 | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displace-<br>ment | r                                                 | 4-bit Working Register |

| DA           | Destination address                     | R                                                 | 8-bit register         |

| ER           | Extended Addressing Register            | r1, R1, Ir1, Irr1,<br>IR1, rr1, RR1,<br>IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register               | RA                                                | Relative               |

| IR           | Indirect Register                       | rr                                                | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                                | Register Pair          |

### Table 114. Op Code Map Abbreviations

|                             | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |     |     |        |                                                 |

|-----------------------------|----------------------------------------------------------------|-----|-----|-------------------------------------------------------------------|-----|-----|--------|-------------------------------------------------|

| Parameter                   | Min                                                            | Тур | Max | Min                                                               | Тур | Max | Units  | Notes                                           |

| NVDS Byte Read<br>Time      |                                                                |     |     | 71                                                                | -   | 258 | μs     | Withsystemclockat<br>20MHz                      |

| NVDS Byte Pro-<br>gram Time |                                                                |     |     | 126                                                               | -   | 136 | μs     | Withsystemclockat<br>20MHz                      |

| Data Retention              |                                                                |     |     | 10                                                                | _   | _   | years  | 25°C                                            |

| Endurance                   |                                                                |     |     | 100,000                                                           | -   | -   | cycles | Cumulative write<br>cycles for entire<br>memory |

#### Table 121. Nonvolatile Data Storage

**Note:** For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write can take up to 58 ms to complete.

#### Table 122. Analog-to-Digital Converter Electrical Characteristics and Timing

|                  |                                                 | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |     |     |       |                |

|------------------|-------------------------------------------------|----------------------------------------------------------------|-----|-----|-------------------------------------------------------------------|-----|-----|-------|----------------|

| Symbol           | Parameter                                       | Min                                                            | Тур | Max | Min                                                               | Тур | Мах | Units | Conditions     |

|                  | Resolution                                      |                                                                |     |     | _                                                                 | 10  | _   | bits  |                |

|                  | Differential<br>Nonlinearity (DNL) <sup>1</sup> |                                                                |     |     | -1                                                                | -   | +4  | LSB   |                |

|                  | Integral<br>Nonlinearity (INL) <sup>1</sup>     |                                                                |     |     | -5                                                                | _   | +5  | LSB   |                |

|                  | Gain Error                                      |                                                                |     |     |                                                                   | 15  |     | LSB   |                |

|                  | Offset Error                                    |                                                                |     |     | -15                                                               | _   | 15  | LSB   | PDIP package   |

|                  | -                                               |                                                                |     |     | -9                                                                | -   | 9   | LSB   | Other packages |

| V <sub>REF</sub> | On chip reference                               |                                                                |     |     | 1.9                                                               | 2.0 | 2.1 | V     |                |

|                  | Active Power<br>Consumption                     |                                                                |     |     |                                                                   | 4   |     | mA    |                |

|                  | Power Down<br>Current                           |                                                                |     |     |                                                                   |     | 1   | μA    |                |

Note: <sup>1</sup>When the input voltage is lower than 20mV, the conversion error is out of spec.

193

>

### Hex Address: F01

#### Table 131. Timer 0 Low Byte Register (T0L)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | TL                          |   |   |   |   |   |   |  |  |

| RESET   | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 1 |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | F01H                        |   |   |   |   |   |   |  |  |

### Hex Address: F02

#### Table 132. Timer 0 Reload High Byte Register (T0RH)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | TRH                         |   |   |   |   |   |   |  |  |

| RESET   | 1   | 1                           | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | F02H                        |   |   |   |   |   |   |  |  |

## Hex Address: F03

#### Table 133. Timer 0 Reload Low Byte Register (T0RL)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | TRL                         |   |   |   |   |   |   |  |  |

| RESET   | 1   | 1                           | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | F03H                        |   |   |   |   |   |   |  |  |

### Hex Address: F04

#### Table 134. Timer 0 PWM High Byte Register (T0PWMH)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | PWMH                        |   |   |   |   |   |   |  |  |

| RESET   | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | F04H                        |   |   |   |   |   |   |  |  |