Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 12KB (12K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1232ph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 28

### Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! F0830 Series device is in STOP Mode and the external RESET pin is driven low, a system reset occurs. Because of a glitch filter operating on the RESET pin, the low pulse must be greater than the minimum width specified about 12 ns or it is ignored. The EXT bit in the Reset Status (RSTSTAT) Register is set.

### **Debug Pin Driven Low**

Debug reset is initiated when the On-Chip Debugger detects any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received STOP bit is Low)

- Transmit collision (simultaneous OCD and host transmission detected by the OCD)

When the Z8F0830 Series device is operating in STOP Mode, the debug reset will cause a system reset. The On-Chip Debugger block is not reset, but the remainder of the chip's operations go through a normal system reset. The POR bit in the Reset Status (RSTSTAT) Register is set to 1.

### **Reset Register Definitions**

The following sections define the Reset registers.

#### **Reset Status Register**

The Reset Status (RSTSTAT) Register, shown in Table 12, is a read-only register that indicates the source of the most recent Reset event, Stop Mode Recovery event or Watchdog Timer time-out event. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer Control Register, which is writeonly.

### Architecture

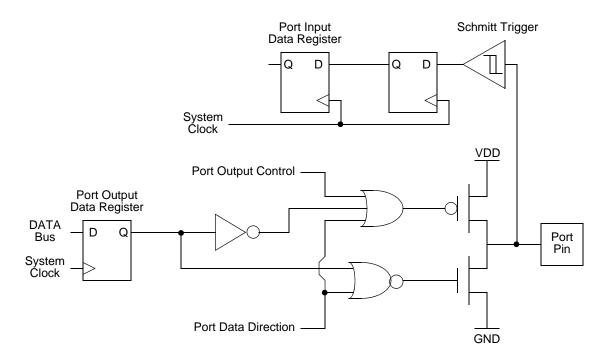

Figure 8 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

## **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general purpose input/output and access to onchip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function subregisters configure these pins for either GPIO or Alternate function operation. When a pin is configured for Alternate function, control of the port pin direction (input/output) is passed from the Port A–D data direction registers to the Alternate function assigned to this pin. <u>Table 16</u> on page 36 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, pins PA0 and PA1 functions as input and output for the crystal oscillator.

### Port A–C Input Data Registers

Reading from the Port A–C Input Data registers, shown in Table 29, return the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those not included in the 8- and 28-pin packages, as well as those not included in the ADC-enabled 28-pin packages.

| Bit     | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------------------|------|------|------|------|------|------|------|

| Field   | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W     | R                | R    | R    | R    | R    | R    | R    | R    |

| Address | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |

|         |                  |      |      |      |      |      |      |      |

#### Table 29. Port A–C Input Data Registers (PxIN)

Bit Description

[7:0] Port Input Data

PxIN Sampled data from the corresponding port pin input. 0 = Input data is logical 0 (Low).

1 =Input data is logical 1 (High).

Note: x indicates the specific GPIO port pin number (7–0).

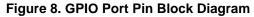

# Interrupt Controller

The Interrupt Controller on the Z8 Encore!<sup>®</sup> F0830 Series products prioritize the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the Interrupt Controller include:

- Seventeen interrupt sources using sixteen unique interrupt vectors:

- Twelve GPIO port pin interrupt sources

- Five on-chip peripheral interrupt sources (Comparator Output interrupt shares one interrupt vector with PA6)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt m

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the Interrupt Controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU User Manual (UM0128)</u>, which is available for download at <u>www.zilog.com</u>.

## **Interrupt Vector Listing**

Table 34 lists the interrupts available in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even program memory address and the least significant byte (LSB) at the odd program memory address.

**Note:** Some port interrupts are not available on the 20-pin and 28-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

## Architecture

Figure 9 displays the Interrupt Controller block diagram.

Figure 9. Interrupt Controller Block Diagram

## Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 55

Interrupt Vectors and Priority: see page 56

Interrupt Assertion: see page 56

Software Interrupt Assertion: see page 57

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables the interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (enable interrupt) instruction

- Execution of an IRET (return from interrupt) instruction

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register, shown in Table 35 stores the interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 Register to determine if any interrupt requests are pending.

| Bit     | 7           | 6   | 5   | 4   | 3        | 2   | 1   | 0   |  |

|---------|-------------|-----|-----|-----|----------|-----|-----|-----|--|

| Field   | Reserved    | T1I | TOI |     | Reserved |     |     |     |  |

| RESET   | 0           | 0   | 0   | 0   | 0        | 0   | 0   | 0   |  |

| R/W     | R/W         | R/W | R/W | R/W | R/W      | R/W | R/W | R/W |  |

| Address |             |     |     | FC  | ОН       | 1   |     |     |  |

| Bit     | Description | n   |     |     |          |     |     |     |  |

### Table 35. Interrupt Request 0 Register (IRQ0)

| Bit   | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| [7]   | Reserved                                                                           |

|       | This bit is reserved and must be programmed to 0.                                  |

| [6]   | Timer 1 Interrupt Request                                                          |

| T1I   | 0 = No interrupt request is pending for timer 1.                                   |

|       | 1 = An interrupt request from timer 1 is awaiting service.                         |

| [5]   | Timer 0 Interrupt Request                                                          |

| TOI   | 0 = No interrupt request is pending for timer 0.                                   |

|       | 1 = An interrupt request from timer 0 is awaiting service.                         |

| [4:1] | Reserved                                                                           |

|       | These registers are reserved and must be programmed to 0000.                       |

| [0]   | ADC Interrupt Request                                                              |

| ADCI  | 0 = No interrupt request is pending for the analog-to-digital converter.           |

|       | 1 = An interrupt request from the analog-to-digital converter is awaiting service. |

## **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7    | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|----------|---|---|---|---|---|---|

| Field   | IRQE | Reserved |   |   |   |   |   |   |

| RESET   | 0    | 0        | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W     | R/W  | R        | R | R | R | R | R | R |

| Address |      | FCFH     |   |   |   |   |   |   |

|         |      |          |   |   |   |   |   |   |

### Table 49. Interrupt Control Register (IRQCTL)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by executing an Enable Interrupts (EI) or Interrupt Return (IRET) instruction or by a direct register write of 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset, or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                                                                                                            |

Observe the following steps for configuring a timer for PWM DUAL OUTPUT Mode and for initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM deadband delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM High and Low Byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the timer output and timer output complement alternate functions. The timer output complement function is shared with the timer input function for both timers. Setting the timer mode to DUAL PWM will automatically switch the function from timer-in to timer-out complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output high time to the total period is represented by:

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines whether the capture occurs on a rising edge or a falling edge of the timer input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt has been caused by an input capture event.

If no capture event occurs, the timer counts up to 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

#### Bit Description (Continued)

#### [6] Timer Input/Output Polarity

TPOL Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### **COUNTER Mode**

If the timer is disabled, the timer output signal is set to the value of this bit. If the timer is enabled the timer output signal is complemented after timer reload.

- 0 = Count occurs on the rising edge of the timer input signal.

- 1 = Count occurs on the falling edge of the timer input signal.

#### PWM SINGLE OUTPUT Mode

- 0 = Timer output is forced Low (0), when the timer is disabled. The timer output is forced High (1) when the timer is enabled and the PWM count matches and the timer output is forced Low (0) when the timer is enabled and reloaded.

- 1 = Timer output is forced High (1), when the timer is disabled. The timer output is forced low(0), when the timer is enabled and the PWM count matches and forced High (1) when the timer is enabled and reloaded.

#### CAPTURE Mode

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### COMPARE Mode

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### GATED Mode

- 0 = Timer counts when the timer input signal is High (1) and interrupts are generated on the falling edge of the timer input.

- 1 = Timer counts when the timer input signal is Low (0) and interrupts are generated on the rising edge of the timer input.

#### CAPTURE/COMPARE Mode

- 0 = Counting is started on the first rising edge of the timer input signal. The current count is captured on subsequent rising edges of the timer input signal.

- 1 = Counting is started on the first falling edge of the timer input signal. The current count is captured on subsequent falling edges of the timer input signal.

# Comparator

The Z8 Encore! F0830 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or from an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The comparator includes the following features:

- Positive input is connected to a GPIO pin

- Negative input can be connected to either a GPIO pin or a programmable internal reference

- Output can be either an interrupt source or an output to an external pin

## Operation

One of the comparator inputs can be connected to an internal reference that is a user-selectable reference and is user-programmable with 200 mV resolution.

The comparator can be powered down to save supply current. For details, see the <u>Power</u> <u>Control Register 0</u> section on page 31.

**Caution:** As a result of the propagation delay of the comparator, Zilog does not recommend enabling the comparator without first disabling interrupts and waiting for the comparator output to settle. This delay prevents spurious interrupts after comparator enabling.

The following example shows how to safely enable the comparator:

```

di

ld cmp0,r0; load some new configuration

nop

nop ; wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

### **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control Register before programming or erasing Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, Flash memory can be enabled for mass erase or page erase by writing the appropriate enable command to the FCTL. Page erase applies only to the active page selected in Flash Page Select Register. Mass erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its Locked state. The write-only Flash Control Register shares its register file address with the read-only Flash Status Register.

| Bit     | 7    | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|---------------|---|---|---|---|---|---|--|

| Field   | FCMD |               |   |   |   |   |   |   |  |

| RESET   | 0    | 0             | 0 | 0 | 0 | 0 | 0 | 0 |  |

| R/W     | W    | W W W W W W W |   |   |   |   |   |   |  |

| Address | FF8H |               |   |   |   |   |   |   |  |

| Table 72. | Flash | Control | Register | (FCTL) |

|-----------|-------|---------|----------|--------|

|-----------|-------|---------|----------|--------|

#### Bit Description

| [7:0] | Flash Command |

|-------|---------------|

|-------|---------------|

- FCMD 73H = First unlock command.

- 8CH = Second unlock command.

- 95H = Page erase command (must be third command in sequence to initiate page erase).

- 63H = Mass erase command (must be third command in sequence to initiate mass erase).

- 5EH = Enable Flash Sector Protect Register access.

### **Runtime Counter**

The OCD contains a 16-bit runtime counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

## **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash read protect option bit (FRP). The FRP prevents the code in memory from being read out of the Z8 Encore! F0830 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 95 summarizes the On-Chip Debugger commands. This table indicates the commands that operate when the device is not in DEBUG Mode (normal operation) and the commands that are disabled by programming the FRP.

| Debug Command              | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                                     |

|----------------------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                | -                                                                                                                                                                                |

| Reserved                   | 01H             | _                                  | _                                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                                | _                                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                                  | -                                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                                | Cannot clear DBGMODE bit                                                                                                                                                         |

| Read OCD Control Register  | 05H             | Yes                                | _                                                                                                                                                                                |

| Write Program Counter      | 06H             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Counter       | 07H             | _                                  | Disabled                                                                                                                                                                         |

| Write Register             | 08H             | _                                  | Only writes of the Flash Memory Con-<br>trol registers are allowed. Additionally,<br>only the Mass Erase command is<br>allowed to be written to the Flash Con-<br>trol register. |

| Read Register              | 09H             | _                                  | Disabled                                                                                                                                                                         |

| Write Program Memory       | 0AH             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Memory        | 0BH             | _                                  | Disabled                                                                                                                                                                         |

| Write Data Memory          | 0CH             | _                                  | Yes                                                                                                                                                                              |

| Read Data Memory           | 0DH             | _                                  | _                                                                                                                                                                                |

#### Table 95. On-Chip Debugger Command Summary

**Read OCD Control Register (05H).** The read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

**Write Program Counter (06H).** The write program counter command, writes the data that follows to the eZ8 CPU's program counter (PC). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, the program counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

**Read Program Counter (07H).** The read program counter command, reads the value in the eZ8 CPUs program counter (PC). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The write register command, writes data to the register file. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash read protect option bit is enabled, only writes to the Flash control registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**Read Register (09H).** The read register command, reads data from the register file. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFH for all of the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

**Write Program Memory (0AH).** The write program memory command, writes data to program memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, the data is discarded.

# eZ8 CPU Instruction Set

This chapter describes the following features of the eZ8 CPU instruction set: <u>Assembly Language Programming Introduction</u>: see page 162 <u>Assembly Language Syntax</u>: see page 163 <u>eZ8 CPU Instruction Notation</u>: see page 164 <u>eZ8 CPU Instruction Classes</u>: see page 166 <u>eZ8 CPU Instruction Summary</u>: see page 171

## **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (op codes and operands) to represent the instructions themselves. The op codes identify the instruction while the operands represent memory locations, registers or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement contains labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, these pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is provided in the following example.

Z8 Encore!<sup>®</sup> F0830 Series Product Specification

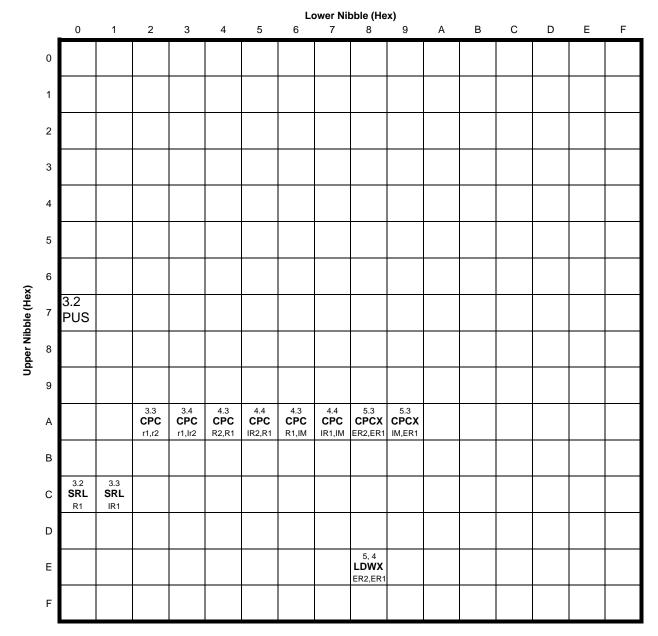

Figure 30. Second Op Code Map after 1FH

183

|                      |                                                  | $V_{DD} = 2.7 \text{ to } 3.6 \text{ V}$ $T_{A} = -4$ |     |     | .7 to 3.6V<br>-40°C to<br>05°C |       |                           |  |  |

|----------------------|--------------------------------------------------|-------------------------------------------------------|-----|-----|--------------------------------|-------|---------------------------|--|--|

| Symbol               | Parameter                                        | Min                                                   | Max | Min | Max                            | Units | Conditions                |  |  |

| T <sub>XINR</sub>    | System Clock Rise<br>Time                        |                                                       |     | -   | 3                              | ns    | T <sub>CLK</sub> = 50 ns  |  |  |

| T <sub>XINF</sub>    | System Clock Fall<br>Time                        |                                                       |     | -   | 3                              | ns    | T <sub>CLK</sub> = 50 ns  |  |  |

| T <sub>XTALSET</sub> | Crystal Oscillator<br>Setup Time                 |                                                       |     | _   | 30,000                         | cycle | Crystal oscillator cycles |  |  |

| T <sub>IPOSET</sub>  | Internal Precision<br>Oscillator Startup<br>Time |                                                       |     | _   | 25                             | μs    | Startup time after enable |  |  |

| T <sub>WDTSET</sub>  | WDT Startup Time                                 |                                                       |     | _   | 50                             | μs    | Startup time after reset  |  |  |

#### Table 117. AC Characteristics (Continued)

## **On-Chip Peripheral AC and DC Electrical Characteristics**

|                  |                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = −40°C to<br>+105°C |                  |      |       |                                                                                                          |  |

|------------------|---------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|------|-------|----------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                                                 | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max  | Units | Conditions                                                                                               |  |

| V <sub>POR</sub> | Power-On Reset<br>Voltage Threshold                                       |                               |     |     | 2.20                                | 2.45             | 2.70 | V     | V <sub>DD</sub> = V <sub>POR</sub><br>(default VBO trim)                                                 |  |

| V <sub>VBO</sub> | Voltage Brown-Out<br>Reset Voltage<br>Threshold                           |                               |     |     | 2.15                                | 2.40             | 2.65 | V     | V <sub>DD</sub> = V <sub>VBO</sub><br>(default VBO trim)                                                 |  |

|                  | V <sub>POR</sub> to V <sub>VBO</sub><br>hysteresis                        |                               |     |     |                                     | 50               | 75   | mV    |                                                                                                          |  |

|                  | Starting V <sub>DD</sub><br>voltage to ensure<br>valid Power-On<br>Reset. |                               |     |     | _                                   | V <sub>SS</sub>  | -    | V     |                                                                                                          |  |

| T <sub>ANA</sub> | Power-On Reset<br>Analog Delay                                            |                               |     |     | -                                   | 50               | _    | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub><br>Digital Reset delay<br>follows T <sub>ANA</sub> |  |

Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

Note: <sup>1</sup>Data in the typical column is from characterization at 3.3V and 0°C. These values are provided for design guidance only and are not tested in production.

## **Analog-to-Digital Converter**

For more information about these ADC registers, see the <u>ADC Control Register Defini-</u> tions section on page 101.

### Hex Address: F70

| Bit     | 7     | 6        | 5     | 4     | 3        | 2          | 1   | 0   |

|---------|-------|----------|-------|-------|----------|------------|-----|-----|

| Field   | START | Reserved | REFEN | ADCEN | Reserved | ANAIN[2:0] |     |     |

| RESET   | 0     | 0        | 0     | 0     | 0        | 0          | 0   | 0   |

| R/W     | R/W1  | R/W      | R/W   | R/W   | R/W      | R/W        | R/W | R/W |

| Address | F70h  |          |       |       |          |            |     |     |

#### Table 146. ADC Control Register 0 (ADCCTL0)

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>START   | <ul> <li>ADC Start/Busy</li> <li>0 = Writing to 0 has no effect; reading a 0 indicates that the ADC is available to begin a conversion.</li> <li>1 = Writing to 1 starts a conversion; reading a 1 indicates that a conversion is currently in progress.</li> </ul>                                                                                                                                                                                                                                                                                                                               |

| [6]            | This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [5]<br>REFEN   | <ul> <li>Reference Enable</li> <li>0 = Internal reference voltage is disabled allowing an external reference voltage to be used by the ADC.</li> <li>1 = Internal reference voltage for the ADC is enabled. The internal reference voltage can be measured on the V<sub>REF</sub> pin.</li> </ul>                                                                                                                                                                                                                                                                                                 |

| [4]<br>ADCEN   | ADC Enable<br>0 = ADC is disabled for low power operation.<br>1 = ADC is enabled for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [3]            | This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [2:0]<br>ANAIN | Analog Input Select000 = ANA0 input is selected for analog to digital conversion.001 = ANA1 input is selected for analog to digital conversion.010 = ANA2 input is selected for analog to digital conversion.011 = ANA3 input is selected for analog to digital conversion.100 = ANA4 input is selected for analog to digital conversion.101 = ANA5 input is selected for analog to digital conversion.101 = ANA5 input is selected for analog to digital conversion.111 = ANA6 input is selected for analog to digital conversion.111 = ANA7 input is selected for analog to digital conversion. |

#### Hex Address: FD3

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |  |

| Address |       | FD3H  |       |       |       |       |       |       |  |  |  |

#### Table 172. Port A Output Data Register (PAOUT)

#### Hex Address: FD4

#### Table 173. Port B GPIO Address Register (PBADDR)

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |      | PADDR[7:0]                  |   |   |   |   |   |   |  |  |

| RESET   | 00H  |                             |   |   |   |   |   |   |  |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address | FD4H |                             |   |   |   |   |   |   |  |  |

### Hex Address: FD5

#### Table 174. Port B Control Registers (PBCTL)

| Bit     | 7    | 6                       | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|-------------------------|---|---|---|---|---|---|--|--|

| Field   |      | PCTL                    |   |   |   |   |   |   |  |  |

| RESET   |      | 00H                     |   |   |   |   |   |   |  |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address | FD5H |                         |   |   |   |   |   |   |  |  |

#### Hex Address: FD6

#### Table 175. Port B Input Data Registers (PBIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|------|------|------|------|------|------|------|------|--|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |  |

| Address | FD6H |      |      |      |      |      |      |      |  |

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

read program memory CRC (0EH) 147 read register (09H) 146 read runtime counter (03H) 145 step instruction (10H) 148 stuff instruction (11H) 148 write data memory (0CH) 147 write OCD control register (04H) 145 write program counter (06H) 146 write program memory (0AH) 146 write register (08H) 146 on-chip debugger (OCD) 139 on-chip debugger signals 12 on-chip oscillator 157 one-shot mode 89 opcode map abbreviations 181 cell description 180 first 182 second after 1FH 183 operation 100 current measurement 99 voltage measurement timing diagram 100 Operational Description 21, 30, 33, 53, 68, 92, 98, 106, 108, 124, 134, 139, 151, 157, 161 OR 169 ordering information 200 ORX 169 oscillator signals 12

### Ρ

p 164

Packaging 199

part selection guide 2

PC 165

peripheral AC and DC electrical characteristics 190

pin characteristics 13

Pin Descriptions 7

polarity 164

POP 168

pop using extended addressing 168

POPX 168

port availability, device 33

port input timing (GPIO) 195

port output timing, GPIO 196 power supply signals 12 power-on reset (POR) 23 program control instructions 169 program counter 165 program memory 15 PUSH 168 push using extended addressing 168 PUSHX 168 PWM mode 89, 90 PxADDR register 40, 222, 223, 224, 225 PxCTL register 41, 222, 223, 224, 225

## R

R 165 r 164 RA register address 165 RCF 167, 168 register 165 flash control (FCTL) 119, 126, 127, 228 flash high and low byte (FFREQH and FRE-EQL) 123 flash page select (FPS) 121, 122 flash status (FSTAT) 120 GPIO port A-H address (PxADDR) 40, 222, 223, 224, 225 GPIO port A-H alternate function sub-registers 42 GPIO port A-H control address (PxCTL) 41, 222, 223, 224, 225 GPIO port A-H data direction sub-registers 41 OCD control 148 OCD status 150 watch-dog timer control (WDTCTL) 95, 107, 154, 217, 218, 226 watchdog timer control (WDTCTL) 29 watch-dog timer reload high byte (WDTH) 227 watchdog timer reload high byte (WDTH) 96 watch-dog timer reload low byte (WDTL) 227 watchdog timer reload low byte (WDTL) 97 watch-dog timer reload upper byte (WDTU) 227

236