# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

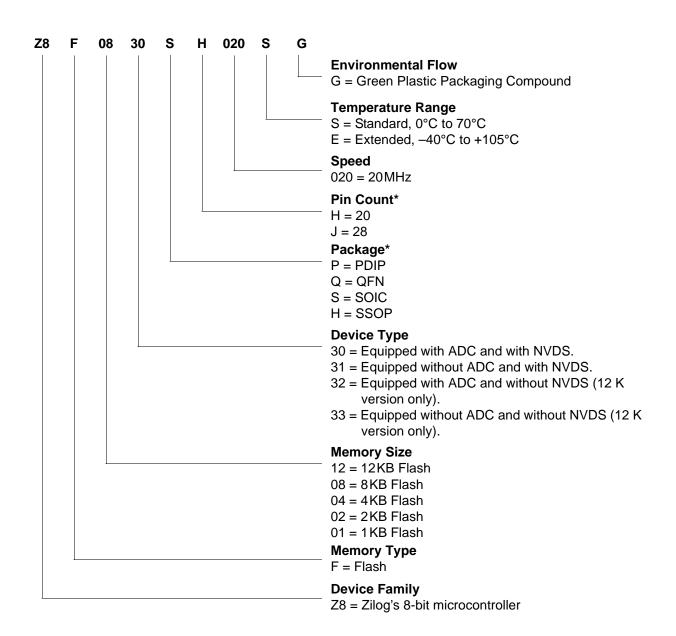

| Product StatusActiveCore ProcessoreZ8Core Size8-BitSpeed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O17Program Memory Size12KB (12K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 7x10b |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size8-BitSpeed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O17Program Memory Size12KB (12K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                              |

| Speed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O17Program Memory Size12KB (12K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                            |

| Connectivity-PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O17Program Memory Size12KB (12K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                      |

| PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O17Program Memory Size12KB (12K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                   |

| Number of I/O17Program Memory Size12KB (12K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                                        |

| Program Memory Size12KB (12K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                                                       |

| Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                                                                                        |

| EEPROM Size     -       RAM Size     256 x 8       Voltage - Supply (Vcc/Vdd)     2.7V ~ 3.6V                                                                                                                                                                                                   |

| RAM Size         256 x 8           Voltage - Supply (Vcc/Vdd)         2.7V ~ 3.6V                                                                                                                                                                                                               |

| Voltage - Supply (Vcc/Vdd) 2.7V ~ 3.6V                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                 |

| Data Converters     A/D 7x10b                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                 |

| Oscillator Type Internal                                                                                                                                                                                                                                                                        |

| Operating Temperature-40°C ~ 105°C (TA)                                                                                                                                                                                                                                                         |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                     |

| Package / Case 20-VQFN Exposed Pad                                                                                                                                                                                                                                                              |

| Supplier Device Package -                                                                                                                                                                                                                                                                       |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f1232qh020eg                                                                                                                                                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Signal<br>Mnemonic | I/O | Description                                                                                                                                                                                                                                                                   |

|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators        |     |                                                                                                                                                                                                                                                                               |

| X <sub>IN</sub>    | I   | External crystal input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| X <sub>OUT</sub>   | 0   | External crystal output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input        |     |                                                                                                                                                                                                                                                                               |

| CLK <sub>IN</sub>  | Ι   | Clock input signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |

| LED Drivers        |     |                                                                                                                                                                                                                                                                               |

| LED                | 0   | Direct LED drive capability. All Port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |

| On-Chip Debugger   | •   |                                                                                                                                                                                                                                                                               |

| DBG                | I/O | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |

|                    |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                                                                                                                                                               |

| Reset              |     |                                                                                                                                                                                                                                                                               |

| RESET              | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                            |

| Power Supply       |     |                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub>    | Ι   | Digital power supply.                                                                                                                                                                                                                                                         |

| AV <sub>DD</sub>   | I   | Analog power supply.                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>    | I   | Digital ground.                                                                                                                                                                                                                                                               |

| AV <sub>SS</sub>   | I   | Analog ground.                                                                                                                                                                                                                                                                |

|                    |     | gnals are available only in the 28-pin packages with ADC. They are replaced by PB6 kages without ADC.                                                                                                                                                                         |

#### Table 4. Signal Descriptions (Continued)

# **Reset Sources**

Table 10 lists the possible sources of a system reset.

| Operating Mode       | Reset Source                                             | Special Conditions                                                  |

|----------------------|----------------------------------------------------------|---------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-Out                         | Reset delay begins after supply voltage exceeds POR level.          |

|                      | Watchdog Timer time-out when con-<br>figured for reset   | None.                                                               |

|                      | RESET pin assertion                                      | All reset pulses less than four system clocks in width are ignored. |

|                      | On-Chip Debugger initiated reset<br>(OCDCTL[0] set to 1) | System, except the On-Chip Debugger is unaffected by the reset.     |

| STOP Mode            | Power-On Reset/Voltage Brown-Out                         | Reset delay begins after supply voltage exceeds POR level.          |

|                      | RESET pin assertion                                      | All reset pulses less than 12 ns are ignored.                       |

|                      | DBG pin driven Low                                       | None.                                                               |

### **Power-On Reset**

Each device in the Z8 Encore! F0830 Series contains an internal Power-On Reset circuit. The POR circuit monitors the digital supply voltage and holds the device in the Reset state until the digital supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR counter has timed out. If the crystal oscillator is enabled by the option bits, the time-out is longer.

After the Z8 Encore! F0830 Series device exits the Power-On Reset state, the eZ8 CPU fetches the reset vector. Following the Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1.

Figure 6 displays the Power-On Reset operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the POR threshold voltage ( $V_{POR}$ ).

# General Purpose Input/Output

The Z8 Encore! F0830 Series products support a maximum of 25 port pins (Ports A–D) for General Purpose Input/Output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

## **GPIO Port Availability by Device**

Table 15 lists the port pins available with each device and package type.

|                                                   |         | 10-Bit |        |        |        |        |           |

|---------------------------------------------------|---------|--------|--------|--------|--------|--------|-----------|

| Devices                                           | Package | ADC    | Port A | Port B | Port C | Port D | Total I/O |

| Z8F1232, Z8F0830,<br>Z8F0430, Z8F0230,<br>Z8F0130 | 20-pin  | Yes    | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F1233, Z8F0831<br>Z8F0431, Z8F0231<br>Z8F0131   | 20-pin  | No     | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F1232, Z8F0830,<br>Z8F0430, Z8F0230,<br>Z8F0130 | 28-pin  | Yes    | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F1233, Z8F0831<br>Z8F0431, Z8F0231<br>Z8F0131   | 28-pin  | No     | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

#### Table 15. Port Availability by Device and Package Type

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for Alternate function CLKIN. Write to the Oscillator Control Register (see the <u>Oscillator Control Register Definitions</u> section on page 154) to select the PB3 as the system clock.

| Port                | Pin | Mnemonic   | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1</sup> | PA0 | T0IN/T0OUT | Timer 0 input/Timer 0 output complement | N/A                                     |

|                     |     | Reserved   |                                         |                                         |

|                     | PA1 | TOOUT      | Timer 0 output                          |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA2 | Reserved   | Reserved                                |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA3 | Reserved   | Reserved                                |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA4 | Reserved   | Reserved                                |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA5 | Reserved   | Reserved                                |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA6 | T1IN/T1OUT | Timer 1 input/Timer 1 output complement |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA7 | T1OUT      | Timer 1 output                          |                                         |

|                     |     | Reserved   |                                         |                                         |

#### Table 16. Port Alternate Function Mapping

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

| Port                | Pin                    | Mnemonic  | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|------------------------|-----------|--------------------------------|-----------------------------------------|

| Port C <sup>3</sup> | ort C <sup>3</sup> PC0 | Reserved  |                                | AFS1[0]: 0                              |

|                     |                        | ANA4/CINP | ADC or comparator input        | AFS1[0]: 1                              |

|                     | PC1                    | Reserved  |                                | AFS1[1]: 0                              |

|                     |                        | ANA5/CINN | ADC or comparator input        | AFS1[1]: 1                              |

|                     | PC2                    | Reserved  |                                | AFS1[2]: 0                              |

|                     |                        | ANA6      | ADC analog input               | AFS1[2]: 1                              |

|                     | PC3                    | COUT      | Comparator output              | AFS1[3]: 0                              |

|                     |                        | Reserved  |                                | AFS1[3]: 1                              |

|                     | PC4                    | Reserved  |                                | AFS1[4]: 0                              |

|                     |                        |           |                                | AFS1[4]: 1                              |

|                     | PC5                    | Reserved  |                                | AFS1[5]: 0                              |

|                     |                        |           |                                | AFS1[5]: 1                              |

|                     | PC6                    | Reserved  |                                | AFS1[6]: 0                              |

|                     |                        |           |                                | AFS1[6]: 1                              |

|                     | PC7                    | Reserved  |                                | AFS1[7]: 0                              |

|                     |                        |           |                                | AFS1[7]: 1                              |

| Port D <sup>1</sup> | PD0                    | RESET     | Default to be Reset function   | N/A                                     |

#### Table 16. Port Alternate Function Mapping (Continued)

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

## Port A–C Input Data Registers

Reading from the Port A–C Input Data registers, shown in Table 29, return the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those not included in the 8- and 28-pin packages, as well as those not included in the ADC-enabled 28-pin packages.

| Bit     | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------------------|------|------|------|------|------|------|------|

| Field   | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W     | R                | R    | R    | R    | R    | R    | R    | R    |

| Address | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |

|         |                  |      |      |      |      |      |      |      |

#### Table 29. Port A–C Input Data Registers (PxIN)

Bit Description

[7:0] Port Input Data

PxIN Sampled data from the corresponding port pin input. 0 = Input data is logical 0 (Low).

1 =Input data is logical 1 (High).

Note: x indicates the specific GPIO port pin number (7–0).

# **Analog-to-Digital Converter**

The Z8 Encore! MCU includes an eight-channel Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC). The ADC converts an analog input signal to a 10-bit binary number. The features of the SAR ADC include:

- Eight analog input sources multiplexed with general purpose I/O ports

- Fast conversion time, less than 11.9µs

- Programmable timing controls

- Interrupt on conversion complete

- Internal voltage reference generator

- Ability to select external reference voltage

- When configuring an ADC using external  $V_{\text{REF}}, \text{PB5}$  is used as  $V_{\text{REF}}$  in the 28-pin package

### Architecture

The ADC architecture, displayed in Figure 11, consists of an 8-input multiplexer, sampleand-hold amplifier and 10-bit SAR ADC. The ADC digitizes the signal on a selected channel and stores the digitized data in the ADC data registers. In an environment with high electrical noise, an external RC filter must be added at the input pins to reduce highfrequency noise.

$T_{CONV} = T_{S/H} + T_{CON}$  $T_{CONV} = T_S + T_H + 13 * SCLK * 16$

where:

$$\begin{split} & \text{SCLK} = \text{System Clock} \\ & \text{T}_{\text{CONV}} = \text{Total conversion time} \\ & \text{T}_{\text{S}} = \text{Sample time} (\text{SCLK} * \text{ADCST}) \\ & \text{T}_{\text{CON}} = \text{Conversion time} (13 * \text{SCLK} * 16) \\ & \text{T}_{\text{H}} = \text{Hold time} (\text{SCLK} * \text{ADCSST}) \\ & \text{DIV} = 16 (\text{fixed to divide by 16 for F0830 Series products}) \end{split}$$

**Example:** For an F0830 Series MCU running @ 20MHz:

$$\begin{split} T_{CONV} &= 1 \mu s + 0.5 \mu s + 13 * SCLK * DIV \\ T_{CONV} &= 1 \mu s + 0.5 \mu s + 13 * (1/20 \text{ MHz}) * 16 = 11.9 \mu s \end{split}$$

# Flash Memory

The products in the Z8 Encore! F0830 Series features either 1KB (1024 bytes with NVDS), 2KB (2048 bytes with NVDS), 4KB (4096 bytes with NVDS), 8KB (8192 bytes with NVDS) or 12KB (12288 bytes with no NVDS) of nonvolatile Flash memory with read/write/erase capability. Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F0830 Series, each sector maps to one page (for 1KB, 2KB and 4KB devices), two pages (8KB device) or three pages (12KB device).

The first two bytes of Flash program memory is used as Flash option bits. For more information, see *the* <u>Flash Option Bits</u> chapter on page 124.

Table 69 lists the Flash memory configuration for each device in the Z8 Encore! F0830 Series. Figures 14 through 18 display the memory arrangements for each Flash memory size.

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F123x     | 12 (12,288)              | 24          | 0000H–2FFFH                    | 1536                         |

| Z8F083x     | 8 (8196)                 | 16          | 0000H-1FFFH                    | 1024                         |

| Z8F043x     | 4 (4096)                 | 8           | 0000H–0FFFH                    | 512                          |

| Z8F023x     | 2 (2048)                 | 4           | 0000H–07FFH                    | 512                          |

| Z8F013x     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

Figure 14. 1K Flash with NVDS

<sup>03</sup>FFH

03FFH

03FFH

0200H

Sector 1

Page 1

0200H

01FFH

Sector 0

Page 0

01FFh

0000H

0000H

0000H

0000H

## **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control Register before programming or erasing Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, Flash memory can be enabled for mass erase or page erase by writing the appropriate enable command to the FCTL. Page erase applies only to the active page selected in Flash Page Select Register. Mass erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its Locked state. The write-only Flash Control Register shares its register file address with the read-only Flash Status Register.

| Bit     | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|------|---|---|----|----|---|---|---|--|

| Field   | FCMD |   |   |    |    |   |   |   |  |

| RESET   | 0    | 0 | 0 | 0  | 0  | 0 | 0 | 0 |  |

| R/W     | W    | W | W | W  | W  | W | W | W |  |

| Address |      |   |   | FF | 8H |   |   |   |  |

| Table 72. | Flash | Control | Register | (FCTL) |

|-----------|-------|---------|----------|--------|

|-----------|-------|---------|----------|--------|

#### Bit Description

FCMD

| [7:0] | Flash Command |

|-------|---------------|

|-------|---------------|

- 73H = First unlock command.

- 8CH = Second unlock command.

- 95H = Page erase command (must be third command in sequence to initiate page erase).

- 63H = Mass erase command (must be third command in sequence to initiate mass erase).

- 5EH = Enable Flash Sector Protect Register access.

# **Oscillator Control**

The Z8 Encore! F0830 Series device uses five possible clocking schemes. Each one of these is user-selectable.

- On-chip precision trimmed RC oscillator

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low precision Watchdog Timer Oscillator

In addition, Z8 Encore! F0830 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

## Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined further in this document.

### **System Clock Selection**

The oscillator control block selects from the available clocks. *Table 98* describes each clock source and its usage.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! F0830 Series device ceases functioning and can only be recovered by power-on-reset.

## **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

#### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

Figure 24 displays the oscillator control clock switching flow. See <u>Table 117</u> on page 189 to review the waiting times of various oscillator circuits.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2           | 1      | 0 |  |  |

|---------|-------|-------|-------|-------|-------|-------------|--------|---|--|--|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN |             | SCKSEL |   |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0           | 0      | 0 |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W R/W R/W |        |   |  |  |

| Address |       | F86H  |       |       |       |             |        |   |  |  |

| Table 99. O | Scillator | Control | Register | (OSCCTL) |

|-------------|-----------|---------|----------|----------|

|-------------|-----------|---------|----------|----------|

| Bit   | Description                                                       |

|-------|-------------------------------------------------------------------|

| [7]   | Internal Precision Oscillator Enable                              |

| INTEN | 1 = Internal Precision Oscillator is enabled.                     |

|       | 0 = Internal Precision Oscillator is disabled.                    |

| [6]   | Crystal Oscillator Enable                                         |

| XTLEN | This setting overrides the GPIO register control for PA0 and PA1. |

|       | 1 = Crystal oscillator is enabled.                                |

|       | 0 = Crystal oscillator is disabled.                               |

| [5]   | Watchdog Timer Oscillator Enable                                  |

| WDTEN | 1 = Watchdog Timer Oscillator is enabled.                         |

|       | 0 = Watchdog Timer Oscillator is disabled.                        |

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

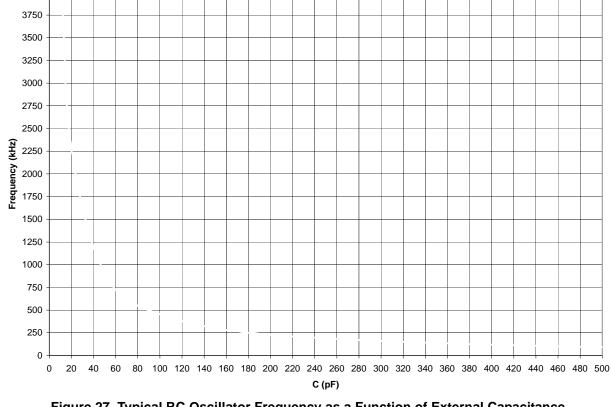

Figure 27. Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$  Resistor

**Caution:** When using the external RC OSCILLATOR Mode, the oscillator can stop oscillating if the power supply drops below 2.7V but before it drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7V.

160

4000

| Assembly      |                          |      | ress<br>ode | Op<br>Code(s) | Flags |   |   |   |   |   | Fetch | Instr. |

|---------------|--------------------------|------|-------------|---------------|-------|---|---|---|---|---|-------|--------|

| Mnemonic      | Symbolic Operation       | dst  | src         | (Hex)         | С     | Ζ | S | ۷ | D | Н |       |        |

| LD dst, rc    | dst ← src                | r    | IM          | 0C-FC         | _     | - | - | _ | - | _ | 2     | 2      |

|               |                          | r    | X(r)        | C7            | _     |   |   |   |   |   | 3     | 3      |

|               |                          | X(r) | r           | D7            | _     |   |   |   |   |   | 3     | 4      |

|               |                          | r    | lr          | E3            | _     |   |   |   |   |   | 2     | 3      |

|               |                          | R    | R           | E4            | _     |   |   |   |   |   | 3     | 2      |

|               |                          | R    | IR          | E5            | _     |   |   |   |   |   | 3     | 4      |

|               |                          | R    | IM          | E6            | _     |   |   |   |   |   | 3     | 2      |

|               |                          | IR   | IM          | E7            | _     |   |   |   |   |   | 3     | 3      |

|               |                          | lr   | r           | F3            | _     |   |   |   |   |   | 2     | 3      |

|               |                          | IR   | R           | F5            | _     |   |   |   |   |   | 3     | 3      |

| LDC dst, src  | dst ← src                | r    | Irr         | C2            | -     | _ | _ | _ | _ | - | 2     | 5      |

|               |                          | lr   | Irr         | C5            | _     |   |   |   |   |   | 2     | 9      |

|               |                          | Irr  | r           | D2            | _     |   |   |   |   |   | 2     | 5      |

| LDCI dst, src | dst ← src                | lr   | Irr         | C3            | -     | - | - | - | - | - | 2     | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | D3            |       |   |   |   |   |   | 2     | 9      |

| LDE dst, src  | dst ← src                | r    | Irr         | 82            | _     | _ | _ | _ | _ | - | 2     | 5      |

|               |                          | Irr  | r           | 92            | _     |   |   |   |   |   | 2     | 5      |

| LDEI dst, src | dst ← src                | lr   | Irr         | 83            | _     | _ | _ | _ | _ | _ | 2     | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | 93            |       |   |   |   |   |   | 2     | 9      |

| LDWX dst, src | dst ← src                | ER   | ER          | 1FE8          | -     | _ | _ | _ | _ | _ | 5     | 4      |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

|                      |                                                  |                                                                                                                                                                             |     |         | •        |       |                           |  |

|----------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|----------|-------|---------------------------|--|

|                      |                                                  | $V_{DD} = 2.7 \text{ to } 3.6 \text{V}$<br>$V_{DD} = 2.7 \text{ to } 3.6 \text{V}$<br>$T_{A} = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}$<br>$+105^{\circ}\text{C}$ |     |         | -40°C to |       |                           |  |

| Symbol               | Parameter                                        | Min                                                                                                                                                                         | Max | Min Max |          | Units | Conditions                |  |

| T <sub>XINR</sub>    | System Clock Rise<br>Time                        |                                                                                                                                                                             |     | -       | 3        | ns    | T <sub>CLK</sub> = 50 ns  |  |

| T <sub>XINF</sub>    | System Clock Fall<br>Time                        |                                                                                                                                                                             |     | -       | 3        | ns    | T <sub>CLK</sub> = 50 ns  |  |

| T <sub>XTALSET</sub> | Crystal Oscillator<br>Setup Time                 |                                                                                                                                                                             |     | _       | 30,000   | cycle | Crystal oscillator cycles |  |

| T <sub>IPOSET</sub>  | Internal Precision<br>Oscillator Startup<br>Time |                                                                                                                                                                             |     | _       | 25       | μs    | Startup time after enable |  |

| T <sub>WDTSET</sub>  | WDT Startup Time                                 |                                                                                                                                                                             |     | _       | 50       | μs    | Startup time after reset  |  |

#### Table 117. AC Characteristics (Continued)

## **On-Chip Peripheral AC and DC Electrical Characteristics**

|                  |                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = −40°C to<br>+105°C |                  |      |       |                                                                                                          |  |

|------------------|---------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|------|-------|----------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                                                 | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max  | Units | Conditions                                                                                               |  |

| V <sub>POR</sub> | Power-On Reset<br>Voltage Threshold                                       |                               |     |     | 2.20                                | 2.45             | 2.70 | V     | V <sub>DD</sub> = V <sub>POR</sub><br>(default VBO trim)                                                 |  |

| V <sub>VBO</sub> | Voltage Brown-Out<br>Reset Voltage<br>Threshold                           |                               |     |     | 2.15                                | 2.40             | 2.65 | V     | V <sub>DD</sub> = V <sub>VBO</sub><br>(default VBO trim)                                                 |  |

|                  | V <sub>POR</sub> to V <sub>VBO</sub><br>hysteresis                        |                               |     |     |                                     | 50               | 75   | mV    |                                                                                                          |  |

|                  | Starting V <sub>DD</sub><br>voltage to ensure<br>valid Power-On<br>Reset. |                               |     |     | _                                   | V <sub>SS</sub>  | _    | V     |                                                                                                          |  |

| T <sub>ANA</sub> | Power-On Reset<br>Analog Delay                                            |                               |     |     | _                                   | 50               | _    | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub><br>Digital Reset delay<br>follows T <sub>ANA</sub> |  |

Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

Note: <sup>1</sup>Data in the typical column is from characterization at 3.3V and 0°C. These values are provided for design guidance only and are not tested in production.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# **Analog-to-Digital Converter**

For more information about these ADC registers, see the <u>ADC Control Register Defini-</u> tions section on page 101.

#### Hex Address: F70

| Bit     | 7     | 6        | 5     | 4     | 3        | 2           | 1          | 0 |  |  |

|---------|-------|----------|-------|-------|----------|-------------|------------|---|--|--|

| Field   | START | Reserved | REFEN | ADCEN | Reserved |             | ANAIN[2:0] |   |  |  |

| RESET   | 0     | 0        | 0     | 0     | 0        | 0           | 0          | 0 |  |  |

| R/W     | R/W1  | R/W      | R/W   | R/W   | R/W      | R/W R/W R/W |            |   |  |  |

| Address |       | F70h     |       |       |          |             |            |   |  |  |

#### Table 146. ADC Control Register 0 (ADCCTL0)

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>START   | <ul> <li>ADC Start/Busy</li> <li>0 = Writing to 0 has no effect; reading a 0 indicates that the ADC is available to begin a conversion.</li> <li>1 = Writing to 1 starts a conversion; reading a 1 indicates that a conversion is currently in progress.</li> </ul>                                                                                                                                                                                                                                                                                                                               |

| [6]            | This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [5]<br>REFEN   | <ul> <li>Reference Enable</li> <li>0 = Internal reference voltage is disabled allowing an external reference voltage to be used by the ADC.</li> <li>1 = Internal reference voltage for the ADC is enabled. The internal reference voltage can be measured on the V<sub>REF</sub> pin.</li> </ul>                                                                                                                                                                                                                                                                                                 |

| [4]<br>ADCEN   | ADC Enable<br>0 = ADC is disabled for low power operation.<br>1 = ADC is enabled for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [3]            | This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [2:0]<br>ANAIN | Analog Input Select000 = ANA0 input is selected for analog to digital conversion.001 = ANA1 input is selected for analog to digital conversion.010 = ANA2 input is selected for analog to digital conversion.011 = ANA3 input is selected for analog to digital conversion.100 = ANA4 input is selected for analog to digital conversion.101 = ANA5 input is selected for analog to digital conversion.101 = ANA5 input is selected for analog to digital conversion.111 = ANA6 input is selected for analog to digital conversion.111 = ANA7 input is selected for analog to digital conversion. |

## **GPIO Port A**

For more information about the GPIO registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

#### Hex Address: FD0

#### Table 169. Port A GPIO Address Register (PAADDR)

| Bit     | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|-----|-----------------------------|---|----|----|---|---|---|--|--|--|

| Field   |     | PADDR[7:0]                  |   |    |    |   |   |   |  |  |  |

| RESET   |     | 00H                         |   |    |    |   |   |   |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |  |  |

| Address |     |                             |   | FD | 0H |   |   |   |  |  |  |

#### Hex Address: FD1

#### Table 170. Port A Control Registers (PACTL)

| Bit     | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|-----|-----------------------------|---|----|----|---|---|---|--|--|--|

| Field   |     | PCTL                        |   |    |    |   |   |   |  |  |  |

| RESET   |     | 00H                         |   |    |    |   |   |   |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |  |  |

| Address |     |                             |   | FD | 1H |   |   |   |  |  |  |

#### Hex Address: FD2

#### Table 171. Port A Input Data Registers (PAIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |

| Address | FD2H |      |      |      |      |      |      |      |

#### Hex Address: FF1

#### Table 186. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit                                                                                       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                     | WDTU |      |      |      |      |      |      |      |

| RESET                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W                                                                                       | R/W* |

| Address                                                                                   | FF1H |      |      |      |      |      |      |      |

| Note: *Read returns the current WDT count value; write sets the appropriate reload value. |      |      |      |      |      |      |      |      |

#### Hex Address: FF2

#### Table 187. Watchdog Timer Reload High Byte Register (WDTH)

| Bit                                                                                       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|--|

| Field                                                                                     | WDTH |      |      |      |      |      |      |      |  |

| RESET                                                                                     | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    |  |

| R/W                                                                                       | R/W* |  |

| Address                                                                                   | FF2H |      |      |      |      |      |      |      |  |

| Note: *Read returns the current WDT count value; write sets the appropriate reload value. |      |      |      |      |      |      |      |      |  |

#### Hex Address: FF3

#### Table 188. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit                                                                                       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|--|

| Field                                                                                     | WDTL |      |      |      |      |      |      |      |  |

| RESET                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |

| R/W                                                                                       | R/W* |  |

| Address                                                                                   | FF3H |      |      |      |      |      |      |      |  |

| Note: *Read returns the current WDT count value; write sets the appropriate reload value. |      |      |      |      |      |      |      |      |  |

#### Hex Addresses: FF4–FF5

This address range is reserved.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# Index

### **Symbols**

@ 165# 165% 165

### **Numerics**

10-bit ADC 4

## Α

absolute maximum ratings 184 AC characteristics 189 ADC 166 block diagram 99 overview 98 ADC Channel Register 1 (ADCCTL) 102 ADC Data High Byte Register (ADCDH) 103 ADC Data Low Bit Register (ADCDL) 103, 104, 105 **ADCX 166** ADD 166 add - extended addressing 166 add with carry 166 add with carry - extended addressing 166 additional symbols 165 address space 14 **ADDX 166** analog block/PWM signal synchronization 100 analog block/PWM signal zynchronization 100 analog signals 11 analog-to-digital converter overview 98 AND 169 **ANDX 169** architecture voltage measurements 98 arithmetic instructions 166 assembly language programming 162 assembly language syntax 163

## В

B 165 b 164 **BCLR 167** binary number suffix 165 BIT 167 bit 164 clear 167 manipulation instructions 167 set 167 set or clear 167 swap 167 test and jump 169 test and jump if non-zero 169 test and jump if zero 169 bit jump and test if non-zero 166 bit swap 169 block diagram 3 block transfer instructions 167 **BRK 169 BSET 167** BSWAP 167. 169 **BTJ** 169 BTJNZ 166, 169 **BTJZ 169**

## С

calibration and compensation, motor control measurements 101 CALL procedure 169 capture mode 89, 90 capture/compare mode 89 cc 164 CCF 168 characteristics, electrical 184 clear 168 CLR 168 COM 169 compare 89

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

load external data to/from data memory and autoincrement addresses 167 load external to/from data memory and auto-increment addresses 168 load instructions 168 load using extended addressing 168 logical AND 169 logical AND/extended addressing 169 logical exclusive OR 169 logical exclusive OR/extended addressing 169 logical OR 169 logical OR 169 logical OR/extended addressing 169

### Μ

master interrupt enable 55 memory data 16 program 15 mode capture 89, 90 capture/compare 89 continuous 89 counter 89 gated 89 one-shot 89 PWM 89.90 modes 89 motor control measurements ADC Control register definitions 101 calibration and compensation 101 interrupts 101 overview 98 **MULT 167** multiply 167

## Ν

noise, electrical 98 NOP (no operation) 168 notation b 164

DA 164 ER 164 IM 164 IR 164 Ir 164 IRR 164 Irr 164 p 164 R 165 r 164 RA 165 RR 165 rr 165 vector 165 X 165 notational shorthand 164

cc 164

## 0

OCD architecture 139 auto-baud detector/generator 142 baud rate limits 142 block diagram 139 breakpoints 143 commands 144 control register 148 data format 142 DBG pin to RS-232 Interface 140 debug mode 141 debugger break 169 interface 140 serial errors 143 status register 150 timing 197 OCD commands execute instruction (12H) 148 read data memory (0DH) 147 read OCD control register (05H) 146 read OCD revision (00H) 145 read OCD status register (02H) 145 read program counter (07H) 146 read program memory (0BH) 147