# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 12KB (12K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-VQFN Exposed Pad                                       |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1232qh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2012 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES or TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES or TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Table of Contents**

| Revision History                   | ii |

|------------------------------------|----|

| List of Figures                    | х  |

| List of Tables x                   | ii |

| Overview                           | 1  |

| Features                           | 1  |

| Part Selection Guide               | 2  |

| Block Diagram                      | 3  |

| CPU and Peripheral Overview        | 4  |

| General Purpose Input/Output       | 4  |

| Flash Controller                   | 4  |

| Nonvolatile Data Storage           | 5  |

| Internal Precision Oscillator      | 5  |

| External Crystal Oscillator        | 5  |

| 10-Bit Analog-to-Digital Converter | 5  |

| Analog Comparator                  | 5  |

| Timers                             | 5  |

| Interrupt Controller               | 5  |

| Reset Controller                   | 6  |

| On-Chip Debugger                   | 6  |

| Acronyms and Expansions            | 6  |

| Pin Description                    | 7  |

| Available Packages                 |    |

| Pin Configurations                 | 7  |

| Signal Descriptions                | 1  |

| Pin Characteristics                |    |

| Address Space                      | 4  |

| Register File                      |    |

| Program Memory                     | 5  |

| Data Memory                        |    |

| Flash Information Area 1           |    |

| Register Map 1                     | 7  |

| Reset and Stop Mode Recovery       | 21 |

| Reset Types                        |    |

| Reset Sources                      |    |

| Power-On Reset                     |    |

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

### xvi

| Table 119. | Flash Memory Electrical Characteristics and Timing 192                |

|------------|-----------------------------------------------------------------------|

| Table 120. | Watchdog Timer Electrical Characteristics and Timing 192              |

| Table 121. | Nonvolatile Data Storage                                              |

| Table 122. | Analog-to-Digital Converter Electrical Characteristics and Timing 193 |

| Table 123. | Comparator Electrical Characteristics                                 |

| Table 124. | GPIO Port Input Timing                                                |

| Table 125. | GPIO Port Output Timing 196                                           |

| Table 126. | On-Chip Debugger Timing 197                                           |

| Table 127. | Power Consumption Reference Table                                     |

| Table 128. | Z8 Encore! XP F0830 Series Ordering Matrix 200                        |

| Table 129. | Package and Pin Count Description 207                                 |

| Table 130. | Timer 0 High Byte Register (T0H) 208                                  |

| Table 131. | Timer 0 Low Byte Register (T0L) 209                                   |

| Table 132. | Timer 0 Reload High Byte Register (T0RH) 209                          |

| Table 133. | Timer 0 Reload Low Byte Register (T0RL)                               |

| Table 134. | Timer 0 PWM High Byte Register (T0PWMH) 209                           |

| Table 135. | Timer 0 PWM Low Byte Register (T0PWML) 210                            |

| Table 136. | Timer 0 Control Register 0 (T0CTL0)                                   |

| Table 137. | Timer 0 Control Register 1 (T0CTL1)                                   |

| Table 138. | Timer 1 High Byte Register (T1H) 210                                  |

| Table 139. | Timer 1 Low Byte Register (T1L) 211                                   |

| Table 140. | Timer 1 Reload High Byte Register (T1RH) 211                          |

| Table 141. | Timer 1 Reload Low Byte Register (T1RL)                               |

| Table 142. | Timer 1 PWM High Byte Register (T1PWMH) 211                           |

| Table 143. | Timer 1 PWM Low Byte Register (T1PWML)                                |

| Table 144. | Timer 1 Control Register 0 (T1CTL0)                                   |

| Table 145. | Timer 1 Control Register 1 (T1CTL1)                                   |

| Table 146. | ADC Control Register 0 (ADCCTL0)                                      |

| Table 147. | ADC Data High Byte Register (ADCD_H) 214                              |

| Table 148. | ADC Data Low Bits Register (ADCD_L) 214                               |

#### 1

# **Overview**

Zilog's Z8 Encore! MCU family of products are the first in a line of Zilog microcontroller products based on the 8-bit eZ8 CPU. The Z8 Encore! F0830 Series products expand on Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward-compatible with existing Z8 CPU instructions. The rich peripheral set of Z8 Encore! F0830 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices and sensors.

### **Features**

The key features of Z8 Encore! F0830 Series MCU include:

- 20MHz eZ8 CPU

- Up to 12KB Flash memory with in-circuit programming capability

- Up to 256B register RAM

- 64B Nonvolatile Data Storage (NVDS)

- Up to 25 I/O pins depending upon package

- Internal Precision Oscillator (IPO)

- External crystal oscillator

- Two enhanced 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Single-pin, On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-chip analog comparator

- Up to 17 interrupt sources

- Voltage Brown-Out (VBO) protection

- Power-On Reset (POR)

- 2.7V to 3.6V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 20- and 28-pin packages

- 0°C to +70°C standard temperature range and -40°C to +105°C extended temperature operating ranges

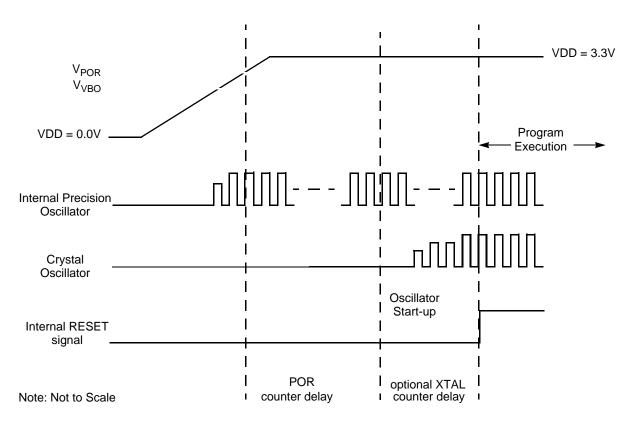

Figure 6. Power-On Reset Operation

### **Voltage Brown-Out Reset**

The devices in the Z8 Encore! F0830 Series provide low Voltage Brown-Out (VBO) protection. The VBO circuit forces the device to the Reset state, when the supply voltage drops below the VBO threshold voltage (unsafe level). While the supply voltage remains below the Power-On Reset threshold voltage ( $V_{POR}$ ), the VBO circuit holds the device in reset.

After the supply voltage exceeds the Power-On Reset threshold voltage, the device progresses through a full system reset sequence, as described in the POR section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 7 displays the Voltage Brown-Out operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

### 39

## **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the input pin signal. Other port pin interrupt sources, generate an interrupt when any edge occurs (both rising and falling). See the <u>Interrupt Controller</u> chapter on page 53 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data and output data; Table 17 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| P <i>x</i> ADDR           | Port A–D Address Register (selects subregisters)            |

| PxCTL                     | Port A–D Control Register (provides access to subregisters) |

| PxIN                      | Port A–D Input Data Register                                |

| P <i>x</i> OUT            | Port A–D Output Data Register                               |

| Port Subregister Mnemonic | Port Register Name                                          |

| PxDD                      | Data Direction                                              |

| P <i>x</i> AF             | Alternate Function                                          |

| PxOC                      | Output Control (open-drain)                                 |

| PxHDE                     | High Drive Enable                                           |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable                            |

| PxPUE                     | Pull-Up Enable                                              |

| PxAFS1                    | Alternate Function Set 1                                    |

| PxAFS2                    | Alternate Function Set 2                                    |

#### Table 17. GPIO Port Registers and Subregisters

reload. For the timer output to make a state change at a ONE-SHOT time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode

- Set the prescale value

- Set the initial output level (High or Low) if using the timer output Alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

One-Shot Mode Time-Out Period (s) =  $\frac{(\text{Reload Value} - \text{Start Value}) \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and for initiating the count:

1. Write to the Timer Control Register to:

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers. <u>Timer 0–1 High and Low Byte Registers</u>: see page 83

Timer Reload High and Low Byte Registers: see page 85

Timer 0-1 PWM High and Low Byte Registers: see page 86

Timer 0-1 Control Registers: see page 87

# Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers, shown in Tables 50 and 51, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register content when the timer is enabled; however, when the timer is disabled, a read from the TxL reads the TxL Register content directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations; therefore, simultaneous 16-bit writes are not possible. If either the timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low byte) at the next clock edge. The counter continues counting from the new value.

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     |     |     | Т     | Н    |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F00H, | F08H |     |     |     |

Table 50. Timer 0–1 High Byte Register (TxH)

| Table 51 | . Timer 0–1 | Low Byte | Register | (TxL) |

|----------|-------------|----------|----------|-------|

|          |             |          |          |       |

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     |     |     | Т     | Ľ    |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 1   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F01H, | F09H |     |     |     |

### Watchdog Timer Refresh

Upon first enable, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the Reload operation.

When the Z8 Encore! F0830 Series devices are operating in DEBUG Mode (using the On-Chip Debugger), the Watchdog Timer must be continuously refreshed to prevent any WDT time-outs.

### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash option bit determines the time-out response of the Watchdog Timer. See *the* <u>Flash Option</u> <u>Bits</u> chapter on page 124 for information about programming the WDT\_RES Flash option bit.

### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the Interrupt Controller and sets the WDT status bit in the Reset Status Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter resets to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter will not automatically return to its reload value.

The Reset Status Register (see <u>Table 12</u> on page 29) must be read before clearing the WDT interrupt. This read clears the WDT time-out flag and prevents further WDT interrupts occurring immediately.

### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! F0830 Series devices are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. See *the* <u>Reset and Stop Mode Recovery</u> *chapter on page 21* for more information about Stop Mode Recovery operations.

If interrupts are enabled, following completion of the Stop Mode Recovery, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executes the code from the vector address.

# **Option Bit Types**

This section describes the two types of Flash option bits offered in the F0830 Series.

### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits is provided because these locations contain application specific device configurations. The information contained here is lost when page 0 of program memory is erased.

## **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered by the user. Program memory can be erased without endangering these values. It is possible to alter working values of these bits by accessing the trim bit address and data registers, but these working values are lost after a power loss.

There are 32 bytes of trim data. To modify one of these values, the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20–3F only. The remaining information page is not accessible via the Trim Bit Address and Data registers.

During reset, the first 43 system clock cycles perform 43 Flash accesses. The six bits of the counter provide the lower six bits of the Flash memory address. All other address bits are set to 0. The option bit registers use the 6-bit address from the counter as an address and latch the data from the Flash on the positive edge of the IPO clock, allowing for a maximum of 344-bits (43 bytes) of option information to be read from Flash.

Because option information is stored in both the first two bytes of program memory and in the information area of Flash memory, the data must be placed in specific locations to be read correctly. In this case, the first two bytes at addresses 0 and 1 in program memory are read out and the remainder of the bytes are read out of the Flash information area.

### **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the Byte Write routine ( $0 \times 20B3$ ). At the return from the subroutine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 91. Additionally, user code should pop the address and data bytes off the stack.

The write routine uses 16 bytes of stack space in addition to the two bytes of address and data pushed by the user code. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $136\mu s$  (assuming a 20MHz system clock). For every 200 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 58ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $7\mu$ s execution time.

| Bit              | 7                                                 | 6            | 5               | 4           | 3             | 2           | 1                              | 0            |

|------------------|---------------------------------------------------|--------------|-----------------|-------------|---------------|-------------|--------------------------------|--------------|

| Field            |                                                   |              | Reserved        |             |               | FE          | IGADDR                         | WE           |

| Default<br>Value | 0                                                 | 0            | 0               | 0           | 0             | 0           | 0                              | 0            |

| Bit              | Descriptio                                        | n            |                 |             |               |             |                                |              |

| [7:3]            | Reserved<br>These bits                            | are reserved | d and must b    | e programn  | ned to 00000  | ).          |                                |              |

| [2]<br>FE        | Flash Erro<br>If a Flash e                        | -            | ted, this bit i | s set to 1. |               |             |                                |              |

| [1]<br>IGADDR    | <b>Illegal Add</b><br>When an N<br>this bit is se | VDS byte w   | rites to invali | d addresses | s occur (thos | e exceeding | g the NVDS a                   | array size), |

| [0]<br>WE        |                                                   | curs during  |                 |             | •             |             | ertain addres<br>he value writ | -            |

#### Table 91. Write Status Byte

is set to 1.

If the OCD receives a serial break (nine or more continuous bits low), the autobaud detector/generator resets. Reconfigure the autobaud detector/generator by sending 80H.

### **OCD Serial Errors**

The OCD can detect any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received Stop bit is Low)

- Transmit collision (simultaneous transmission by OCD and host detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long serial break back to the host and resets the autobaud detector/generator. A framing error or transmit collision may be caused by the host sending a serial break to the OCD. As a result of the open-drain nature of the interface, returning a serial break back to the host only extends the length of the serial break if the host releases the serial break early.

The host transmits a serial break on the DBG pin when first connecting to the Z8 Encore! F0830 Series devices or when recovering from an error. A serial break from the host resets the autobaud generator/detector, but does not reset the OCD Control Register. A serial break leaves the device in DEBUG Mode, if that is the current mode. The OCD is held in reset until the end of the serial break when the DBG pin returns high. Because of the opendrain nature of the DBG pin, the host can send a serial break to the OCD even if the OCD is transmitting a character.

### **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

# **Crystal Oscillator**

The products in the Z8 Encore! F0830 Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of its on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must remain unconnected. The on-chip crystal oscillator also contains a clock filter function. To see the settings for this clock filter, see Table 90 on page 133. By default, however, this clock filter is disabled; therefore, no divide to the input clock (namely, the frequency of the signal on the X<sub>IN</sub> input pin) can determine the frequency of the system clock when using the default settings.

**Note:** Although the X<sub>IN</sub> pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use. See *the* System Clock Selection *section on page 151* for more information.

# **Operating Modes**

The Z8 Encore! F0830 Series products support the following four OSCILLATOR Modes:

- Minimum power for use with very low frequency crystals (32kHz to 1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The OSCILLATOR Mode is selected using user-programmable Flash option bits. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

# **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Reg-

| 179 |

|-----|

|-----|

| Assembly      |                                                                                                                        |     | lress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | Fetch | Instr. |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------|---------------|---|---|-----|-----|---|---|-------|--------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst | src          | (Hex)         | С | Ζ | S   | ۷   | D | Н |       |        |

| TM dst, src   | dst AND src                                                                                                            | r   | r            | 72            | - | * | *   | 0   | _ | - | 2     | 3      |

|               |                                                                                                                        | r   | lr           | 73            | _ |   |     |     |   |   | 2     | 4      |

|               |                                                                                                                        | R   | R            | 74            |   |   |     |     |   |   | 3     | 3      |

|               |                                                                                                                        | R   | IR           | 75            | _ |   |     |     |   |   | 3     | 4      |

|               |                                                                                                                        | R   | IM           | 76            |   |   |     |     |   |   | 3     | 3      |

|               |                                                                                                                        | IR  | IM           | 77            |   |   |     |     |   |   | 3     | 4      |

| TMX dst, src  | dst AND src                                                                                                            | ER  | ER           | 78            | _ | * | *   | 0   | - | - | 4     | 3      |

|               |                                                                                                                        | ER  | IM           | 79            |   |   |     |     |   |   | 4     | 3      |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |     | Vec-<br>tor  | F2            | _ | - | -   | -   | - | - | 2     | 6      |

| WDT           |                                                                                                                        |     |              | 5F            | - | - | _   | _   | _ | - | 1     | 2      |

| XOR dst, src  | $dst \gets dst \; XOR \; src$                                                                                          | r   | r            | B2            | _ | * | *   | 0   | - | - | 2     | 3      |

|               |                                                                                                                        | r   | lr           | B3            |   |   |     |     |   |   | 2     | 4      |

|               |                                                                                                                        | R   | R            | B4            |   |   |     |     |   |   | 3     | 3      |

|               |                                                                                                                        | R   | IR           | B5            |   |   |     |     |   |   | 3     | 4      |

|               |                                                                                                                        | R   | IM           | B6            |   |   |     |     |   |   | 3     | 3      |

|               |                                                                                                                        | IR  | IM           | B7            |   |   |     |     |   |   | 3     | 4      |

| XORX dst, src | $dst \gets dst \; XOR \; src$                                                                                          | ER  | ER           | B8            | - | * | *   | 0   | - | - | 4     | 3      |

|               |                                                                                                                        | ER  | IM           | B9            | _ |   |     |     |   |   | 4     | 3      |

### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F0830 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 115 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | 0       | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     |       |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 125     | mA    |       |

#### **Table 115. Absolute Maximum Ratings**

|                      |              |       |      | ADC | 5           |

|----------------------|--------------|-------|------|-----|-------------|

| Part Number          | Flash        | RAM   | NVDS |     | Description |

| Z8F1233QH020EG       | 12KB         | 256   | No   | 0   | QFN 20-pin  |

| Z8F1232SJ020EG       | 12KB         | 256   | No   | 8   | SOIC 28-pin |

| Z8F1232HJ020EG       | 12KB         | 256   | No   | 8   | SSOP 28-pin |

| Z8F1232PJ020EG       | 12KB         | 256   | No   | 8   | PDIP 28-pin |

| Z8F1232QJ020EG       | 12KB         | 256   | No   | 8   | QFN 28-pin  |

| Z8F1233SJ020EG       | 12KB         | 256   | No   | 0   | SOIC 28-pin |

| 28F1233HJ020EG       | 12KB         | 256   | No   | 0   | SSOP 28-pin |

| 8F1233PJ020EG        | 12KB         | 256   | No   | 0   | PDIP 28-pin |

| 8F1233QJ020EG        | 12KB         | 256   | No   | 0   | QFN 28-pin  |

| 8 Encore! F0830 witl | h 8KB Flash  | l     |      |     |             |

| Standard Temperatur  | e: 0°C to 70 | °C    |      |     |             |

| 28F0830SH020SG       | 8KB          | 256   | Yes  | 7   | SOIC 20-pin |

| 28F0830HH020SG       | 8KB          | 256   | Yes  | 7   | SSOP 20-pin |

| 8F0830PH020SG        | 8KB          | 256   | Yes  | 7   | PDIP 20-pin |

| 8F0830QH020SG        | 8KB          | 256   | Yes  | 7   | QFN 20-pin  |

| 8F0831SH020SG        | 8KB          | 256   | Yes  | 0   | SOIC 20-pin |

| 8F0831HH020SG        | 8KB          | 256   | Yes  | 0   | SSOP 20-pin |

| 8F0831PH020SG        | 8KB          | 256   | Yes  | 0   | PDIP 20-pin |

| 8F0831QH020SG        | 8KB          | 256   | Yes  | 0   | QFN 20-pin  |

| 8F0830SJ020SG        | 8KB          | 256   | Yes  | 8   | SOIC 28-pin |

| 8F0830HJ020SG        | 8KB          | 256   | Yes  | 8   | SSOP 28-pin |

| 8F0830PJ020SG        | 8KB          | 256   | Yes  | 8   | PDIP 28-pin |

| 8F0830QJ020SG        | 8KB          | 256   | Yes  | 8   | QFN 28-pin  |

| 8F0831SJ020SG        | 8KB          | 256   | Yes  | 0   | SOIC 28-pin |

| 8F0831HJ020SG        | 8KB          | 256   | Yes  | 0   | SSOP 28-pin |

| 8F0831PJ020SG        | 8KB          | 256   | Yes  | 0   | PDIP 28-pin |

| 8F0831QJ020SG        | 8KB          | 256   | Yes  | 0   | QFN 28-pin  |

| xtended Temperatur   | re: -40°C to | 105°C |      |     |             |

| 8F0830SH020EG        | 8KB          | 256   | Yes  | 7   | SOIC 20-pin |

| 8F0830HH020EG        | 8KB          | 256   | Yes  | 7   | SSOP 20-pin |

| 8F0830PH020EG        | 8KB          | 256   | Yes  | 7   | PDIP 20-pin |

| 8F0830QH020EG        | 8KB          | 256   | Yes  | 7   | QFN 20-pin  |

| 8F0831SH020EG        | 8KB          | 256   | Yes  | 0   | SOIC 20-pin |

|                      |              |       |      |     |             |

### Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

# Low Power Control

For more information about the Power Control Register, see the <u>Power Control Register</u> <u>Definitions</u> section on page 31.

### Hex Address: F80

| Bit     | 7        | 6   | 5   | 4   | 3        | 2        | 1    | 0        |

|---------|----------|-----|-----|-----|----------|----------|------|----------|

| Field   | Reserved |     |     | VBO | Reserved | Reserved | COMP | Reserved |

| RESET   | 1        | 0   | 0   | 0   | 1        | 0        | 0    | 0        |

| R/W     | R/W      | R/W | R/W | R/W | R/W      | R/W      | R/W  | R/W      |

| Address | F80H     |     |     |     |          |          |      |          |

#### Table 151. Power Control Register 0 (PWRCTL0)

### Hex Address: F81

This address range is reserved.

# **LED Controller**

For more information about the LED Drive registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

### Hex Address: F82

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | LEDEN[7:0] |     |     |     |     |     |     |     |  |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F82H       |     |     |     |     |     |     |     |  |

### Table 152. LED Drive Enable (LEDEN)

### Hex Addresses: F87–F8F

This address range is reserved.

# Comparator 0

For more information about the Comparator Register, see the <u>Comparator Control Register Definitions</u> section on page 107.

### Hex Address: F90

| Bit     | 7        | 6      | 5      | 4   | 3   | 2   | 1        | 0   |

|---------|----------|--------|--------|-----|-----|-----|----------|-----|

| Field   | Reserved | INNSEL | REFLVL |     |     |     | Reserved |     |

| RESET   | 0        | 0      | 0      | 1   | 0   | 1   | 0        | 0   |

| R/W     | R/W      | R/W    | R/W    | R/W | R/W | R/W | R/W      | R/W |

| Address | F90H     |        |        |     |     |     |          |     |

#### Table 156. Comparator Control Register (CMP0)

### Hex Addresses: F91–FBF

This address range is reserved.

# **Interrupt Controller**

For more information about the Interrupt Control registers, see the <u>Interrupt Control Reg-</u> <u>ister Definitions</u> section on page 57.

### Hex Address: FC0

| Bit     | 7        | 6   | 5   | 4        | 3        | 2        | 1        | 0    |

|---------|----------|-----|-----|----------|----------|----------|----------|------|

| Field   | Reserved | T1I | TOI | Reserved | Reserved | Reserved | Reserved | ADCI |

| RESET   | 0        | 0   | 0   | 0        | 0        | 0        | 0        | 0    |

| R/W     | R/W      | R/W | R/W | R/W      | R/W      | R/W      | R/W      | R/W  |

| Address | FC0H     |     |     |          |          |          |          |      |

### Table 157. Interrupt Request 0 Register (IRQ0)

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

load external data to/from data memory and autoincrement addresses 167 load external to/from data memory and auto-increment addresses 168 load instructions 168 load using extended addressing 168 logical AND 169 logical AND/extended addressing 169 logical exclusive OR 169 logical exclusive OR/extended addressing 169 logical instructions 169 logical OR 169 logical OR/extended addressing 169

### Μ

master interrupt enable 55 memory data 16 program 15 mode capture 89, 90 capture/compare 89 continuous 89 counter 89 gated 89 one-shot 89 PWM 89.90 modes 89 motor control measurements ADC Control register definitions 101 calibration and compensation 101 interrupts 101 overview 98 **MULT 167** multiply 167

## Ν

noise, electrical 98 NOP (no operation) 168 notation b 164

DA 164 ER 164 IM 164 IR 164 Ir 164 IRR 164 Irr 164 p 164 R 165 r 164 RA 165 RR 165 rr 165 vector 165 X 165 notational shorthand 164

cc 164

## 0

OCD architecture 139 auto-baud detector/generator 142 baud rate limits 142 block diagram 139 breakpoints 143 commands 144 control register 148 data format 142 DBG pin to RS-232 Interface 140 debug mode 141 debugger break 169 interface 140 serial errors 143 status register 150 timing 197 OCD commands execute instruction (12H) 148 read data memory (0DH) 147 read OCD control register (05H) 146 read OCD revision (00H) 145 read OCD status register (02H) 145 read program counter (07H) 146 read program memory (0BH) 147

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

read program memory CRC (0EH) 147 read register (09H) 146 read runtime counter (03H) 145 step instruction (10H) 148 stuff instruction (11H) 148 write data memory (0CH) 147 write OCD control register (04H) 145 write program counter (06H) 146 write program memory (0AH) 146 write register (08H) 146 on-chip debugger (OCD) 139 on-chip debugger signals 12 on-chip oscillator 157 one-shot mode 89 opcode map abbreviations 181 cell description 180 first 182 second after 1FH 183 operation 100 current measurement 99 voltage measurement timing diagram 100 Operational Description 21, 30, 33, 53, 68, 92, 98, 106, 108, 124, 134, 139, 151, 157, 161 OR 169 ordering information 200 ORX 169 oscillator signals 12

### Ρ

p 164

Packaging 199

part selection guide 2

PC 165

peripheral AC and DC electrical characteristics 190

pin characteristics 13

Pin Descriptions 7

polarity 164

POP 168

pop using extended addressing 168

POPX 168

port availability, device 33

port input timing (GPIO) 195

port output timing, GPIO 196 power supply signals 12 power-on reset (POR) 23 program control instructions 169 program memory 15 PUSH 168 push using extended addressing 168 PUSHX 168 PWM mode 89, 90 PxADDR register 40, 222, 223, 224, 225 PxCTL register 41, 222, 223, 224, 225

# R

R 165 r 164 RA register address 165 RCF 167, 168 register 165 flash control (FCTL) 119, 126, 127, 228 flash high and low byte (FFREQH and FRE-EQL) 123 flash page select (FPS) 121, 122 flash status (FSTAT) 120 GPIO port A-H address (PxADDR) 40, 222, 223, 224, 225 GPIO port A-H alternate function sub-registers 42 GPIO port A-H control address (PxCTL) 41, 222, 223, 224, 225 GPIO port A-H data direction sub-registers 41 OCD control 148 OCD status 150 watch-dog timer control (WDTCTL) 95, 107, 154, 217, 218, 226 watchdog timer control (WDTCTL) 29 watch-dog timer reload high byte (WDTH) 227 watchdog timer reload high byte (WDTH) 96 watch-dog timer reload low byte (WDTL) 227 watchdog timer reload low byte (WDTL) 97 watch-dog timer reload upper byte (WDTU) 227

236