Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | -                                                         |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 17                                                        |  |

| Program Memory Size        | 12KB (12K x 8)                                            |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | A/D 7x10b                                                 |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1232sh020eg |  |

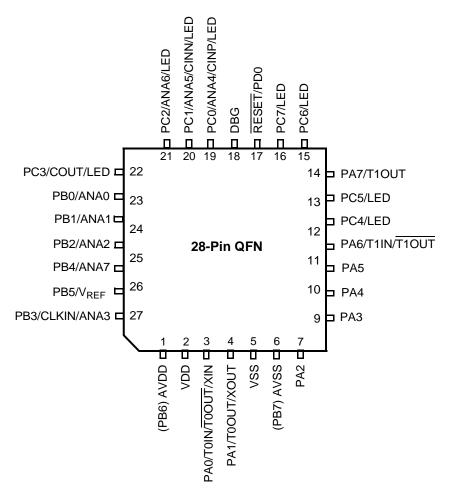

Figure 5. Z8F0830 Series in 28-Pin QFN Package

PS025113-1212 Pin Configurations

## **Pin Characteristics**

Table 5 provides detailed characteristics of each pin available on the Z8 Encore! F0830 Series 20- and 28-pin devices. Data in Table 5 are sorted alphabetically by the pin symbol mnemonic.

Table 5. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction               | Active<br>Low or<br>Active<br>High | Tristate<br>Output   | Internal<br>Pull-Up or<br>Pull-Down                  | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance |

|--------------------|-----------|----------------------------------|------------------------------------|----------------------|------------------------------------------------------|------------------------------|------------------------------------------------------|-----------------|

| $AV_{DD}$          | N/A       | N/A                              | N/A                                | N/A                  | N/A                                                  | N/A                          | N/A                                                  | N/A             |

| AV <sub>SS</sub>   | N/A       | N/A                              | N/A                                | N/A                  | N/A                                                  | N/A                          | N/A                                                  | NA              |

| DBG                | I/O       | I                                | N/A                                | Yes                  | No                                                   | Yes                          | Yes                                                  | Yes             |

| PA[7:0]            | I/O       | I                                | N/A                                | Yes                  | Programma-<br>ble pull-up                            | Yes                          | Yes,<br>Programma-<br>ble                            | PA[7:2]<br>only |

| PB[7:0]            | I/O       | I                                | N/A                                | Yes                  | Programma-<br>ble pull-up                            | Yes                          | Yes,<br>Programma-<br>ble                            | PB[7:6]<br>only |

| PC[7:0]            | I/O       | I                                | N/A                                | Yes                  | Programma-<br>ble pull-up                            | Yes                          | Yes,<br>Programma-<br>ble                            | PC[7:3]<br>only |

| RESET/PD0          | I/O       | I/O<br>(defaults<br>to<br>RESET) | Low (in<br>RESET<br>mode)          | Yes<br>(PD0<br>only) | Programma-<br>ble for PD0;<br>always on<br>for RESET | Yes                          | Programma-<br>ble for PD0;<br>always on<br>for RESET | Yes             |

| $V_{DD}$           | N/A       | N/A                              | N/A                                | N/A                  |                                                      |                              | N/A                                                  | N/A             |

| V <sub>SS</sub>    | N/A       | N/A                              | N/A                                | N/A                  |                                                      |                              | N/A                                                  | N/A             |

Note: PB6 and PB7 are available only in devices without an ADC function.

PS025113-1212 Pin Characteristics

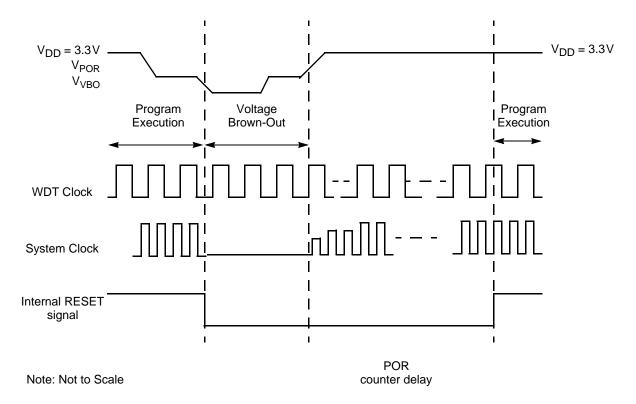

The Voltage Brown-Out circuit can be either enabled or disabled during STOP Mode. Operations during STOP Mode is set by the VBO\_AO Flash option bit. See the <u>Flash Option Bits</u> chapter on page 124 for information about configuring VBO\_AO.

Figure 7. Voltage Brown-Out Reset Operation

# **Watchdog Timer Reset**

If the device is operating in NORMAL or STOP Mode, the Watchdog Timer can initiate a system reset at time-out if the WDT\_RES Flash option bit is programmed to 1; this state is the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt – not a system reset – at time-out. The WDT status bit in the Reset Status (RSTSTAT) Register is set to 1 to signify that the reset was initiated by the Watchdog Timer.

# **External Reset Input**

The RESET pin has a Schmitt-triggered input and an internal pull-up resistor. After the  $\overline{RESET}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the system reset sequence. Because of the possible asynchronicity of the system

PS025113-1212 Reset Sources

## **Architecture**

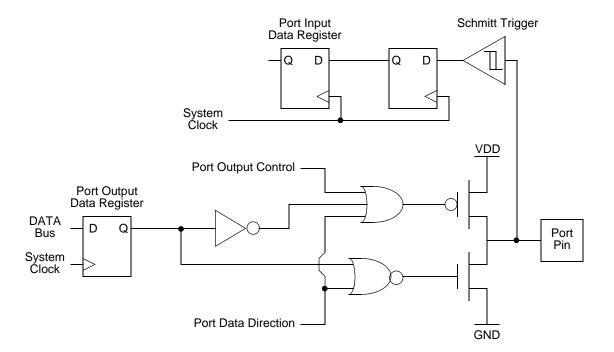

Figure 8 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

Figure 8. GPIO Port Pin Block Diagram

## **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general purpose input/output and access to onchip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function subregisters configure these pins for either GPIO or Alternate function operation. When a pin is configured for Alternate function, control of the port pin direction (input/output) is passed from the Port A–D data direction registers to the Alternate function assigned to this pin. Table 16 on page 36 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, pins PA0 and PA1 functions as input and output for the crystal oscillator.

PS025113-1212 Architecture

**Table 16. Port Alternate Function Mapping (Continued)**

| Port                | Pin | Mnemonic         | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------|--------------------------------|-----------------------------------------|

| Port B <sup>2</sup> | PB0 | Reserved         |                                | AFS1[0]: 0                              |

|                     |     | ANA0             | ADC analog input               | AFS1[0]: 1                              |

|                     | PB1 | Reserved         |                                | AFS1[1]: 0                              |

|                     |     | ANA1             | ADC analog input               | AFS1[1]: 1                              |

|                     | PB2 | Reserved         |                                | AFS1[2]: 0                              |

|                     |     | ANA2             | ADC analog input               | AFS1[2]: 1                              |

|                     | PB3 | CLKIN            | External input clock           | AFS1[3]: 0                              |

|                     |     | ANA3             | ADC analog input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved         |                                | AFS1[4]: 0                              |

|                     |     | ANA7             | ADC analog input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved         |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> | ADC reference voltage          | AFS1[5]: 1                              |

|                     | PB6 | Reserved         |                                | AFS1[6]: 0                              |

|                     |     | Reserved         |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved         |                                | AFS1[7]: 0                              |

|                     |     | Reserved         |                                | AFS1[7]: 1                              |

#### Notes:

- 1. Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate functions (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate functions (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate functions (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and P

- 2. Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <a href="Port A-D Alternate Function Subregisters">Port A-D Alternate Function Subregisters</a> section on page 42) must also be enabled.

- 3. Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <a href="Port A-D Alternate Function Subregisters">Port A-D Alternate Function Subregisters</a> section on page 42) must also be enabled.

## Port A–D Address Registers

The Port A–D Address registers select the GPIO port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO port controls; see Tables 18 and 19.

Table 18. Port A–D GPIO Address Registers (PxADDR)

| Bit     | 7   | 7 6 5 4 3 2 1 0         |  |  |  |  |  |  |  |  |  |

|---------|-----|-------------------------|--|--|--|--|--|--|--|--|--|

| Field   |     | PADDR[7:0]              |  |  |  |  |  |  |  |  |  |

| RESET   |     | 00H                     |  |  |  |  |  |  |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W |  |  |  |  |  |  |  |  |  |

| Address |     | FD0H, FD4H, FD8H, FDCH  |  |  |  |  |  |  |  |  |  |

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The port address selects one of the subregisters accessible through the Port Control Register. |

**Table 19. Port Control Subregister Access**

| PADDR[7:0] | Port Control Subregister accessible using the Port A–D Control registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental port reconfiguration. |

| 01H        | Data Direction                                                                 |

| 02H        | Alternate Function                                                             |

| 03H        | Output Control (open-drain)                                                    |

| 04H        | High Drive Enable                                                              |

| 05H        | Stop Mode Recovery Source Enable                                               |

| 06H        | Pull-Up Enable                                                                 |

| 07H        | Alternate Function Set 1                                                       |

| 08H        | Alternate Function Set 2                                                       |

| 09H–FFH    | No function                                                                    |

#### Bit Description (Continued)

#### [6] PWM DUAL OUTPUT Mode

# TPOL (cont'd)

- 0 = Timer output is forced Low (0) and timer output complement is forced High (1), when the timer is disabled. When enabled and the PWM count matches, the timer output is forced High (1) and forced Low (0) when enabled and reloaded. When enabled and the PWM count matches, the timer output complement is forced Low (0) and forced High (1) when enabled and reloaded.

- 1 = Timer output is forced High (1) and timer output complement is forced Low (0) when the timer is disabled. When enabled and the PWM count matches, the timer output is forced Low (0) and forced High (1) when enabled and reloaded. When enabled and the PWM count matches, the timer output complement is forced High (1) and forced Low (0) when enabled and reloaded. The PWMD field in the TxCTL0 register determines an optional added delay on the assertion (Low to High) transition of both timer output and timer output complement for deadband generation.

#### **CAPTURE RESTART Mode**

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.

**Caution:** When the timer output alternate function TxOUT on a GPIO port pin is enabled, TxOUT will change to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Additionally, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit when the timer is enabled and running does not immediately change the polarity TxOUT.

#### [5:3] **Prescale Value**

#### **PRES**

The timer input clock is divided by 2<sup>PRES</sup>, where PRES can be set from 0 to 7. The prescaler is reset each time the timer is disabled. This reset ensures proper clock division each time the timer is restarted.

- 000 = Divide by 1.

- 001 = Divide by 2.

- 010 = Divide by 4.

- 011 = Divide by 8.

- 100 = Divide by 16.

- 101 = Divide by 32.

- 110 = Divide by 64.

- 111 = Divide by 128.

## Watchdog Timer Refresh

Upon first enable, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the Reload operation.

When the Z8 Encore! F0830 Series devices are operating in DEBUG Mode (using the On-Chip Debugger), the Watchdog Timer must be continuously refreshed to prevent any WDT time-outs.

## **Watchdog Timer Time-Out Response**

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash option bit determines the time-out response of the Watchdog Timer. See *the* Flash Option Bits chapter on page 124 for information about programming the WDT\_RES Flash option bit.

## **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the Interrupt Controller and sets the WDT status bit in the Reset Status Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter resets to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter will not automatically return to its reload value.

The Reset Status Register (see <u>Table 12</u> on page 29) must be read before clearing the WDT interrupt. This read clears the WDT time-out flag and prevents further WDT interrupts occurring immediately.

## WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! F0830 Series devices are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. See *the* Reset and Stop Mode Recovery *chapter on page 21* for more information about Stop Mode Recovery operations.

If interrupts are enabled, following completion of the Stop Mode Recovery, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executes the code from the vector address.

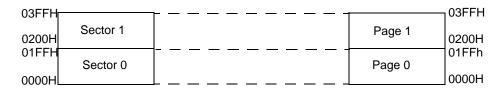

# Flash Memory

The products in the Z8 Encore! F0830 Series features either 1KB (1024 bytes with NVDS), 2KB (2048 bytes with NVDS), 4KB (4096 bytes with NVDS), 8KB (8192 bytes with NVDS) or 12KB (12288 bytes with no NVDS) of nonvolatile Flash memory with read/write/erase capability. Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F0830 Series, each sector maps to one page (for 1 KB, 2 KB and 4 KB devices), two pages (8 KB device) or three pages (12 KB device).

The first two bytes of Flash program memory is used as Flash option bits. For more information, see *the* Flash Option Bits chapter on page 124.

Table 69 lists the Flash memory configuration for each device in the Z8 Encore! F0830 Series. Figures 14 through 18 display the memory arrangements for each Flash memory size.

| Table 69. Z8 Encore! F0830 | Series Flash Memory | Configuration |

|----------------------------|---------------------|---------------|

|----------------------------|---------------------|---------------|

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F123x     | 12 (12,288)              | 24          | 0000H-2FFFH                    | 1536                         |

| Z8F083x     | 8 (8196)                 | 16          | 0000H-1FFFH                    | 1024                         |

| Z8F043x     | 4 (4096)                 | 8           | 0000H-0FFFH                    | 512                          |

| Z8F023x     | 2 (2048)                 | 4           | 0000H-07FFH                    | 512                          |

| Z8F013x     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

Figure 14. 1K Flash with NVDS

PS025113-1212 Flash Memory

- The Flash Sector Protect Register is ignored for programming and Erase operations.

- Programming operations are not limited to the page selected in the page select register.

- Bits in the Flash Sector Protect Register can be written to one or zero.

- The second write of the page select register to unlock the Flash Controller is not necessary.

- The page select register can be written when the Flash Controller is unlocked.

- The mass erase command is enabled through the Flash Control Register

**Caution:** For security reasons, Flash Controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the Flash Controller must go through the unlock sequence again to select another page.

# **NVDS Operational Requirements**

The device uses a 12 KB Flash memory space, despite the maximum specified Flash size of 8 KB (with the exception of 12 KB mode with non-NVDS). User code accesses the lower 8 KB of Flash, leaving the upper 4 KB for proprietary (for Zilog-only) memory. The NVDS is implemented by using this proprietary memory space for special-purpose routines and for the data required by these routines, which are factory-programmed and cannot be altered by the user. The NVDS operation is described in detail in *the* Nonvolatile Data Storage *chapter on page 134*.

The NVDS routines are triggered by a user code: CALL into proprietary memory. Code executing from this proprietary memory must be able to read and write other locations within proprietary memory. User code must not be able to read or write proprietary memory.

# Flash Control Register Definitions

This section defines the features of the following Flash Control registers.

<u>Flash Control Register</u>: see page 119 <u>Flash Status Register</u>: see page 120

<u>Flash Page Select Register</u>: see page 121 <u>Flash Sector Protect Register</u>: see page 122

Flash Frequency High and Low Byte Registers: see page 123

## **Option Bit Types**

This section describes the two types of Flash option bits offered in the F0830 Series.

## **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits is provided because these locations contain application specific device configurations. The information contained here is lost when page 0 of program memory is erased.

## **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered by the user. Program memory can be erased without endangering these values. It is possible to alter working values of these bits by accessing the trim bit address and data registers, but these working values are lost after a power loss.

There are 32 bytes of trim data. To modify one of these values, the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

Note:

The trim address range is from information address 20-3F only. The remaining information page is not accessible via the Trim Bit Address and Data registers.

During reset, the first 43 system clock cycles perform 43 Flash accesses. The six bits of the counter provide the lower six bits of the Flash memory address. All other address bits are set to 0. The option bit registers use the 6-bit address from the counter as an address and latch the data from the Flash on the positive edge of the IPO clock, allowing for a maximum of 344-bits (43 bytes) of option information to be read from Flash.

Because option information is stored in both the first two bytes of program memory and in the information area of Flash memory, the data must be placed in specific locations to be read correctly. In this case, the first two bytes at addresses 0 and 1 in program memory are read out and the remainder of the bytes are read out of the Flash information area.

| Bit         | Description (Continued)                              |

|-------------|------------------------------------------------------|

| [1:0]       | Filter Select                                        |

| FilterSely  | 2-bit selection for the clock filter mode.           |

|             | 00 = No filter.                                      |

|             | 01 = Filter low level noise on high level signal.    |

|             | 10 = Filter high level noise on low level signal.    |

|             | 11 = Filter both.                                    |

| Notes: x ir | ndicates bit values 3–1; v indicates bit values 1–0. |

**Note:** The bit values used in Table 89 are set at factory and no calibration is required.

Table 90. ClkFlt Delay Control Definition

| DlyCtl3, DlyCtl2,<br>DlyCtl1 | Low Noise Pulse<br>on High Signal (ns) | High Noise Pulse<br>on Low Signal (ns) |

|------------------------------|----------------------------------------|----------------------------------------|

| 000                          | 5                                      | 5                                      |

| 001                          | 7                                      | 7                                      |

| 010                          | 9                                      | 9                                      |

| 011                          | 11                                     | 11                                     |

| 100                          | 13                                     | 13                                     |

| 101                          | 17                                     | 17                                     |

| 110                          | 20                                     | 20                                     |

| 111                          | 25                                     | 25                                     |

| Note: The variation is       | about 30%.                             |                                        |

138

Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

2. Use as few unique addresses as possible to optimize the impact of refreshing.

PS025113-1212 NVDS Code Interface

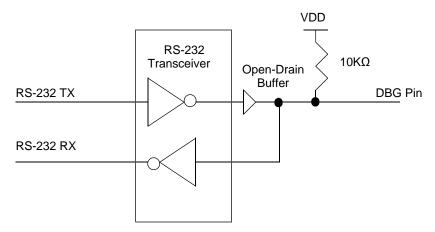

Figure 22. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

### **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates, unless the device is in STOP Mode

- All enabled on-chip peripherals operate, unless the device is in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

## **Entering DEBUG Mode**

- The device enters DEBUG Mode after the eZ8 CPU executes a Breakpoint (BRK) instruction

- If the DBG pin is held low during the most recent clock cycle of system reset, the device enters DEBUG Mode on exiting system reset

#### **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

**Read OCD Control Register (05H).** The read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

Write Program Counter (06H). The write program counter command, writes the data that follows to the eZ8 CPU's program counter (PC). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, the program counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

**Read Program Counter (07H).** The read program counter command, reads the value in the eZ8 CPUs program counter (PC). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFFFH.

```

DBG ← 07H

DBG → ProgramCounter[15:8]

DBG → ProgramCounter[7:0]

```

**Write Register (08H).** The write register command, writes data to the register file. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash read protect option bit is enabled, only writes to the Flash control registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**Read Register (09H).** The read register command, reads data from the register file. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFH for all of the data values.

```

DBG ← 09H

DBG ← {4'h0,Register Address[11:8]

DBG ← Register Address[7:0]

DBG ← Size[7:0]

DBG → 1-256 data bytes

```

Write Program Memory (0AH). The write program memory command, writes data to program memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, the data is discarded.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer Oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The Internal Precision Oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## **Clock Failure Detection and Recovery**

### **Primary Oscillator Failure**

The Z8F04xA family devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer Oscillator to drive the system clock. The Watchdog Timer Oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer Oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the Watchdog Timer chapter of this document.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 KHz  $\pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

#### **Watchdog Timer Failure**

In the event of failure of a Watchdog Timer Oscillator, a similar nonmaskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer Oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer Oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure is detected. A very slow system clock results in very slow detection times.

Figures 29 and 30 provide information about each of the eZ8 CPU instructions.

| Rt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                    |                    |                    |                    |                   |                   | Lo                | ower Nil          | oble (He           | x)                 |          |    |    |    |     |                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|----------|----|----|----|-----|---------------------------|

| BRK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 0                  | 1                  | 2                  | 3                  | 4                 | 5                 | 6                 | 7                 | 8                  | 9                  | Α        | В  | С  | D  | Е   | F                         |

| Table   Tabl   | 0 |                    | SRP                | ADD                | ADD                | ADD               | ADD               | ADD               | ADD               | ADDX               | ADDX               | DJNZ     | JR | LD | JP | INC | 1.2<br><b>NOP</b>         |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | RLC                | RLC                | ADC                | ADC                | ADC               | ADC               | ADC               | ADC               | ADCX               | ADCX               |          |    |    |    |     | See 2nd<br>Op Code<br>Map |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 | INC                | INC                | 2.3<br><b>SUB</b>  | 2.4<br><b>SUB</b>  | 3.3<br><b>SUB</b> | 3.4<br><b>SUB</b> | 3.3<br><b>SUB</b> | 3.4<br><b>SUB</b> | 4.3<br>SUBX        | 4.3<br>SUBX        |          |    |    |    |     | ·                         |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3 | 2.2<br><b>DEC</b>  | 2.3<br><b>DEC</b>  | 2.3<br><b>SBC</b>  | 2.4<br><b>SBC</b>  | 3.3<br><b>SBC</b> | 3.4<br><b>SBC</b> | 3.3<br><b>SBC</b> | 3.4<br><b>SBC</b> | SBCX               | SBCX               |          |    |    |    |     |                           |

| The image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4 | 2.2<br><b>DA</b>   | 2.3<br><b>DA</b>   | 2.3<br><b>OR</b>   | 2.4<br><b>OR</b>   | 3.3<br><b>OR</b>  | 3.4<br><b>OR</b>  | 3.3<br><b>OR</b>  | 3.4<br><b>OR</b>  | 4.3<br><b>ORX</b>  | 4.3<br><b>ORX</b>  |          |    |    |    |     |                           |

| COM   COM   TCM    | 5 | 2.2<br><b>POP</b>  | 2.3<br><b>POP</b>  | 2.3<br><b>AND</b>  | 2.4<br><b>AND</b>  | 3.3<br><b>AND</b> | 3.4<br><b>AND</b> | 3.3<br><b>AND</b> | 3.4<br><b>AND</b> | 4.3<br><b>ANDX</b> | 4.3<br><b>ANDX</b> |          |    |    |    |     | 1.2<br><b>WDT</b>         |

| PUSH PUSH TM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _ | 2.2<br><b>COM</b>  | 2.3<br><b>COM</b>  | 2.3<br><b>TCM</b>  | 2.4<br><b>TCM</b>  | 3.3<br><b>TCM</b> | 3.4<br><b>TCM</b> | 3.3<br><b>TCM</b> | 3.4<br><b>TCM</b> | 4.3<br><b>TCMX</b> | 4.3<br>TCMX        |          |    |    |    |     | stop                      |

| 9 RL RL LDE LDEI LDX LDX LDX LDX LEA LEA R1 IR1 r2,Irr1 Ir2,Irr1 r2,ER1 Ir2,ER1 R2,IRR1 IR2,IRR1 r1,r2,X r1,rr2,X r1,rr2,X r2,5 2.6 2.3 2.4 3.3 3.4 4.3 4.3 4.3 4.3 4.3 4.3 4.3 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7 | 2.2<br><b>PUSH</b> | 2.3<br><b>PUSH</b> | 2.3<br><b>TM</b>   | 2.4<br><b>TM</b>   | 3.3<br><b>TM</b>  | 3.4<br><b>TM</b>  | 3.3<br><b>TM</b>  | 3.4<br><b>TM</b>  | 4.3<br><b>TMX</b>  | 4.3<br><b>TMX</b>  |          |    |    |    |     | 1.2<br>HALT               |

| 9 RL RL LDE LDEI LDX LDX LDX LDX LEA LEA R1 IR1 r2,Irr1   r2,ER1   r2,ER1   r2,ER1   r2,ER1   r1,r2,X   r1,r2,X   r1,r2,X   r1,r2,X   r1,r2,X   r2,5   2.6   2.3   2.4   3.3   3.4   3.3   3.4   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   | 8 | 2.5<br><b>DECW</b> | 2.6<br><b>DECW</b> | 2.5<br><b>LDE</b>  | 2.9<br><b>LDEI</b> | 3.2<br><b>LDX</b> | 3.3<br><b>LDX</b> | 3.4<br><b>LDX</b> | 3.5<br><b>LDX</b> | 3.4<br><b>LDX</b>  | 3.4<br><b>LDX</b>  |          |    |    |    |     | 1.2<br><b>DI</b>          |

| A   2.5   2.6   2.3   2.4   3.3   3.4   3.3   3.4   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4. |   | 2.2<br><b>RL</b>   | 2.3<br><b>RL</b>   | 2.5<br><b>LDE</b>  | 2.9<br><b>LDEI</b> | 3.2<br><b>LDX</b> | 3.3<br><b>LDX</b> | 3.4<br><b>LDX</b> | 3.5<br><b>LDX</b> | 3.3<br><b>LEA</b>  | 3.5<br><b>LEA</b>  |          |    |    |    |     | 1.2<br><b>El</b>          |

| B CLR CLR XOR XOR XOR XOR XOR XOR XOR XOR XOR XO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Α | 2.5<br>INCW        | 2.6<br>INCW        | 2.3<br><b>CP</b>   | 2.4<br><b>CP</b>   | 3.3<br><b>CP</b>  | 3.4<br><b>CP</b>  | 3.3<br><b>CP</b>  | 3.4<br><b>CP</b>  | 4.3<br><b>CPX</b>  | 4.3<br><b>CPX</b>  |          |    |    |    |     | 1.4<br>RET                |

| C RC RC LDC LDCI JP LDC LDC LDCI R1 IR1 IR1 IR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR1 IR1 IR1 IR1 IR1 IR1 IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | В | 2.2<br><b>CLR</b>  | 2.3<br><b>CLR</b>  | 2.3<br><b>XOR</b>  | 2.4<br><b>XOR</b>  | 3.3<br><b>XOR</b> | 3.4<br><b>XOR</b> | 3.3<br><b>XOR</b> | 3.4<br><b>XOR</b> | XORX               | XORX               |          |    |    |    |     | 1.5<br>IRET               |

| D   2.2   2.3   2.5   2.9   2.6   2.2   3.3   3.4   3.2   3.2   3.3   3.4   3.2   3.2   3.3   3.4   3.2   3.3   3.4   3.2   3.3   3.4   3.2   3.3   3.4   3.2   3.3   3.4   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3.3   3.2   3. | С | 2.2<br><b>RRC</b>  | 2.3<br><b>RRC</b>  | 2.5<br><b>LDC</b>  | 2.9<br><b>LDCI</b> | 2.3<br><b>JP</b>  | 2.9<br><b>LDC</b> | K1,IIVI           | 3.4<br><b>LD</b>  | 3.2<br>PUSHX       | IIVI,EK I          |          |    |    |    |     | 1.2<br><b>RCF</b>         |

| E RR RR BIT LD LD LD LD LD LD LDX LDX R1 IR1 p,b,r1 r1,lr2 R2,R1 IR2,R1 R1,IM IR1,IM ER2,ER1 IM,ER1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D | 2.2<br><b>SRA</b>  | 2.3<br><b>SRA</b>  | 2.5<br><b>LDC</b>  | 2.9<br><b>LDCI</b> | 2.6<br>CALL       | 2.2<br>BSWAP      | CALL              | 3.4<br><b>LD</b>  | 3.2<br><b>POPX</b> |                    |          |    |    |    |     | 1.2<br><b>SCF</b>         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E | 2.2<br><b>RR</b>   | 2.3<br><b>RR</b>   | 2.2<br><b>BIT</b>  | 2.3<br><b>LD</b>   | 3.2<br><b>LD</b>  | 3.3<br><b>LD</b>  | 3.2<br><b>LD</b>  | 3.3<br><b>LD</b>  | 4.2<br><b>LDX</b>  | LDX                |          |    |    |    |     | 1.2<br><b>CCF</b>         |

| F   2.2   2.3   2.6   2.3   2.8   3.3   3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | F | SWAP               | SWAP               | 2.6<br><b>TRAP</b> | 2.3<br><b>LD</b>   | 2.8<br>MULT       | 3.3<br><b>LD</b>  | 3.3<br><b>BTJ</b> | 3.4<br><b>BTJ</b> | EKZ,EK1            | ıM,EK1             | <b>V</b> |    |    |    |     |                           |

Figure 29. First Op Code Map

PS025113-1212 Op Code Maps

**Table 127. Power Consumption Reference Table**

|                         | Power Consumption                                                                                             |                                                                                                                                                    |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Block                   | Typical                                                                                                       | Maximum                                                                                                                                            |  |  |  |

| CPU/Peripherals @ 20MHz | 5mA                                                                                                           |                                                                                                                                                    |  |  |  |

| Flash @20MHz            |                                                                                                               | 12mA                                                                                                                                               |  |  |  |

| ADC @20MHz              | 4mA                                                                                                           | 4.5 mA                                                                                                                                             |  |  |  |

| IPO                     | 350µA                                                                                                         | 400µA                                                                                                                                              |  |  |  |