Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 12KB (12K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1233hj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Program Memory**

The eZ8 CPU supports 64KB of program memory address space. The Z8 Encore! F0830 Series devices contain 1KB to 12KB of on-chip Flash memory in the program memory address space, depending on the device. Reading from program memory addresses outside the available Flash memory address range returns FFH. Writing to these unimplemented program memory addresses produces no effect. Table 6 shows a program memory map for the Z8 Encore! F0830 Series products.

|                                             | 0 , 1                      |

|---------------------------------------------|----------------------------|

| Program Memory Address (Hex)                | Function                   |

| Z8F0830 and Z8F0831 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-1FFF                                   | Program Memory             |

| Z8F0430 and Z8F0431 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-0FFF                                   | Program Memory             |

| Z8F0130 and Z8F0131 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-03FF                                   | Program Memory             |

| Z8F0230 and Z8F0231 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-07FF                                   | Program Memory             |

| Note: *See <u>Table 34</u> on page 54 for a | list of interrupt vectors. |

| Table 6 | . Z8 | Encore! | F0830 | Series | Program | Memory Ma | ips |

|---------|------|---------|-------|--------|---------|-----------|-----|

|---------|------|---------|-------|--------|---------|-----------|-----|

### 17

# **Register Map**

Table 8 provides an address map of the Z8 Encore! F0830 Series register file. Not all devices and package styles in the Z8 Encore! F0830 Series support the ADC or all of the GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)    | Register Description              | Mnemonic      | Reset (Hex) | Page No. |

|------------------|-----------------------------------|---------------|-------------|----------|

| General Purpos   | e RAM                             |               |             |          |

| 000–0FF          | General purpose register file RAM |               | XX          |          |

| 100–EFF          | Reserved                          | _             | XX          |          |

| Timer 0          |                                   |               |             |          |

| F00              | Timer 0 high byte                 | T0H           | 00          | 83       |

| F01              | Timer 0 low byte                  | TOL           | 01          | 83       |

| F02              | Timer 0 reload high byte          | TORH          | FF          | 85       |

| F03              | Timer 0 reload low byte           | TORL          | FF          | 85       |

| F04              | Timer 0 PWM high byte             | <b>T0PWMH</b> | 00          | 86       |

| F05              | Timer 0 PWM low byte              | TOPWML        | 00          | 86       |

| F06              | Timer 0 control 0                 | T0CTL0        | 00          | 87       |

| F07              | Timer 0 control 1                 | T0CTL1        | 00          | 88       |

| Timer 1          |                                   |               |             |          |

| F08              | Timer 1 high byte                 | T1H           | 00          | 83       |

| F09              | Timer 1 low byte                  | T1L           | 01          | 83       |

| F0A              | Timer 1 reload high byte          | T1RH          | FF          | 85       |

| F0B              | Timer 1 reload low byte           | T1RL          | FF          | 85       |

| F0C              | Timer 1 PWM high byte             | T1PWMH        | 00          | 86       |

| F0D              | Timer 1 PWM low byte              | T1PWML        | 00          | 86       |

| F0E              | Timer 1 control 0                 | T1CTL0        | 00          | 87       |

| F0F              | Timer 1 control 1                 | T1CTL1        | 00          | 83       |

| F10–F6F          | Reserved                          | _             | XX          |          |

| Analog-to-Digita | al Converter (ADC)                |               |             |          |

| F70              | ADC control 0                     | ADCCTL0       | 00          | 102      |

| F71              | Reserved                          |               | XX          |          |

| F72              | ADC data high byte                | ADCD_H        | XX          | 103      |

#### Table 8. Register File Address Map

Note: XX = Undefined.

|                  | _                          |          | -           |          |

|------------------|----------------------------|----------|-------------|----------|

| Address (Hex)    | Register Description       | Mnemonic | Reset (Hex) | Page No. |

| Analog-to-Digita | al Converter (ADC, cont'd) |          |             |          |

| F73              | ADC data low bits          | ADCD_L   | XX          | 103      |

| F74              | ADC sample settling time   | ADCSST   | 0F          | 104      |

| F75              | ADC sample time            | ADCST    | 3F          | 105      |

| F76              | Reserved                   | —        | XX          |          |

| F77–F7F          | Reserved                   | —        | XX          |          |

| Low Power Con    | trol                       |          |             |          |

| F80              | Power control 0            | PWRCTL0  | 88          | 32       |

| F81 Reserved     |                            | _        | XX          |          |

| LED Controller   |                            |          |             |          |

| F82              | LED drive enable           | LEDEN    | 00          | 51       |

| F83              | LED drive level high       | LEDLVLH  | 00          | 51       |

| F84              | LED drive level low        | LEDLVLL  | 00          | 52       |

| F85              | Reserved                   | _        | XX          |          |

| Oscillator Contr | ol                         |          |             |          |

| F86              | Oscillator control         | OSCCTL   | A0          | 154      |

| F87–F8F          | Reserved                   | —        | XX          |          |

| Comparator 0     |                            |          |             |          |

| F90              | Comparator 0 control       | CMP0     | 14          | 107      |

| F91–FBF          | Reserved                   | _        | XX          |          |

| Interrupt Contro | bller                      |          |             |          |

| FC0              | Interrupt request 0        | IRQ0     | 00          | 58       |

| FC1              | IRQ0 enable high bit       | IRQ0ENH  | 00          | 61       |

| FC2              | IRQ0 enable low Bit        | IRQ0ENL  | 00          | 61       |

| FC3              | Interrupt request 1        | IRQ1     | 00          | 59       |

| FC4              | IRQ1 enable high bit       | IRQ1ENH  | 00          | 62       |

| FC5              | IRQ1 enable low bit        | IRQ1ENL  | 00          | 63       |

| FC6              | Interrupt request 2        | IRQ2     | 00          | 60       |

| FC7              | IRQ2 enable high bit       | IRQ2ENH  | 00          | 64       |

| FC8              | IRQ2 enable low bit        | IRQ2ENL  | 00          | 64       |

| FC9–FCC          | Reserved                   | —        | XX          |          |

| FCD              | Interrupt edge select      | IRQES    | 00          | 66       |

## Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

| Address (Hex)    | Register Description                  | Mnemonic | Reset (Hex) | Page No.                          |

|------------------|---------------------------------------|----------|-------------|-----------------------------------|

| Trim Bit Control |                                       |          |             |                                   |

| FF6              | Trim bit address                      | TRMADR   | 00          | 126                               |

| FF7              | Trim data                             | TRMDR    | XX          | 127                               |

| Flash Memory C   | Controller                            |          |             |                                   |

| FF8              | Flash control                         | FCTL     | 00          | 119                               |

| FF8              | Flash status                          | FSTAT    | 00          | 120                               |

| FF9              | Flash page select                     | FPS      | 00          | 121                               |

|                  | Flash sector protect                  | FPROT    | 00          | 122                               |

| FFA              | Flash programming frequency high byte | FFREQH   | 00          | 123                               |

| FFB              | Flash programming frequency low byte  | FFREQL   | 00          | 123                               |

| eZ8 CPU          |                                       |          |             |                                   |

| FFC              | Flags                                 | —        | XX          | Refer to the                      |

| FFD              | Register pointer                      | RP       | XX          | <u>eZ8 CPU</u>                    |

| FFE              | Stack pointer high byte               | SPH      | XX          | <u>Core User</u><br><u>Manual</u> |

| FFF              | Stack pointer low byte                | SPL      | XX          | <u>(UM0128)</u>                   |

| Note: XX = Undef | ined.                                 |          |             |                                   |

#### Table 8. Register File Address Map (Continued)

#### 31

# HALT Mode

Executing the eZ8 CPU HALT instruction places the device into HALT Mode. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any one of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as digital inputs must be driven to  $V_{DD}$  when pull-up register bit is enabled or to one of power rail ( $V_{DD}$  or GND) when pull-up register bit is disabled.

# **Peripheral Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! F0830 Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

#### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

PA0 and PA6 contain two different Timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the TIMER mode. For more details, see the <u>Timers</u> chapter on page 68.

## **Direct LED Drive**

The Port C pins provide a sinked current output, capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels, 3mA, 7mA, 13mA and 20mA. This mode is enabled through the LED Control registers.

For proper function, the LED anode must be connected to  $V_{\rm DD}$  and the cathode to the GPIO pin.

Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See the <u>Electrical Characteristics</u> chapter on page 184 for the maximum total current for the applicable package.

## Shared Reset Pin

On the 20- and 28-pin devices, the Port D0 pin shares function with a bidirectional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bidirectional input/output open-drain reset with an internal pull-up until the user software reconfigures it as a GPIO PD0. When in GPIO mode, the Port D0 pin functions as output only, and must be configured as an output. PD0 supports the high drive feature, but not the stop-mode recovery feature.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, the pins PA0 and PA1 are connected to the crystal. When the crystal oscillator is enabled, the GPIO settings are overridden and PA0 and PA1 are disabled. See the <u>Oscillator Control Register Definitions</u> section on page 154.

# **5V Tolerance**

In the 20- and 28-pin versions of this device, any pin, which shares functionality with an ADC, crystal or comparator port is not 5V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5V-tolerant and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled, but with excess power consumption on pull-up resistor.

• Writing 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (disable interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the Interrupt Controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction Trap

- Primary oscillator fail trap

- Watchdog Oscillator fail trap

## **Interrupt Vectors and Priority**

The Interrupt Controller supports three levels of interrupt priority. Level 3 is the highest priority, level 2 is the second highest priority and level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 54. Level 3 interrupts are always assigned higher priority than level 2 interrupts and level 2 interrupts are assigned higher priority than level 1 interrupts. Within each interrupt priority level (level 1, level 2 or level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), primary oscillator fail trap, Watchdog Oscillator fail trap and illegal instruction trap always have highest (level 3) priority.

## **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the interrupt request register is cleared. Writing 0 to the corresponding bit in the interrupt request register clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

## Table 45. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|-----|------|-------|-----|-------|-------|-------|-------|

| Field   |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address |     | FC7H |       |     |       |       |       |       |

| Bit          | Description                                                                     |

|--------------|---------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit                                       |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit                                       |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit                                       |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit                                       |

#### Table 46. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7    | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|------|------|-------|-----|-------|-------|-------|-------|

| Field   |      | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET   | 0    | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address | FC8H |      |       |     |       |       |       |       |

| Bit          | Description                                                                     |

|--------------|---------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000. |

| [3]<br>C3ENL | Port C3 Interrupt Request Enable Low Bit                                        |

| [2]<br>C2ENL | Port C2 Interrupt Request Enable Low Bit                                        |

| [1]<br>C1ENL | Port C1 Interrupt Request Enable Low Bit                                        |

| [0]<br>COENL | Port C0 Interrupt Request Enable Low Bit                                        |

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7    | 6    | 5 | 4 | 3        | 2 | 1 | 0 |

|---------|------|------|---|---|----------|---|---|---|

| Field   | IRQE |      |   |   | Reserved |   |   |   |

| RESET   | 0    | 0    | 0 | 0 | 0        | 0 | 0 | 0 |

| R/W     | R/W  | R    | R | R | R        | R | R | R |

| Address |      | FCFH |   |   |          |   |   |   |

|         |      |      |   |   |          |   |   |   |

## Table 49. Interrupt Control Register (IRQCTL)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by executing an Enable Interrupts (EI) or Interrupt Return (IRET) instruction or by a direct register write of 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset, or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                                                                                                            |

# **Timers**

The Z8 Encore! F0830 Series products contain up to two 16-bit reloadable timers that can be used for timing, event counting or generation of pulse width modulated (PWM) signals. The timers feature include:

- 16-bit reload counter

- Programmable prescaler with prescale values ranging from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

# Architecture

Figure 10 displays the architecture of the timers.

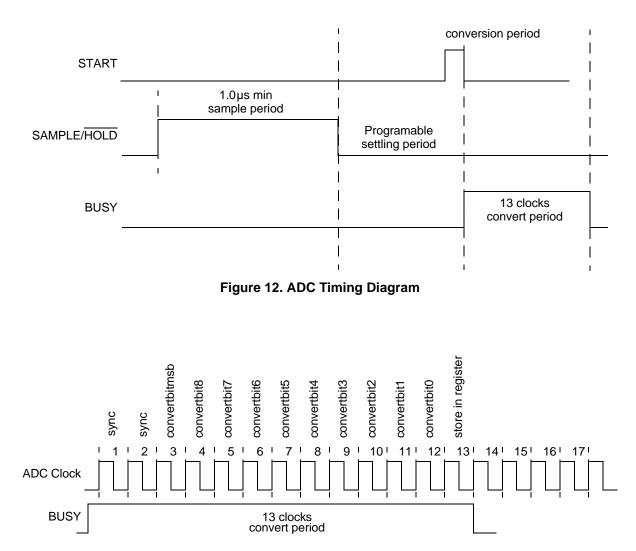

## **ADC** Timing

Each ADC measurement consists of three phases:

- 1. Input sampling (programmable, minimum of 1.0µs)

- 2. Sample-and-hold amplifier settling (programmable, minimum of 0.5µs)

- 3. Conversion is 13 ADCLK cycles

Figures 12 and 13 display the timing of an ADC conversion.

## **Page Erase**

Flash memory can be erased one page (512 bytes) at a time. Page erasing Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the page erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the page erase is complete, the Flash Controller returns to its Locked state.

## **Mass Erase**

Flash memory can also be mass erased using the Flash Controller, but only by using the On-Chip Debugger. Mass erasing Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the mass erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the mass erase is complete, the Flash Controller returns to its Locked state.

## **Flash Controller Bypass**

The Flash Controller can be bypassed; instead, the control signals for Flash memory can be brought out to the GPIO pins. Bypassing the Flash Controller allows faster row programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of Flash memory. Mass Erase and Page Erase operations are also supported, when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to *Third-Party Flash Programming Support for Z8 Encore!*. This document is available for download at <u>www.zilog.com</u>.

## Flash Controller Behavior in Debug Mode

The following behavioral changes can be observed in the Flash Controller when the Flash Controller is accessed using the On-Chip Debugger:

• The Flash write protect option bit is ignored.

| Description (Continued)                             |

|-----------------------------------------------------|

| Filter Select                                       |

| 2-bit selection for the clock filter mode.          |

| 00 = No filter.                                     |

| 01 = Filter low level noise on high level signal.   |

| 10 = Filter high level noise on low level signal.   |

| 11 = Filter both.                                   |

| dicates bit values 3–1; y indicates bit values 1–0. |

|                                                     |

**Note:** The bit values used in Table 89 are set at factory and no calibration is required.

| DlyCtl3, DlyCtl2,<br>DlyCtl1 | Low Noise Pulse<br>on High Signal (ns) | High Noise Pulse<br>on Low Signal (ns) |

|------------------------------|----------------------------------------|----------------------------------------|

| 000                          | 5                                      | 5                                      |

| 001                          | 7                                      | 7                                      |

| 010                          | 9                                      | 9                                      |

| 011                          | 11                                     | 11                                     |

| 100                          | 13                                     | 13                                     |

| 101                          | 17                                     | 17                                     |

| 110                          | 20                                     | 20                                     |

| 111                          | 25                                     | 25                                     |

| Note: The variation is       | about 30%.                             |                                        |

#### Table 90. ClkFlt Delay Control Definition

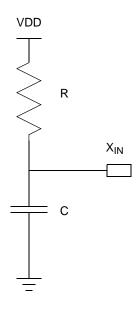

# **Oscillator Operation with an External RC Network**

Figure 26 displays a recommended configuration for connection with an external resistorcapacitor (RC) network.

#### Figure 26. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of  $45 \text{ k}\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is  $40 \text{ k}\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (R in k $\Omega$ ) and capacitor (C in pF) elements using the following equation:

Oscillator Frequency (kHz) =  $\frac{1 \times 10^{6}}{(0.4 \times R \times C) + (4 \times C)}$

Figure 27 displays the typical (3.3V and 25°C) oscillator frequency as a function of the capacitor (C in pF) employed in the RC network assuming a 45 k $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator X<sub>IN</sub> pin and the printed circuit board should be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20pF are recommended. 159

## Example 2

In general, when an instruction format requires an 8-bit register address, the address can specify any register location in the range 0–255 or, using escaped mode addressing, a working register R0–R15. If the contents of register 43H and working register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 102. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device specific product specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU instruction summary and description sections, the operands, condition codes, status flags and address modes are represented by the notational shorthand listed in Table 103.

| Notation | Description                    | Operand | Range                                                     |

|----------|--------------------------------|---------|-----------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).          |

| CC       | Condition Code                 | —       | See condition codes overview in the eZ8 CPU User Manual.  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH     |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                       |

| lr       | Indirect Working Register      | @Rn     | n = 0 –15                                                 |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH       |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12 or 14                           |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH    |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B. |

| r        | Working Register               | Rn      | n = 0 – 15                                                |

#### Table 103. Notational Shorthand

#### 180

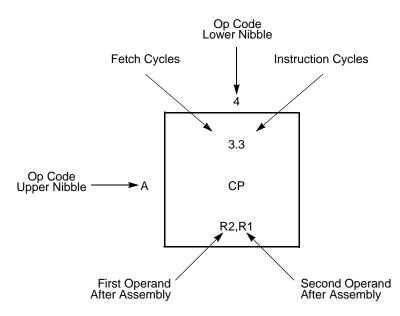

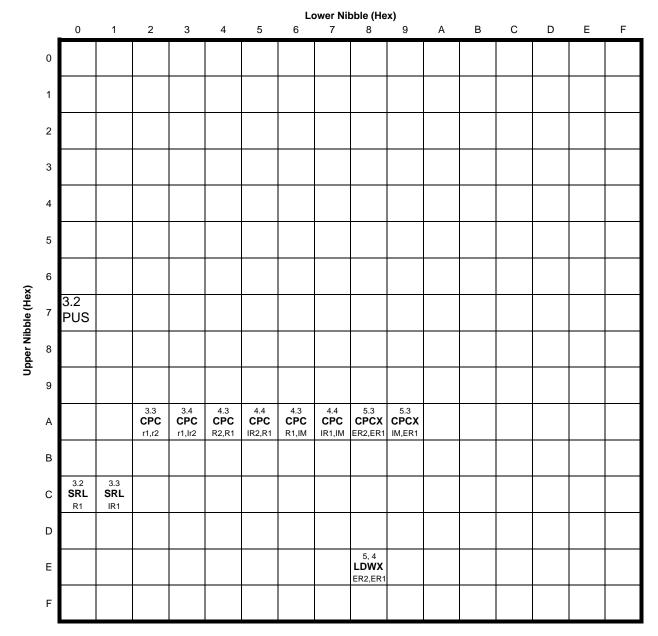

# **Op Code Maps**

A description of the opcode map data and the abbreviations are provided in Figure 28. Table 114 on page 181 lists opcode map abbreviations.

Figure 28. Op Code Map Cell Description

Z8 Encore!<sup>®</sup> F0830 Series Product Specification

Figure 30. Second Op Code Map after 1FH

183

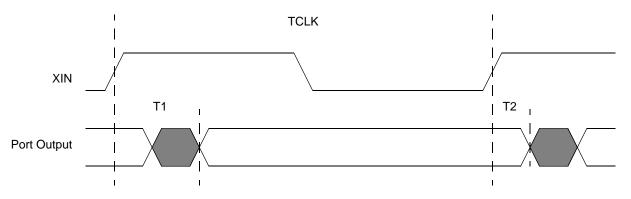

## **General Purpose I/O Port Output Timing**

Figure 34 and Table 125 provide timing information for the GPIO port pins.

|                |                                     | Dela    | y (ns)  |  |  |  |  |

|----------------|-------------------------------------|---------|---------|--|--|--|--|

| Parameter      | Abbreviation                        | Minimum | Maximum |  |  |  |  |

| GPIO Port Pins |                                     |         |         |  |  |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _       | 15      |  |  |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2       | _       |  |  |  |  |

#### Table 125. GPIO Port Output Timing

## Hex Address: FC5

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|--|--|

| Field   | PA7ENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |  |  |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |

| Address |        | FC5H    |        |        |               |        |        |        |  |  |

#### Hex Address: FC6

#### Table 163. Interrupt Request 2 Register (IRQ2)

| Bit     | 7   | 6        | 5   | 4   | 3   | 2    | 1    | 0    |  |

|---------|-----|----------|-----|-----|-----|------|------|------|--|

| Field   |     | Reserved |     |     |     | PC2I | PC1I | PC0I |  |

| RESET   | 0   | 0        | 0   | 0   | 0   | 0    | 0    | 0    |  |

| R/W     | R/W | R/W      | R/W | R/W | R/W | R/W  | R/W  | R/W  |  |

| Address |     | FC6H     |     |     |     |      |      |      |  |

## Hex Address: FC7

#### Table 164. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7        | 6    | 5   | 4   | 3     | 2     | 1     | 0     |  |

|---------|----------|------|-----|-----|-------|-------|-------|-------|--|

| Field   | Reserved |      |     |     | C3ENH | C2ENH | C1ENH | C0ENH |  |

| RESET   | 0        | 0    | 0   | 0   | 0     | 0     | 0     | 0     |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   |  |

| Address |          | FC7H |     |     |       |       |       |       |  |

#### Hex Address: FC8

#### Table 165. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |

|---------|-----|------|-------|-----|-------|-------|-------|-------|--|

| Field   |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |  |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |

| Address |     | FC8H |       |     |       |       |       |       |  |

## Hex Address: FFB

## Table 196. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|---|--------|---|----|----|---|---|---|--|--|

| Field   |   | FFREQL |   |    |    |   |   |   |  |  |

| RESET   | 0 |        |   |    |    |   |   |   |  |  |

| R/W     |   | R/W    |   |    |    |   |   |   |  |  |

| Address |   |        |   | FF | BH |   |   |   |  |  |