Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | -                                                         |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 25                                                        |  |

| Program Memory Size        | 12KB (12K x 8)                                            |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Through Hole                                              |  |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1233pj020eg |  |

| Master Interrupt Enable                                  | 55  |

|----------------------------------------------------------|-----|

| Interrupt Vectors and Priority                           | 56  |

| Interrupt Assertion                                      | 56  |

| Software Interrupt Assertion                             | 57  |

| Interrupt Control Register Definitions                   | 57  |

| Interrupt Request 0 Register                             | 58  |

| Interrupt Request 1 Register                             | 59  |

| Interrupt Request 2 Register                             | 60  |

| IRQ0 Enable High and Low Bit Registers                   | 60  |

| IRQ1 Enable High and Low Bit Registers                   | 62  |

| IRQ2 Enable High and Low Bit Registers                   | 63  |

| Interrupt Edge Select Register                           |     |

| Shared Interrupt Select Register                         |     |

| Interrupt Control Register                               | 67  |

| Timers                                                   | 68  |

| Architecture                                             | 68  |

| Operation                                                | 69  |

| Timer Operating Modes                                    | 69  |

| Reading the Timer Count Values                           | 82  |

| Timer Pin Signal Operation                               | 82  |

| Timer Control Register Definitions                       | 83  |

| Timer 0–1 High and Low Byte Registers                    | 83  |

| Timer Reload High and Low Byte Registers                 | 85  |

| Timer 0–1 PWM High and Low Byte Registers                |     |

| Timer 0–1 Control Registers                              | 87  |

| Watchdog Timer                                           | 92  |

| Operation                                                |     |

| Watchdog Timer Refresh                                   | 93  |

| Watchdog Timer Time-Out Response                         | 93  |

| Watchdog Timer Reload Unlock Sequence                    | 94  |

| Watchdog Timer Control Register Definitions              | 95  |

| Watchdog Timer Control Register                          | 95  |

| Watchdog Timer Reload Upper, High and Low Byte Registers | 96  |

| Analog-to-Digital Converter                              | 98  |

| Architecture                                             |     |

| Operation                                                |     |

| ADC Timing                                               |     |

| ADC Interrupt                                            |     |

| Reference Buffer                                         |     |

| Internal Voltage Reference Generator                     | 101 |

PS025113-1212 Table of Contents

## Z8 Encore!® F0830 Series Product Specification

xiv

| Table 59. | Watchdog Timer Control Register (WDTCTL)           |

|-----------|----------------------------------------------------|

| Table 60. | Watchdog Timer Reload Upper Byte Register (WDTU)   |

| Table 61. | Watchdog Timer Reload High Byte Register (WDTH) 96 |

| Table 62. | Watchdog Timer Reload Low Byte Register (WDTL)     |

| Table 63. | ADC Control Register 0 (ADCCTL0)                   |

| Table 64. | ADC Data High Byte Register (ADCD_H)               |

| Table 65. | ADC Data Low Bits Register (ADCD_L)                |

| Table 66. | Sample Settling Time (ADCSST)                      |

| Table 67. | Sample Time (ADCST)                                |

| Table 68. | Comparator Control Register (CMP0)                 |

| Table 69. | Z8 Encore! F0830 Series Flash Memory Configuration |

| Table 70. | Z8F083 Flash Memory Area Map                       |

| Table 71. | Flash Code Protection using the Flash Option Bits  |

| Table 72. | Flash Control Register (FCTL)                      |

| Table 73. | Flash Status Register (FSTAT)                      |

| Table 74. | Flash Page Select Register (FPS)                   |

| Table 75. | Flash Sector Protect Register (FPROT)              |

| Table 76. | Flash Frequency High Byte Register (FFREQH)        |

| Table 77. | Flash Frequency Low Byte Register (FFREQL)         |

| Table 78. | Trim Bit Address Register (TRMADR)                 |

| Table 79. | Trim Bit Address Map                               |

| Table 80. | Trim Bit Data Register (TRMDR)                     |

| Table 81. | Flash Option Bits at Program Memory Address 0000H  |

| Table 82. | Flash Options Bits at Program Memory Address 0001H |

| Table 83. | Trim Option Bits at 0000H (ADCREF)                 |

| Table 84. | Trim Option Bits at 0001H (TADC_COMP)              |

| Table 85. | Trim Bit Address Space                             |

| Table 86. | Trim Option Bits at 0002H (TIPO)                   |

| Table 87. | Trim Option Bits at 0003H (TVBO)                   |

| Table 88. | VBO Trim Definition                                |

PS025113-1212 List of Tables

PA0 and PA6 contain two different Timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the TIMER mode. For more details, see the <u>Timers</u> chapter on page 68.

#### **Direct LED Drive**

The Port C pins provide a sinked current output, capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels, 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the LED Control registers.

For proper function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin.

Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See the <u>Electrical Characteristics</u> chapter on page 184 for the maximum total current for the applicable package.

#### **Shared Reset Pin**

On the 20- and 28-pin devices, the Port D0 pin shares function with a bidirectional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bidirectional input/output open-drain reset with an internal pull-up until the user software reconfigures it as a GPIO PD0. When in GPIO mode, the Port D0 pin functions as output only, and must be configured as an output. PD0 supports the high drive feature, but not the stop-mode recovery feature.

## **Crystal Oscillator Override**

For systems using a crystal oscillator, the pins PA0 and PA1 are connected to the crystal. When the crystal oscillator is enabled, the GPIO settings are overridden and PA0 and PA1 are disabled. See the <u>Oscillator Control Register Definitions</u> section on page 154.

#### **5V Tolerance**

In the 20- and 28-pin versions of this device, any pin, which shares functionality with an ADC, crystal or comparator port is not 5V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5V-tolerant and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled, but with excess power consumption on pull-up resistor.

PS025113-1212 Direct LED Drive

reload. For the timer output to make a state change at a ONE-SHOT time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode

- Set the prescale value

- Set the initial output level (High or Low) if using the timer output Alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

$$One-Shot\ Mode\ Time-Out\ Period\ (s)\ =\ \frac{(Reload\ Value-Start\ Value)\times Prescale}{System\ Clock\ Frequency\ (Hz)}$$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and for initiating the count:

1. Write to the Timer Control Register to:

PS025113-1212 Operation

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the timer output Alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the timer output function) for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

Continuous Mode Time-Out Period (s) =

$$\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin: timer input alternate function. The TPOL bit in the Timer Control Register determines whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function

PS025113-1212 Operation

### Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 54 and 55, control PWM operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

| Bit     | 7    | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|------------|-----|-----|-----|-----|-----|-----|

| Field   | PWMH |            |     |     |     |     |     |     |

| RESET   | 0    | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |      | F04H, F0CH |     |     |     |     |     |     |

Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7    | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|------------|-----|-----|-----|-----|-----|-----|

| Field   | PWML |            |     |     |     |     |     |     |

| RESET   | 0    | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |      | F05H, F0DH |     |     |     |     |     |     |

| Bit   | Description                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Pulse Width Modulator High and Low Bytes                                                                                                                   |

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current                                                               |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1). |

|       | The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in capture or CAPTURE/COMPARE modes.                             |

# Flash Memory

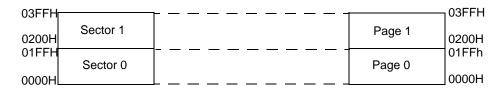

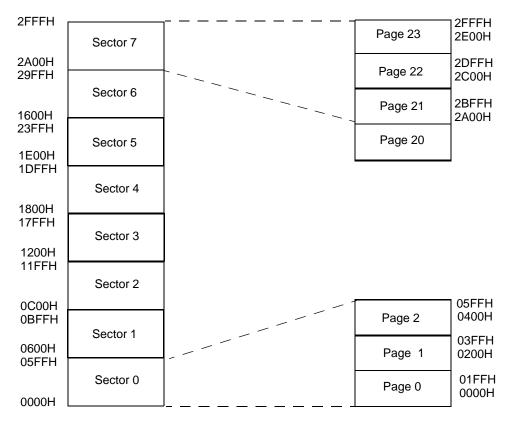

The products in the Z8 Encore! F0830 Series features either 1KB (1024 bytes with NVDS), 2KB (2048 bytes with NVDS), 4KB (4096 bytes with NVDS), 8KB (8192 bytes with NVDS) or 12KB (12288 bytes with no NVDS) of nonvolatile Flash memory with read/write/erase capability. Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F0830 Series, each sector maps to one page (for 1 KB, 2 KB and 4 KB devices), two pages (8 KB device) or three pages (12 KB device).

The first two bytes of Flash program memory is used as Flash option bits. For more information, see *the* Flash Option Bits chapter on page 124.

Table 69 lists the Flash memory configuration for each device in the Z8 Encore! F0830 Series. Figures 14 through 18 display the memory arrangements for each Flash memory size.

| Table 69. Z8 Encore! F0830 | Series Flash Memory | Configuration |

|----------------------------|---------------------|---------------|

|----------------------------|---------------------|---------------|

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F123x     | 12 (12,288)              | 24          | 0000H-2FFFH                    | 1536                         |

| Z8F083x     | 8 (8196)                 | 16          | 0000H-1FFFH                    | 1024                         |

| Z8F043x     | 4 (4096)                 | 8           | 0000H-0FFFH                    | 512                          |

| Z8F023x     | 2 (2048)                 | 4           | 0000H-07FFH                    | 512                          |

| Z8F013x     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

Figure 14. 1K Flash with NVDS

PS025113-1212 Flash Memory

Figure 18. 12K Flash without NVDS

## **Data Memory Address Space**

The Flash information area, including Zilog Flash option bits, are located in the data memory address space. The Z8 Encore! MCU is configured by these proprietary Flash option bits to prevent the user from writing to the eZ8 CPU data memory address space.

### **Flash Information Area**

The Flash information area is physically separate from program memory and is mapped to the address range FE00H to FE7FH. Not all of these addresses are user-accessible. Factory trim values for the VBO, Internal Precision Oscillator and factory calibration data for the ADC are stored here.

Table 70 describes the Flash information area. This 128-byte information area is accessed by setting the bit 7 of the Flash Page Select Register to 1. When access is enabled, the

### **Byte Read**

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine  $(0 \times 2000)$ . At the return from the subroutine, the read byte resides in working register R0 and the read status byte resides in working register R1. The bit fields of this status byte are defined in Table 92. Additionally, the user code should pop the address byte off the stack.

The read routine uses 16 bytes of stack space in addition to the one byte of address pushed by the user code. Sufficient memory must be available for this stack usage.

Due to the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between  $71\mu s$  and  $258\mu s$  (assuming a 20MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a  $6\mu s$  execution time.

The status byte returned by the NVDS read routine is zero for a successful read. If the status byte is nonzero, there is a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have an error.

Table 92. Read Status Byte

| Bit              | 7        | 6 | 5 | 4  | 3        | 2  | 1      | 0        |

|------------------|----------|---|---|----|----------|----|--------|----------|

| Field            | Reserved |   |   | DE | Reserved | FE | IGADDR | Reserved |

| Default<br>Value | 0        | 0 | 0 | 0  | 0        | 0  | 0      | 0        |

| Bit           | Description                                                                                                                                                                                                          |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]         | Reserved These bits are reserved and must be programmed to 000.                                                                                                                                                      |

| [4]<br>DE     | Data Error When reading an NVDS address, if an error is found in the latest data corresponding to this NVDS address, this bit is set to 1. NVDS source code steps forward until it finds valid data at this address. |

| [3]           | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                           |

| [2]<br>FE     | Flash Error If a Flash error is detected, this bit is set to 1.                                                                                                                                                      |

| [1]<br>IGADDR | Illegal Address When NVDS byte reads from invalid addresses (those exceeding the NVDS array size) occur, this bit is set to 1.                                                                                       |

| [0]           | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                           |

PS025113-1212 NVDS Code Interface

If the OCD receives a serial break (nine or more continuous bits low), the autobaud detector/generator resets. Reconfigure the autobaud detector/generator by sending 80H.

#### **OCD Serial Errors**

The OCD can detect any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received Stop bit is Low)

- Transmit collision (simultaneous transmission by OCD and host detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long serial break back to the host and resets the autobaud detector/generator. A framing error or transmit collision may be caused by the host sending a serial break to the OCD. As a result of the open-drain nature of the interface, returning a serial break back to the host only extends the length of the serial break if the host releases the serial break early.

The host transmits a serial break on the DBG pin when first connecting to the Z8 Encore! F0830 Series devices or when recovering from an error. A serial break from the host resets the autobaud generator/detector, but does not reset the OCD Control Register. A serial break leaves the device in DEBUG Mode, if that is the current mode. The OCD is held in reset until the end of the serial break when the DBG pin returns high. Because of the opendrain nature of the DBG pin, the host can send a serial break to the OCD even if the OCD is transmitting a character.

## **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

PS025113-1212 Operation

#### **Runtime Counter**

The OCD contains a 16-bit runtime counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

## **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash read protect option bit (FRP). The FRP prevents the code in memory from being read out of the Z8 Encore! F0830 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 95 summarizes the On-Chip Debugger commands. This table indicates the commands that operate when the device is not in DEBUG Mode (normal operation) and the commands that are disabled by programming the FRP.

**Table 95. On-Chip Debugger Command Summary**

| Debug Command              | Command<br>Byte | Enabled when not in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                     |

|----------------------------|-----------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                             | -                                                                                                                                                                |

| Reserved                   | 01H             | _                               | -                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                             | -                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                               | -                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                             | Cannot clear DBGMODE bit                                                                                                                                         |

| Read OCD Control Register  | 05H             | Yes                             | -                                                                                                                                                                |

| Write Program Counter      | 06H             | _                               | Disabled                                                                                                                                                         |

| Read Program Counter       | 07H             | _                               | Disabled                                                                                                                                                         |

| Write Register             | 08H             | -                               | Only writes of the Flash Memory Control registers are allowed. Additionally, only the Mass Erase command is allowed to be written to the Flash Control register. |

| Read Register              | 09H             | _                               | Disabled                                                                                                                                                         |

| Write Program Memory       | 0AH             | -                               | Disabled                                                                                                                                                         |

| Read Program Memory        | 0BH             | _                               | Disabled                                                                                                                                                         |

| Write Data Memory          | 0CH             | _                               | Yes                                                                                                                                                              |

| Read Data Memory           | 0DH             | _                               | -                                                                                                                                                                |

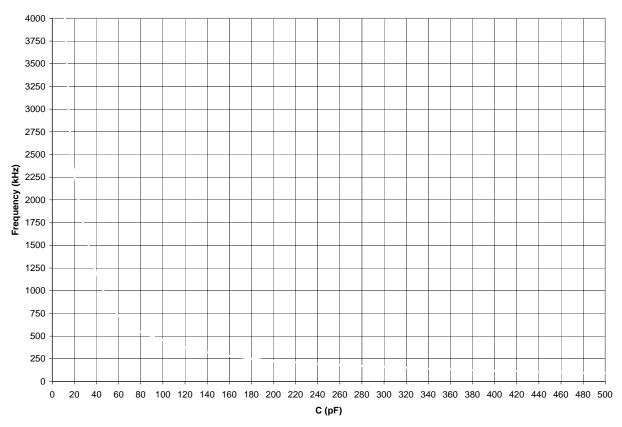

Figure 27. Typical RC Oscillator Frequency as a Function of External Capacitance with a 45  $k\Omega$  Resistor

**Caution:** When using the external RC OSCILLATOR Mode, the oscillator can stop oscillating if the power supply drops below 2.7 V but before it drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

#### **eZ8 CPU Instruction Classes**

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit manipulation

- Block transfer

- CPU control

- Load

- Logical

- Program control

- Rotate and shift

Tables 105 through 112 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instructions can be considered as a subset of more than one category. Within these tables, the source operand is identified as *src*, the destination operand is *dst* and a condition code is *cc*.

**Table 105. Arithmetic Instructions**

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| СРХ      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

## **eZ8 CPU Instruction Summary**

Table 113 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch and the number of CPU clock cycles required for the instruction execution.

Table 113. eZ8 CPU Instruction Summary

| Assembly      |                                |     | ress<br>ode | Op<br>Code(s) |   |   | Fla | ıgs |   |   | Fetch | Instr. |

|---------------|--------------------------------|-----|-------------|---------------|---|---|-----|-----|---|---|-------|--------|

| Mnemonic      | Symbolic Operation             | dst | src         | (Hex)         | С | Z | S   | ٧   | D | Н |       |        |

| ADC dst, src  | $dst \leftarrow dst + src + C$ | r   | r           | 12            | * | * | *   | *   | 0 | * | 2     | 3      |

|               |                                | r   | lr          | 13            | _ |   |     |     |   |   | 2     | 4      |

|               |                                | R   | R           | 14            | _ |   |     |     |   |   | 3     | 3      |

|               |                                | R   | IR          | 15            | _ |   |     |     |   |   | 3     | 4      |

|               |                                | R   | IM          | 16            | _ |   |     |     |   |   | 3     | 3      |

|               |                                | IR  | IM          | 17            | _ |   |     |     |   |   | 3     | 4      |

| ADCX dst, src | dst ← dst + src + C            | ER  | ER          | 18            | * | * | *   | *   | 0 | * | 4     | 3      |

|               |                                | ER  | IM          | 19            | _ |   |     |     |   |   | 4     | 3      |

| ADD dst, src  | dst ← dst + src                | r   | r           | 02            | * | * | *   | *   | 0 | * | 2     | 3      |

|               |                                | r   | lr          | 03            | _ |   |     |     |   |   | 2     | 4      |

|               |                                | R   | R           | 04            | _ |   |     |     |   |   | 3     | 3      |

|               |                                | R   | IR          | 05            | _ |   |     |     |   |   | 3     | 4      |

|               |                                | R   | IM          | 06            | _ |   |     |     |   |   | 3     | 3      |

|               |                                | IR  | IM          | 07            | _ |   |     |     |   |   | 3     | 4      |

| ADDX dst, src | dst ← dst + src                | ER  | ER          | 08            | * | * | *   | *   | 0 | * | 4     | 3      |

|               |                                | ER  | IM          | 09            | _ |   |     |     |   |   | 4     | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

# Op Code Maps

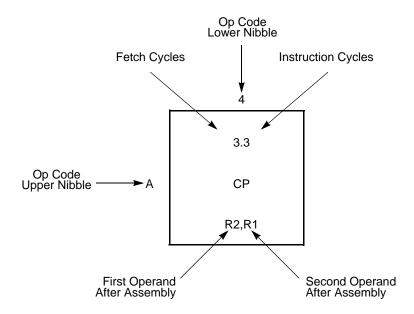

A description of the opcode map data and the abbreviations are provided in Figure 28. Table 114 on page 181 lists opcode map abbreviations.

Figure 28. Op Code Map Cell Description

PS025113-1212 Op Code Maps

**Table 117. AC Characteristics (Continued)**

|                      |                                                  | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     | T <sub>A</sub> = - | .7 to 3.6V<br>-40°C to<br>05°C |       |                           |  |

|----------------------|--------------------------------------------------|----------------------------------------------------------------|-----|--------------------|--------------------------------|-------|---------------------------|--|

| Symbol               | Parameter                                        | Min                                                            | Max | Min                | Max                            | Units | Conditions                |  |

| T <sub>XINR</sub>    | System Clock Rise<br>Time                        |                                                                |     | -                  | 3                              | ns    | T <sub>CLK</sub> = 50 ns  |  |

| T <sub>XINF</sub>    | System Clock Fall Time                           |                                                                |     | -                  | 3                              | ns    | T <sub>CLK</sub> = 50 ns  |  |

| T <sub>XTALSET</sub> | Crystal Oscillator<br>Setup Time                 |                                                                |     | -                  | 30,000                         | cycle | Crystal oscillator cycles |  |

| T <sub>IPOSET</sub>  | Internal Precision<br>Oscillator Startup<br>Time |                                                                |     | -                  | 25                             | μs    | Startup time after enable |  |

| T <sub>WDTSET</sub>  | WDT Startup Time                                 |                                                                |     | _                  | 50                             | μs    | Startup time after reset  |  |

## On-Chip Peripheral AC and DC Electrical Characteristics

Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                  |                                                                           | T <sub>A</sub> = | 0°C to ⋅ | +70°C | T <sub>A</sub> | = -40°C<br>+105°C |      |       |                                                                                                          |

|------------------|---------------------------------------------------------------------------|------------------|----------|-------|----------------|-------------------|------|-------|----------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                                 | Min              | Тур      | Max   | Min            | Typ <sup>1</sup>  | Max  | Units | Conditions                                                                                               |

| V <sub>POR</sub> | Power-On Reset<br>Voltage Threshold                                       |                  |          |       | 2.20           | 2.45              | 2.70 | V     | V <sub>DD</sub> = V <sub>POR</sub><br>(default VBO trim)                                                 |

| $V_{VBO}$        | Voltage Brown-Out<br>Reset Voltage<br>Threshold                           |                  |          |       | 2.15           | 2.40              | 2.65 | V     | V <sub>DD</sub> = V <sub>VBO</sub><br>(default VBO trim)                                                 |

|                  | V <sub>POR</sub> to V <sub>VBO</sub><br>hysteresis                        |                  |          |       |                | 50                | 75   | mV    |                                                                                                          |

|                  | Starting V <sub>DD</sub><br>voltage to ensure<br>valid Power-On<br>Reset. |                  |          |       | -              | V <sub>SS</sub>   | _    | V     |                                                                                                          |

| T <sub>ANA</sub> | Power-On Reset<br>Analog Delay                                            |                  |          |       | -              | 50                | -    | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub><br>Digital Reset delay<br>follows T <sub>ANA</sub> |

Note: <sup>1</sup>Data in the typical column is from characterization at 3.3 V and 0°C. These values are provided for design guidance only and are not tested in production.

**Hex Address: F0D**

Table 143. Timer 1 PWM Low Byte Register (T1PWML)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------|-----|-----|-----|-----|-----|-----|

| Field   |     | PWML |     |     |     |     |     |     |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F0DH |     |     |     |     |     |     |

**Hex Address: F0E**

Table 144. Timer 1 Control Register 0 (T1CTL0)

| Bit     | 7       | 6    | 5    | 4        | 3   | 2    | 1   | 0      |

|---------|---------|------|------|----------|-----|------|-----|--------|

| Field   | TMODEHI | TICO | NFIG | Reserved |     | PWMD |     | INPCAP |

| RESET   | 0       | 0    | 0    | 0        | 0   | 0    | 0   | 0      |

| R/W     | R/W     | R/W  | R/W  | R/W      | R/W | R/W  | R/W | R/W    |

| Address |         | F0EH |      |          |     |      |     |        |

**Hex Address: F0F**

Table 145. Timer 1 Control Register 1 (T1CTL1)

| Bit     | 7   | 6    | 5   | 4    | 3   | 2     | 1   | 0   |  |

|---------|-----|------|-----|------|-----|-------|-----|-----|--|

| Field   | TEN | TPOL |     | PRES |     | TMODE |     |     |  |

| RESET   | 0   | 0    | 0   | 0    | 0   | 0     | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W  | R/W | R/W   | R/W | R/W |  |

| Address |     | F0FH |     |      |     |       |     |     |  |

Hex Addresses: F10-F6F

This address range is reserved.

PS025113-1212 Timer 0

**Hex Address: FC1**

Table 158. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit     | 7        | 6     | 5     | 4        | 3        | 2        | 1        | 0      |

|---------|----------|-------|-------|----------|----------|----------|----------|--------|

| Field   | Reserved | T1ENH | T0ENH | Reserved | Reserved | Reserved | Reserved | ADCENH |

| RESET   | 0        | 0     | 0     | 0        | 0        | 0        | 0        | 0      |

| R/W     | R/W      | R/W   | R/W   | R/W      | R/W      | R/W      | R/W      | R/W    |

| Address |          | FC1H  |       |          |          |          |          |        |

**Hex Address: FC2**

Table 159. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5     | 4        | 3        | 2        | 1        | 0      |

|---------|----------|-------|-------|----------|----------|----------|----------|--------|

| Field   | Reserved | T1ENL | T0ENL | Reserved | Reserved | Reserved | Reserved | ADCENL |

| RESET   | 0        | 0     | 0     | 0        | 0        | 0        | 0        | 0      |

| R/W     | R        | R/W   | R/W   | R/W      | R/W      | R        | R        | R/W    |

| Address |          | FC2H  |       |          |          |          |          |        |

**Hex Address: FC3**

Table 160. Interrupt Request 1 Register (IRQ1)

| Bit     | 7    | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|-------|------|------|------|------|------|------|

| Field   | PA7I | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET   | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |      |       |      | FC   | 3H   |      |      |      |

**Hex Address: FC4**

Table 161. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | PA3ENH | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0      | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |        | FC4H    |        |        |        |        |        |        |

PS025113-1212 Interrupt Controller

| page select register 121, 122                                                 | indexed 165                        |

|-------------------------------------------------------------------------------|------------------------------------|

| FPS register 121, 122                                                         | indirect address prefix 165        |

| FSTAT register 120                                                            | indirect register 164              |

| •                                                                             | indirect register pair 164         |

|                                                                               | indirect working register 164      |

| G                                                                             | indirect working register pair 164 |

| gated mode 89                                                                 | instruction set, ez8 CPU 162       |

| general-purpose I/O 33                                                        | instructions                       |

| GPIO 4, 33                                                                    | ADC 166                            |

| alternate functions 34                                                        | ADCX 166                           |

| architecture 34                                                               | ADD 166                            |

| control register definitions 39                                               | ADDX 166                           |

| input data sample timing 195                                                  | AND 169                            |

| interrupts 39                                                                 | ANDX 169                           |

| port A-C pull-up enable sub-registers 46, 47, 48                              | arithmetic 166                     |

| port A-H address registers 40                                                 | BCLR 167                           |

| port A-H address registers 40<br>port A-H alternate function sub-registers 42 | BIT 167                            |

| port A-H control registers 41                                                 | bit manipulation 167               |

| port A-H data direction sub-registers 41                                      | block transfer 167                 |

| port A-H high drive enable sub-registers 44                                   | BRK 169                            |

| port A-H input data registers 49                                              | BSET 167                           |

| port A-H output control sub-registers 43                                      | BSWAP 167, 169                     |

| port A-H output data registers 50, 51                                         | BTJ 169                            |

| port A-H stop mode recovery sub-registers 45                                  | BTJNZ 166, 169                     |

| port availability by device 33                                                | BTJZ 169                           |

| port input timing 195                                                         | CALL 169                           |

| port output timing 196                                                        | CCF 167, 168                       |

| port output timing 170                                                        | CLR 168                            |

|                                                                               | COM 169                            |

| Н                                                                             | CP 166                             |

| H 165                                                                         | CPC 166                            |

| HALT 168                                                                      | CPCX 166                           |

| halt mode 31, 168                                                             | CPU control 168                    |

| hexadecimal number prefix/suffix 165                                          | CPX 166                            |

| nexadecimal number prenty/surnx 103                                           | DA 166                             |

|                                                                               | DEC 166                            |

| 1                                                                             | DECW 166                           |

| IM 164                                                                        | DI 168                             |

| IM 164                                                                        | DJNZ 169                           |

| immediate data 164                                                            | EI 168                             |

| immediate operand prefix 165                                                  | HALT 168                           |

| INC 166 increment 166                                                         | INC 166                            |

|                                                                               | INCW 167                           |

| increment word 167<br>INCW 167                                                | IRET 169                           |

| INCW 10/                                                                      |                                    |

# **Customer Support**

To share comments, get your technical questions answered or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at http://support.zilog.com.

To learn more about this product, find additional documentation or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <a href="http://zilog.com/ktp://zilog.com/forum">http://zilog.com/forum</a>. <a href="http://zilog.com/forum">kb</a> or consider participating in the Zilog Forum at <a href="http://zilog.com/forum">http://zilog.com/forum</a>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <a href="http://www.zilog.com">http://www.zilog.com</a>.

PS025113-1212 Customer Support