Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 12KB (12K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1233pj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Tables

| Table 1.  | Z8 Encore! F0830 Series Family Part Selection Guide 2              |

|-----------|--------------------------------------------------------------------|

| Table 2.  | Acronyms and Expansions                                            |

| Table 3.  | Z8 Encore! F0830 Series Package Options 7                          |

| Table 4.  | Signal Descriptions                                                |

| Table 5.  | Pin Characteristics (20- and 28-pin Devices) 13                    |

| Table 6.  | Z8 Encore! F0830 Series Program Memory Maps 15                     |

| Table 7.  | Z8 Encore! F0830 Series Flash Memory Information Area Map 16       |

| Table 8.  | Register File Address Map 17                                       |

| Table 9.  | Reset and Stop Mode Recovery Characteristics and Latency 22        |

| Table 10. | Reset Sources and Resulting Reset Type                             |

| Table 11. | Stop Mode Recovery Sources and Resulting Action 27                 |

| Table 12. | POR Indicator Values                                               |

| Table 13. | Reset Status Register (RSTSTAT)                                    |

| Table 14. | Power Control Register 0 (PWRCTL0)                                 |

| Table 15. | Port Availability by Device and Package Type                       |

| Table 16. | Port Alternate Function Mapping                                    |

| Table 17. | GPIO Port Registers and Subregisters                               |

| Table 18. | Port A-D GPIO Address Registers (PxADDR) 40                        |

| Table 19. | Port Control Subregister Access                                    |

| Table 20. | Port A–D Control Registers (PxCTL)                                 |

| Table 21. | Port A–D Data Direction Subregisters (PxDD) 41                     |

| Table 22. | Port A–D Alternate Function Subregisters (PxAF)                    |

| Table 23. | Port A–D Output Control Subregisters (PxOC)                        |

| Table 24. | Port A–D High Drive Enable Subregisters (PxHDE)                    |

| Table 25. | Port A–D Stop Mode Recovery Source Enable Subregisters (PxSMRE) 45 |

| Table 26. | Port A–D Pull-Up Enable Subregisters (PxPUE)                       |

| Table 27. | Port A–D Alternate Function Set 1 Subregisters (PxAFS1) 47         |

| Table 28. | Port A–D Alternate Function Set 2 Subregisters (PxAFS2)            |

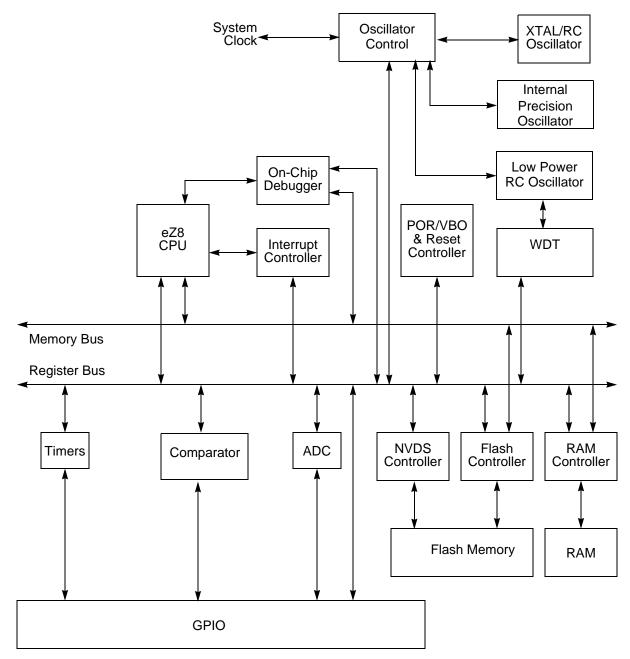

# **Block Diagram**

Figure 1 displays a block diagram of the Z8 Encore! F0830 Series architecture.

Figure 1. Z8 Encore! F0830 Series Block Diagram

### 17

# **Register Map**

Table 8 provides an address map of the Z8 Encore! F0830 Series register file. Not all devices and package styles in the Z8 Encore! F0830 Series support the ADC or all of the GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)    | Register Description              | Mnemonic      | Reset (Hex) | Page No. |

|------------------|-----------------------------------|---------------|-------------|----------|

| General Purpos   | e RAM                             |               |             |          |

| 000–0FF          | General purpose register file RAM |               | XX          |          |

| 100–EFF          | Reserved                          | _             | XX          |          |

| Timer 0          |                                   |               |             |          |

| F00              | Timer 0 high byte                 | T0H           | 00          | 83       |

| F01              | Timer 0 low byte                  | TOL           | 01          | 83       |

| F02              | Timer 0 reload high byte          | TORH          | FF          | 85       |

| F03              | Timer 0 reload low byte           | TORL          | FF          | 85       |

| F04              | Timer 0 PWM high byte             | <b>T0PWMH</b> | 00          | 86       |

| F05              | Timer 0 PWM low byte              | TOPWML        | 00          | 86       |

| F06              | Timer 0 control 0                 | T0CTL0        | 00          | 87       |

| F07              | Timer 0 control 1                 |               | 00          | 88       |

| Timer 1          |                                   |               |             |          |

| F08              | Timer 1 high byte                 | T1H           | 00          | 83       |

| F09              | Timer 1 low byte                  | T1L           | 01          | 83       |

| F0A              | Timer 1 reload high byte          | T1RH          | FF          | 85       |

| F0B              | Timer 1 reload low byte           | T1RL          | FF          | 85       |

| F0C              | Timer 1 PWM high byte             | T1PWMH        | 00          | 86       |

| F0D              | Timer 1 PWM low byte              | T1PWML        | 00          | 86       |

| F0E              | Timer 1 control 0                 | T1CTL0        | 00          | 87       |

| F0F              | Timer 1 control 1                 | T1CTL1        | 00          | 83       |

| F10–F6F          | Reserved                          | _             | XX          |          |

| Analog-to-Digita | al Converter (ADC)                |               |             |          |

| F70              | ADC control 0                     | ADCCTL0       | 00          | 102      |

| F71              | Reserved                          |               | XX          |          |

| F72              | ADC data high byte                | ADCD_H        | XX          | 103      |

#### Table 8. Register File Address Map

Note: XX = Undefined.

#### 31

# HALT Mode

Executing the eZ8 CPU HALT instruction places the device into HALT Mode. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any one of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as digital inputs must be driven to  $V_{DD}$  when pull-up register bit is enabled or to one of power rail ( $V_{DD}$  or GND) when pull-up register bit is disabled.

# **Peripheral Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! F0830 Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

#### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

# Port A–D Control Registers

The Port A–D Control registers, shown in Table 20, set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction.

| Bit     | 7                      | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------------------|-----------------------------|---|---|---|---|---|---|

| Field   | PCTL                   |                             |   |   |   |   |   |   |

| RESET   | 00H                    |                             |   |   |   |   |   |   |

| R/W     | R/W                    | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| Address | FD1H, FD5H, FD9H, FDDH |                             |   |   |   |   |   |   |

| Table 20 | . Port A-D | Control | Registers | (PxCTL) |

|----------|------------|---------|-----------|---------|

|----------|------------|---------|-----------|---------|

| Bit   | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Port Control</b>                                                                                   |

| PCTL  | The Port Control Register provides access to all subregisters that configure the GPIO port operation. |

### Port A–D Data Direction Subregisters

The Port A–D Data Direction Subregister, shown in Table 21, is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register.

| Bit     | 7         | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| Field   | DD7       | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET   | 1         | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W       | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | If 01H ir | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Direction                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction Register setting.</li> <li>0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register The output driver is tristated.</li> </ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                       |

Note: x indicates the specific GPIO port pin number (7–0).

#### Port A–D Alternate Function Set 1 Subregisters

The Port A–D Alternate Function Set 1 Subregister, shown in Table 27, is accessed through the Port A–D Control Register by writing 07H to the Port A–D Address Register. The Alternate Function Set 1 subregisters select the alternate function available at a port pin. Alternate functions selected by setting or clearing bits in this register are defined in the <u>GPIO Alternate Functions</u> section on page 34.

Note:Alternate function selection on the port pins must also be enabled, as described in the PortA-D Alternate Function Subregisters section on page 42.

| Bit     | 7                                                                                     | 6      | 5      | 4      | 3      | 2      | 1           | 0      |

|---------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|-------------|--------|

| Field   | PAFS17                                                                                | PAFS16 | PAFS15 | PAFS14 | PAFS13 | PAFS12 | PAFS11      | PAFS10 |

| RESET   | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0           | 0      |

| R/W     | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W         | R/W    |

| Address | If 07H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |             |        |

| Dit     | Description                                                                           |        |        |        |        |        | E Control 1 | Cyster |

#### Table 27. Port A–D Alternate Function Set 1 Subregisters (PxAFS1)

#### Bit Description

#### [7:0] Port Alternate Function Set 1

PAFS1x 0 = Port Alternate function selected as defined in Table 16 in GPIO Alternate Functions section.

> 1 = Port Alternate function selected as defined in Table 16 in GPIO Alternate Functions section.

Note: x indicates the specific GPIO port pin number (7–0).

# LED Drive Enable Register

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6    | 5   | 4    | 3      | 2   | 1   | 0   |

|---------|-----|------|-----|------|--------|-----|-----|-----|

| Field   |     |      |     | LEDE | N[7:0] |     |     |     |

| RESET   | 0   | 0    | 0   | 0    | 0      | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Address |     | F82H |     |      |        |     |     |     |

| Bit   | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | LED Drive Enable                                                                                                                                                           |

| LEDEN | These bits determine which Port C pins are connected to an internal current sink.<br>0 = Tristate the Port C pin.<br>1= Connect controlled current sink to the Port C pin. |

# LED Drive Level High Register

The LED Drive Level High Register, shown in Table 32, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | LEDLVLH[7:0] |     |     |     |     |     |     |     |

| RESET   | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F83H         |     |     |     |     |     |     |     |

#### Bit Description

[7:0] LED Level High Bits

LEDLVLH {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3mA.

01= 7 mA.

10= 13mA.

11= 20mA.

## **Shared Interrupt Select Register**

The shared interrupt select (IRQSS) register determines the source of the PADxS interrupts. See Table 48. The shared interrupt select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit     | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |

|---------|----------|-------|----------|-----|-----|-----|-----|-----|

| Field   | Reserved | PA6CS | Reserved |     |     |     |     |     |

| RESET   | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |

| Address | FCEH     |       |          |     |     |     |     |     |

#### Table 48. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                                         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]          | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt caused by PA6CS interrupt request.</li> <li>1 = The comparator is used for the interrupt caused by PA6CS interrupt request.</li> </ul> |

| [5:0]        | <b>Reserved</b><br>These registers are reserved and must be programmed to 000000.                                                                                                                                   |

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7    | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|----------|---|---|---|---|---|---|

| Field   | IRQE | Reserved |   |   |   |   |   |   |

| RESET   | 0    | 0        | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W     | R/W  | R        | R | R | R | R | R | R |

| Address | FCFH |          |   |   |   |   |   |   |

|         |      |          |   |   |   |   |   |   |

### Table 49. Interrupt Control Register (IRQCTL)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by executing an Enable Interrupts (EI) or Interrupt Return (IRET) instruction or by a direct register write of 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset, or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                                                                                                            |

## **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers, shown in Tables 52 and 53, store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte Register are stored in a temporary holding register. When a write to the Timer Reload Low Byte Register occurs, the temporary holding register value is written to the Timer High Byte Register. This operation allows simultaneous updates of the 16-bit timer reload value. In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit compare value.

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TRH        |     |     |     |     |     |     |     |

| RESET   | 1          | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F02H, F0AH |     |     |     |     |     |     |     |

#### Table 52. Timer 0–1 Reload High Byte Register (TxRH)

#### Table 53. Timer 0–1 Reload Low Byte Register (TxRL)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   |            | TRL |     |     |     |     |     |     |

| RESET   | 1          | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F03H, F0BH |     |     |     |     |     |     |     |

| Bit      | Description                                                                                                                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]    | Timer Reload Register High and Low                                                                                                                                                                                            |

| TRH, TRL | These two bytes form the 16-bit reload value, {TRH[7:0], TRL[7:0]}. This value sets the max-<br>imum count value, which initiates a timer reload to 0001H. In COMPARE Mode, these two<br>bytes form the 16-bit compare value. |

### **Page Erase**

Flash memory can be erased one page (512 bytes) at a time. Page erasing Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the page erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the page erase is complete, the Flash Controller returns to its Locked state.

### **Mass Erase**

Flash memory can also be mass erased using the Flash Controller, but only by using the On-Chip Debugger. Mass erasing Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the mass erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the mass erase is complete, the Flash Controller returns to its Locked state.

### **Flash Controller Bypass**

The Flash Controller can be bypassed; instead, the control signals for Flash memory can be brought out to the GPIO pins. Bypassing the Flash Controller allows faster row programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of Flash memory. Mass Erase and Page Erase operations are also supported, when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to *Third-Party Flash Programming Support for Z8 Encore!*. This document is available for download at <u>www.zilog.com</u>.

### Flash Controller Behavior in Debug Mode

The following behavioral changes can be observed in the Flash Controller when the Flash Controller is accessed using the On-Chip Debugger:

• The Flash write protect option bit is ignored.

## **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control Register before programming or erasing Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, Flash memory can be enabled for mass erase or page erase by writing the appropriate enable command to the FCTL. Page erase applies only to the active page selected in Flash Page Select Register. Mass erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its Locked state. The write-only Flash Control Register shares its register file address with the read-only Flash Status Register.

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|---|---|---|---|---|---|---|

| Field   | FCMD |   |   |   |   |   |   |   |

| RESET   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W     | W    | W | W | W | W | W | W | W |

| Address | FF8H |   |   |   |   |   |   |   |

| Table 72. | Flash | Control | Register | (FCTL) |

|-----------|-------|---------|----------|--------|

|-----------|-------|---------|----------|--------|

#### Bit Description

| [7:0] | Flash Command |

|-------|---------------|

|-------|---------------|

- FCMD 73H = First unlock command.

- 8CH = Second unlock command.

- 95H = Page erase command (must be third command in sequence to initiate page erase).

- 63H = Mass erase command (must be third command in sequence to initiate mass erase).

- 5EH = Enable Flash Sector Protect Register access.

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a system reset

# **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 start bit, 8 data bits (least-significant bit first) and 1 stop bit. See Figure 23.

| <br>START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-----------|----|----|----|----|----|----|----|----|------|

| OTAR      | 00 | ы  | 02 | 05 | D4 | 00 | DU | ы  | 0101 |

### Figure 23. OCD Data Format

# **OCD Autobaud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an autobaud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits low (one Start bit plus 7 data bits), framed between high bits. The autobaud detector measures this period and sets the OCD baud rate generator accordingly.

The autobaud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 94 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency<br>(MHz) | Recommended<br>Maximum Baud Rate<br>(kbps) | Recommended<br>Standard PC Baud Rate<br>(bps) | Minimum Baud Rate<br>(kbps) |  |

|------------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|--|

| 20.0                               | 2500.0                                     | 1,843,200                                     | 39                          |  |

| 1.0                                | 125.0                                      | 115,200                                       | 1.95                        |  |

| 0.032768 (32 KHz)                  | 4.096                                      | 2400                                          | 0.064                       |  |

| Table 9 | 94. OCD | Baud-Rate | Limits |

|---------|---------|-----------|--------|

|         |         |           |        |

If the OCD receives a serial break (nine or more continuous bits low), the autobaud detector/generator resets. Reconfigure the autobaud detector/generator by sending 80H.

### **OCD Serial Errors**

The OCD can detect any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received Stop bit is Low)

- Transmit collision (simultaneous transmission by OCD and host detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long serial break back to the host and resets the autobaud detector/generator. A framing error or transmit collision may be caused by the host sending a serial break to the OCD. As a result of the open-drain nature of the interface, returning a serial break back to the host only extends the length of the serial break if the host releases the serial break early.

The host transmits a serial break on the DBG pin when first connecting to the Z8 Encore! F0830 Series devices or when recovering from an error. A serial break from the host resets the autobaud generator/detector, but does not reset the OCD Control Register. A serial break leaves the device in DEBUG Mode, if that is the current mode. The OCD is held in reset until the end of the serial break when the DBG pin returns high. Because of the opendrain nature of the DBG pin, the host can send a serial break to the OCD even if the OCD is transmitting a character.

### **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

149

#### Table 96. OCD Control Register (OCDCTL)

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                     | 6                                                                                                                                                                                                                                                                                                                                                                                                 | 5           | 4          | 3           | 2     | 1 | 0   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-------|---|-----|--|--|--|--|

| Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DBGMODE                                                               | BRKEN                                                                                                                                                                                                                                                                                                                                                                                             | DBGACK      |            | Res         | erved |   | RST |  |  |  |  |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                 | 0           | 0          | 0           | 0     | 0 | 0   |  |  |  |  |

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                                               | R/W         | R          | R           | R     | R | R/W |  |  |  |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Descriptio                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                       |             |            |             |       |   |     |  |  |  |  |

| <ul> <li>[7] DEBUG Mode</li> <li>DBGMODE The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Flash read protect option bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.</li> <li>0 = The Z8 Encore! F0830 Series device is operating in NORMAL Mode.</li> <li>1 = The Z8 Encore! F0830 Series device is in DEBUG Mode.</li> </ul> |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                   |             |            |             |       |   |     |  |  |  |  |

| [6]<br>BRKEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | This bit co<br>are disable<br>when a BR<br>cally set to<br>0 = Breakp | <b>Breakpoint Enable</b> This bit controls the behavior of the BRK instruction (opcode 00H). By default, breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1 when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.         0 = Breakpoints are disabled.         1 = Breakpoints are enabled. |             |            |             |       |   |     |  |  |  |  |

| [5]<br>DBGACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This bit en<br>Debug ack<br>0 = Debug                                 | <ul> <li>Debug Acknowledge</li> <li>This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a</li> <li>Debug acknowledge character (FFH) to the host when a breakpoint occurs.</li> <li>0 = Debug acknowledge is disabled.</li> <li>1 = Debug acknowledge is enabled.</li> </ul>                                                                                   |             |            |             |       |   |     |  |  |  |  |

| [4:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reserved<br>These bits                                                | are reserve                                                                                                                                                                                                                                                                                                                                                                                       | ed and must | be progran | nmed to 000 | 00.   |   |     |  |  |  |  |

| [0]       Reset         RST       Setting this bit to 1 resets the Z8F04xA family device. The device goes through a Power-On Reset sequence with the exception that the On-Chip Debugger is not r bit is automatically cleared to 0 at the end of the reset sequence.         0 = No effect.       1 = Reset the Flash read protect option bit device.                                                                                                                                                                                                                                               |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                   |             |            |             |       |   |     |  |  |  |  |

# **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Table 97. OCD Status Register (OCDSTAT) | Table 97. | OCD | Status | Register | (OCDSTAT) |

|-----------------------------------------|-----------|-----|--------|----------|-----------|

|-----------------------------------------|-----------|-----|--------|----------|-----------|

| Bit   | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|-----|------|--------|----------|---|---|---|---|--|--|--|--|

| Field | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |  |  |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |  |  |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |  |  |  |

| Bit   |     |      |        |          |   |   |   |   |  |  |  |  |

| Description                                                      |

|------------------------------------------------------------------|

| Debug Status<br>0 = NORMAL Mode.                                 |

| 1 = DEBUG Mode.                                                  |

| HALT Mode                                                        |

| 0 = Not in HALT Mode.                                            |

| 1 = In HALT Mode.                                                |

| Flash Read Protect Option Bit Enable                             |

| 0 = FRP bit enabled, that allows disabling of many OCD commands. |

| 1 = FRP bit has no effect.                                       |

| Reserved                                                         |

| These bits are reserved and must be programmed to 00000.         |

|                                                                  |

### Table 110. Logical Instructions

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

#### Table 111. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | —               | On-chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | —               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

|          |                 |                               |

#### Table 112. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction               |

|----------|----------|---------------------------|

| BSWAP    | dst      | Bit Swap                  |

| RL       | dst      | Rotate Left               |

| RLC      | dst      | Rotate Left through Carry |

|                   |                                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = −40°C to<br>+105°C |                  |     |       |                                                             |  |

|-------------------|-------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|-----|-------|-------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                 | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max | Units | Conditions                                                  |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>disabled                              |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>enabled                               |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                                            |                               |     |     | _                                   | 10               | _   | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to gen<br>erate a Reset. |  |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to<br>transition from $V_{SS}$<br>to $V_{POR}$ to ensure<br>valid Reset |                               |     |     | 0.10                                | _                | 100 | ms    |                                                             |  |

### Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

ance only and are not tested in production.

# Low Power Control

For more information about the Power Control Register, see the <u>Power Control Register</u> <u>Definitions</u> section on page 31.

### Hex Address: F80

| Bit     | 7   | 6        | 5   | 4   | 3        | 2        | 1    | 0        |  |  |  |

|---------|-----|----------|-----|-----|----------|----------|------|----------|--|--|--|

| Field   |     | Reserved |     | VBO | Reserved | Reserved | COMP | Reserved |  |  |  |

| RESET   | 1   | 0        | 0   | 0   | 1        | 0        | 0    | 0        |  |  |  |

| R/W     | R/W | R/W      | R/W | R/W | R/W      | R/W      | R/W  | R/W      |  |  |  |

| Address |     | F80H     |     |     |          |          |      |          |  |  |  |

#### Table 151. Power Control Register 0 (PWRCTL0)

### Hex Address: F81

This address range is reserved.

# **LED Controller**

For more information about the LED Drive registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

### Hex Address: F82

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | LEDEN[7:0] |     |     |     |     |     |     |     |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F82H       |     |     |     |     |     |     |     |

#### Table 152. LED Drive Enable (LEDEN)

# **Customer Support**

To share comments, get your technical questions answered or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://zilog.com/</u><u>kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.