Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 12KB (12K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-VQFN Exposed Pad                                       |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1233qh020sg |

# Z8 Encore!® F0830 Series Product Specification

viii

| Operation                                        |           |

|--------------------------------------------------|-----------|

| NVDS Code Interface                              |           |

| Byte Write                                       |           |

| Byte Read                                        |           |

| Power Failure Protection                         |           |

| Optimizing NVDS Memory Usage for Execution Speed | . 137     |

| On-Chip Debugger                                 |           |

| Architecture                                     |           |

| Operation                                        |           |

| OCD Interface                                    | . 140     |

| DEBUG Mode                                       |           |

| OCD Data Format                                  |           |

| OCD Autobaud Detector/Generator                  |           |

| OCD Serial Errors                                | . 143     |

| Breakpoints                                      | . 143     |

| Runtime Counter                                  | . 144     |

| On-Chip Debugger Commands                        | . 144     |

| On-Chip Debugger Control Register Definitions    | . 148     |

| OCD Control Register                             | . 148     |

| OCD Status Register                              | . 150     |

| Oscillator Control                               | . 151     |

| Operation                                        |           |

| System Clock Selection                           |           |

| Clock Failure Detection and Recovery             |           |

| Oscillator Control Register Definitions          |           |

| Crystal Oscillator                               |           |

|                                                  |           |

| Operating Modes                                  |           |

| Crystal Oscillator Operation                     |           |

| Oscillator Operation with an External RC Network |           |

| Internal Precision Oscillator                    |           |

| Operation                                        | . 161     |

| eZ8 CPU Instruction Set                          | . 162     |

| Assembly Language Programming Introduction       | . 162     |

| Assembly Language Syntax                         |           |

| eZ8 CPU Instruction Notation                     |           |

| eZ8 CPU Instruction Classes                      |           |

| eZ8 CPU Instruction Summary                      | . 171     |

| On Code Mans                                     | . 180     |

| N/// N/// N// 17101/07                           | . , ( ) \ |

PS025113-1212 Table of Contents

## List of Figures

| Figure 1.  | Z8 Encore! F0830 Series Block Diagram                                        | 3    |

|------------|------------------------------------------------------------------------------|------|

| Figure 2.  | Z8F0830 Series in 20-Pin SOIC, SSOP, PDIP Package                            | 8    |

| Figure 3.  | Z8F0830 Series in 28-Pin SOIC, SSOP, PDIP Package                            | 8    |

| Figure 4.  | Z8F0830 Series in 20-Pin QFN Package                                         | 9    |

| Figure 5.  | Z8F0830 Series in 28-Pin QFN Package                                         | . 10 |

| Figure 6.  | Power-On Reset Operation                                                     | . 24 |

| Figure 7.  | Voltage Brown-Out Reset Operation                                            | . 25 |

| Figure 8.  | GPIO Port Pin Block Diagram                                                  | . 34 |

| Figure 9.  | Interrupt Controller Block Diagram                                           | . 55 |

| Figure 10. | Timer Block Diagram                                                          | . 69 |

| Figure 11. | Analog-to-Digital Converter Block Diagram                                    | . 99 |

| Figure 12. | ADC Timing Diagram                                                           | 100  |

| Figure 13. | ADC Convert Timing                                                           | 100  |

| Figure 14. | 1K Flash with NVDS                                                           | 108  |

| Figure 15. | 2K Flash with NVDS                                                           | 109  |

| Figure 16. | 4K Flash with NVDS                                                           | 109  |

| Figure 17. | 8K Flash with NVDS                                                           | 110  |

| Figure 18. | 12K Flash without NVDS                                                       | 111  |

| Figure 19. | Flash Controller Operation Flow Chart                                        | 113  |

| Figure 20. | On-Chip Debugger Block Diagram                                               | 139  |

| Figure 21. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2 | 140  |

| Figure 22. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2 | 141  |

| Figure 23. | OCD Data Format                                                              | 142  |

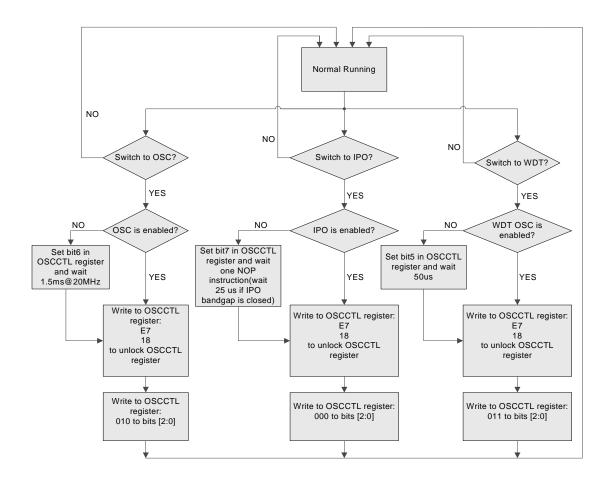

| Figure 24. | Oscillator Control Clock Switching Flow Chart                                | 156  |

| Figure 25. | Recommended 20MHz Crystal Oscillator Configuration                           | 158  |

| Figure 26  | Connecting the On-Chin Oscillator to an External RC Network                  | 150  |

PS025113-1212 List of Figures

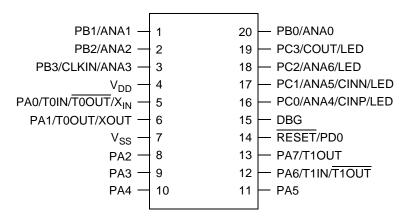

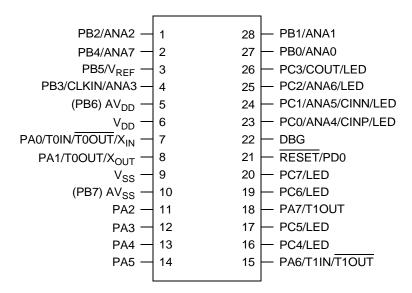

The analog supply pins ( $AV_{DD}$  and  $AV_{SS}$ ) are also not available on these parts and are replaced by PB6 and PB7.

At reset, by default, all pins of Port A, B and C are in Input state. The alternate functionality is also disabled, so the pins function as general purpose input ports until programmed otherwise. At power-up, the Port D0 pin defaults to the RESET Alternate function.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

Figure 2. Z8F0830 Series in 20-Pin SOIC, SSOP, PDIP Package

Figure 3. Z8F0830 Series in 28-Pin SOIC, SSOP, PDIP Package

PS025113-1212 Pin Configurations

### **Stop Mode Recovery Using the External RESET Pin**

When the Z8 Encore! F0830 Series device is in STOP Mode and the external RESET pin is driven low, a system reset occurs. Because of a glitch filter operating on the RESET pin, the low pulse must be greater than the minimum width specified about 12 ns or it is ignored. The EXT bit in the Reset Status (RSTSTAT) Register is set.

### **Debug Pin Driven Low**

Debug reset is initiated when the On-Chip Debugger detects any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received STOP bit is Low)

- Transmit collision (simultaneous OCD and host transmission detected by the OCD)

When the Z8F0830 Series device is operating in STOP Mode, the debug reset will cause a system reset. The On-Chip Debugger block is not reset, but the remainder of the chip's operations go through a normal system reset. The POR bit in the Reset Status (RSTSTAT) Register is set to 1.

### **Reset Register Definitions**

The following sections define the Reset registers.

#### **Reset Status Register**

The Reset Status (RSTSTAT) Register, shown in Table 12, is a read-only register that indicates the source of the most recent Reset event, Stop Mode Recovery event or Watchdog Timer time-out event. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer Control Register, which is write-only.

#### Port A-D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the Port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high-output current drive operation. The Port A–D High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit     | 7         | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Field   | PHDE7     | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET   | 0         | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W       | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | If 04H ir | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |

| Bit        | Description                                                       |  |  |  |  |  |

|------------|-------------------------------------------------------------------|--|--|--|--|--|

| [7:0]      | Port High Drive Enable                                            |  |  |  |  |  |

| PHDEx      | 0 = The port pin is configured for standard output current drive. |  |  |  |  |  |

|            | 1 = The port pin is configured for high output current drive.     |  |  |  |  |  |

| Note: x ir | Note: x indicates the specific GPIO port pin number (7–0).        |  |  |  |  |  |

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the timer input signal. No interrupt is generated by the first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{\text{(Capture Value - Start Value)} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on Timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the timer low byte register are placed in a holding register. A subsequent read from the timer low byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value when enabled. When the timers are not enabled, a read from the timer low byte register returns the actual value in the counter.

### **Timer Pin Signal Operation**

Timer output is a GPIO port pin alternate function. The timer output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO alternate function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT Mode. For this mode, no timer input is available.

PS025113-1212 Operation

### Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 54 and 55, control PWM operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

| Bit     | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|------|-----|-----|-----|-----|-----|-----|

| Field   |            | PWMH |     |     |     |     |     |     |

| RESET   | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F04H, F0CH |      |     |     |     |     |     |     |

Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   |     | PWML       |     |     |     |     |     |     |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F05H, F0DH |     |     |     |     |     |     |

| Bit           | Description                                                                                                                                                                                                                                                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]         | Pulse Width Modulator High and Low Bytes                                                                                                                                                                                                                                                                                                         |

| PWMH,<br>PWML | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1).  The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operat- |

|               | ing in capture or CAPTURE/COMPARE modes.                                                                                                                                                                                                                                                                                                         |

### Flash Control Register

The Flash Controller must be unlocked using the Flash Control Register before programming or erasing Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, Flash memory can be enabled for mass erase or page erase by writing the appropriate enable command to the FCTL. Page erase applies only to the active page selected in Flash Page Select Register. Mass erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its Locked state. The write-only Flash Control Register shares its register file address with the read-only Flash Status Register.

Table 72. Flash Control Register (FCTL)

| Bit     | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|------|---|---|---|---|---|---|

| Field   |   | FCMD |   |   |   |   |   |   |

| RESET   | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W     | W | W    | W | W | W | W | W | W |

| Address |   | FF8H |   |   |   |   |   |   |

| Bit   | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| [7:0] | Flash Command                                                                        |

| FCMD  | 73H = First unlock command.                                                          |

|       | 8CH = Second unlock command.                                                         |

|       | 95H = Page erase command (must be third command in sequence to initiate page erase). |

|       | 63H = Mass erase command (must be third command in sequence to initiate mass erase). |

|       | 5EH = Enable Flash Sector Protect Register access.                                   |

## On-Chip Debugger

The Z8 Encore! devices contain an integrated On-Chip Debugger (OCD) that provides the following advanced debugging features:

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

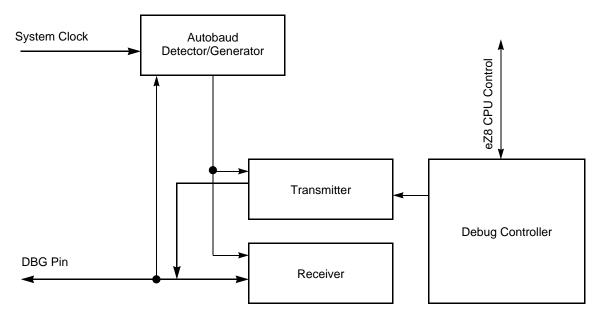

#### **Architecture**

The On-Chip Debugger consists of four primary functional blocks: transmitter, receiver, autobaud detector/generator and debug controller. Figure 20 displays the architecture of the On-Chip Debugger.

Figure 20. On-Chip Debugger Block Diagram

PS025113-1212 On-Chip Debugger

```

DBG ← 0AH

DBG ← Program Memory Address[15:8]

DBG ← Program Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG ← 1-65536 data bytes

```

**Read Program Memory (0BH).** The read program memory command, reads data from program memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFH for the data.

```

DBG ← 0BH

DBG ← Program Memory Address[15:8]

DBG ← Program Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG → 1-65536 data bytes

```

Write Data Memory (0CH). The write data memory command, writes data to data memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG Mode or if the flash read protect option bit is enabled, the data is discarded.

```

DBG 		OCH

DBG 		Data Memory Address[15:8]

DBG 		Data Memory Address[7:0]

DBG 		Size[15:8]

DBG 		Size[7:0]

DBG 		T-65536 data bytes

```

**Read Data Memory (0DH).** The read data memory command, reads from data memory. This command is equivalent to the LDE and LDEI instructions. Data can be read from 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG ← 0DH

DBG ← Data Memory Address[15:8]

DBG ← Data Memory Address[7:0]

DBG ← Size[15:8]

DBG ← Size[7:0]

DBG → 1-65536 data bytes

```

Read Program Memory CRC (0EH). The read program memory CRC command, computes and returns the cyclic redundancy check (CRC) of program memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike the other OCD read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads program memory, calculates the CRC value and returns the result. The delay is a function of program mem-

### **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

Table 97. OCD Status Register (OCDSTAT)

| Bit   | 7   | 6    | 5      | 4 | 3 | 2        | 1 | 0 |

|-------|-----|------|--------|---|---|----------|---|---|

| Field | DBG | HALT | FRPENB |   |   | Reserved |   |   |

| RESET | 0   | 0    | 0      | 0 | 0 | 0        | 0 | 0 |

| R/W   | R   | R    | R      | R | R | R        | R | R |

| Bit           | Description                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status 0 = NORMAL Mode. 1 = DEBUG Mode.                                                                                      |

| [6]<br>HALT   | HALT Mode  0 = Not in HALT Mode.  1 = In HALT Mode.                                                                                |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable  0 = FRP bit enabled, that allows disabling of many OCD commands.  1 = FRP bit has no effect. |

| [4:0]         | Reserved These bits are reserved and must be programmed to 00000.                                                                  |

### **Oscillator Control**

The Z8 Encore! F0830 Series device uses five possible clocking schemes. Each one of these is user-selectable.

- On-chip precision trimmed RC oscillator

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low precision Watchdog Timer Oscillator

In addition, Z8 Encore! F0830 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

### **Operation**

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined further in this document.

### **System Clock Selection**

The oscillator control block selects from the available clocks. *Table 98* describes each clock source and its usage.

PS025113-1212 Oscillator Control

Figure 24. Oscillator Control Clock Switching Flow Chart

## Crystal Oscillator

The products in the Z8 Encore! F0830 Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of its on-chip peripherals. Alternatively, the  $X_{\rm IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{\rm OUT}$  pin must remain unconnected. The on-chip crystal oscillator also contains a clock filter function. To see the settings for this clock filter, see Table 90 on page 133. By default, however, this clock filter is disabled; therefore, no divide to the input clock (namely, the frequency of the signal on the  $X_{\rm IN}$  input pin) can determine the frequency of the system clock when using the default settings.

Note:

Although the  $X_{IN}$  pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use. See *the* System Clock Selection section on page 151 for more information.

### **Operating Modes**

The Z8 Encore! F0830 Series products support the following four OSCILLATOR Modes:

- Minimum power for use with very low frequency crystals (32kHz to 1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8 MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The OSCILLATOR Mode is selected using user-programmable Flash option bits. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

### **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Reg-

PS025113-1212 Crystal Oscillator

#### **Assembly Language Source Program Example**

; Everything after the semicolon is a comment. JP START START: ; A label called "START". The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs. ; A Load (LD) instruction with two operands. The first operand, LD R4, R7 : Working register R4, is the destination. The second operand. ; Working register R7, is the source. The contents of R7 is ; written into R4. ; Another Load (LD) instruction with two operands. LD 234H, #%01 ; The first operand, extended mode register Address 234H, ; identifies the destination. The second operand, immediate data : value 01H, is the source. The value 01H is written into the ; register at address 234H.

### **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as *destination*, *source*. After assembly, the object code usually reflects the operands in the order *source*, *destination*, but ordering is op code-dependent.

The following examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

#### Example 1

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 101. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, | src) |

|------------------------|-----|------|-----|-----------|------|

| Object Code            | 04  | 08   | 43  | (OPC src, | dst) |

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

#### **eZ8 CPU Instruction Classes**

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit manipulation

- Block transfer

- CPU control

- Load

- Logical

- Program control

- Rotate and shift

Tables 105 through 112 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instructions can be considered as a subset of more than one category. Within these tables, the source operand is identified as *src*, the destination operand is *dst* and a condition code is *cc*.

**Table 105. Arithmetic Instructions**

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| СРХ      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

## **Ordering Information**

Order your F0830 Series products from Zilog using the part numbers shown in Table 128. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

| Part Number                                  | Flash         | RAM   | NVDS | ADC Channels | Description |  |  |

|----------------------------------------------|---------------|-------|------|--------------|-------------|--|--|

| Z8 Encore! F0830 Series MCUs with 12KB Flash |               |       |      |              |             |  |  |

| Standard Temperatur                          | e: 0°C to 70° | ,C    |      |              |             |  |  |

| Z8F1232SH020SG                               | 12KB          | 256   | No   | 7            | SOIC 20-pin |  |  |

| Z8F1232HH020SG                               | 12KB          | 256   | No   | 7            | SSOP 20-pin |  |  |

| Z8F1232PH020SG                               | 12KB          | 256   | No   | 7            | PDIP 20-pin |  |  |

| Z8F1232QH020SG                               | 12KB          | 256   | No   | 7            | QFN 20-pin  |  |  |

| Z8F1233SH020SG                               | 12KB          | 256   | No   | 0            | SOIC 20-pin |  |  |

| Z8F1233HH020SG                               | 12KB          | 256   | No   | 0            | SSOP 20-pin |  |  |

| Z8F1233PH020SG                               | 12KB          | 256   | No   | 0            | PDIP 20-pin |  |  |

| Z8F1233QH020SG                               | 12KB          | 256   | No   | 0            | QFN 20-pin  |  |  |

| Z8F1232SJ020SG                               | 12KB          | 256   | No   | 8            | SOIC 28-pin |  |  |

| Z8F1232HJ020SG                               | 12KB          | 256   | No   | 8            | SSOP 28-pin |  |  |

| Z8F1232PJ020SG                               | 12KB          | 256   | No   | 8            | PDIP 28-pin |  |  |

| Z8F1232QJ020SG                               | 12KB          | 256   | No   | 8            | QFN 28-pin  |  |  |

| Z8F1233SJ020SG                               | 12KB          | 256   | No   | 0            | SOIC 28-pin |  |  |

| Z8F1233HJ020SG                               | 12KB          | 256   | No   | 0            | SSOP 28-pin |  |  |

| Z8F1233PJ020SG                               | 12KB          | 256   | No   | 0            | PDIP 28-pin |  |  |

| Z8F1233QJ020SG                               | 12KB          | 256   | No   | 0            | QFN 28-pin  |  |  |

| Extended Temperatur                          | re: -40°C to  | 105°C |      |              |             |  |  |

| Z8F1232SH020EG                               | 12KB          | 256   | No   | 7            | SOIC 20-pin |  |  |

| Z8F1232HH020EG                               | 12KB          | 256   | No   | 7            | SSOP 20-pin |  |  |

| Z8F1232PH020EG                               | 12KB          | 256   | No   | 7            | PDIP 20-pin |  |  |

| Z8F1232QH020EG                               | 12KB          | 256   | No   | 7            | QFN 20-pin  |  |  |

| Z8F1233SH020EG                               | 12KB          | 256   | No   | 0            | SOIC 20-pin |  |  |

| Z8F1233HH020EG                               | 12KB          | 256   | No   | 0            | SSOP 20-pin |  |  |

| Z8F1233PH020EG                               | 12KB          | 256   | No   | 0            | PDIP 20-pin |  |  |

|                                              |               |       |      |              |             |  |  |

PS025113-1212 Ordering Information

**Hex Address: F01**

Table 131. Timer 0 Low Byte Register (T0L)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   |      | TL  |     |     |     |     |     |     |

| RESET   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F01H |     |     |     |     |     |     |     |

**Hex Address: F02**

Table 132. Timer 0 Reload High Byte Register (T0RH)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TRH  |     |     |     |     |     |     |     |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F02H |     |     |     |     |     |     |     |

**Hex Address: F03**

Table 133. Timer 0 Reload Low Byte Register (T0RL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TRL  |     |     |     |     |     |     |     |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F03H |     |     |     |     |     |     |     |

Hex Address: F04

Table 134. Timer 0 PWM High Byte Register (T0PWMH)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PWMH |     |     |     |     |     |     |     |

| RESET   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F04H |     |     |     |     |     |     |     |

PS025113-1212 Timer 0

## Index

| Symbols                                     | В                                                            |

|---------------------------------------------|--------------------------------------------------------------|

| @ 165                                       | B 165                                                        |

| # 165                                       | b 164                                                        |

| % 165                                       | BCLR 167                                                     |

|                                             | binary number suffix 165                                     |

|                                             | BIT 167                                                      |

| Numerics                                    | bit 164                                                      |

| 10-bit ADC 4                                | clear 167                                                    |

|                                             | manipulation instructions 167                                |

|                                             | set 167                                                      |

| A                                           | set or clear 167                                             |

| absolute maximum ratings 184                | swap 167                                                     |

| AC characteristics 189                      | test and jump 169                                            |

| ADC 166                                     | test and jump if non-zero 169                                |

| block diagram 99                            | test and jump if zero 169                                    |

| overview 98                                 | bit jump and test if non-zero 166                            |

| ADC Channel Register 1 (ADCCTL) 102         | bit swap 169                                                 |

| ADC Data High Byte Register (ADCDH) 103     | block diagram 3                                              |

| ADC Data Low Bit Register (ADCDL) 103, 104, | block transfer instructions 167                              |

| 105                                         | BRK 169                                                      |

| ADCX 166                                    | BSET 167                                                     |

| ADD 166                                     | BSWAP 167, 169                                               |

| add - extended addressing 166               | BTJ 169<br>DTINZ 166 160                                     |

| add with carry 166                          | BTJNZ 166, 169<br>BTJZ 169                                   |

| add with carry - extended addressing 166    | D13Z 109                                                     |

| additional symbols 165                      |                                                              |

| address space 14                            | С                                                            |

| ADDX 166                                    |                                                              |

| analog block/PWM signal synchronization 100 | calibration and compensation, motor control measurements 101 |

| analog block/PWM signal zynchronization 100 | CALL procedure 169                                           |

| analog signals 11                           | capture mode 89, 90                                          |

| analog-to-digital converter<br>overview 98  | capture/compare mode 89                                      |

| AND 169                                     | cc 164                                                       |

| ANDX 169                                    | CCF 168                                                      |

| architecture                                | characteristics, electrical 184                              |

| voltage measurements 98                     | clear 168                                                    |

| arithmetic instructions 166                 | CLR 168                                                      |

| assembly language programming 162           | COM 169                                                      |

| assembly language syntax 163                | compare 89                                                   |

| , , ,                                       |                                                              |

| page select register 121, 122                                                 | indexed 165                        |

|-------------------------------------------------------------------------------|------------------------------------|

| FPS register 121, 122                                                         | indirect address prefix 165        |

| FSTAT register 120                                                            | indirect register 164              |

| •                                                                             | indirect register pair 164         |

|                                                                               | indirect working register 164      |

| G                                                                             | indirect working register pair 164 |

| gated mode 89                                                                 | instruction set, ez8 CPU 162       |

| general-purpose I/O 33                                                        | instructions                       |

| GPIO 4, 33                                                                    | ADC 166                            |

| alternate functions 34                                                        | ADCX 166                           |

| architecture 34                                                               | ADD 166                            |

| control register definitions 39                                               | ADDX 166                           |

| input data sample timing 195                                                  | AND 169                            |

| interrupts 39                                                                 | ANDX 169                           |

| port A-C pull-up enable sub-registers 46, 47, 48                              | arithmetic 166                     |

| port A-H address registers 40                                                 | BCLR 167                           |

| port A-H address registers 40<br>port A-H alternate function sub-registers 42 | BIT 167                            |

| port A-H control registers 41                                                 | bit manipulation 167               |

| port A-H data direction sub-registers 41                                      | block transfer 167                 |

| port A-H high drive enable sub-registers 44                                   | BRK 169                            |

| port A-H input data registers 49                                              | BSET 167                           |

| port A-H output control sub-registers 43                                      | BSWAP 167, 169                     |

| port A-H output data registers 50, 51                                         | BTJ 169                            |

| port A-H stop mode recovery sub-registers 45                                  | BTJNZ 166, 169                     |

| port availability by device 33                                                | BTJZ 169                           |

| port input timing 195                                                         | CALL 169                           |

| port output timing 196                                                        | CCF 167, 168                       |

| port output timing 170                                                        | CLR 168                            |

|                                                                               | COM 169                            |

| Н                                                                             | CP 166                             |

| H 165                                                                         | CPC 166                            |

| HALT 168                                                                      | CPCX 166                           |

| halt mode 31, 168                                                             | CPU control 168                    |

| hexadecimal number prefix/suffix 165                                          | CPX 166                            |

| nexadecimal number prenty/surnx 103                                           | DA 166                             |

|                                                                               | DEC 166                            |

| 1                                                                             | DECW 166                           |

| IM 164                                                                        | DI 168                             |

| IM 164                                                                        | DJNZ 169                           |

| immediate data 164                                                            | EI 168                             |

| immediate operand prefix 165                                                  | HALT 168                           |

| INC 166 increment 166                                                         | INC 166                            |

|                                                                               | INCW 167                           |

| increment word 167<br>INCW 167                                                | IRET 169                           |

| INCW 10/                                                                      |                                    |