Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 12KB (12K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-VQFN                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1233qj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Tables

| Table 1.  | Z8 Encore! F0830 Series Family Part Selection Guide 2              |

|-----------|--------------------------------------------------------------------|

| Table 2.  | Acronyms and Expansions                                            |

| Table 3.  | Z8 Encore! F0830 Series Package Options 7                          |

| Table 4.  | Signal Descriptions                                                |

| Table 5.  | Pin Characteristics (20- and 28-pin Devices) 13                    |

| Table 6.  | Z8 Encore! F0830 Series Program Memory Maps 15                     |

| Table 7.  | Z8 Encore! F0830 Series Flash Memory Information Area Map 16       |

| Table 8.  | Register File Address Map 17                                       |

| Table 9.  | Reset and Stop Mode Recovery Characteristics and Latency 22        |

| Table 10. | Reset Sources and Resulting Reset Type                             |

| Table 11. | Stop Mode Recovery Sources and Resulting Action 27                 |

| Table 12. | POR Indicator Values                                               |

| Table 13. | Reset Status Register (RSTSTAT)                                    |

| Table 14. | Power Control Register 0 (PWRCTL0)                                 |

| Table 15. | Port Availability by Device and Package Type                       |

| Table 16. | Port Alternate Function Mapping                                    |

| Table 17. | GPIO Port Registers and Subregisters                               |

| Table 18. | Port A-D GPIO Address Registers (PxADDR) 40                        |

| Table 19. | Port Control Subregister Access                                    |

| Table 20. | Port A–D Control Registers (PxCTL)                                 |

| Table 21. | Port A–D Data Direction Subregisters (PxDD) 41                     |

| Table 22. | Port A–D Alternate Function Subregisters (PxAF)                    |

| Table 23. | Port A–D Output Control Subregisters (PxOC)                        |

| Table 24. | Port A–D High Drive Enable Subregisters (PxHDE)                    |

| Table 25. | Port A–D Stop Mode Recovery Source Enable Subregisters (PxSMRE) 45 |

| Table 26. | Port A–D Pull-Up Enable Subregisters (PxPUE)                       |

| Table 27. | Port A–D Alternate Function Set 1 Subregisters (PxAFS1) 47         |

| Table 28. | Port A–D Alternate Function Set 2 Subregisters (PxAFS2)            |

# **Program Memory**

The eZ8 CPU supports 64KB of program memory address space. The Z8 Encore! F0830 Series devices contain 1KB to 12KB of on-chip Flash memory in the program memory address space, depending on the device. Reading from program memory addresses outside the available Flash memory address range returns FFH. Writing to these unimplemented program memory addresses produces no effect. Table 6 shows a program memory map for the Z8 Encore! F0830 Series products.

|                                             | 0 , 1                      |

|---------------------------------------------|----------------------------|

| Program Memory Address (Hex)                | Function                   |

| Z8F0830 and Z8F0831 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-1FFF                                   | Program Memory             |

| Z8F0430 and Z8F0431 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-0FFF                                   | Program Memory             |

| Z8F0130 and Z8F0131 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-03FF                                   | Program Memory             |

| Z8F0230 and Z8F0231 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-07FF                                   | Program Memory             |

| Note: *See <u>Table 34</u> on page 54 for a | list of interrupt vectors. |

| Table 6 | . Z8 | Encore! | F0830 | Series | Program | Memory Ma | ips |

|---------|------|---------|-------|--------|---------|-----------|-----|

|---------|------|---------|-------|--------|---------|-----------|-----|

# **Data Memory**

The Z8 Encore! F0830 Series does not use the eZ8 CPU's 64KB data memory address space.

# **Flash Information Area**

Table 7 maps the Z8 Encore! F0830 Series Flash information area. The 128-byte information area is accessed, by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash information area is mapped into program memory and overlays these 128 bytes at addresses FE00H to FE7FH. When information area access is enabled, all reads from these program memory addresses return information area data rather than program memory data. Access to the Flash information area is read-only.

| Program<br>Memory<br>Address (Hex) | Function                                                                                 |

|------------------------------------|------------------------------------------------------------------------------------------|

| FE00–FE3F                          | Zilog option bits                                                                        |

| FE40-FE53                          | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH |

| FE54–FE5F                          | Reserved                                                                                 |

| FE60–FE7F                          | Reserved                                                                                 |

| FE80–FFFF                          | Reserved                                                                                 |

#### Table 7. Z8 Encore! F0830 Series Flash Memory Information Area Map

|                  | _                          |          | -           |          |

|------------------|----------------------------|----------|-------------|----------|

| Address (Hex)    | Register Description       | Mnemonic | Reset (Hex) | Page No. |

| Analog-to-Digita | al Converter (ADC, cont'd) |          |             |          |

| F73              | ADC data low bits          | ADCD_L   | XX          | 103      |

| F74              | ADC sample settling time   | ADCSST   | 0F          | 104      |

| F75              | ADC sample time            | ADCST    | 3F          | 105      |

| F76              | Reserved                   | —        | XX          |          |

| F77–F7F          | Reserved                   | —        | XX          |          |

| Low Power Con    | trol                       |          |             |          |

| F80              | Power control 0            | PWRCTL0  | 88          | 32       |

| F81              | Reserved                   | _        | XX          |          |

| LED Controller   |                            |          |             |          |

| F82              | LED drive enable           | LEDEN    | 00          | 51       |

| F83              | LED drive level high       | LEDLVLH  | 00          | 51       |

| F84              | LED drive level low        | LEDLVLL  | 00          | 52       |

| F85              | Reserved                   | _        | XX          |          |

| Oscillator Contr | ol                         |          |             |          |

| F86              | Oscillator control         | OSCCTL   | A0          | 154      |

| F87–F8F          | Reserved                   | —        | XX          |          |

| Comparator 0     |                            |          |             |          |

| F90              | Comparator 0 control       | CMP0     | 14          | 107      |

| F91–FBF          | Reserved                   | _        | XX          |          |

| Interrupt Contro | bller                      |          |             |          |

| FC0              | Interrupt request 0        | IRQ0     | 00          | 58       |

| FC1              | IRQ0 enable high bit       | IRQ0ENH  | 00          | 61       |

| FC2              | IRQ0 enable low Bit        | IRQ0ENL  | 00          | 61       |

| FC3              | Interrupt request 1        | IRQ1     | 00          | 59       |

| FC4              | IRQ1 enable high bit       | IRQ1ENH  | 00          | 62       |

| FC5              | IRQ1 enable low bit        | IRQ1ENL  | 00          | 63       |

| FC6              | Interrupt request 2        | IRQ2     | 00          | 60       |

| FC7              | IRQ2 enable high bit       | IRQ2ENH  | 00          | 64       |

| FC8              | IRQ2 enable low bit        | IRQ2ENL  | 00          | 64       |

| FC9–FCC          | Reserved                   | —        | XX          |          |

| FCD              | Interrupt edge select      | IRQES    | 00          | 66       |

### Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

clock and reset signals, the required reset duration may be three or four clock periods. A reset pulse of three clock cycles in duration might trigger a reset and a reset pulse of four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted low, the Z8 Encore! F0830 Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held low beyond the system reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a system reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

## **External Reset Indicator**

During system reset or when enabled by the GPIO logic, the RESET pin functions as an open-drain (active low) RESET mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! F0830 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events. See the <u>Port A–D Control Registers</u> section on page 41.

After an internal Reset event occurs, the internal circuitry begins driving the RESET pin low. The  $\overrightarrow{\text{RESET}}$  pin is held low by the internal circuitry until the appropriate delay listed in <u>Table 9</u> (see page 22) has elapsed.

## **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset, but the remainder of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

## Stop Mode Recovery

The device enters the STOP Mode when the STOP instruction is executed by the eZ8 CPU. See the <u>Low-Power Modes</u> chapter on page 30 for detailed STOP Mode information. During Stop Mode Recovery, the CPU is held in reset for about 66 IPO cycles if the crystal oscillator is disabled or about 5000 cycles if it is enabled.

Stop Mode Recovery does not affect the on-chip registers other than the Reset Status (RSTSTAT) Register and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for Alternate function CLKIN. Write to the Oscillator Control Register (see the <u>Oscillator Control Register Definitions</u> section on page 154) to select the PB3 as the system clock.

| Port                | Pin | Mnemonic   | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1</sup> | PA0 | T0IN/T0OUT | Timer 0 input/Timer 0 output complement | N/A                                     |

|                     |     | Reserved   |                                         |                                         |

|                     | PA1 | TOOUT      | Timer 0 output                          |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA2 | Reserved   | Reserved                                |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA3 | Reserved   | Reserved                                |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA4 | Reserved   | Reserved                                |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA5 | Reserved   | Reserved                                |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA6 | T1IN/T1OUT | Timer 1 input/Timer 1 output complement |                                         |

|                     |     | Reserved   |                                         |                                         |

|                     | PA7 | T1OUT      | Timer 1 output                          |                                         |

|                     |     | Reserved   |                                         |                                         |

#### Table 16. Port Alternate Function Mapping

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

### Port A–D Pull-up Enable Subregisters

The Port A–D Pull-Up Enable Subregister is accessed through the Port A–D Control Register by writing 06H to the Port A–D Address Register. See Table 26. Setting the bits in the Port A–D Pull-Up Enable subregisters enables a weak internal resistive pull-up on the specified port pins.

| Bit     | 1                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | PPUE7                                                                                 | PPUE6 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |       |  |

#### Table 26. Port A–D Pull-Up Enable Subregisters (PxPUE)

| Bit       | Description                                       |

|-----------|---------------------------------------------------|

| [7:0]     | Port Pull-Up Enable                               |

| PxPUE     | 0 = The weak pull-up on the port pin is disabled. |

|           | 1 = The weak pull-up on the port pin is enabled.  |

| Note: x i | ndicates the specific GPIO port pin number (7–0). |

### Table 39. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit     | 7        | 6     | 5     | 4   | 3        | 2   | 1   | 0   |  |  |

|---------|----------|-------|-------|-----|----------|-----|-----|-----|--|--|

| Field   | Reserved | T1ENH | T0ENH |     | Reserved |     |     |     |  |  |

| RESET   | 0        | 0     | 0     | 0   | 0        | 0   | 0   | 0   |  |  |

| R/W     | R/W      | R/W   | R/W   | R/W | R/W      | R/W | R/W | R/W |  |  |

| Address |          | FC1H  |       |     |          |     |     |     |  |  |

| Bit           | Description                                                          |

|---------------|----------------------------------------------------------------------|

| [7]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 0. |

| [6]<br>T1ENH  | Timer 1 Interrupt Request Enable High Bit                            |

| [5]<br>T0ENH  | Timer 0 Interrupt Request Enable High Bit                            |

| [4:1]         | Reserved                                                             |

|               | These registers are reserved and must be programmed to 0000.         |

| [0]<br>ADCENH | ADC Interrupt Request Enable High Bit                                |

#### Table 40. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5     | 4   | 3        | 2 | 1 | 0   |  |

|---------|----------|-------|-------|-----|----------|---|---|-----|--|

| Field   | Reserved | T1ENL | T0ENL |     | Reserved |   |   |     |  |

| RESET   | 0        | 0     | 0     | 0   | 0        | 0 | 0 | 0   |  |

| R/W     | R        | R/W   | R/W   | R/W | R/W      | R | R | R/W |  |

| Address | FC2H     |       |       |     |          |   |   |     |  |

| Bit           | Description                                                                     |

|---------------|---------------------------------------------------------------------------------|

| [7]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.            |

| [6]<br>T1ENL  | Timer 1 Interrupt Request Enable Low Bit                                        |

| [5]<br>T0ENL  | Timer 0 Interrupt Request Enable Low Bit                                        |

| [4:1]         | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                                            |

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines whether the capture occurs on a rising edge or a falling edge of the timer input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt has been caused by an input capture event.

If no capture event occurs, the timer counts up to 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

## **ADC Interrupt**

The ADC can generate an interrupt request when a conversion has been completed. An interrupt request that is pending when the ADC is disabled is not cleared automatically.

## **Reference Buffer**

The reference buffer, RBUF, supplies the reference voltage for the ADC. When enabled, the internal voltage reference generator supplies the ADC. When RBUF is disabled, the ADC must have the reference voltage supplied externally through the  $V_{REF}$  pin in 28-pin package. RBUF is controlled by the REFEN bit in the ADC Control Register.

## **Internal Voltage Reference Generator**

The internal voltage reference generator provides the voltage VR2, for the RBUF. VR2 is 2V.

## **Calibration and Compensation**

A user can perform calibration and store the values into Flash or the user code can perform a manual offset calibration. There is no provision for manual gain calibration.

# **ADC Control Register Definitions**

The ADC Control registers are defined in this section.

# Flash Memory

The products in the Z8 Encore! F0830 Series features either 1KB (1024 bytes with NVDS), 2KB (2048 bytes with NVDS), 4KB (4096 bytes with NVDS), 8KB (8192 bytes with NVDS) or 12KB (12288 bytes with no NVDS) of nonvolatile Flash memory with read/write/erase capability. Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F0830 Series, each sector maps to one page (for 1KB, 2KB and 4KB devices), two pages (8KB device) or three pages (12KB device).

The first two bytes of Flash program memory is used as Flash option bits. For more information, see *the* <u>Flash Option Bits</u> chapter on page 124.

Table 69 lists the Flash memory configuration for each device in the Z8 Encore! F0830 Series. Figures 14 through 18 display the memory arrangements for each Flash memory size.

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F123x     | 12 (12,288)              | 24          | 0000H–2FFFH                    | 1536                         |

| Z8F083x     | 8 (8196)                 | 16          | 0000H-1FFFH                    | 1024                         |

| Z8F043x     | 4 (4096)                 | 8           | 0000H–0FFFH                    | 512                          |

| Z8F023x     | 2 (2048)                 | 4           | 0000H–07FFH                    | 512                          |

| Z8F013x     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

Figure 14. 1K Flash with NVDS

<sup>03</sup>FFH

03FFH

03FFH

0200H

Sector 1

Page 1

0200H

01FFH

Sector 0

Page 0

01FFH

0000H

0000H

0000H

0000H

## **Page Erase**

Flash memory can be erased one page (512 bytes) at a time. Page erasing Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the page erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the page erase is complete, the Flash Controller returns to its Locked state.

## **Mass Erase**

Flash memory can also be mass erased using the Flash Controller, but only by using the On-Chip Debugger. Mass erasing Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the mass erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the mass erase is complete, the Flash Controller returns to its Locked state.

## **Flash Controller Bypass**

The Flash Controller can be bypassed; instead, the control signals for Flash memory can be brought out to the GPIO pins. Bypassing the Flash Controller allows faster row programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of Flash memory. Mass Erase and Page Erase operations are also supported, when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to *Third-Party Flash Programming Support for Z8 Encore!*. This document is available for download at <u>www.zilog.com</u>.

## Flash Controller Behavior in Debug Mode

The following behavioral changes can be observed in the Flash Controller when the Flash Controller is accessed using the On-Chip Debugger:

• The Flash write protect option bit is ignored.

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>XTLDIS | <ul> <li>State of the Crystal Oscillator at Reset</li> <li>This bit enables only the crystal oscillator. Selecting the crystal oscillator as the system clock must be performed manually.</li> <li>0 = The crystal oscillator is enabled during reset, resulting in longer reset timing.</li> <li>1 = The crystal oscillator is disabled during reset, resulting in shorter reset timing.</li> </ul> |

| [3:0]         | <b>Reserved</b> These bits are reserved and must be programmed to 1111.                                                                                                                                                                                                                                                                                                                              |

# **Trim Bit Address Space**

All available trim bit addresses and their functions are listed in Tables 83 through 90.

Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

2. Use as few unique addresses as possible to optimize the impact of refreshing.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

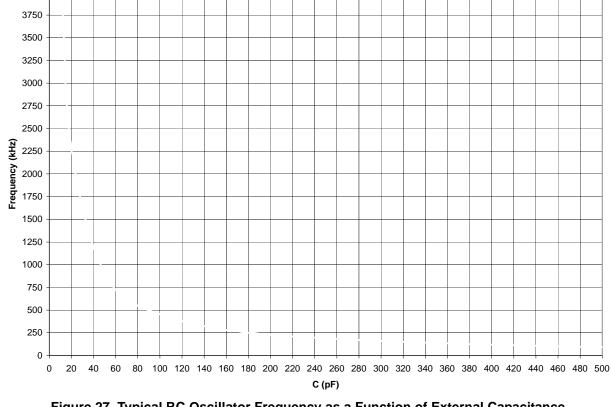

Figure 27. Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$  Resistor

**Caution:** When using the external RC OSCILLATOR Mode, the oscillator can stop oscillating if the power supply drops below 2.7V but before it drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7V.

160

4000

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

## eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit manipulation

- Block transfer

- CPU control

- Load

- Logical

- Program control

- Rotate and shift

Tables 105 through 112 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instructions can be considered as a subset of more than one category. Within these tables, the source operand is identified as *src*, the destination operand is *dst* and a condition code is *cc*.

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| CPX      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

### Table 105. Arithmetic Instructions (Continued)

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### Table 106. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                             |

|----------|-------------|---------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                               |

| BIT      | p, bit, dst | Bit Set or Clear                                        |

| BSET     | bit, dst    | Bit Set                                                 |

| BSWAP    | dst         | Bit Swap                                                |

| CCF      | —           | Complement Carry Flag                                   |

| RCF      | —           | Reset Carry Flag                                        |

| SCF      | —           | Set Carry Flag                                          |

| ТСМ      | dst, src    | Test Complement Under Mask                              |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended<br>Addressing |

| ТМ       | dst, src    | Test Under Mask                                         |

| TMX      | dst, src    | Test Under Mask using Extended Addressing               |

#### Table 107. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

|                   |                              | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = -40°C to +105°C |                  |      |       |                                   |

|-------------------|------------------------------|-------------------------------|-----|-----|----------------------------------|------------------|------|-------|-----------------------------------|

| Symbol            | Parameter                    | Min                           | Тур | Мах | Min                              | Тур              | Max  | Units | Conditions                        |

| I <sub>LED</sub>  | Controlled<br>Current Drive  |                               |     |     | 1.5                              | 3                | 4.5  | mA    | See GPIO section on               |

|                   |                              |                               |     |     | 2.8                              | 7                | 10.5 | mA    | LED description                   |

|                   |                              |                               |     |     | 7.8                              | 13               | 19.5 | mA    | -                                 |

|                   |                              |                               |     |     | 12                               | 20               | 30   | mA    | -                                 |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance |                               |     |     | _                                | 8.0 <sup>2</sup> | _    | pF    | TBD                               |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance       |                               |     |     | -                                | 8.0 <sup>2</sup> | -    | pF    | TBD                               |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance      |                               |     |     | -                                | 9.5 <sup>2</sup> | -    | pF    | TBD                               |

| I <sub>PU</sub>   | Weak Pull-up<br>Current      |                               |     |     | 50                               | 120              | 220  | μA    | V <sub>DD</sub> = 2.7 - 3.6V      |

| ICCH <sup>3</sup> | Supply Current in HALT Mode  |                               |     |     |                                  | TBD              |      | mA    | TBD                               |

| ICCS              | Supply Current in STOP Mode  |                               |     | 2   |                                  |                  | 8    | μA    | Without Watchdog Timer<br>running |

#### Table 116. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

3. See Figure 31 for HALT Mode current.

186

| Part Number          | Flash      | RAM   | NVDS | ADC<br>Channels | Description                                    |

|----------------------|------------|-------|------|-----------------|------------------------------------------------|

| Z8F0131PJ020SG       | 1KB        | 256   | Yes  | 0               | PDIP 28-pin                                    |

| Z8F0131QJ020SG       | 1KB        | 256   | Yes  | 0               | QFN 28-pin                                     |

| Extended Temperature | : −40°C to | 105°C |      |                 |                                                |

| Z8F0130SH020EG       | 1KB        | 256   | Yes  | 7               | SOIC 20-pin                                    |

| Z8F0130HH020EG       | 1KB        | 256   | Yes  | 7               | SSOP 20-pin                                    |

| Z8F0130PH020EG       | 1KB        | 256   | Yes  | 7               | PDIP 20-pin                                    |

| Z8F0130QH020EG       | 1KB        | 256   | Yes  | 7               | QFN 20-pin                                     |

| Z8F0131SH020EG       | 1KB        | 256   | Yes  | 0               | SOIC 20-pin                                    |

| Z8F0131HH020EG       | 1KB        | 256   | Yes  | 0               | SSOP 20-pin                                    |

| Z8F0131PH020EG       | 1KB        | 256   | Yes  | 0               | PDIP 20-pin                                    |

| Z8F0131QH020EG       | 1KB        | 256   | Yes  | 0               | QFN 20-pin                                     |

| Z8F0130SJ020EG       | 1KB        | 256   | Yes  | 8               | SOIC 28-pin                                    |

| Z8F0130HJ020EG       | 1KB        | 256   | Yes  | 8               | SSOP 28-pin                                    |

| Z8F0130PJ020EG       | 1KB        | 256   | Yes  | 8               | PDIP 28-pin                                    |

| Z8F0130QJ020EG       | 1KB        | 256   | Yes  | 8               | QFN 28-pin                                     |

| Z8F0131SJ020EG       | 1KB        | 256   | Yes  | 0               | SOIC 28-pin                                    |

| Z8F0131HJ020EG       | 1KB        | 256   | Yes  | 0               | SSOP 28-pin                                    |

| Z8F0131PJ020EG       | 1KB        | 256   | Yes  | 0               | PDIP 28-pin                                    |

| Z8F0131QJ020EG       | 1KB        | 256   | Yes  | 0               | QFN 28-pin                                     |

| ZUSBSC00100ZACG      |            |       |      |                 | USB Smart Cable Accessory Kit                  |

| ZUSBOPTSC01ZACG      |            |       |      |                 | Opto-Isolated USB Smart Cable<br>Accessory Kit |

#### Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

## **Part Number Suffix Designations**

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0830SH020SG is an 8-bit 20MHz Flash MCU with 8KB Program Memory and equipped with ADC and NVDS in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.