# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 12KB (12K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1233sh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

## xi

| Figure 27. | Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$ Resistor |

|------------|-----------------------------------------------------------------------------------------------------|

| Figure 28. | Op Code Map Cell Description 180                                                                    |

| Figure 29. | First Op Code Map                                                                                   |

| Figure 30. | Second Op Code Map after 1FH 183                                                                    |

| Figure 31. | $I_{CC}$ Versus System Clock Frequency (HALT Mode) 187                                              |

| Figure 32. | I <sub>CC</sub> Versus System Clock Frequency (NORMAL Mode) 188                                     |

| Figure 33. | Port Input Sample Timing 195                                                                        |

| Figure 34. | GPIO Port Output Timing 196                                                                         |

| Figure 35. | On-Chip Debugger Timing 197                                                                         |

| Figure 36. | Flash Current Diagram                                                                               |

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| Table 59. | Watchdog Timer Control Register (WDTCTL)               |

|-----------|--------------------------------------------------------|

| Table 60. | Watchdog Timer Reload Upper Byte Register (WDTU)       |

| Table 61. | Watchdog Timer Reload High Byte Register (WDTH)        |

| Table 62. | Watchdog Timer Reload Low Byte Register (WDTL)         |

| Table 63. | ADC Control Register 0 (ADCCTL0) 102                   |

| Table 64. | ADC Data High Byte Register (ADCD_H) 103               |

| Table 65. | ADC Data Low Bits Register (ADCD_L) 103                |

| Table 66. | Sample Settling Time (ADCSST) 104                      |

| Table 67. | Sample Time (ADCST) 105                                |

| Table 68. | Comparator Control Register (CMP0) 107                 |

| Table 69. | Z8 Encore! F0830 Series Flash Memory Configuration 108 |

| Table 70. | Z8F083 Flash Memory Area Map 112                       |

| Table 71. | Flash Code Protection using the Flash Option Bits 115  |

| Table 72. | Flash Control Register (FCTL) 119                      |

| Table 73. | Flash Status Register (FSTAT) 120                      |

| Table 74. | Flash Page Select Register (FPS) 121                   |

| Table 75. | Flash Sector Protect Register (FPROT) 122              |

| Table 76. | Flash Frequency High Byte Register (FFREQH) 123        |

| Table 77. | Flash Frequency Low Byte Register (FFREQL) 123         |

| Table 78. | Trim Bit Address Register (TRMADR) 126                 |

| Table 79. | Trim Bit Address Map 126                               |

| Table 80. | Trim Bit Data Register (TRMDR) 127                     |

| Table 81. | Flash Option Bits at Program Memory Address 0000H 127  |

| Table 82. | Flash Options Bits at Program Memory Address 0001H 128 |

| Table 83. | Trim Option Bits at 0000H (ADCREF) 130                 |

| Table 84. | Trim Option Bits at 0001H (TADC_COMP) 130              |

| Table 85. | Trim Bit Address Space                                 |

| Table 86. | Trim Option Bits at 0002H (TIPO) 131                   |

| Table 87. | Trim Option Bits at 0003H (TVBO) 131                   |

| Table 88. | VBO Trim Definition                                    |

# **Program Memory**

The eZ8 CPU supports 64KB of program memory address space. The Z8 Encore! F0830 Series devices contain 1KB to 12KB of on-chip Flash memory in the program memory address space, depending on the device. Reading from program memory addresses outside the available Flash memory address range returns FFH. Writing to these unimplemented program memory addresses produces no effect. Table 6 shows a program memory map for the Z8 Encore! F0830 Series products.

|                                             | 0 , 1                      |  |  |  |  |

|---------------------------------------------|----------------------------|--|--|--|--|

| Program Memory Address (Hex)                | Function                   |  |  |  |  |

| Z8F0830 and Z8F0831 Products                |                            |  |  |  |  |

| 0000–0001                                   | Flash Option Bits          |  |  |  |  |

| 0002–0003                                   | Reset Vector               |  |  |  |  |

| 0004–003D                                   | Interrupt Vectors*         |  |  |  |  |

| 003E-1FFF                                   | Program Memory             |  |  |  |  |

| Z8F0430 and Z8F0431 Products                |                            |  |  |  |  |

| 0000–0001                                   | Flash Option Bits          |  |  |  |  |

| 0002–0003                                   | Reset Vector               |  |  |  |  |

| 0004–003D                                   | Interrupt Vectors*         |  |  |  |  |

| 003E-0FFF                                   | Program Memory             |  |  |  |  |

| Z8F0130 and Z8F0131 Products                |                            |  |  |  |  |

| 0000–0001                                   | Flash Option Bits          |  |  |  |  |

| 0002–0003                                   | Reset Vector               |  |  |  |  |

| 0004–003D                                   | Interrupt Vectors*         |  |  |  |  |

| 003E-03FF                                   | Program Memory             |  |  |  |  |

| Z8F0230 and Z8F0231 Products                |                            |  |  |  |  |

| 0000–0001                                   | Flash Option Bits          |  |  |  |  |

| 0002–0003                                   | Reset Vector               |  |  |  |  |

| 0004–003D                                   | Interrupt Vectors*         |  |  |  |  |

| 003E-07FF                                   | Program Memory             |  |  |  |  |

| Note: *See <u>Table 34</u> on page 54 for a | list of interrupt vectors. |  |  |  |  |

| Table 6 | . Z8 | Encore! | F0830 | Series | Program | Memory Ma | ips |

|---------|------|---------|-------|--------|---------|-----------|-----|

|---------|------|---------|-------|--------|---------|-----------|-----|

# Architecture

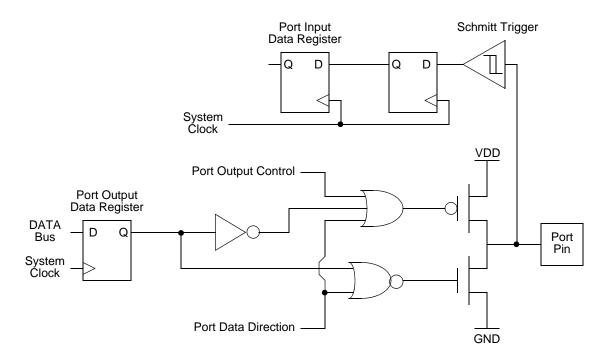

Figure 8 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

# **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general purpose input/output and access to onchip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function subregisters configure these pins for either GPIO or Alternate function operation. When a pin is configured for Alternate function, control of the port pin direction (input/output) is passed from the Port A–D data direction registers to the Alternate function assigned to this pin. <u>Table 16</u> on page 36 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, pins PA0 and PA1 functions as input and output for the crystal oscillator.

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# Architecture

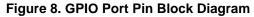

Figure 9 displays the Interrupt Controller block diagram.

Figure 9. Interrupt Controller Block Diagram

# Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 55

Interrupt Vectors and Priority: see page 56

Interrupt Assertion: see page 56

Software Interrupt Assertion: see page 57

# **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables the interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (enable interrupt) instruction

- Execution of an IRET (return from interrupt) instruction

| Bit                      | 7                                                    | 6                 | 5            | 4           | 3             | 2 1 0     |                |  |  |  |  |  |  |  |

|--------------------------|------------------------------------------------------|-------------------|--------------|-------------|---------------|-----------|----------------|--|--|--|--|--|--|--|

| Field                    | PA7ENL                                               | PA6CENL           | PA5ENL       | PA4ENL      | <b>PA3ENL</b> | PA2ENL    | L PA1ENL PA0EN |  |  |  |  |  |  |  |

| RESET                    | 0                                                    | 0 0 0 0 0 0 0 0 0 |              |             |               |           |                |  |  |  |  |  |  |  |

| R/W                      | R/W R/W R/W R/W R/W R/W R/W                          |                   |              |             |               |           |                |  |  |  |  |  |  |  |

| Address                  |                                                      | FC5H              |              |             |               |           |                |  |  |  |  |  |  |  |

| Bit                      | Descrip                                              | Description       |              |             |               |           |                |  |  |  |  |  |  |  |

| [7]<br>PA7ENL            | Port A E                                             | Bit[7] Interru    | ipt Request  | Enable Lo   | w Bit         |           |                |  |  |  |  |  |  |  |

| [6]<br>PA6CENL           | Port A E                                             | Bit[7] or Con     | nparator In  | terrupt Req | uest Enable   | e Low Bit |                |  |  |  |  |  |  |  |

| [5:0]<br>PA <i>x</i> ENL | [5:0] Port A Bit[x] Interrupt Request Enable Low Bit |                   |              |             |               |           |                |  |  |  |  |  |  |  |

| Note: x inc              | licates registe                                      | er bits in the a  | ddress range | e 5–0.      |               |           |                |  |  |  |  |  |  |  |

### Table 43. IRQ1 Enable Low Bit Register (IRQ1ENL)

## **IRQ2 Enable High and Low Bit Registers**

Table 44 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 45 and 46, form a priority-encoded enabling service for interrupts in the Interrupt Request 2 Register. Priority is generated by setting the bits in each register.

| IRQ2ENH[x]                                                  | IRQ2ENL[x] | Priority | Description |  |  |  |  |  |  |

|-------------------------------------------------------------|------------|----------|-------------|--|--|--|--|--|--|

| 0                                                           | 0          | Disabled | Disabled    |  |  |  |  |  |  |

| 0                                                           | 1          | Level 1  | Low         |  |  |  |  |  |  |

| 1                                                           | 0          | Level 2  | Nominal     |  |  |  |  |  |  |

| 1                                                           | 1          | Level 3  | High        |  |  |  |  |  |  |

| Note: $x$ indicates register bits in the address range 7–0. |            |          |             |  |  |  |  |  |  |

Table 44. IRQ2 Enable and Priority Encoding

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the timer PWM High and Low Byte registers to 0000H. This allows user software to determine if interrupts are generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt were generated by a reload.

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. The user can configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **COMPARE Mode**

In COMPARE Mode, the timer counts up to 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) upon compare.

If the timer reaches FFFFH, the timer resets to 0000H and continues counting.

Observe the following steps for configuring a timer for COMPARE Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

### Bit Description (Continued)

### [6] Timer Input/Output Polarity

TPOL Operation of this bit is a function of the current operating mode of the timer.

### **ONE-SHOT Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.

### **CONTINUOUS Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

### **COUNTER Mode**

If the timer is disabled, the timer output signal is set to the value of this bit. If the timer is enabled the timer output signal is complemented after timer reload.

- 0 = Count occurs on the rising edge of the timer input signal.

- 1 = Count occurs on the falling edge of the timer input signal.

#### PWM SINGLE OUTPUT Mode

- 0 = Timer output is forced Low (0), when the timer is disabled. The timer output is forced High (1) when the timer is enabled and the PWM count matches and the timer output is forced Low (0) when the timer is enabled and reloaded.

- 1 = Timer output is forced High (1), when the timer is disabled. The timer output is forced low(0), when the timer is enabled and the PWM count matches and forced High (1) when the timer is enabled and reloaded.

### CAPTURE Mode

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### COMPARE Mode

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

### GATED Mode

- 0 = Timer counts when the timer input signal is High (1) and interrupts are generated on the falling edge of the timer input.

- 1 = Timer counts when the timer input signal is Low (0) and interrupts are generated on the rising edge of the timer input.

### CAPTURE/COMPARE Mode

- 0 = Counting is started on the first rising edge of the timer input signal. The current count is captured on subsequent rising edges of the timer input signal.

- 1 = Counting is started on the first falling edge of the timer input signal. The current count is captured on subsequent falling edges of the timer input signal.

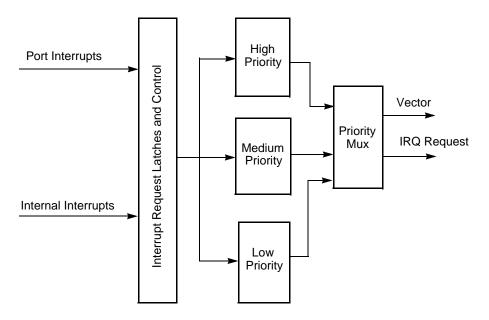

# **Analog-to-Digital Converter**

The Z8 Encore! MCU includes an eight-channel Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC). The ADC converts an analog input signal to a 10-bit binary number. The features of the SAR ADC include:

- Eight analog input sources multiplexed with general purpose I/O ports

- Fast conversion time, less than 11.9µs

- Programmable timing controls

- Interrupt on conversion complete

- Internal voltage reference generator

- Ability to select external reference voltage

- When configuring an ADC using external  $V_{\text{REF}}, \text{PB5}$  is used as  $V_{\text{REF}}$  in the 28-pin package

## Architecture

The ADC architecture, displayed in Figure 11, consists of an 8-input multiplexer, sampleand-hold amplifier and 10-bit SAR ADC. The ADC digitizes the signal on a selected channel and stores the digitized data in the ADC data registers. In an environment with high electrical noise, an external RC filter must be added at the input pins to reduce highfrequency noise.

$T_{CONV} = T_{S/H} + T_{CON}$  $T_{CONV} = T_S + T_H + 13 * SCLK * 16$

where:

$$\begin{split} & \text{SCLK} = \text{System Clock} \\ & \text{T}_{\text{CONV}} = \text{Total conversion time} \\ & \text{T}_{\text{S}} = \text{Sample time} (\text{SCLK} * \text{ADCST}) \\ & \text{T}_{\text{CON}} = \text{Conversion time} (13 * \text{SCLK} * 16) \\ & \text{T}_{\text{H}} = \text{Hold time} (\text{SCLK} * \text{ADCSST}) \\ & \text{DIV} = 16 (\text{fixed to divide by 16 for F0830 Series products}) \end{split}$$

**Example:** For an F0830 Series MCU running @ 20MHz:

$$\begin{split} T_{CONV} &= 1 \mu s + 0.5 \mu s + 13 * SCLK * DIV \\ T_{CONV} &= 1 \mu s + 0.5 \mu s + 13 * (1/20 \text{ MHz}) * 16 = 11.9 \mu s \end{split}$$

Figure 11. Analog-to-Digital Converter Block Diagram

# Operation

The ADC converts the analog input,  $ANA_X$ , to a 10-bit digital representation. The equation for calculating the digital value is represented by:

ADCOutput =  $1024 \times (ANA_x \div V_{REF})$

Assuming zero gain and offset errors, any voltage outside the ADC input limits of  $AV_{SS}$  and  $V_{REF}$  returns all 0s or 1s, respectively. A new conversion can be initiated by a software to the ADC Control Register's start bit.

Initiating a new conversion, stops any conversion currently in progress and begins a new conversion. To avoid disrupting a conversion already in progress, the START bit can be read to determine ADC operation status (busy or available).

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

113

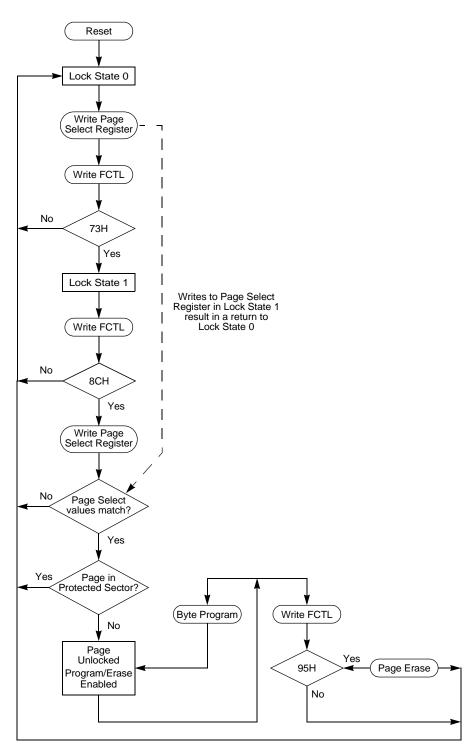

Figure 19. Flash Controller Operation Flow Chart

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

## Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

## Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

# Nonvolatile Data Storage

Z8 Encore! F0830 Series devices contain a Nonvolatile Data Storage (NVDS) element of up to 64 bytes (except when in Flash 12KB mode). This type of memory can perform over 100,000 write cycles.

# Operation

NVDS is implemented by special-purpose Zilog software stored in areas of program memory that are not user-accessible. These special-purpose routines use Flash memory to store the data, and incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

**Note:** The products in the Z8 Encore! F0830 Series feature multiple NVDS array sizes. See the <u>Z8 Encore! F0830 Series Family Part Selection Guide</u> section on page 2 for details.

# **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a predefined address outside of program memory that is accessible to the user. Both the NVDS address and data are singlebyte values. In order to not disturb the user code, these routines save the working register set before using it so that 16 bytes of stack space are required to preserve the site. After finishing the call to these routines, the working register set of the user code is recovered.

During both read and write accesses to the NVDS, interrupt service is not disabled. Any interrupts that occur during NVDS execution must not disturb the working register and existing stack contents; otherwise, the array can become corrupted. Zilog recommends the user disable interrupts before executing NVDS operations.

Use of the NVDS requires 16 bytes of available stack space. The contents of the working register set are saved before calling NVDS read or write routines.

For correct NVDS operation, the Flash Frequency registers must be programmed based on the system clock frequency. See *the* <u>Flash Operation Timing Using the Flash Frequency</u><u>Registers</u> *section on page 114*.

## **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the Byte Write routine ( $0 \times 20B3$ ). At the return from the subroutine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 91. Additionally, user code should pop the address and data bytes off the stack.

The write routine uses 16 bytes of stack space in addition to the two bytes of address and data pushed by the user code. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $136\mu s$  (assuming a 20MHz system clock). For every 200 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 58ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $7\mu$ s execution time.

| Bit              | 7                          | 6                                                                                                                                                                                                                    | 5               | 4           | 3  | 2 | 1 | 0 |  |  |  |  |

|------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|----|---|---|---|--|--|--|--|

| Field            |                            |                                                                                                                                                                                                                      | FE              | IGADDR      | WE |   |   |   |  |  |  |  |

| Default<br>Value | 0                          | 0                                                                                                                                                                                                                    | 0               | 0           | 0  | 0 | 0 | 0 |  |  |  |  |

| Bit              | Description                |                                                                                                                                                                                                                      |                 |             |    |   |   |   |  |  |  |  |

| [7:3]            | Reserved<br>These bits     | <b>Reserved</b><br>These bits are reserved and must be programmed to 00000.                                                                                                                                          |                 |             |    |   |   |   |  |  |  |  |

| [2]<br>FE        | Flash Erro<br>If a Flash e | -                                                                                                                                                                                                                    | ted, this bit i | s set to 1. |    |   |   |   |  |  |  |  |

| [1]<br>IGADDR    | lllegal Address            |                                                                                                                                                                                                                      |                 |             |    |   |   |   |  |  |  |  |

| [0]<br>WE        | A failure oc               | Write Error<br>A failure occurs during data writes to Flash. When writing data into a certain address, a read-<br>back operation is performed. If the read-back value is not the same as the value written, this bit |                 |             |    |   |   |   |  |  |  |  |

#### Table 91. Write Status Byte

is set to 1.

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a system reset

## **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 start bit, 8 data bits (least-significant bit first) and 1 stop bit. See Figure 23.

| <br>START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-----------|----|----|----|----|----|----|----|----|------|

| OTAR      | 00 | ы  | 02 | 05 | D4 | 00 | DU | ы  | 0101 |

## Figure 23. OCD Data Format

# **OCD Autobaud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an autobaud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits low (one Start bit plus 7 data bits), framed between high bits. The autobaud detector measures this period and sets the OCD baud rate generator accordingly.

The autobaud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 94 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency<br>(MHz) | Recommended<br>Maximum Baud Rate<br>(kbps) | Recommended<br>Standard PC Baud Rate<br>(bps) | Minimum Baud Rate<br>(kbps) |

|------------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                               | 2500.0                                     | 1,843,200                                     | 39                          |

| 1.0                                | 125.0                                      | 115,200                                       | 1.95                        |

| 0.032768 (32 KHz)                  | 4.096                                      | 2400                                          | 0.064                       |

| Table 9 | 94. OCD | Baud-Rate | Limits |

|---------|---------|-----------|--------|

|         |         |           |        |

| Assembly         |                                                                                           |     |     | Op<br>Code(s) | ) Flags |   |   |   |   |   | Fetch | Instr. |

|------------------|-------------------------------------------------------------------------------------------|-----|-----|---------------|---------|---|---|---|---|---|-------|--------|

| Mnemonic         | Symbolic Operation                                                                        | dst | src | (Hex)         | С       | Ζ | S | ۷ | D | Н |       |        |

| AND dst, src     | $dst \gets dst \; AND \; src$                                                             | r   | r   | 52            | _       | * | * | 0 | _ | _ | 2     | 3      |

|                  |                                                                                           | r   | lr  | 53            | _       |   |   |   |   |   | 2     | 4      |

|                  |                                                                                           | R   | R   | 54            |         |   |   |   |   |   | 3     | 3      |

|                  |                                                                                           | R   | IR  | 55            | _       |   |   |   |   |   | 3     | 4      |

|                  |                                                                                           | R   | IM  | 56            | _       |   |   |   |   |   | 3     | 3      |

|                  |                                                                                           | IR  | IM  | 57            | _       |   |   |   |   |   | 3     | 4      |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER  | ER  | 58            | _       | * | * | 0 | _ | _ | 4     | 3      |

|                  |                                                                                           | ER  | IM  | 59            | _       |   |   |   |   |   | 4     | 3      |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |     |     | 2F            | -       | _ | _ | _ | _ | _ | 1     | 2      |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r   |     | E2            | _       | * | * | 0 | _ | _ | 2     | 2      |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r   |     | E2            | _       | * | * | 0 | _ | _ | 2     | 2      |

| BRK              | Debugger Break                                                                            |     |     | 00            | -       | _ | - | - | _ | _ | 1     | 1      |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r   |     | E2            | -       | * | * | 0 | - | - | 2     | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R   |     | D5            | Х       | * | * | 0 | - | - | 2     | 2      |

| BTJ p, bit, src, | if src[bit] = p                                                                           |     | r   | F6            | -       | _ | - | - | _ | _ | 3     | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr  | F7            | _       |   |   |   |   |   | 3     | 4      |

| BTJNZ bit, src,  |                                                                                           |     | r   | F6            | -       | - | - | - | - | - | 3     | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr  | F7            | _       |   |   |   |   |   | 3     | 4      |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |     | r   | F6            | _       | - | _ | _ | - | - | 3     | 3      |

| dst              | $PC \gets PC + X$                                                                         |     | Ir  | F7            |         |   |   |   |   |   | 3     | 4      |

| CALL dst         | $SP \leftarrow SP -\!\!\!\!\!-\!\!\!\!\!2$                                                | IRR |     | D4            | _       | _ | - | - | _ | - | 2     | 6      |

|                  | @SP ← PC<br>PC ← dst                                                                      | DA  |     | D6            |         |   |   |   |   |   | 3     | 3      |

| CCF              | $C \leftarrow \sim C$                                                                     |     |     | EF            | *       | _ | _ | _ | _ |   | 1     | 2      |

## Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

|                   |                                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = -40°C to<br>+105°C |                  |     |       |                                                             |  |

|-------------------|-------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|-----|-------|-------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                 | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max | Units | Conditions                                                  |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>disabled                              |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>enabled                               |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                                            |                               |     |     | _                                   | 10               | _   | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to gen<br>erate a Reset. |  |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to<br>transition from $V_{SS}$<br>to $V_{POR}$ to ensure<br>valid Reset |                               |     |     | 0.10                                | _                | 100 | ms    |                                                             |  |

## Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

ance only and are not tested in production.

|                       |              |       |      |                 | -           |

|-----------------------|--------------|-------|------|-----------------|-------------|

| Part Number           | Flash        | RAM   | NVDS | ADC<br>Channels | Description |

| Extended Temperatur   | re: -40°C to | 105°C |      |                 |             |

| Z8F0230SH020EG        | 2KB          | 256   | Yes  | 7               | SOIC 20-pin |

| Z8F0230HH020EG        | 2KB          | 256   | Yes  | 7               | SSOP 20-pin |

| Z8F0230PH020EG        | 2KB          | 256   | Yes  | 7               | PDIP 20-pin |

| Z8F0230QH020EG        | 2KB          | 256   | Yes  | 7               | QFN 20-pin  |

| Z8F0231SH020EG        | 2KB          | 256   | Yes  | 0               | SOIC 20-pin |

| Z8F0231HH020EG        | 2KB          | 256   | Yes  | 0               | SSOP 20-pin |

| Z8F0231PH020EG        | 2KB          | 256   | Yes  | 0               | PDIP 20-pin |

| Z8F0231QH020EG        | 2KB          | 256   | Yes  | 0               | QFN 20-pin  |

| Z8F0230SJ020EG        | 2KB          | 256   | Yes  | 8               | SOIC 28-pin |

| Z8F0230HJ020EG        | 2KB          | 256   | Yes  | 8               | SSOP 28-pin |

| Z8F0230PJ020EG        | 2KB          | 256   | Yes  | 8               | PDIP 28-pin |

| Z8F0230QJ020EG        | 2KB          | 256   | Yes  | 8               | QFN 28-pin  |

| Z8F0231SJ020EG        | 2KB          | 256   | Yes  | 0               | SOIC 28-pin |

| Z8F0231HJ020EG        | 2KB          | 256   | Yes  | 0               | SSOP 28-pin |

| Z8F0231PJ020EG        | 2KB          | 256   | Yes  | 0               | PDIP 28-pin |

| Z8F0231QJ020EG        | 2KB          | 256   | Yes  | 0               | QFN 28-pin  |

| Z8 Encore! F0830 with | h 1KB Flash  | 1     |      |                 |             |

| Standard Temperatur   | e: 0°C to 70 | °C    |      |                 |             |

| Z8F0130SH020SG        | 1KB          | 256   | Yes  | 7               | SOIC 20-pin |

| Z8F0130HH020SG        | 1KB          | 256   | Yes  | 7               | SSOP 20-pin |

| Z8F0130PH020SG        | 1KB          | 256   | Yes  | 7               | PDIP 20-pin |

| Z8F0130QH020SG        | 1KB          | 256   | Yes  | 7               | QFN 20-pin  |

| Z8F0131SH020SG        | 1KB          | 256   | Yes  | 0               | SOIC 20-pin |

| Z8F0131HH020SG        | 1KB          | 256   | Yes  | 0               | SSOP 20-pin |

| Z8F0131PH020SG        | 1KB          | 256   | Yes  | 0               | PDIP 20-pin |

| Z8F0131QH020SG        | 1KB          | 256   | Yes  | 0               | QFN 20-pin  |

| Z8F0130SJ020SG        | 1KB          | 256   | Yes  | 8               | SOIC 28-pin |

| Z8F0130HJ020SG        | 1KB          | 256   | Yes  | 8               | SSOP 28-pin |

| Z8F0130PJ020SG        | 1KB          | 256   | Yes  | 8               | PDIP 28-pin |

| Z8F0130QJ020SG        | 1KB          | 256   | Yes  | 8               | QFN 28-pin  |

| Z8F0131SJ020SG        | 1KB          | 256   | Yes  | 0               | SOIC 28-pin |

| Z8F0131HJ020SG        | 1KB          | 256   | Yes  | 0               | SSOP 28-pin |

|                       |              |       |      |                 |             |

## Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

# Appendix A. Register Tables

For the reader's convenience, this appendix lists all F0830 Series registers numerically by hexadecimal address.

# **General Purpose RAM**

In the F0830 Series, the 000–EFF hexadecimal address range is partitioned for general-purpose random access memory, as follows.

## Hex Addresses: 000–0FF

This address range is reserved for general-purpose register file RAM. For more details, see the <u>Register File</u> section on page 14.

## Hex Addresses: 100-EFF

This address range is reserved.

# Timer 0

For more information about these Timer Control registers, see the <u>Timer Control Register</u> <u>Definitions</u> section on page 83.

## Hex Address: F00

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|

| Field   | TH  |      |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F00H |     |     |     |     |     |     |  |  |

### Table 130. Timer 0 High Byte Register (T0H)

## Hex Address: FD3

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |       | FD3H  |       |       |       |       |       |       |  |  |

### Table 172. Port A Output Data Register (PAOUT)

### Hex Address: FD4

### Table 173. Port B GPIO Address Register (PBADDR)

| Bit     | 7          | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------|-----------------------------|---|---|---|---|---|---|--|

| Field   | PADDR[7:0] |                             |   |   |   |   |   |   |  |

| RESET   | 00H        |                             |   |   |   |   |   |   |  |

| R/W     | R/W        | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FD4H       |                             |   |   |   |   |   |   |  |

## Hex Address: FD5

### Table 174. Port B Control Registers (PBCTL)

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|

| Field   | PCTL |                             |   |   |   |   |   |   |  |

| RESET   | 00H  |                             |   |   |   |   |   |   |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FD5H |                             |   |   |   |   |   |   |  |

### Hex Address: FD6

### Table 175. Port B Input Data Registers (PBIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |

| Address | FD6H |      |      |      |      |      |      |      |