# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                   |

|----------------------------|----------------------------------------------------------|

| Core Processor             | HC08                                                     |

| Core Size                  | 8-Bit                                                    |

| Speed                      | 8MHz                                                     |

| Connectivity               | SCI                                                      |

| Peripherals                | LVD, POR, PWM                                            |

| Number of I/O              | 12                                                       |

| Program Memory Size        | 8KB (8K x 8)                                             |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                | -                                                        |

| RAM Size                   | 256 x 8                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                              |

| Data Converters            | A/D 4x10b                                                |

| Oscillator Type            | Internal                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                        |

| Mounting Type              | Through Hole                                             |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                 |

| Supplier Device Package    | 28-PDIP                                                  |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908mr8cpe |

|                            |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table of Contents

| Stop Mode                       |

|---------------------------------|

| SIM Break Status Register       |

| SIM Reset Status Register       |

| SIM Break Flag Control Register |

|                                 |

# Section 8. Clock Generator Module (CGM)

| 8.1 Contents     |                                      |

|------------------|--------------------------------------|

| 8.2 Introduction |                                      |

| 8.3 Features     |                                      |

| 8.4 Functional [ | Description                          |

| 8.4.1 Crystal C  | Oscillator Circuit                   |

| •                | ocked Loop Circuit (PLL)             |

|                  | ircuits                              |

|                  | sition and Tracking Modes            |

|                  | al and Automatic PLL Bandwidth Modes |

| 8.4.2.4 Progra   | amming the PLL                       |

| 8.4.2.5 Specia   | al Programming Exceptions            |

| -                | ck Selector Circuit                  |

| 8.4.4 CGM Ext    | ernal Connections                    |

| 8.5 I/O Signals  |                                      |

| 8.5.1 Crystal A  | mplifier Input Pin (OSC1)123         |

|                  | mplifier Output Pin (OSC2)           |

|                  | Filter Capacitor Pin (CGMXFC)        |

|                  | log Power Pin (V <sub>DDA</sub> )    |

|                  | r Enable Signal (SIMOSCEN)           |

| 8.5.6 Crystal C  | Output Frequency Signal (CGMXCLK)    |

| 8.5.7 CGM Bas    | se Clock Output (CGMOUT)             |

| 8.5.8 CGM CP     | U Interrupt (CGMINT)124              |

| 8.6 CGM Regis    | ters                                 |

| 8.6.1 PLL Con    | trol Register                        |

| 8.6.2 PLL Ban    | dwidth Control Register129           |

| 8.6.3 PLL Prog   | ramming Register                     |

| 8.7 Interrupts   |                                      |

| 8.8 Wait Mode.   |                                      |

| 8.9 Stop Mode    |                                      |

| Addr.           | Register Name                              |                 | Bit 7  | 6                         | 5           | 4          | 3               | 2      | 1        | Bit 0      |  |  |  |

|-----------------|--------------------------------------------|-----------------|--------|---------------------------|-------------|------------|-----------------|--------|----------|------------|--|--|--|

| \$0014          | TIMA Channel 0 Regis-<br>ter High (TACH0H) | Read:<br>Write: | Bit 15 | 14                        | 13          | 12         | 11              | 10     | 9        | Bit 8      |  |  |  |

| See page 222.   |                                            | Reset:          |        | Indeterminate after reset |             |            |                 |        |          |            |  |  |  |

| \$0015          | TIMA Channel 0 Regis-<br>ter Low (TACH0L)  |                 | Bit 7  | 6                         | 5           | 4          | 3               | 2      | 1        | Bit 0      |  |  |  |

|                 | See page 218.                              | Reset:          |        |                           | I           | ndetermina | ate after res   | set    |          |            |  |  |  |

|                 | TIMA Channel 1 Sta-                        | Read:           | CH1F   |                           | 0           |            |                 |        | TO)/4    | CH1MA      |  |  |  |

| \$0016          | tus/Control<br>Register (TASC1)            | Write:          | 0      | CH1IE                     | R           | MS1A       | ELS1B           | ELS1A  | TOV1     | х          |  |  |  |

|                 | See page <b>222</b> .                      | Reset:          | 0      | 0                         | 0           | 0          | 0               | 0      | 0        | 0          |  |  |  |

| \$0017          | TIMA Channel 1 Regis-<br>ter High (TACH1H) |                 | Bit 15 | 14                        | 13          | 12         | 11              | 10     | 9        | Bit 8      |  |  |  |

|                 | See page 222.                              | Reset:          |        |                           | I           | ndetermina | ate after res   | set    |          |            |  |  |  |

| \$0018          | TIMA Channel 1 Regis-<br>ter Low (TACH1L)  | Read:<br>Write: | Bit 7  | 6                         | 5           | 4          | 3               | 2      | 1        | Bit 0      |  |  |  |

|                 | See page 222.                              | Reset:          |        | Indeterminate after reset |             |            |                 |        |          |            |  |  |  |

| \$0019          |                                            |                 |        |                           |             | Unimpl     | emented         |        |          |            |  |  |  |

| $\downarrow$    |                                            |                 |        |                           |             |            |                 |        |          |            |  |  |  |

| \$001E          |                                            |                 |        |                           |             | Unimpl     | emented         |        |          |            |  |  |  |

|                 |                                            |                 |        |                           |             |            |                 |        |          |            |  |  |  |

| \$001F          | Configuration Register<br>(CONFIG)         | Read:<br>Write: | EDGE   | BOT-<br>NEG               | TOP-<br>NEG | INDEP      | LVIRST          | LVIPWR | STOPE    | COPD       |  |  |  |

|                 | See page 68.                               | Reset:          | 0      | 0                         | 0           | 0          | 1               | 1      | 0        | 0          |  |  |  |

| \$0020          | PWM Control Register 1<br>(PCTL1)          | Read:<br>Write: | DISX   | DISY                      | PW-<br>MINT | PWMF       |                 |        | LDOK     | PW-<br>MEN |  |  |  |

|                 | See page 175.                              | Reset:          | 0      | 0                         | 0           | 0          | 0               | 0      | 0        | 0          |  |  |  |

| \$0021          | PWM Control Register 2<br>(PCTL2)          |                 | LDFQ1  | LDFQ0                     | 0           | SEL12      | SEL34           | SEL56  | PRSC1    | PRSC0      |  |  |  |

|                 | See page 177.                              | Reset:          | 0      | 0                         | 0           | 0          | 0               | 0      | 0        | 0          |  |  |  |

| U = Una<br>nate | iffected X = Indetermi-                    |                 | R      | = Reserv                  | ved         | Bold       | = Buff-<br>ered |        | = Unimpl | emented    |  |  |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 10)

#### TOPNEG — Top-Side PWM Polarity Bit

TOPNEG determines if the top-side PWMs will have positive or negative polarity. See **Section 9. Pulse-Width Modulator for Motor Control (PWMMC)**.

- 1 = Negative polarity

- 0 = Positive polarity

- INDEP Independent Mode Enable Bit

INDEP determines if the motor control PWMs will be six independent PWMs or three complementary PWM pairs. See **Section 9.**

Pulse-Width Modulator for Motor Control (PWMMC).

1 = Six independent PWMs

0 = Three complementary PWM pairs

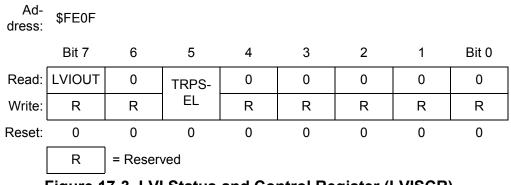

LVIPWR — LVI Power Enable Bit

LVIPWR enables the LVI module. See **Section 17. Low-Voltage Inhibit (LVI)**.

1 = LVI module power enabled

0 = LVI module power disabled

LVIRST — LVI Reset Enable Bit

LVIRST enables the reset signal from the LVI module. See **Section 17. Low-Voltage Inhibit (LVI)**.

1 = LVI module resets enabled

0 = LVI module resets disabled

STOPE — STOP Enable Bit

STOPE enables the STOP instruction. See **Section 6. Central Processor Unit (CPU)**.

- 1 = STOP instruction is enabled.

- 0 = STOP instruction is disabled and executes as an illegal instruction.

- COPD COP Disable Bit

- COPD disables the COP module. See **Section 15. Computer Operating Properly (COP)**.

- 1 = COP module disabled

- 0 = COP module enabled

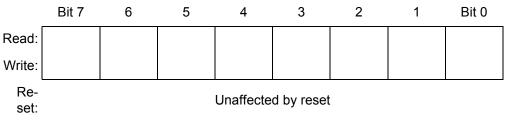

#### 6.4.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 6-2. Accumulator (A)

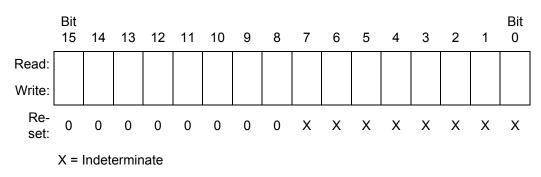

#### 6.4.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

Figure 6-3. Index Register (H:X)

The index register can serve also as a temporary data storage location.

Freescale Semiconductor

| Source                                                                                                | • *                               | <b>D</b> 1 //                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I | Effe | ecto | on | CCI | R  | ess                                                                                                      | qe                                       | and                                                                           | S                                                                  |

|-------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|------|----|-----|----|----------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Form                                                                                                  | Operation                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ۷ | Н    | I    | Ν  | Z   | С  | Address<br>Mode                                                                                          | Opcode                                   | Operand                                                                       | Cycles                                                             |

| BNE rel                                                                                               | Branch if Not Equal               | PC ← (PC) + 2 + <i>rel</i> ? (Z) = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - | -    | -    | -  | -   | -  | REL                                                                                                      | 26                                       | rr                                                                            | 3                                                                  |

| BPL rel                                                                                               | Branch if Plus                    | PC ← (PC) + 2 + <i>rel</i> ? (N) = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - | -    | -    | -  | -   | -  | REL                                                                                                      | 2A                                       | rr                                                                            | 3                                                                  |

| BRA rel                                                                                               | Branch Always                     | PC " (PC) + 2 + <i>rel</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - | -    | -    | -  | -   | -  | REL                                                                                                      | 20                                       | rr                                                                            | 3                                                                  |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _ | _    | _    | _  | _   | \$ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b7)             | 05<br>07<br>09<br>0B<br>0D               | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BRN rel                                                                                               | Branch Never                      | $PC \leftarrow (PC) + 2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - | -    | -    | -  | -   | -  | REL                                                                                                      | 21                                       | rr                                                                            | 3                                                                  |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set   | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _ | _    | _    | _  | _   | \$ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b7)             | 06<br>08<br>0A<br>0C                     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 555555555                                                          |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M             | Mn ← 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _ | _    | _    | _  | _   | _  | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 14<br>16<br>18<br>1A<br>1C               | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                            | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4                               |

| BSR rel                                                                                               | Branch to Subroutine              | $\begin{array}{l} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ & SP \leftarrow (SP) - 1 \\ & PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _ | -    | -    | _  | _   | _  | REL                                                                                                      | AD                                       | rr                                                                            | 4                                                                  |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal       | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel ? (A) - (M) = \$00 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - | _    | _    | _  | _   | -  | DIR<br>IMM<br>IX1+<br>IX+<br>SP1                                                                         | 51<br>61<br>71                           | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                               | 544546                                                             |

| CLC                                                                                                   | Clear Carry Bit                   | $C \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - | _    | -    | _  | -   | 0  | INH                                                                                                      | 98                                       |                                                                               | 1                                                                  |

| CLI                                                                                                   | Clear Interrupt Mask              | l ← 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _ | -    | 0    | _  | -   | -  | INH                                                                                                      | 9A                                       |                                                                               | 2                                                                  |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                                  | Clear                             | $\begin{array}{l} M \leftarrow \$00\\ A \leftarrow \$00\\ X \leftarrow \$00\\ H \leftarrow \$00\\ M \leftarrow M \leftarrow M \leftarrow M \bullet M \leftarrow \mathsf$ | 0 | _    | _    | 0  | 1   | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F | dd<br>ff<br>ff                                                                | 3<br>1<br>1<br>3<br>2<br>4                                         |

#### Table 6-1. Instruction Set Summary (Sheet 3 of 8)

#### 7.3.3 Clocks in Wait Mode

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

#### 7.4 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE\_FFF (\$FEFE\_FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see **7.5 SIM Counter**), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See **7.7.4 SIM Reset Status Register**.

#### 7.4.1 External Pin Reset

Pulling the asynchronous RST pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as RST is held low for a minimum of 67 CGMXCLK cycles, assuming that neither the POR nor the LVI was the source of the reset. See **Table 7-2** for details. **Figure 7-4** shows the relative timing.

MC68HC908MR8 — Rev 4.1

is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

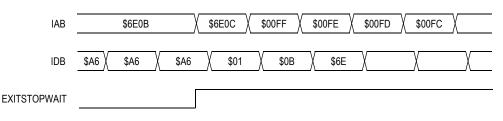

Wait mode can also be exited by a reset or break. A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the SIM break status register (SBSR). If the COP disable bit, COPD, in the configuration register is logic 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

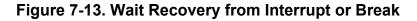

Figure 7-13 and Figure 7-14 show the timing for wait recovery.

Note: EXITSTOPWAIT = RST pin or CPU interrupt or break interrupt

Figure 7-14. Wait Recovery from Internal Reset

#### 7.7.2 Stop Mode

In stop mode, the SIM counter is reset and the system clock is disabled. An external interrupt request will cause an exit from stop mode. Stacking for interrupts begins after the stop recovery delay time of 4096 CGMXCLK cycles has elapsed. Reset or break also cause an exit from stop mode.

The SIM disables the clock generator module outputs in stop mode, stopping the CPU and all peripherals.

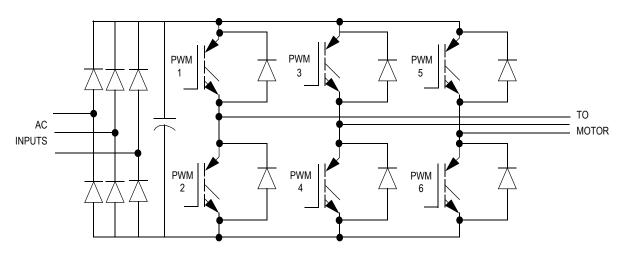

**NOTE:** It is important to note that when using the PWM generator Its outputs will stop toggling when stop mode is entered. The PWM module must be disabled before entering stop mode to prevent external inverter failure.

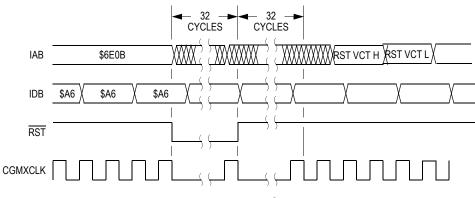

#### 7.7.3 SIM Break Status Register

The SIM break status register (SBSR) contains a flag to indicate that a break caused an exit from wait mode.

SBSW — SIM Break Stop/Wait Bit

This status bit is useful in applications requiring a return to wait mode after exiting from a break interrupt. Clear SBSW by writing a logic 0 to it. Reset clears SBSW.

1 = Wait mode was exited by break interrupt.

0 = Wait mode was not exited by break interrupt.

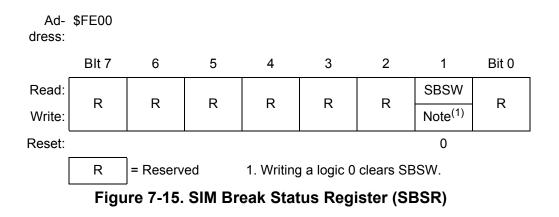

#### 8.6.3 PLL Programming Register

The PLL programming register (PPG) contains the programming information for the modulo feedback divider and the programming information for the hardware configuration of the VCO.

Figure 8-7. PLL Programming Register (PPG)

MUL[7:4] — Multiplier Select Bits

These read/write bits control the modulo feedback divider that selects the VCO frequency multiplier, N. See **8.4.2.1 PLL Circuits** and **8.4.2.4 Programming the PLL**. A value of \$0 in the multiplier select bits configures the modulo feedback divider the same as a value of \$1. Reset initializes these bits to \$6 to give a default multiply value of 6.

Table 8-1. VCO Frequency Multiplier (N) Selection

| MUL7:MUL6:MUL5:MUL4 | VCO Frequency Multiplier (N) |

|---------------------|------------------------------|

| 0000                | 1                            |

| 0001                | 1                            |

| 0010                | 2                            |

| 0011                | 3                            |

|                     |                              |

| 1101                | 13                           |

| 1110                | 14                           |

| 1111                | 15                           |

**NOTE:** The multiplier select bits have built-in protection that prevents them from being written when the PLL is on (PLLON = 1).

MC68HC908MR8 - Rev 4.1

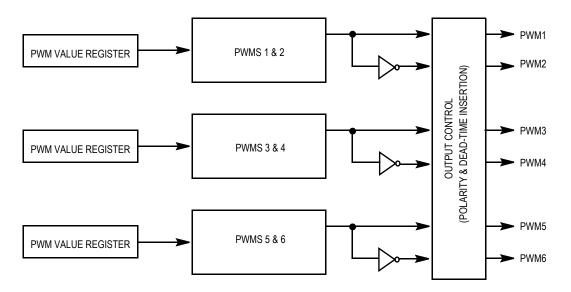

Figure 9-11. Complementary Pairing

Figure 9-12. Typical AC Motor Drive

When complementary operation is used, two additional features are provided:

- Dead-time insertion

- Separate top/bottom pulse width correction to correct for distortions caused by the motor drive characteristics.

If independent operation is chosen, each PWM has its own PWM value register.

MC68HC908MR8 - Rev 4.1

## Monitor ROM (MON)

#### **10.4 Functional Description**

The monitor ROM receives and executes commands from a host computer. **Figure 10-1** shows a sample circuit used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute host-computer code in RAM while all MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the serial communications interface (SCI). A level-shifting RS-232 interface is required between the SCI and the host computer. PTB1 requires a pulldown resistor to ensure proper entry into monitor mode.

#### **10.4.1 Entering Monitor Mode**

**Table 10-1** shows the pin conditions for entering monitor mode.

| IRQ<br>Pin      | RESET                                    | \$FFFE/<br>\$FFFF | PLL | PTB0            | PTB1     | External<br>Clock | CGMOUT              | f <sub>op</sub>     | СОР      | Baud<br>Rate              | Comment                                                                            |

|-----------------|------------------------------------------|-------------------|-----|-----------------|----------|-------------------|---------------------|---------------------|----------|---------------------------|------------------------------------------------------------------------------------|

| х               | $V_{SS}$                                 | х                 | х   | х               | х        | х                 | 0                   | 0                   | Disabled | 0                         | No operation<br>until reset = V <sub>DD</sub>                                      |

| V <sub>HI</sub> | V <sub>DD</sub><br>or<br>V <sub>HI</sub> | х                 | ON  | V <sub>DD</sub> | $V_{SS}$ | 4.0 MHz           | 16.0 MHz            | 8.0 MHz             | Disabled | 9600                      | PLL configured with<br>BCS set by monitor<br>code                                  |

| V <sub>DD</sub> | V <sub>DD</sub>                          | Blank<br>(FF)     | ON  | х               | х        | 4.0 MHz           | 16.0 MHz            | 8.0 MHz             | Disabled | 9600                      | PLL configured with<br>BCS set by monitor<br>code                                  |

| V <sub>SS</sub> | V <sub>DD</sub>                          | Blank<br>(FF)     | OFF | х               | x        | f <sub>osc</sub>  | f <sub>OSC</sub> /2 | f <sub>OSC</sub> /4 | Disabled | f <sub>OSC</sub><br>/1024 | Enters monitor<br>mode with any<br>external clock rate<br>within operating<br>spec |

| $V_{DD}$        | $V_{DD}$                                 | Non-blank         | Х   | Х               | Х        | Х                 | Х                   | Х                   | Enabled  | Х                         | Enters user mode                                                                   |

Table 10-1. Mode Selection

X = Don't care

PTB0 =  $V_{DD}$  and PTB1 =  $V_{SS}$  to enter monitor mode

PTB0 (RXD) and PTB1 (TXD) used for serial communications (all monitor mode)

## Timer Interface A (TIMA)

#### 11.10.2 TIMA Counter Registers

Register Name and Ad-

The two read-only TIMA counter registers contain the high and low bytes of the value in the TIMA counter. Reading the high byte (TACNTH) latches the contents of the low byte (TACNTL) into a buffer. Subsequent reads of TACNTH do not affect the latched TACNTL value until TACNTL is read. Reset clears the TIMA counter registers. Setting the TIMA reset bit (TRST) also clears the TIMA counter registers.

**NOTE:** If TACNTH is read during a break interrupt, be sure to unlatch TACNTL by reading TACNTL before exiting the break interrupt. Otherwise, TACNTL retains the value latched during the break.

**TACNTH — \$000F**

| dress:             |          |          | -      |          |        |        |       |       |

|--------------------|----------|----------|--------|----------|--------|--------|-------|-------|

|                    | Bit 7    | 6        | 5      | 4        | 3      | 2      | 1     | Bit 0 |

| Read:              | Bit 15   | Bit 14   | Bit 13 | Bit 12   | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| Write:             | R        | R        | R      | R        | R      | R      | R     | R     |

| Reset:             | 0        | 0        | 0      | 0        | 0      | 0      | 0     | 0     |

|                    |          |          |        |          |        |        |       |       |

| Register<br>dress: | Name and | d Ad-    | TACNTL | — \$0010 |        |        |       |       |

|                    | Bit 7    | 6        | 5      | 4        | 3      | 2      | 1     | Bit 0 |

| Read:              | Bit 7    | Bit 6    | Bit 5  | Bit 4    | Bit 3  | Bit 2  | Bit 1 | Bit 0 |