Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | HC08                                                                |

| Core Size                  | 8-Bit                                                               |

| Speed                      | 8MHz                                                                |

| Connectivity               | SCI                                                                 |

| Peripherals                | LVD, POR, PWM                                                       |

| Number of I/O              | 12                                                                  |

| Program Memory Size        | 8KB (8K x 8)                                                        |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 256 x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                         |

| Data Converters            | A/D 4x10b                                                           |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                  |

| Mounting Type              | Through Hole                                                        |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                            |

| Supplier Device Package    | 28-PDIP                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908mr8mpe |

| 11.4.3 Output Compare                                 | 205 |

|-------------------------------------------------------|-----|

| 11.4.3.1 Unbuffered Output Compare                    |     |

| 11.4.3.2 Buffered Output Compare                      | 206 |

| 11.4.4 Pulse-Width Modulation (PWM)                   | 207 |

| 11.4.4.1 Unbuffered PWM Signal Generation             | 208 |

| 11.4.4.2 Buffered PWM Signal Generation               |     |

| 11.4.4.3 PWM Initialization                           | 210 |

| 11.5 Interrupts                                       | 211 |

| 11.6 Wait Mode                                        | 211 |

| 11.7 Stop Mode                                        | 212 |

| 11.8 TIMA During Break Interrupts                     | 212 |

| 11.9 I/O Signals                                      |     |

| 11.9.1 TIMA Clock Pin (PTB2/TCLKA)                    |     |

| 11.9.2 TIMA Channel I/O Pins (PTB3/TCH0A–PTB4/TCH1A). |     |

| 11.10 I/O Registers                                   | 213 |

| 11.10.1 TIMA Status and Control Register              | 214 |

| 11.10.2 TIMA Counter Registers                        | 216 |

| 11.10.3 TIMA Counter Modulo Registers                 | 217 |

| 11.10.4 TIMA Channel Status and Control Registers     |     |

| 11.10.5 TIMA Channel Registers                        | 222 |

| Section 12. Timer Interface B (TIMB)                  |     |

| 12.1 Contents                                         | 223 |

| 12.2 Introduction                                     | 224 |

| 12.3 Features                                         | 224 |

| 12.4 Functional Description                           | 227 |

| 12.4.1 TIMB Counter Prescaler                         |     |

| 12.4.2 Input Capture                                  |     |

| 12.4.3 Output Compare                                 |     |

| 12.4.3.1 Unbuffered Output Compare                    |     |

| 12.4.3.2 Buffered Output Compare                      | 231 |

| 12.4.4 Pulse-Width Modulation (PWM)                   |     |

| 12.4.4.1 Unbuffered PWM Signal Generation             | 232 |

| 12.4.4.2 Buffered PWM Signal Generation               | 233 |

| 12.4.4.3 PWM Initialization                           | 234 |

MC68HC908MR8 — Rev 4.1

# Technical Data — MC68HC908MR8

# **Section 1. General Description**

### 1.1 Contents

| 1.2    | Introduction                                                   | . 29 |

|--------|----------------------------------------------------------------|------|

| 1.3    | Features                                                       | .30  |

| 1.4    | MCU Block Diagram                                              | .31  |

| 1.5    | Pin Assignments                                                | .33  |

| 1.5.1  | Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> )       | . 34 |

| 1.5.2  | Oscillator Pins (OSC1 and OSC2)                                | . 34 |

| 1.5.3  | External Reset Pin (RST)                                       | . 34 |

| 1.5.4  | External Interrupt Pin (IRQ)                                   | . 35 |

| 1.5.5  | CGM Power Supply Pins (V <sub>DDA</sub> and V <sub>SSA</sub> ) | . 35 |

| 1.5.6  | ADC Reference Voltage Input Pin (V <sub>REFH</sub> )           | . 35 |

| 1.5.7  | External Filter Capacitor Pin (CGMXFC)                         | . 35 |

| 1.5.8  | Port A Input/Output (I/O) Pins (PTA6/ATD6-PTA0/ATD             | 0)   |

|        |                                                                | . 35 |

| 1.5.9  | Port B I/O Pins (PTB6/TCHB1-PTB0/RxD)                          |      |

| 1.5.10 | Port C I/O Pins (PTC1/FAULT1-PTC0/FAULT4)                      | . 36 |

| 1.5.11 | PWM Pins (PWM6–PWM1)                                           | .36  |

|        |                                                                |      |

### 1.2 Introduction

The MC68HC908MR8 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCU). The M68HC08 Family is based on the customer-specified integrated circuit (CSIC) design strategy. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

MC68HC908MR8 — Rev 4.1

# **Memory Map**

# 2.3 Unimplemented Memory Locations

Some addresses are unimplemented. Accessing an unimplemented address will cause an illegal address reset. In the memory map and in the input/output (I/O) register summary, unimplemented addresses are shaded.

Some I/O bits are read-only; the write function is unimplemented. Writing to a read-only I/O bit has no effect on MCU operation. In register figures, the write function of read-only bits is shaded. Similarly, some I/O bits are write-only; the read function is unimplemented. Reading of write-only I/O bits has no effect on microcontroller unit (MCU) operation. In register figures, the read function of write-only bits is shaded.

# 2.4 Reserved Memory Locations

Some addresses are reserved. Writing to a reserved address can have unpredictable effects on MCU operation. In the memory map and in the I/O register summary, reserved addresses are marked with the word reserved.

Some I/O bits are reserved. Writing to a reserved bit can have unpredictable effects on MCU operation. In register figures, reserved bits are marked with the letter R.

| Addr.                            | Register Name                                      |                 | Bit 7               | 6          | 5      | 4        | 3           | 2       | 1      | Bit 0    |  |

|----------------------------------|----------------------------------------------------|-----------------|---------------------|------------|--------|----------|-------------|---------|--------|----------|--|

|                                  | IRQ Status/Control Reg-                            | Read:           | 0                   | 0          | 0      | 0        | IRQF        | 0       | IMASK1 | MODE1    |  |

| \$003F ister                     | Write:                                             | R               | R                   | R          | R      | INQF     | ACK1        | INASKI  | MODET  |          |  |

|                                  | See page <b>303</b> .                              | Reset:          | 0                   | 0          | 0      | 0        | 0           | 0       | 0      | 0        |  |

| \$0040                           | ADC Status and Control<br>Register (ADSCR)         | Read:<br>Write: | coco                | AIEN       | ADCO   | ADCH4    | ADCH3       | ADCH2   | ADCH1  | ADCH0    |  |

|                                  | See page <b>319</b> .                              | Reset:          | 0                   | 0          | 0      | 1        | 1           | 1       | 1      | 1        |  |

|                                  | ADC Data Register High                             | Read:           | 0                   | 0          | 0      | 0        | 0           | 0       | AD9    | AD8      |  |

| \$0041                           | (ADRH)                                             | Write:          | R                   | R          | R      | R        | R           | R       | R      | R        |  |

|                                  | See page 322.                                      | Reset:          | Unaffected by reset |            |        |          |             |         |        |          |  |

|                                  | ADC Data Register Low                              | Read:           | AD7                 | AD6        | AD5    | AD4      | AD3         | AD2     | AD1    | AD0      |  |

| \$0042                           | (ADRL)                                             | Write:          | R                   | R          | R      | R        | R           | R       | R      | R        |  |

|                                  | See page <b>323</b> .                              | Reset:          |                     |            |        | Unaffect | ed by reset |         |        | <u> </u> |  |

| \$0043                           | ADC Clock Register<br>(ADCLK)                      | Read:<br>Write: | ADIV2               | ADIV1      | ADIV0  | ADICLK   | MODE1       | MODE0   | 0      | 0<br>R   |  |

|                                  | Coo nogo 204                                       | Reset:          | 0                   | 0          | 0      | 0        | 0           | 1       | 0      | 0        |  |

| \$0044                           |                                                    |                 |                     |            |        | Unimpl   | lemented    |         |        |          |  |

| $\downarrow$                     |                                                    |                 |                     |            |        |          |             |         |        |          |  |

| \$0050                           |                                                    |                 | Unimplemented       |            |        |          |             |         |        |          |  |

|                                  | TIMB Status/Control                                | Read:           | TOF                 | TOIL       | TOTOD  | 0        | 0           | DCO     | DC1    | DCO      |  |

| \$0051                           | Register (TBSC)                                    | Write:          | 0                   | TOIE       | TSTOP  | TRST     | R           | PS2 PS1 | P51    | PS0      |  |

|                                  | See page <b>238</b> .                              | Reset:          | 0                   | 0          | 1      | 0        | 0           | 0       | 0      | 0        |  |

|                                  | TIMB Counter Register                              | Read:           | Bit 15              | Bit 14     | Bit 13 | Bit 12   | Bit 11      | Bit 10  | Bit 9  | Bit 8    |  |

| \$0052                           | High<br>(TBCNTH)                                   | Write:          | R                   | R          | R      | R        | R           | R       | R      | R        |  |

|                                  | See page 240.                                      | Reset:          | 0                   | 0          | 0      | 0        | 0           | 0       | 0      | 0        |  |

|                                  | TIMB Counter Register                              | Read;           | Bit 7               | Bit 6      | Bit 5  | Bit 4    | Bit 3       | Bit 2   | Bit 1  | Bit 0    |  |

| \$0053                           | Low<br>(TBCNTL)                                    | Write:          | R                   | R          | R      | R        | R           | R       | R      | R        |  |

|                                  | See page 240.                                      | Reset:          | 0                   | 0          | 0      | 0        | 0           | 0       | 0      | 0        |  |

| \$0054                           | TIMB Counter Modulo<br>Register High (TB-<br>MODH) | Read:<br>Write: | Bit 15              | Bit 14     | Bit 13 | Bit 12   | Bit 11      | Bit 10  | Bit 9  | Bit 8    |  |

|                                  | See page <b>241</b> .                              | Reset:          | 1                   | 1          | 1      | 1        | 1           | 1       | 1      | 1        |  |

| U = Unaffected X = Indeterminate |                                                    |                 | R                   | = Reserved |        |          | emented     |         |        |          |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 7 of 10)

MC68HC908MR8 — Rev 4.1 Technical Data

# Technical Data — MC68HC908MR8

# Section 5. Configuration Register (CONFIG)

### 5.1 Contents

| <b>5.2</b>  | Introduction | 67 |

|-------------|--------------|----|

| <b>5</b> .3 | CONFIG       | 68 |

| 5.4         | CONFIG Bits  | 68 |

### 5.2 Introduction

This section describes the configuration register (CONFIG).

The CONFIG registers contain bits that configure these options:

- Resets caused by the low-voltage inhibit (LVI) module

- Power to the LVI module

- Computer operating properly (COP) module

- Top-side pulse-width modulator (PWM) polarity

- · Bottom-side PWM polarity

- · Edge-aligned versus center-aligned PWMs

- Six independent PWMs versus three complementary PWM pairs

- STOP instruction enable

# **System Integration Module (SIM)**

### 7.6.1 Interrupts

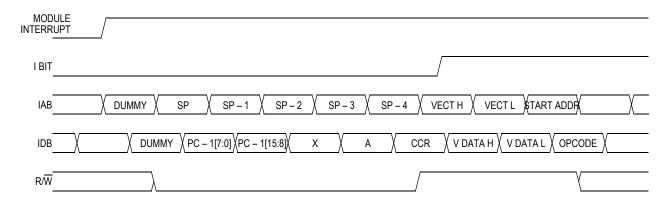

At the beginning of an interrupt, the CPU saves the CPU register contents on the stack and sets the interrupt mask (I bit) to prevent additional interrupts. At the end of an interrupt, the return from interrupt (RTI) instruction recovers the CPU register contents from the stack so that normal processing can resume. **Figure 7-8** shows interrupt entry timing. **Figure 7-10** shows interrupt recovery timing.

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared). See Figure 7-9.

Figure 7-8. Interrupt Entry

# **System Integration Module (SIM)**

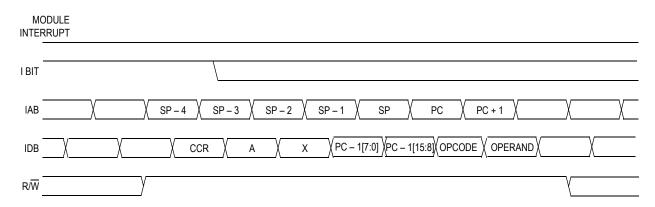

Figure 7-10. Interrupt Recovery

## 7.6.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register), and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

If more than one interrupt is pending at the end of an instruction execution, the highest priority interrupt is serviced first. **Figure 7-11** demonstrates what happens when two interrupts are pending. If an interrupt is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

The LDA opcode is prefetched by both the INT1 and INT2 RTI instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

**NOTE:**

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

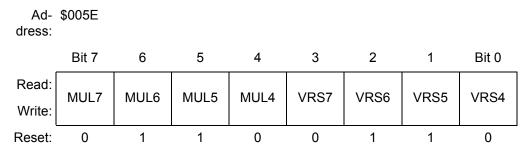

### 8.6.3 PLL Programming Register

The PLL programming register (PPG) contains the programming information for the modulo feedback divider and the programming information for the hardware configuration of the VCO.

Figure 8-7. PLL Programming Register (PPG)

MUL[7:4] — Multiplier Select Bits

These read/write bits control the modulo feedback divider that selects the VCO frequency multiplier, N. See **8.4.2.1 PLL Circuits** and **8.4.2.4 Programming the PLL**. A value of \$0 in the multiplier select bits configures the modulo feedback divider the same as a value of \$1. Reset initializes these bits to \$6 to give a default multiply value of 6.

MUL7:MUL6:MUL5:MUL4 **VCO Frequency Multiplier (N)** 0000 1 0001 1 0010 2 0011 3 1101 13 1110 14 15 1111

Table 8-1. VCO Frequency Multiplier (N) Selection

**NOTE:** The multiplier select bits have built-in protection that prevents them from being written when the PLL is on (PLLON = 1).

MC68HC908MR8 — Rev 4.1

This equation does not always yield a commonly available capacitor size, so round to the nearest available size. If the value is between two different sizes, choose the higher value for better stability. Choosing the lower size may seem attractive for acquisition time improvement, but the PLL can become unstable. Also, always choose a capacitor with a tight tolerance ( $\pm 20$  percent or better) and low dissipation.

#### 8.11.4 Reaction Time Calculation

The actual acquisition and lock times can be calculated using the equations here. These equations yield nominal values under these conditions:

- Correct selection of filter capacitor, C<sub>F</sub>; see 8.11.3 Choosing a Filter Capacitor

- Room temperature operation

- Negligible external leakage on CGMXFC

- Negligible noise

The K factor in the equations is derived from internal PLL parameters.  $K_{ACQ}$  is the K factor when the PLL is configured in acquisition mode, and  $K_{TRK}$  is the K factor when the PLL is configured in tracking mode. See **8.4.2.2 Acquisition and Tracking Modes**.

$$t_{ACQ} = \left(\frac{V_{DDA}}{f_{RDV}}\right) \left(\frac{8}{K_{ACQ}}\right)$$

$$t_{AL} = \left(\frac{V_{DDA}}{f_{RDV}}\right) \left(\frac{4}{K_{TRK}}\right)$$

$$t_{Lock} = t_{ACQ} + t_{AL}$$

**NOTE:** Inverse proportionality between the lock time and the reference frequency

In automatic bandwidth control mode, the acquisition and lock times are quantized into units based on the reference frequency, see **8.4.2.3 Manual and Automatic PLL Bandwidth Modes**. A certain number of clock cycles,  $n_{ACQ}$ , is required to ascertain that the PLL is within the tracking mode entry tolerance,  $\Delta_{TRK}$ , before exiting acquisition mode. A

MC68HC908MR8 — Rev 4.1

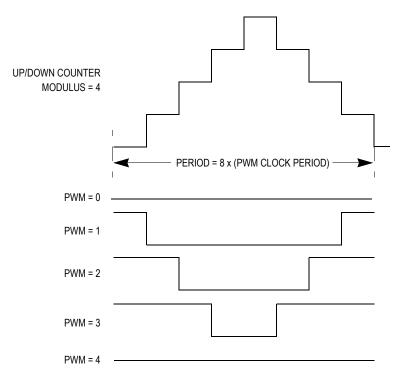

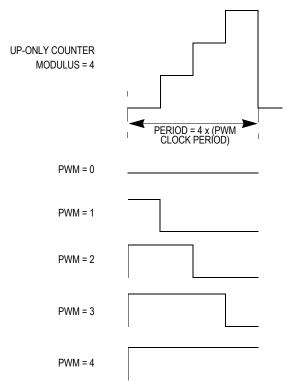

Figure 9-3. Center-Aligned PWM (Positive Polarity)

Figure 9-4. Edge-Aligned PWM (Positive Polarity)

MC68HC908MR8 — Rev 4.1

# **Pulse-Width Modulator for Motor Control**

# 9.12 Control Logic Block

This subsection provides a description of the control logic block.

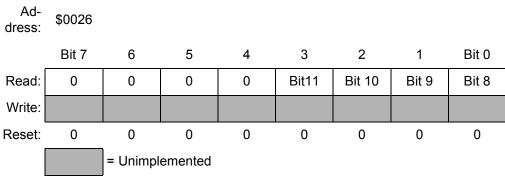

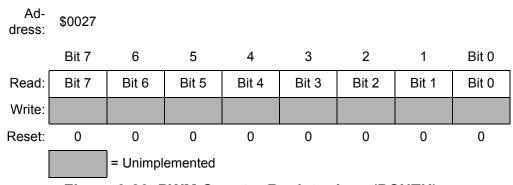

## 9.12.1 PWM Counter Registers

The PWM counter registers (PCNTH and PCNTL) display the 12-bit up/down or up-only counter. When the high byte of the counter is read, the lower byte is latched. PCNTL will hold this latched value until it is read.

Figure 9-29. PWM Counter Register High (PCNTH)

Figure 9-30. PWM Counter Register Low (PCNTH)

### 12.4.3.2 Buffered Output Compare

Channels 0 and 1 can be linked to form a buffered output compare channel whose output appears on the PTB5/TCH0B pin. The TIMB channel registers of the linked pair alternately control the output.

Setting the MS0B bit in TIMB channel 0 status and control register (TBSC0) links channel 0 and channel 1. The output compare value in the TIMB channel 0 registers initially controls the output on the PTB5/TCH0B pin. Writing to the TIMB channel 1 registers enables the TIMB channel 1 registers to synchronously control the output after the TIMB overflows. At each subsequent overflow, the TIMB channel registers (0 or 1) that control the output are the ones written to last. TSC0 controls and monitors the buffered output compare function, and TIMB channel 1 status and control register (TBSC1) is unused. While the MS0B bit is set, the channel 1 pin, PTB6/TCH1B, is available as a general-purpose input/output (I/O) pin.

#### NOTE:

In buffered output compare operation, do not write new output compare values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered output compares.

### 12.4.4 Pulse-Width Modulation (PWM)

By using the toggle-on-overflow feature with an output compare channel, the TIMB can generate a PWM signal. The value in the TIMB counter modulo registers determines the period of the PWM signal. The channel pin toggles when the counter reaches the value in the TIMB counter modulo registers. The time between overflows is the period of the PWM signal.

As Figure 12-3 shows, the output compare value in the TIMB channel registers determines the pulse width of the PWM signal. The time between overflow and output compare is the pulse width. Program the TIMB to clear the channel pin on output compare if the state of the PWM pulse is logic 1. Program the TIMB to set the pin if the state of the PWM pulse is logic 0.

Use these methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- When changing to a longer pulse width, enable TIMB overflow interrupts and write the new value in the TIMB overflow interrupt routine. The TIMB overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

**NOTE:**

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0 percent duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

## 12.4.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the PTB5/TCH0B pin. The TIMB channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIMB channel 0 status and control register (TBSC0) links channel 0 and channel 1. The TIMB channel 0 registers initially control the pulse width on the PTB5/TCH0B pin. Writing to the TIMB channel 1 registers enables the TIMB channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIMB channel registers (0 or 1) that control the pulse width are the ones written to last. TBSC0 controls and monitors the buffered PWM function, and TIMB channel 1 status and control register (TBSC1) is unused. While the MS0B bit is set, the channel 1 pin, PTB6/TCH1B, is available as a general-purpose I/O pin.

# **Serial Communications Interface (SCI)**

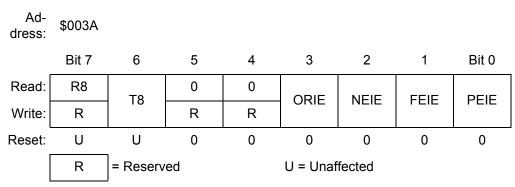

Figure 13-9. SCI Control Register 3 (SCC3)

#### R8 — Received Bit 8

When the SCI is receiving 9-bit characters, R8 is the read-only ninth bit (bit 8) of the received character. R8 is received at the same time that the SCDR receives the other 8 bits.

When the SCI is receiving 8-bit characters, R8 is a copy of the eighth bit (bit 7). Reset has no effect on the R8 bit.

#### T8 — Transmitted Bit 8

When the SCI is transmitting 9-bit characters, T8 is the read/write ninth bit (bit 8) of the transmitted character. T8 is loaded into the transmit shift register at the same time that the SCDR is loaded into the transmit shift register. Reset has no effect on the T8 bit.

#### ORIE — Receiver Overrun Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the receiver overrun bit, OR.

1 = SCI error CPU interrupt requests from OR bit enabled

0 = SCI error CPU interrupt requests from OR bit disabled

## NEIE — Receiver Noise Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the noise error bit, NE. Reset clears NEIE.

1 = SCI error CPU interrupt requests from NE bit enabled

0 = SCI error CPU interrupt requests from NE bit disabled

# Input/Output (I/O) Ports

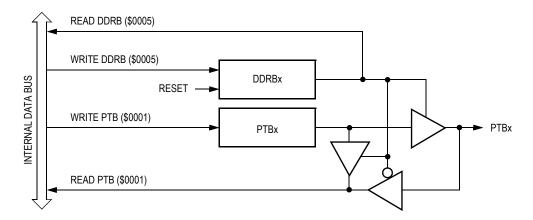

Figure 14-7. Port B I/O Circuit

When bit DDRBx is a logic 1, reading address \$0001 reads the PTBx data latch. When bit DDRBx is a logic 0, reading address \$0001 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. **Table 14-2** summarizes the operation of the port B pins.

| DDRB PTB<br>Bit Bit |                  | I/O Pin Mode               | Accesses<br>to DDRB | Accesses to PTB |                         |  |

|---------------------|------------------|----------------------------|---------------------|-----------------|-------------------------|--|

|                     | Dit              |                            | Read/Write          | Read            | Write                   |  |

| 0                   | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRB[6:0]           | Pin             | PTB[6:0] <sup>(3)</sup> |  |

| 1                   | Х                | Output                     | DDRB[6:0]           | PTB[6:0]        | PTB[6:0]                |  |

Table 14-2. Port B Pin Functions

### 14.5 Port C

Port C is a 2-bit special-purpose I/O port sharing its pins with the pulse width modulator for motor control module (PMC) FAULT input pins. These two pins mirror the state of FAULT1 and FAULT4 pins. Level changes on these input pins will be interpreted as fault conditions.

The port C data register contains a data latch for each of the two port pins.

**Technical Data**

MC68HC908MR8 — Rev 4.1

<sup>1.</sup> X = don't care

<sup>2.</sup> Hi-Z = high impedance

<sup>3.</sup> Writing affects data register, but does not affect input.

### 15.7 Monitor Mode

The COP is disabled in monitor mode when  $V_{DD}$  +  $V_{HI}$  is present on the  $\overline{IRQ}$  pin or on the  $\overline{RST}$  pin.

### 15.8 Wait Mode

The WAIT instruction puts the MCU in low power-consumption standby mode.

The COP continues to operate during wait mode.

# 15.9 Stop Mode

Stop mode turns off the COP prescaler clock. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

# 15.10 COP Module During Break Mode

The COP is disabled during a break interrupt when  $V_{DD} + V_{HI}$  is present on the  $\overline{RST}$  pin.

# Low-Voltage Inhibit (LVI)

With the LVIPWR bit in the configuration register programmed to logic 1, the LVI module is active after a STOP instruction.

With the LVIRST bit in the configuration register programmed to logic 1, the LVI module can generate a reset and bring the MCU out of stop mode.

# Power-On Reset (POR)

# 21.7 Memory Characteristics

| Characteristic                             | Symbol                             | Min | Тур                 | Max  | Unit   |

|--------------------------------------------|------------------------------------|-----|---------------------|------|--------|

| RAM data retention voltage                 | V <sub>RDR</sub>                   | 1.3 | _                   | _    | V      |

| FLASH program bus clock frequency          | _                                  | 1   | _                   | _    | MHz    |

| FLASH read bus clock frequency             | f <sub>Read</sub> <sup>(1)</sup>   | 32k | _                   | 8.4M | Hz     |

| FLASH page erase time                      | t <sub>Erase</sub> <sup>(2)</sup>  | 1   | _                   | _    | ms     |

| FLASH mass erase time                      | t <sub>MErase</sub> <sup>(3)</sup> | 4   | _                   | _    | ms     |

| FLASH PGM/ERASE to HVEN set up time        | t <sub>nvs</sub>                   | 10  | _                   | _    | μS     |

| FLASH high-voltage hold time               | t <sub>nvh</sub>                   | 5   | _                   | _    | μS     |

| FLASH high-voltage hold time (mass erase)  | t <sub>nvhl</sub>                  | 100 | _                   | _    | μS     |

| FLASH program hold time                    | t <sub>pgs</sub>                   | 5   | _                   | _    | μS     |

| FLASH program time                         | t <sub>PROG</sub>                  | 30  | _                   | 40   | μS     |

| FLASH return to read time                  | t <sub>rcv</sub> <sup>(4)</sup>    | 1   | _                   | _    | μS     |

| FLASH cumulative program HV period         | t <sub>HV</sub> <sup>(5)</sup>     | _   | _                   | 4    | ms     |

| FLASH row erase endurance <sup>(6)</sup>   | _                                  | 10k | 100k <sup>(7)</sup> | _    | Cycles |

| FLASH row program endurance <sup>(8)</sup> | _                                  | 10k | 100k <sup>(7)</sup> | _    | Cycles |

| FLASH data retention time <sup>(9)</sup>   | _                                  | 10  | 100 <sup>(10)</sup> | _    | Years  |

### Notes:

- 1.  $f_{\mbox{\scriptsize Read}}$  is defined as the frequency range for which the FLASH memory can be read.

- If the page erase time is longer than t<sub>Erase</sub> (Min), there is no erase-disturb, but it reduces the endurance of the FLASH memory.

- If the mass erase time is longer than t<sub>MErase</sub> (Min), there is no erase-disturb, but it reduces the endurance of the FLASH memory.

- 4. t<sub>rcv</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to logic 0.

- 5. t<sub>HV</sub> is defined as the cumulative high voltage programming time to the same row before next erase.

- ti<sub>HV</sub> must satisfy this condition: t<sub>nvs</sub> + t<sub>nvh</sub> + t<sub>pgs</sub> + (t<sub>PROG</sub> × 64) ≤ t<sub>HV</sub> max.

6. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase / program cycles.

- 7. FLASH endurance is a function of the temperature at which erasure occurs. Typical endurance degrades when the temperature while erasing is less than 25°C.

- 8. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase / program cycles.

- 9. The FLASH is guaranteed to retain data over the entire operating temperature range for at least the minimum time specified.

- 10. Freescale performs reliability testing for data retention. These tests are based on samples tested at elevated temperatures. Due to the higher activation energy of the elevated test temperature, calculated life tests correspond to more than 100 years of operation/storage at 55°C

# Ordering Information