Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI                                                                    |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908mr8vfae |

|                            |                                                                        |

# Table of Contents

|                | Section 3. Random-Access Memory (RAM)      |         |

|----------------|--------------------------------------------|---------|

| 3.1            | Contents                                   | 53      |

| 3.2            | Introduction                               | 53      |

| 3.3            | Functional Description                     | 53      |

|                | Section 4. FLASH Memory                    |         |

| 4.1            | Contents                                   | 55      |

| 4.2            | Introduction                               | 55      |

| 4.2.1          | Functional Description                     | 56      |

| 4.2.2          |                                            |         |

| 4.2.3          | 3                                          |         |

| 4.2.4          |                                            |         |

| 4.2.5          |                                            |         |

| 4.3            | FLASH Programming Algorithm                |         |

| 4.3.1<br>4.3.2 |                                            |         |

| 4.3.2          |                                            |         |

| 4.3.3          |                                            |         |

| 4.3.3          |                                            |         |

|                |                                            |         |

|                | Section 5. Configuration Register (CONFIG) |         |

| 5.1            | Contents                                   | 67      |

| 5.2            | Introduction                               | 67      |

| 5.3            | CONFIG                                     | 68      |

| 5.4            | CONFIG Bits                                | 68      |

|                | Section 6. Central Processor Unit (CPU)    |         |

| 6.1            | Contents                                   | 71      |

| 6.2            | Introduction                               |         |

| 6.3            | Features                                   |         |

| 6.4            | CPU Registers                              |         |

| 6.4.1          |                                            |         |

| 6.4.2          |                                            |         |

| 6.4.3          |                                            |         |

|                |                                            |         |

|                | MC68HC008MP8                               | Day 4 1 |

| 17.8 Stop Mode                                        |

|-------------------------------------------------------|

| Section 18. Analog-to-Digital Converter (ADC)         |

| 18.1 Contents                                         |

| 18.2 Introduction                                     |

| 18.3 Features                                         |

| 18.4 Functional Description                           |

| 18.4.1 ADC Port I/O Pins                              |

| 18.4.2 Voltage Conversion                             |

| 18.4.3 Conversion Time                                |

| 18.4.4 Continuous Conversion                          |

| 18.4.5 Result Justification                           |

| 18.5 Interrupts                                       |

| 18.6 Wait Mode                                        |

|                                                       |

| 18.7 Stop Mode                                        |

| 18.8 I/O Signals                                      |

| 18.8.1 ADC Voltage Reference Pin (V <sub>REFH</sub> ) |

| 18.8.3 ADC External Connection                        |

| 18.8.3.1 V <sub>REFH</sub>                            |

| 18.8.3.2 ANx                                          |

| 18.8.3.3 Grounding                                    |

| 18.9 I/O Registers319                                 |

| 18.9.1 ADC Status and Control Register                |

| 18.9.2 ADC Data Register High                         |

| 18.9.3 ADC Data Register Low                          |

| 18.9.4 ADC Clock Register                             |

| Section 19. Power-On Reset (POR)                      |

| 19.1 Contents                                         |

| 19.2 Introduction                                     |

| 19.3 Functional Description                           |

MC68HC908MR8 — Rev 4.1

# 1.5.4 External Interrupt Pin (IRQ)

IRQ is an asynchronous external interrupt pin. See **Section 16. External Interrupt (IRQ)**.

#### 1.5.5 CGM Power Supply Pins (VDDA and VSSA)

V<sub>DDA</sub> and V<sub>SSA</sub> are the power supply pins for the analog portion of the clock generator module (CGM) and the analog-to-digital converter (ADC). Decoupling of these pins should be per the digital supply. See Section 8. Clock Generator Module (CGM) and Section 18. Analog-to-Digital Converter (ADC).

## 1.5.6 ADC Reference Voltage Input Pin (V<sub>REFH</sub>)

V<sub>REFH</sub> is the power supply input for setting the reference voltage. See **Section 18. Analog-to-Digital Converter (ADC)**.

#### 1.5.7 External Filter Capacitor Pin (CGMXFC)

CGMXFC is an external filter capacitor connection for the CGM. See **Section 8. Clock Generator Module (CGM)**.

#### 1.5.8 Port A Input/Output (I/O) Pins (PTA6/ATD6-PTA0/ATD0)

Port A is a 7-bit special function port, sharing all of its pins with the analog-to-digital converter (ADC). On the 32-pin QFP package, all seven bits (PTA6/ATD6–PTA0/ATD0) of the port are available. On the 28-pin package, four bits (PTA3/ATD3–PTA0/ATD0) are available.

PTA3–PTA0 have high current source and sink capability. See **Section 14. Input/Output (I/O) Ports**.

MC68HC908MR8 — Rev 4.1 Technical Data

# **Memory Map**

| Addr.            | Register Name                             |                 | Bit 7                    | 6        | 5           | 4    | 3               | 2    | 1        | Bit 0   |  |

|------------------|-------------------------------------------|-----------------|--------------------------|----------|-------------|------|-----------------|------|----------|---------|--|

|                  | LVI Status and Control                    | Read:           | LVI-<br>OUT              | 0        | TRPS-<br>EL | 0    | 0               | 0    | 0        | 0       |  |

| \$FE0F           | Register (LVISCR)<br>See page <b>308.</b> | Write:          | R                        | R        | CL          | R    | R               | R    | R        | R       |  |

|                  | oce page coo.                             | Reset:          | 0                        | 0        | 0           | 0    | 0               | 0    | 0        | 0       |  |

| \$FF7E           | FLASH Block Protect<br>Register (FLBPR)   | Read:<br>Write: | BPR7                     | BPR6     | BPR5        | BPR4 | BPR3            | BPR2 | BPR1     | BPR0    |  |

|                  | See page <b>63</b> .                      |                 | Unaffected by reset      |          |             |      |                 |      |          |         |  |

|                  | COP Control Register                      | Read:           | Low byte of reset vector |          |             |      |                 |      |          |         |  |

| \$FFFF           | (COPCTL)                                  | Write:          | Clear COP counter        |          |             |      |                 |      |          |         |  |

|                  | See page <b>294.</b>                      | Reset:          | Unaffected by reset      |          |             |      |                 |      |          |         |  |

| U = Unaf<br>nate | fected X = Indetermi-                     |                 | R                        | = Reserv | /ed         | Bold | = Buff-<br>ered |      | = Unimpl | emented |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 10 of 10)

Technical Data MC68HC908MR8 — Rev 4.1

50 Memory Map Freescale Semiconductor

# Configuration Register (CONFIG)

MC68HC908MR8 — Rev 4.1

Table 6-2. Opcode Map

|            | Bit Mani             | pulation            | Branch             | Read-Modify-Write  |                     |                     | Control Register/Memory |                    |                    |                    |                   |                   |                   |                   |                   |                   |                   |                   |                  |

|------------|----------------------|---------------------|--------------------|--------------------|---------------------|---------------------|-------------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR                  | DIR                 | REL                | DIR                | INH                 | INH                 | IX1                     | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                    | 1                   | 2                  | 3                  | 4                   | 5                   | 6                       | 9E6                | 7                  | 8                  | 9                 | Α                 | В                 | C                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | 5<br>BRSET0<br>3 DIR | 4<br>BSET0<br>2 DIR | 3<br>BRA<br>2 REL  | 4<br>NEG<br>2 DIR  | 1<br>NEGA<br>1 INH  | 1<br>NEGX<br>1 INH  | 4<br>NEG<br>2 IX1       | 5<br>NEG<br>3 SP1  | 3<br>NEG<br>1 IX   | 7<br>RTI<br>1 INH  | 3<br>BGE<br>2 REL | SUB<br>2 IMM      | 3<br>SUB<br>2 DIR | 4<br>SUB<br>3 EXT | 4<br>SUB<br>3 IX2 | 5<br>SUB<br>4 SP2 | 3<br>SUB<br>2 IX1 | 4<br>SUB<br>3 SP1 | SUB<br>1 IX      |

| 1          | 5<br>BRCLR0<br>3 DIR | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL  | 5<br>CBEQ<br>3 DIR | 4<br>CBEQA<br>3 IMM | 4<br>CBEQX<br>3 IMM | 5<br>CBEQ<br>3 IX1+     | 6<br>CBEQ<br>4 SP1 | 4<br>CBEQ<br>2 IX+ | 4<br>RTS<br>1 INH  | 3<br>BLT<br>2 REL | 2<br>CMP<br>2 IMM | 3<br>CMP<br>2 DIR | 4<br>CMP<br>3 EXT | 4<br>CMP<br>3 IX2 | 5<br>CMP<br>4 SP2 | 3<br>CMP<br>2 IX1 | 4<br>CMP<br>3 SP1 | 2<br>CMP<br>1 IX |

| 2          | 5<br>BRSET1<br>3 DIR | 4<br>BSET1<br>2 DIR | 3<br>BHI<br>2 REL  |                    | 5<br>MUL<br>1 INH   | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH       |                    | 2<br>DAA<br>1 INH  |                    | 3<br>BGT<br>2 REL | SBC<br>2 IMM      | 3<br>SBC<br>2 DIR | 4<br>SBC<br>3 EXT | SBC<br>3 IX2      | 5<br>SBC<br>4 SP2 | 3<br>SBC<br>2 IX1 | 4<br>SBC<br>3 SP1 | SBC<br>1 IX      |

| 3          | 5<br>BRCLR1<br>3 DIR | 4<br>BCLR1<br>2 DIR | 3<br>BLS<br>2 REL  | 4<br>COM<br>2 DIR  | 1<br>COMA<br>1 INH  | 1<br>COMX<br>1 INH  | 4<br>COM<br>2 IX1       | 5<br>COM<br>3 SP1  | COM<br>1 IX        | 9<br>SWI<br>1 INH  | 3<br>BLE<br>2 REL | CPX<br>2 IMM      | 3<br>CPX<br>2 DIR | 4<br>CPX<br>3 EXT | 4<br>CPX<br>3 IX2 | 5<br>CPX<br>4 SP2 | 3<br>CPX<br>2 IX1 | 4<br>CPX<br>3 SP1 | CPX<br>1 IX      |

| 4          | 5<br>BRSET2<br>3 DIR | 4<br>BSET2<br>2 DIR |                    | 4<br>LSR<br>2 DIR  | 1<br>LSRA<br>1 INH  | 1<br>LSRX<br>1 INH  | 4<br>LSR<br>2 IX1       | 5<br>LSR<br>3 SP1  | 3<br>LSR<br>1 IX   | 2<br>TAP<br>1 INH  |                   | 2<br>AND<br>2 IMM | 3<br>AND<br>2 DIR |                   | 4<br>AND<br>3 IX2 | 5<br>AND<br>4 SP2 | 3<br>AND<br>2 IX1 | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          | 5<br>BRCLR2<br>3 DIR | 4<br>BCLR2<br>2 DIR | 3<br>BCS<br>2 REL  | 4<br>STHX<br>2 DIR | 3<br>LDHX<br>3 IMM  | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM      |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH | BIT<br>2 IMM      | 3<br>BIT<br>2 DIR | 4<br>BIT<br>3 EXT | 4<br>BIT<br>3 IX2 | 5<br>BIT<br>4 SP2 | 3<br>BIT<br>2 IX1 | 4<br>BIT<br>3 SP1 | 2<br>BIT<br>1 IX |

| 6          | 5<br>BRSET3<br>3 DIR | BSET3<br>2 DIR      | 3<br>BNE<br>2 REL  | 4<br>ROR<br>2 DIR  | 1<br>RORA<br>1 INH  | 1<br>RORX<br>1 INH  | 4<br>ROR<br>2 IX1       | 5<br>ROR<br>3 SP1  | 3<br>ROR<br>1 IX   | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM | 3<br>LDA<br>2 DIR | 4<br>LDA<br>3 EXT | 4<br>LDA<br>3 IX2 | 5<br>LDA<br>4 SP2 | 3<br>LDA<br>2 IX1 | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          | 5<br>BRCLR3<br>3 DIR | 4<br>BCLR3<br>2 DIR | 3<br>BEQ<br>2 REL  | 4<br>ASR<br>2 DIR  | 1<br>ASRA<br>1 INH  | 1<br>ASRX<br>1 INH  | 4<br>ASR<br>2 IX1       | 5<br>ASR<br>3 SP1  | 3<br>ASR<br>1 IX   | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH | AIS<br>2 IMM      | 3<br>STA<br>2 DIR | 4<br>STA<br>3 EXT | 4<br>STA<br>3 IX2 | 5<br>STA<br>4 SP2 | 3<br>STA<br>2 IX1 | 4<br>STA<br>3 SP1 | 2<br>STA<br>1 IX |

| 8          | 5<br>BRSET4<br>3 DIR | 4<br>BSET4<br>2 DIR | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH  | 1<br>LSLX<br>1 INH  | 4<br>LSL<br>2 IX1       | 5<br>LSL<br>3 SP1  | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | EOR<br>2 IMM      | 3<br>EOR<br>2 DIR | 4<br>EOR<br>3 EXT | 4<br>EOR<br>3 IX2 | 5<br>EOR<br>4 SP2 | 3<br>EOR<br>2 IX1 | 4<br>EOR<br>3 SP1 | 2<br>EOR<br>1 IX |

| 9          | 5<br>BRCLR4<br>3 DIR | 4<br>BCLR4<br>2 DIR | 3<br>BHCS<br>2 REL | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH  | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1       | 5<br>ROL<br>3 SP1  | 3<br>ROL<br>1 IX   | 2<br>PSHX<br>1 INH |                   | ADC<br>2 IMM      | 3<br>ADC<br>2 DIR | 4<br>ADC<br>3 EXT | 4<br>ADC<br>3 IX2 | 5<br>ADC<br>4 SP2 | 3<br>ADC<br>2 IX1 | 4<br>ADC<br>3 SP1 | 2<br>ADC<br>1 IX |

| А          | 5<br>BRSET5<br>3 DIR | 4<br>BSET5<br>2 DIR | 3<br>BPL<br>2 REL  | 4<br>DEC<br>2 DIR  | 1<br>DECA<br>1 INH  | 1<br>DECX<br>1 INH  | 4<br>DEC<br>2 IX1       | 5<br>DEC<br>3 SP1  | 3<br>DEC<br>1 IX   | 2<br>PULH<br>1 INH | 2<br>CLI<br>1 INH | 2<br>ORA<br>2 IMM | 3<br>ORA<br>2 DIR | 4<br>ORA<br>3 EXT | 4<br>ORA<br>3 IX2 | 5<br>ORA<br>4 SP2 | 3<br>ORA<br>2 IX1 | 4<br>ORA<br>3 SP1 | 2<br>ORA<br>1 IX |

| В          | 5<br>BRCLR5<br>3 DIR | 4<br>BCLR5<br>2 DIR | 3<br>BMI<br>2 REL  | 5<br>DBNZ<br>3 DIR | 3<br>DBNZA<br>2 INH | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1      | _                  | 4<br>DBNZ<br>2 IX  | 2<br>PSHH<br>1 INH | 2<br>SEI<br>1 INH | 2<br>ADD<br>2 IMM | 3<br>ADD<br>2 DIR | _                 | 4<br>ADD<br>3 IX2 | 5<br>ADD<br>4 SP2 | 3<br>ADD<br>2 IX1 | 4<br>ADD<br>3 SP1 | 2<br>ADD<br>1 IX |

| С          | 5<br>BRSET6<br>3 DIR | BSET6<br>2 DIR      | 3<br>BMC<br>2 REL  | 4<br>INC<br>2 DIR  | 1<br>INCA<br>1 INH  | 1<br>INCX<br>1 INH  | 4<br>INC<br>2 IX1       | 5<br>INC<br>3 SP1  | 3<br>INC<br>1 IX   | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR |                   | 4<br>JMP<br>3 IX2 |                   | 3<br>JMP<br>2 IX1 |                   | JMP<br>1 IX      |

| D          | 5<br>BRCLR6<br>3 DIR | 4<br>BCLR6<br>2 DIR | 3<br>BMS<br>2 REL  | 3<br>TST<br>2 DIR  | 1<br>TSTA<br>1 INH  | 1<br>TSTX<br>1 INH  | 3<br>TST<br>2 IX1       | 4<br>TST<br>3 SP1  | 2<br>TST<br>1 IX   |                    | 1<br>NOP<br>1 INH | 4<br>BSR<br>2 REL | JSR<br>2 DIR      |                   | 6<br>JSR<br>3 IX2 |                   | 5<br>JSR<br>2 IX1 |                   | JSR<br>1 IX      |

| E          | 5<br>BRSET7<br>3 DIR | 4<br>BSET7<br>2 DIR | 3<br>BIL<br>2 REL  |                    | 5<br>MOV<br>3 DD    | MOV<br>2 DIX+       | 4<br>MOV<br>3 IMD       |                    | 4<br>MOV<br>2 IX+D | 1<br>STOP<br>1 INH | *                 | 2<br>LDX<br>2 IMM | 3<br>LDX<br>2 DIR | _                 | 4<br>LDX<br>3 IX2 | 5<br>LDX<br>4 SP2 | 3<br>LDX<br>2 IX1 | 4<br>LDX<br>3 SP1 | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7<br>3 DIR | BCLR7<br>2 DIR      | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH  | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1       | 4<br>CLR<br>3 SP1  | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | STX<br>2 DIR      | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | 5<br>STX<br>4 SP2 | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | STX<br>1 IX      |

| Inherent       | REL                                              | Relative                                               |

|----------------|--------------------------------------------------|--------------------------------------------------------|

| Immediate      | IX                                               | Indexed, No Offset                                     |

| Direct         | IX1                                              | Indexed, 8-Bit Offset                                  |

| Extended       | IX2                                              | Indexed, 16-Bit Offset                                 |

| Direct-Direct  | IMD                                              | Immediate-Direct                                       |

| Indexed-Direct | DIX+                                             | Direct-Indexed                                         |

|                | Immediate<br>Direct<br>Extended<br>Direct-Direct | Immediate IX Direct IX1 Extended IX2 Direct-Direct IMD |

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment SP1 SP2 IX+

High Byte of Opcode in Hexadecimal LSB 5 Cycles BRSET0 Opcode Mnemonic 3 DIR Number of Bytes / Addressing Mode Low Byte of Opcode in Hexadecimal

<sup>\*</sup>Pre-byte for stack pointer indexed instructions

# System Integration Module (SIM)

#### 7.4.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

Because the MC68HC08MR8 has stop mode disabled by bit 1 in the CONFIG register, execution of the STOP instruction will cause an illegal opcode reset if stop mode has not been enabled by setting CONFIG register bit 1.

#### 7.4.2.4 Illegal Address Reset

An opcode fetch from addresses other than FLASH, I/O, or RAM addresses generates an illegal address reset (unimplemented locations within memory map). The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset.

#### 7.4.2.5 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the LVI<sub>LVRX</sub> voltage and remains at or below that level for at least nine consecutive CPU cycles. The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RST) is held low while the SIM counter counts out 4096 CGMXCLK cycles. Sixty-four CGMXCLK cycles later, the CPU is released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the RST pin for all internal reset sources.

The operating range of the VCO is programmable for a wide range of frequencies and for maximum immunity to external noise, including supply and CGMXFC noise. The VCO frequency is bound to a range from roughly one-half to twice the center-of-range frequency,  $f_{VRS}$ . Modulating the voltage on the CGMXFC pin changes the frequency within this range. By design,  $f_{VRS}$  is equal to the nominal center-of-range frequency,  $f_{NOM}$ , (4.9152 MHz) times a linear factor L, or (L)  $f_{NOM}$ .

CGMRCLK is the PLL reference clock, a buffered version of CGMXCLK. CGMRCLK runs at a frequency,  $f_{RCLK}$ , and is fed to the PLL through a buffer. The buffer output is the final reference clock, CGMRDV, running at a frequency,  $f_{RDV} = f_{RCLK}$ .

The VCO's output clock, CGMVCLK, running at a frequency  $f_{VCLK}$ , is fed back through a programmable modulo divider. The modulo divider reduces the VCO clock by a factor, N. The divider's output is the VCO feedback clock, CGMVDV, running at a frequency,  $f_{VDV} = f_{VCLK/N}$ . See **8.4.2.4 Programming the PLL** for more information.

The phase detector then compares the VCO feedback clock, CGMVDV, with the final reference clock, CGMRDV. A correction pulse is generated based on the phase difference between the two signals. The loop filter then slightly alters the dc voltage on the external capacitor connected to CGMXFC based on the width and direction of the correction pulse. The filter can make fast or slow corrections depending on its mode, described in **8.4.2.2 Acquisition and Tracking Modes**. The value of the external capacitor and the reference frequency determines the speed of the corrections and the stability of the PLL.

The lock detector compares the frequencies of the VCO feedback clock, CGMVDV, and the final reference clock, CGMRDV. Therefore, the speed of the lock detector is directly proportional to the final reference frequency, f<sub>RDV</sub>. The circuit determines the mode of the PLL and the lock condition based on this comparison.

# **Clock Generator Module (CGM)**

## 8.5.4 PLL Analog Power Pin (V<sub>DDA</sub>)

$V_{DDA}$  is a power pin used by the analog portions of the PLL. Connect the  $V_{DDA}$  pin to the same voltage potential as the  $V_{DD}$  pin.

**NOTE:** Route  $V_{DDA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

#### 8.5.5 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and enables the oscillator and PLL.

#### 8.5.6 Crystal Output Frequency Signal (CGMXCLK)

CGMXCLK is the crystal oscillator output signal. It runs at the full speed of the crystal ( $f_{XCLK}$ ) and comes directly from the crystal oscillator circuit. **Figure 8-3** shows only the logical relation of CGMXCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of CGMXCLK is unknown and may depend on the crystal and other external factors. Also, the frequency and amplitude of CGMXCLK can be unstable at startup.

#### 8.5.7 CGM Base Clock Output (CGMOUT)

CGMOUT is the clock output of the CGM. This signal goes to the SIM, which generates the MCU clocks. CGMOUT is a 50 percent duty cycle clock running at twice the bus frequency. CGMOUT is software programmable to be either the oscillator output, CGMXCLK, divided by two or the VCO clock, CGMVCLK, divided by two.

#### 8.5.8 CGM CPU Interrupt (CGMINT)

CGMINT is the interrupt signal generated by the PLL lock detector.

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6—\$FFFD, the host fails to satisfy the security feature. The MCU remains in monitor mode, but reading a ROM location returns an invalid value and trying to execute code from ROM causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

#### **NOTE:**

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$60 is set. If it is, then the correct security code has been entered and ROM can be accessed.

If the security sequence fails, the device can be reset (via power-pin reset only) and brought up in monitor mode to attempt another entry.

After failing the security sequence, the FLASH memory can also be bulk erased by executing an erase routine that was downloaded into internal RAM. The bulk erase operation clears the security code locations so that all eight security bytes become \$FF.

197

## Timer Interface A (TIMA)

counter reaches the value in the registers of an output compare channel, the TIMA can set, clear, or toggle the channel pin. Output compares can generate TIMA CPU interrupt requests.

#### 11.4.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in **11.4.3 Output Compare**. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIMA channel registers.

An unsynchronized write to the TIMA channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIMA overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIMA may pass the new value before it is written.

Use these methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current output compare pulse. The interrupt routine has until the end of the counter overflow period to write the new value.

- When changing to a larger output compare value, enable TIMA overflow interrupts and write the new value in the TIMA overflow interrupt routine. The TIMA overflow interrupt occurs at the end of the current counter overflow period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same counter overflow period.

#### 11.4.3.2 Buffered Output Compare

Channels 0 and 1 can be linked to form a buffered output compare channel whose output appears on the PTB3/TCH0A pin. The TIMA channel registers of the linked pair alternately control the output.

**Technical Data**

MC68HC908MR8 — Rev 4.1

# Timer Interface B (TIMB)

#### 12.4.3 Output Compare

With the output compare function, the TIMB can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIMB can set, clear, or toggle the channel pin. Output compares can generate TIMB CPU interrupt requests.

#### 12.4.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in **12.4.3 Output Compare**. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIMB channel registers.

An unsynchronized write to the TIMB channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIMB overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIMB may pass the new value before it is written.

Use these methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current output compare pulse. The interrupt routine has until the end of the counter overflow period to write the new value.

- When changing to a larger output compare value, enable TIMB

overflow interrupts and write the new value in the TIMB overflow

interrupt routine. The TIMB overflow interrupt occurs at the end of

the current counter overflow period. Writing a larger value in an

output compare interrupt routine (at the end of the current pulse)

could cause two output compares to occur in the same counter

overflow period.

# Timer Interface B (TIMB)

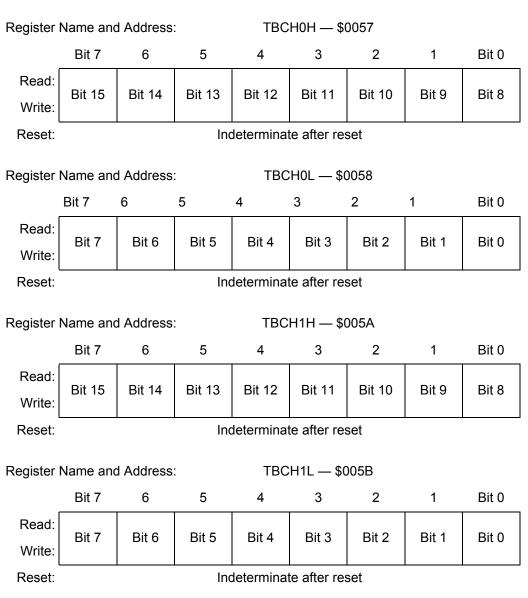

In input capture mode (MSxB–MSxA = 0:0), reading the high byte of the TIMB channel x registers (TBCHxH) inhibits input captures until the low byte (TBCHxL) is read.

In output compare mode (MSxB–MSxA  $\neq$  0:0), writing to the high byte of the TIMB channel x registers (TBCHxH) inhibits output compares until the low byte (TBCHxL) is written.

Figure 12-9. TIMB Channel Registers (TBCH0H/L-TBCH1H/L)

- Interrupt-driven operation with eight interrupt flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

# 13.4 Functional Description

The SCI allows full-duplex, asynchronous, NRZ serial communication among the MCU and remote devices, including other MCUs. The transmitter and receiver of the SCI operate independently, although they use the same baud rate generator. During normal operation, the CPU monitors the status of the SCI, writes the data to be transmitted, and processes received data.

**Figure 13-1** shows the structure of the SCI module. **Figure 13-2** provides a summary of the input/output (I/O) registers.

# Serial Communications Interface (SCI)

**Table 13-7. SCI Baud Rate Selection Examples**

| SCP1:SCP0 | Prescaler<br>Divisor<br>(PD) | SCR2:SCR1:<br>SCR0 | Baud Rate<br>Divisor (BD) | Baud Rate<br>(f <sub>OP</sub> = 7.3728 MHz) | Baud Rate<br>(f <sub>OP</sub> = 8.00 MHz) |

|-----------|------------------------------|--------------------|---------------------------|---------------------------------------------|-------------------------------------------|

| 00        | 1                            | 000                | 1                         | 115,200.00                                  | 125,000.00                                |

| 00        | 1                            | 001                | 2                         | 57,600.00                                   | 62,500.00                                 |

| 00        | 1                            | 010                | 4                         | 28,800.00                                   | 31,250.00                                 |

| 00        | 1                            | 011                | 8                         | 14,400.00                                   | 15,625.00                                 |

| 00        | 1                            | 100                | 16                        | 7200.00                                     | 7812.50                                   |

| 00        | 1                            | 101                | 32                        | 3600.00                                     | 3906.25                                   |

| 00        | 1                            | 110                | 64                        | 1800.00                                     | 1953.13                                   |

| 00        | 1                            | 111                | 128                       | 900.00                                      | 976.56                                    |

| 01        | 3                            | 000                | 1                         | 38,400.00                                   | 41,666.67                                 |

| 01        | 3                            | 001                | 2                         | 19,200.00                                   | 20,833.33                                 |

| 01        | 3                            | 010                | 4                         | 9600.00                                     | 10,416.67                                 |

| 01        | 3                            | 011                | 8                         | 4800.00                                     | 5208.33                                   |

| 01        | 3                            | 100                | 16                        | 2400.00                                     | 2604.17                                   |

| 01        | 3                            | 101                | 32                        | 1200.00                                     | 1302.08                                   |

| 01        | 3                            | 110                | 64                        | 600.00                                      | 651.04                                    |

| 01        | 3                            | 111                | 128                       | 300.00                                      | 325.52                                    |

| 10        | 4                            | 000                | 1                         | 28,800.00                                   | 31,250.00                                 |

| 10        | 4                            | 001                | 2                         | 14,400.00                                   | 15,625.50                                 |

| 10        | 4                            | 010                | 4                         | 7200.00                                     | 7812.50                                   |

| 10        | 4                            | 011                | 8                         | 3600.00                                     | 3906.25                                   |

| 10        | 4                            | 100                | 16                        | 1800.00                                     | 1953.13                                   |

| 10        | 4                            | 101                | 32                        | 900.00                                      | 976.56                                    |

| 10        | 4                            | 110                | 64                        | 450.00                                      | 488.28                                    |

| 10        | 4                            | 111                | 128                       | 225.00                                      | 244.14                                    |

| 11        | 13                           | 000                | 1                         | 8861.54                                     | 9615.38                                   |

| 11        | 13                           | 001                | 2                         | 4430.77                                     | 4807.69                                   |

| 11        | 13                           | 010                | 4                         | 2215.38                                     | 2403.85                                   |

| 11        | 13                           | 011                | 8                         | 1107.69                                     | 1201.92                                   |

| 11        | 13                           | 100                | 16                        | 553.85                                      | 600.96                                    |

| 11        | 13                           | 101                | 32                        | 276.92                                      | 300.48                                    |

| 11        | 13                           | 110                | 64                        | 138.46                                      | 150.24                                    |

| 11        | 13                           | 111                | 128                       | 69.23                                       | 75.12                                     |

Technical Data MC68HC908MR8 — Rev 4.1

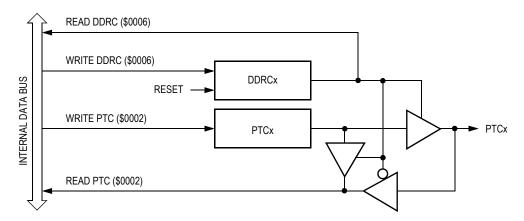

Figure 14-10. Port C I/O Circuit

When bit DDRCx is a logic 1, reading address \$0002 reads the PTCx data latch. When bit DDRCx is a logic 0, reading address \$0002 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. **Table 14-3** summarizes the operation of the port C pins.

**Table 14-3. Port C Pin Functions**

| DDRC | PTC              | I/O Pin Mode               | Accesses to DDRC | Access   | es to PTC               |

|------|------------------|----------------------------|------------------|----------|-------------------------|

| Bit  | Bit              | I/O FIII WIOGE             | Read/Write       | Read     | Write                   |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRC[1:0]        | Pin      | PTC[1:0] <sup>(3)</sup> |

| 1    | Х                | Output                     | DDRC[1:0]        | PTC[1:0] | PTC[1:0]                |

- 1. X = don't care

- 2. Hi-Z = high impedance on PTC0 and a pull-down  $R_{PD}$  on PTC1

- 3. Writing affects data register, but does not affect input.

## Technical Data — MC68HC908MR8

# Section 16. External Interrupt (IRQ)

#### 16.1 Contents

| 16.2 | Introduction                    | 297 |

|------|---------------------------------|-----|

| 16.3 | Features                        | 297 |

| 16.4 | Functional Description          | 298 |

| 16.5 | IRQ Pin                         | 301 |

| 16.6 | IRQ Module During Wait Mode     | 302 |

| 16.7 | IRQ Module During Stop Mode     | 302 |

| 16.8 | IRQ Module During Break Mode    | 302 |

| 16.9 | IRQ Status and Control Register | 303 |

## 16.2 Introduction

This section describes the external interrupt module, which supports external interrupt functions.

#### 16.3 Features

Features of the IRQ module include:

- A dedicated external interrupt pin, IRQ

- · Hysteresis buffers

MC68HC908MR8 — Rev 4.1

## Technical Data — MC68HC908MR8

# **Revision History**

#### **Contents**

| Introduction                                                      | .357 |

|-------------------------------------------------------------------|------|

| Changes from Rev 3.0 published in April 2002 to Rev 4.0 published | ni b |

| July 2002                                                         | .357 |

## Introduction

This section contains the revision history for the MC68HC908MR8 advance information data book.

# Changes from Rev 3.0 published in April 2002 to Rev 4.0 published in July 2002

| Section                      | Page (in Rev 0.4) | Description of change                                                                                       |

|------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------|

| Electrical<br>Specifications | 343               | $V_{OL}$ max updated for $I_{Load}$ = 15 mA<br>Stop $I_{DD}$ limits updated for different temperature specs |

MC68HC908MR8 — Rev 4.0

- **variable** A value that changes during the course of program execution.

- **VCO** See voltage-controlled oscillator.

- **vector** A memory location that contains the address of the beginning of a subroutine written to service an interrupt or reset.

- **voltage-controlled oscillator (VCO)** A circuit that produces an oscillating output signal of a frequency that is controlled by a dc voltage applied to a control input.

- **waveform** A graphical representation in which the amplitude of a wave is plotted against time.

- wired-OR Connection of circuit outputs so that if any output is high, the connection point is high.

- word A set of two bytes (16 bits).

- write The transfer of a byte of data from the CPU to a memory location.

- **X** The lower byte of the index register (H:X) in the CPU08.

- **Z** The zero bit in the condition code register of the CPU08. The CPU08 sets the zero bit when an arithmetic operation, logical operation, or data manipulation produces a result of \$00.

MC68HC908MR8 — Rev 4.1