Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 67MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 1x20b, 1x12b; D/A 4x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 68-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5566lti-017 |

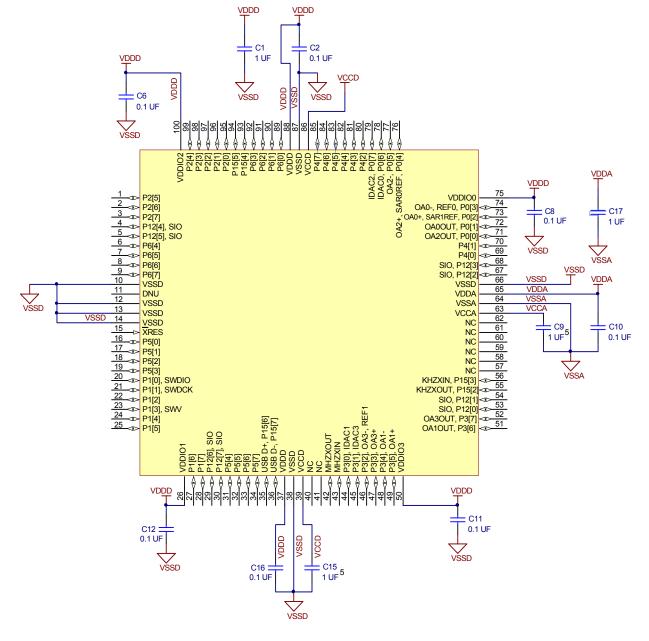

Figure 2-3. Example Schematic for 100-pin TQFP Part with Power Connections

**Note** The two V<sub>CCD</sub> pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-4.

#### Note

5.  $10 \mu F$  is required for sleep mode. See Table 11-3.

The Cortex-M3 does not support ARM instructions.

- Bit-band support for the SRAM region. Atomic bit-level write and read operations for SRAM addresses.

- Unaligned data storage and access. Contiguous storage of data of different byte lengths.

- Operation at two privilege levels (privileged and user) and in two modes (thread and handler). Some instructions can only be executed at the privileged level. There are also two stack pointers: Main (MSP) and Process (PSP). These features support a multitasking operating system running one or more user-level processes.

- Extensive interrupt and system exception support.

#### 4.1.2 Cortex-M3 Operating Modes

The Cortex-M3 operates at either the privileged level or the user level, and in either the thread mode or the handler mode. Because the handler mode is only enabled at the privileged level, there are actually only three states, as shown in Table 4-1.

Table 4-1. Operational Level

| Condition            | Privileged   | User        |

|----------------------|--------------|-------------|

| Running an exception | Handler mode | Not used    |

| Running main program | Thread mode  | Thread mode |

At the user level, access to certain instructions, special registers, configuration registers, and debugging components is blocked. Attempts to access them cause a fault exception. At the privileged level, access to all instructions and registers is allowed.

The processor runs in the handler mode (always at the privileged level) when handling an exception, and in the thread mode when not

## 4.1.3 CPU Registers

The Cortex-M3 CPU registers are listed in Table 4-2. Registers R0-R15 are all 32 bits wide.

Table 4-2. Cortex M3 CPU Registers

| Register | Description                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0-R12   | General purpose registers R0-R12 have no special architecturally defined uses. Most instructions that specify a general purpose register specify R0-R12.                  |

|          | ■ Low registers: Registers R0-R7 are accessible by all instructions that specify a general purpose register.                                                              |

|          | ■ High registers: Registers R8-R12 are accessible by all 32-bit instructions that specify a general purpose register; they are not accessible by all 16-bit instructions. |

Table 4-2. Cortex M3 CPU Registers (continued)

| Register  | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R13       | R13 is the stack pointer register. It is a banked register that switches between two 32-bit stack pointers: the main stack pointer (MSP) and the process stack pointer (PSP). The PSP is used only when the CPU operates at the user level in thread mode. The MSP is used in all other privilege levels and modes. Bits[0:1] of the SP are ignored and considered to be 0, so the SP is always aligned to a word (4 byte) boundary. |

| R14       | R14 is the link register (LR). The LR stores the return address when a subroutine is called.                                                                                                                                                                                                                                                                                                                                         |

| R15       | R15 is the program counter (PC). Bit 0 of the PC is ignored and considered to be 0, so instructions are always aligned to a half word (2 byte) boundary.                                                                                                                                                                                                                                                                             |

| xPSR      | The program status registers are divided into three status registers, which are accessed either together or separately:                                                                                                                                                                                                                                                                                                              |

|           | ■ Application program status register (APSR) holds program execution status bits such as zero, carry, negative, in bits[27:31].                                                                                                                                                                                                                                                                                                      |

|           | ■ Interrupt program status register (IPSR) holds the current exception number in bits[0:8].                                                                                                                                                                                                                                                                                                                                          |

|           | ■ Execution program status register (EPSR) holds control bits for interrupt continuable and IF-THEN instructions in bits[10:15] and [25:26]. Bit 24 is always set to 1 to indicate Thumb mode. Trying to clear it causes a fault exception.                                                                                                                                                                                          |

| PRIMASK   | A 1-bit interrupt mask register. When set, it allows only the nonmaskable interrupt (NMI) and hard fault exception. All other exceptions and interrupts are masked.                                                                                                                                                                                                                                                                  |

| FAULTMASK | A 1-bit interrupt mask register. When set, it allows only the NMI. All other exceptions and interrupts are masked.                                                                                                                                                                                                                                                                                                                   |

| BASEPRI   | A register of up to nine bits that define the masking priority level. When set, it disables all interrupts of the same or higher priority value. If set to 0 then the masking function is disabled.                                                                                                                                                                                                                                  |

| CONTROL   | A 2-bit register for controlling the operating mode.                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Bit 0: 0 = privileged level in thread mode,<br>1 = user level in thread mode.                                                                                                                                                                                                                                                                                                                                                        |

|           | Bit 1: 0 = default stack (MSP) is used,<br>1 = alternate stack is used. If in thread mode or<br>user level then the alternate stack is the PSP.<br>There is no alternate stack for handler mode; the<br>bit must be 0 while in handler mode.                                                                                                                                                                                         |

The fast timewheel is a 100 kHz, 5-bit counter clocked by the ILO that can also be used to generate periodic interrupts. The fast timewheel settings are programmable, and the counter automatically resets when the terminal count is reached. This enables flexible, periodic interrupts to the CPU at a higher rate than is allowed using the central timewheel. The fast timewheel can generate an optional interrupt each time the terminal count is reached. The 33 kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768 kHz ECO clock with no need for a crystal. The fast timewheel cannot be used as a wakeup source and must be turned off before entering sleep or hibernate mode.

#### 6.1.2 External Oscillators

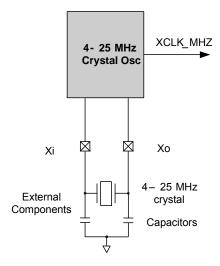

#### 6.1.2.1 MHz External Crystal Oscillator

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports crystals in the range of 4 to 25 MHz. When used in conjunction with the PLL, it can generate CPU and system clocks up to the device's maximum frequency (see Phase-Locked Loop on page 19). The MHzECO with a 24 MHz crystal can be used with the clock doubler to generate a 48 MHz clock for the USB. If a crystal is not used then Xi must be shorted to ground and Xo must be left floating. MHzECO accuracy depends on the crystal chosen.

Figure 6-2. MHzECO Block Diagram

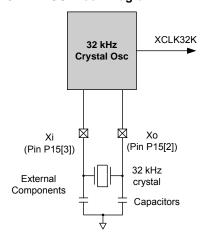

#### 6.1.2.2 32.768 kHz ECO

The 32.768 kHz external crystal oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768 kHz watch crystal (see Figure 6-3). The RTC uses a 1 second interrupt to implement the RTC functionality in firmware. The oscillator works in two distinct power modes. This allows users to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

Figure 6-3. 32kHzECO Block Diagram

It is recommended that the external 32.768-kHz watch crystal have a load capacitance (CL) of 6 pF or 12.5 pF. Check the crystal manufacturer's datasheet. The two external capacitors, CL1 and CL2, are typically of the same value, and their total capacitance, CL1CL2 / (CL1 + CL2), including pin and trace capacitance, should equal the crystal CL value. For more information, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators. See also pin capacitance specifications in the "GPIO" section on page 61.

#### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and UDBs. While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

### 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

- The system clock is used to select and supply the fastest clock in the system for general system clock requirements and clock synchronization of the PSoC device.

- Bus clock 16-bit divider uses the system clock to generate the system's bus clock used for data transfers and the CPU. The CPU clock is directly derived from the bus clock.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the UDBs and fixed function timer/counter/PWMs can also generate clocks.

- Four 16-bit clock dividers generate clocks for the analog system components that require clocking, such as ADCs and mixers. The analog clock dividers include skew control to ensure that critical analog events do not occur simultaneously with digital switching events. This is done to reduce analog system noise.

Each clock divider consists of an 8-input multiplexer, a 16-bit clock divider (divide by 2 and higher) that generates ~50% duty cycle clocks, system clock resynchronization logic, and deglitch logic. The outputs from each digital clock tree can be routed into the digital system interconnect and then brought back into the clock system as an input, allowing clock chaining of up to 32 bits.

#### 6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely asynchronously from the main clock network. The USB logic contains a synchronous bus interface to the chip, while running on an asynchronous clock to process USB data. The USB logic requires a 48 MHz frequency. This frequency can be generated from different sources, including DSI clock at 48 MHz or doubled value of 24 MHz from the MHzECO or DSI signal.

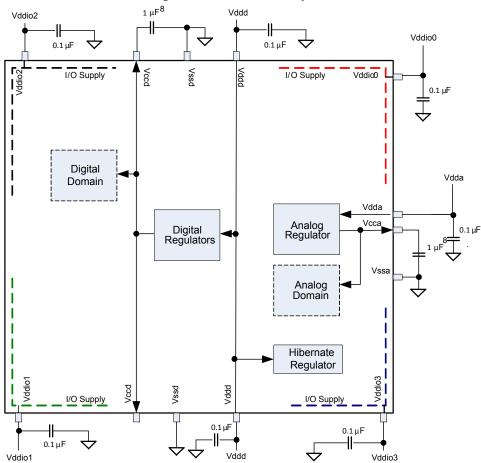

### 6.2 Power System

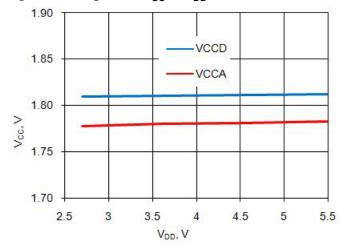

The power system consists of separate analog, digital, and I/O supply pins, labeled VDDA, VDDD, and VDDIO $_{\rm X}$ , respectively. It also includes two internal 1.8 V regulators that provide the digital (VCCD) and analog (VCCA) supplies for the internal core logic. The output pins of the regulators (VCCD and VCCA) and the VDDIO pins must have capacitors connected as shown in Figure 6-4 (10  $\mu F$  is required for sleep mode. See Table 11-3). The two VCCD pins must be shorted together, with as short a trace as possible. The power system also contains a hibernate regulator.

Figure 6-4. PSoC Power System

**Note** The two V<sub>CCD</sub> pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-4.

#### Note

8.  $10 \, \mu F$  is required for sleep mode. See Table 11-3.

#### 6.2.1 Power Modes

PSoC 5 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low power and portable devices.

PSoC 5 power modes, in order of decreasing power consumption are:

- Active

- Alternate active

- Sleep

- Hibernate

Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from reset. Figure 6-5 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all VDDIO supplies are at valid voltage levels and interrupts are enabled.

Table 6-2. Power Modes

| <b>Power Modes</b>  | Description                                                                                                                                                                                                   | <b>Entry Condition</b>                     | Wakeup Source       | Active Clocks         | Regulator                        |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------|-----------------------|----------------------------------|

| Active              | Primary mode of operation, all peripherals available (programmable)                                                                                                                                           | Wakeup, reset,<br>manual register<br>entry | Any interrupt       | Any<br>(programmable) | All regulators available.        |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have<br>fewer peripherals active to<br>reduce power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off | Manual register<br>entry                   | Any interrupt       | Any<br>(programmable) | All regulators available.        |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                         | Manual register entry                      | CTW <sup>[10]</sup> | ILO                   | All regulators available.        |

| Hibernate           | All subsystems automatically disabled Lowest power consuming mode with all peripherals and internal regulators disabled, except hibernate regulator is enabled Configuration and memory contents retained     | Manual register<br>entry                   |                     |                       | Only hibernate regulator active. |

Table 6-3. Power Modes Wakeup Time and Power Consumption

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(Typ)     | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources | Reset<br>Sources |

|---------------------|----------------|----------------------|-------------------|----------------------|---------------------|----------------------------|----------------|------------------|

| Active              | -              | 6 mA <sup>[9]</sup>  | Yes               | All                  | All                 | All                        | _              | All              |

| Alternate<br>Active | _              | -                    | User<br>defined   | All                  | All                 | All                        | _              | All              |

| Sleep               | 125 µs typ     | 2 μA <sup>[10]</sup> | No                | None                 | None                | ILO                        | CTW            | XRES             |

| Hibernate           | _              | 300 nA               | No                | None                 | None                | None                       | _              | XRES             |

#### Notes

Document Number: 001-66235 Rev. \*D Page 22 of 111

<sup>9.</sup> Bus clock off. Execute from CPU instruction buffer at 6 MHz. See Table 11-2 on page 58.

During sleep mode, the CTW generates periodic interrupts to wake up the device. This affects the average current, which is a composite of the sleep mode current and active mode current, and the time spent in each mode. With the maximum wakeup interval of 128 ms, and at wakeup the CPU executes only the standard PSoC Creator sleep API (for a duty cycle of 0.2%), the average current draw is typically 35 μA.

# PSoC® 5: CY8C55 Family Datasheet

- Features supported by both GPIO and SIO:

- ☐ Separate I/O supplies and voltages for up to four groups of I/O

- □ Digital peripherals use DSI to connect the pins

- □ Input or output or both for CPU and DMA

- □ Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- □ Slew rate controlled digital output drive mode

- □ Access port control and configuration registers on either port basis or pin basis

- □ Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- □ LCD segment drive on LCD equipped devices

- ☐ CapSense on CapSense equipped devices<sup>[11]</sup>

- ☐ Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 2.7 V

- Additional features only provided on SIO pins:

- ☐ Higher drive strength than GPIO

- ☐ Hot swap capability (5 V tolerance at any operating VDD)

- □ Programmable and regulated high input and output drive levels down to 1.2 V

- □ No analog input or LCD capability

- Over voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 I/O

- □ Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- □ Digital output (CMOS) drive mode

- □ Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

#### 6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality in addition to their GPIO or SIO functionality. The specific special function pins are listed in "Pinouts" on page 5. The special features are:

- Digital

- □ 32.768 kHz crystal oscillator

- □ SWD and SWV interface pins

- □ External reset

- Analog

- Opamp inputs and outputs

- ☐ High current IDAC outputs

- □ External reference inputs

## 7. Digital Subsystem

The digital programmable system creates application specific combinations of both standard and advanced digital peripherals and custom logic functions. These peripherals and logic are then interconnected to each other and to any pin on the device, providing a high level of design flexibility and IP security.

The features of the digital programmable system are outlined here to provide an overview of capabilities and architecture. Designers do not need to interact directly with the programmable digital system at the hardware and register level. PSoC Creator provides a high level schematic capture graphical interface to automatically place and route resources similar to PLDs.

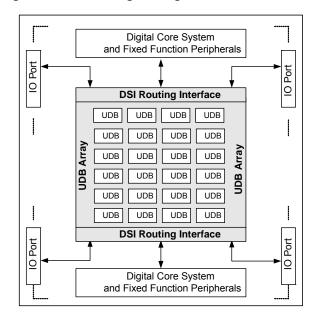

The main components of the digital programmable system are:

- Universal Digital Blocks (UDB) These form the core functionality of the digital programmable system. UDBs are a collection of uncommitted logic (PLD) and structural logic (Datapath) optimized to create all common embedded peripherals and customized functionality that are application or design specific.

- Universal Digital Block Array UDB blocks are arrayed within a matrix of programmable interconnect. The UDB array structure is homogeneous and allows for flexible mapping of digital functions onto the array. The array supports extensive and flexible routing interconnects between UDBs and the Digital System Interconnect.

- Digital System Interconnect (DSI) Digital signals from Universal Digital Blocks (UDBs), fixed function peripherals, I/O pins, interrupts, DMA, and other system core signals are attached to the Digital System Interconnect to implement full featured device connectivity. The DSI allows any digital function to any pin or other feature routability when used with the Universal Digital Block Array.

Figure 7-1. CY8C55 Digital Programmable Architecture

## 7.1 Example Peripherals

The flexibility of the CY8C55 family's UDBs and analog blocks allow the user to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC Creator component catalog, however, users may also create their own custom components using PSoC Creator. Using PSoC Creator, users may also create their own components for reuse within their organization, for example sensor interfaces, proprietary algorithms, and display interfaces.

The number of components available through PSoC Creator is too numerous to list in the data sheet, and the list is always growing. An example of a component available for use in CY8C55 family, but, not explicitly called out in this data sheet is the UART component.

#### 7.1.1 Example Digital Components

The following is a sample of the digital components available in PSoC Creator for the CY8C55 family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Communications

- $\Box$  I<sup>2</sup>C (1 to 3 UDBs)

- □ UART (1 to 3 UDBs)

- Functions

- □ PWM (1 to 2 UDBs)

- Logic (x CPLD product terms per logic function)

- □ NOT

- □ OR

- □ XOR

- □ AND

#### 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

#### 7.2.2.5 Built in CRC/PRS

The datapath has built in support for single cycle Cyclic Redundancy Check (CRC) computation and Pseudo Random Sequence (PRS) generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

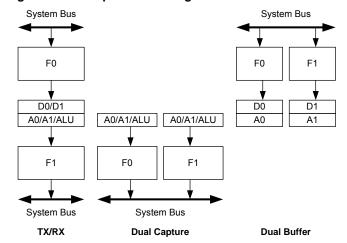

#### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

Figure 7-2. Example FIFO Configurations

#### 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

#### 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry

and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

#### 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

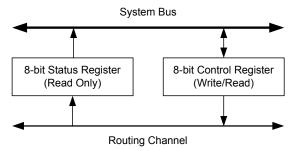

#### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

Figure 7-3. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

#### 7.2.3.2 Clock Generation

Each subcomponent block of a UDB including the two PLDs, the datapath, and Status and Control, has a clock selection and control block. This promotes a fine granularity with respect to allocating clocking resources to UDB component blocks and allows unused UDB resources to be used by other functions for maximum system efficiency.

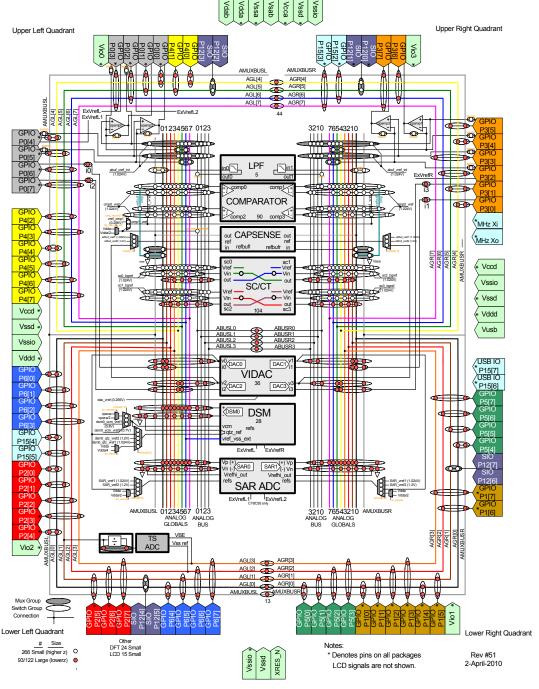

Figure 8-2. CY8C55 Analog Interconnect

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in PSoC 5, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

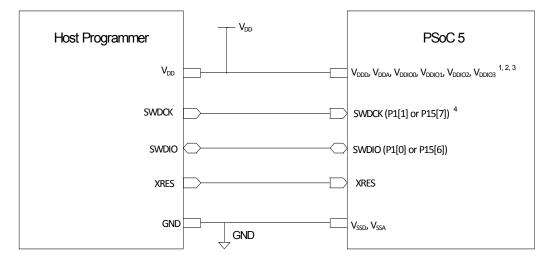

Figure 9-1. SWD Interface Connections between PSoC 5 and Programmer

The voltage levels of the Host Programmer and the PSoC 5 voltage domains involved in programming should be the same. XRES pin is powered by V<sub>DDIO1</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDIO1</sub> of PSoC 5 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 5 voltage domains (V<sub>DDA</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDIO1</sub>. So V<sub>DDIO1</sub> of PSoC 5 should be at same voltage level as host V<sub>DD</sub> for Port 1 SWD programming. Rest of PSoC 5 voltage domains (V<sub>DDD</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

<sup>&</sup>lt;sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 5.

<sup>&</sup>lt;sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 5. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

When USB SWD pins are used for Programming, the P1[1] SWDCK pin must be externally connected to Ground using external pull-down resistor (around 100 K resistor). This is required for P15[7] SWDCK signal to be seen by PSoC 5's internal logic.

Table 11-3. AC Specifications<sup>[22]</sup>

| Parameter              | Description                                                                                                                                    | Conditions                             | Min | Тур | Max   | Units |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|-----|-------|-------|

| F <sub>CPU</sub>       | CPU frequency                                                                                                                                  |                                        | DC  | _   | 67.01 | MHz   |

| F <sub>BUSCLK</sub>    | Bus frequency                                                                                                                                  |                                        | DC  | _   | 67.01 | MHz   |

| S <sub>VDD</sub>       | V <sub>DD</sub> ramp rate                                                                                                                      |                                        | -   | _   | 0.066 | V/µs  |

| T <sub>STARTUP</sub>   | Time from V <sub>DDD</sub> /V <sub>DDA</sub> /V <sub>CCD</sub> /V <sub>CCA</sub> ≥ min operating voltage to CPU executing code at reset vector | No PLL used, IMO boot mode 12 MHz typ. | П   | 45  | 80    | μs    |

| T <sub>SLEEP</sub>     | Wakeup from sleep – CTW timeout to beginning of execution of next CPU instruction                                                              |                                        | _   | 125 | _     | μs    |

| T <sub>SLEEP_INT</sub> | Sleep timer periodic wakeup interval                                                                                                           |                                        | -   | _   | 128   | ms    |

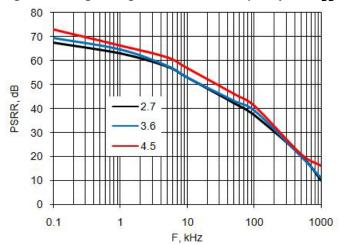

## 11.3 Power Regulators

Specifications are valid for  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$  and  $T_J \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 2.7 V to 5.5 V, except where noted.

## 11.3.1 Digital Core Regulator

Table 11-4. Digital Core Regulator DC Specifications

| Parameter          | Description                                | Conditions                                                                                                                                          | Min | Тур  | Max | Units |

|--------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| $V_{\mathrm{DDD}}$ | Input voltage                              |                                                                                                                                                     | 2.7 | _    | 5.5 | V     |

| $V_{CCD}$          | Output voltage                             |                                                                                                                                                     | -   | 1.80 | _   | V     |

|                    | Regulator output capacitor <sup>[23]</sup> | ±10%, X5R ceramic or better. The two V <sub>CCD</sub> pins must be shorted together, with as short a trace as possible, see Power System on page 21 | _   | 1    | 10  | μF    |

Figure 11-2. Regulators  $V_{CC}$  vs  $V_{DD}$

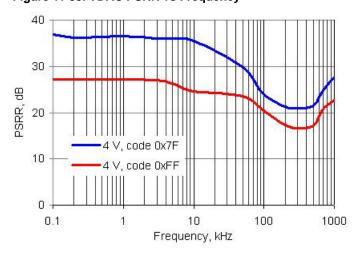

Figure 11-3. Digital Regulator PSRR vs Frequency and  $V_{\rm DD}$

#### Notes

- 21. Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

- 22. Based on device characterization (Not production tested).

- 23. 10  $\mu F$  is required for sleep mode. See Table 11-3.

Table 11-8. SIO DC Specifications (continued)

| Parameter       | Description                                                | Conditions                    | Min | Тур | Max | Units |

|-----------------|------------------------------------------------------------|-------------------------------|-----|-----|-----|-------|

| C <sub>IN</sub> | Input capacitance <sup>[29]</sup>                          |                               | _   | -   | 7   | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt-Trigger) <sup>[29]</sup> | Single ended mode (GPIO mode) | _   | 150 | _   | mV    |

|                 |                                                            | Differential mode             | _   | 35  | _   | mV    |

| Idiode          | Current through protection diode to V <sub>SSIO</sub>      |                               | _   | -   | 100 | μA    |

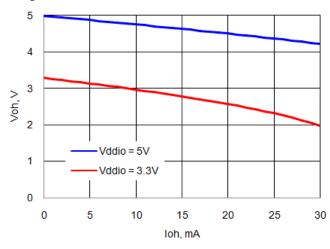

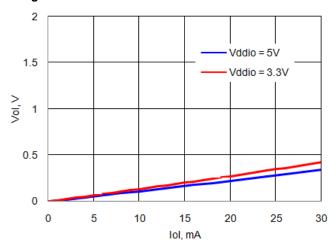

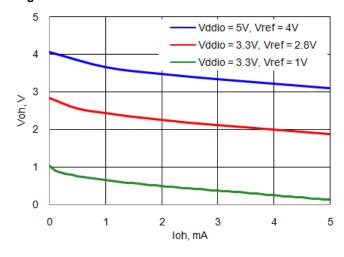

Figure 11-9. SIO Output High Voltage and Current, Unregulated Mode

Figure 11-11. SIO Output Low Voltage and Current, Unregulated Mode

Figure 11-10. SIO Output High Voltage and Current, Regulated Mode

Table 11-9. SIO AC Specifications

| Parameter | Description                                            | Conditions                               | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in fast strong mode (90/10%) <sup>[30]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | _   | _   | 12  | ns    |

| TfallF    | Fall time in fast strong mode (90/10%) <sup>[30]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | 1   | _   | 12  | ns    |

#### Note

<sup>30.</sup> Based on device characterization (Not production tested).

Table 11-18. Delta-sigma ADC AC Specifications

| Parameter     | Description                                                               | Conditions                    | Min | Тур | Max   | Units   |

|---------------|---------------------------------------------------------------------------|-------------------------------|-----|-----|-------|---------|

|               | Startup time                                                              |                               | _   | _   | 4     | Samples |

| THD           | Total harmonic distortion, 16-bit <sup>[37]</sup>                         | Unbuffered, Range ±1.024 V    | -   | -   | 0.006 | %       |

| 20-Bit Resolu | tion Mode                                                                 |                               |     |     |       | - 1     |

| SR20          | Sample Rate, 20-bit <sup>[37]</sup>                                       | Differential range ±1.024 V   | 7.8 | _   | 187   | sps     |

| BW20          | Bandwidth, 20-bit <sup>[37]</sup>                                         | Differential range ±1.024 V   | -   | 40  | _     | Hz      |

| 16-Bit Resolu | tion Mode                                                                 |                               |     | •   |       | •       |

| SR16          | Sample Rate, 16-bit <sup>[37]</sup>                                       | Differential range ±1.024 V   | 2   | _   | 48    | ksps    |

| BW16          | Bandwidth, 16-bit <sup>[37]</sup>                                         | Differential range ±1.024 V   | -   | 11  | _     | kHz     |

| SINAD16int    | Signal to noise + distortion - 16-bit, internal reference <sup>[37]</sup> | Unbuffered, Range = ±1.024 V, | 81  | -   | -     | dB      |

| SINAD_16ext   | Signal to noise + distortion - 16-bit, external reference <sup>[37]</sup> | Unbuffered, Range = ±1.024 V, | 84  | -   | -     | dB      |

| 12-Bit Resolu | tion Mode                                                                 |                               |     | •   |       |         |

| SR12          | Sample Rate, 12-bit <sup>[37]</sup>                                       | Differential range ±1.024 V   | 4   | _   | 192   | kSps    |

| BW12          | Bandwidth, 12-bit <sup>[37]</sup>                                         | Differential range ±1.024 V   | -   | 44  | _     | kHz     |

| SINAD12int    | Signal to noise + distortion - 12-bit, internal reference <sup>[37]</sup> | Unbuffered, Range = ±1.024 V, | 66  | -   | -     | dB      |

| 8-Bit Resolut | ion Mode                                                                  |                               |     |     |       |         |

| SR8           | Sample Rate, 8-bit <sup>[37]</sup>                                        | Differential range ±1.024 V   | 8   | _   | 384   | kSps    |

| BW8           | Bandwidth, 8-bit <sup>[37]</sup>                                          | Differential range ±1.024 V   | _   | 88  | _     | kHz     |

| SINAD8int     | Signal to noise + distortion - 8-bit, internal reference <sup>[37]</sup>  | Unbuffered, Range = ±1.024 V, | 43  | _   | -     | dB      |

Note 37. Based on device characterization (not production tested).

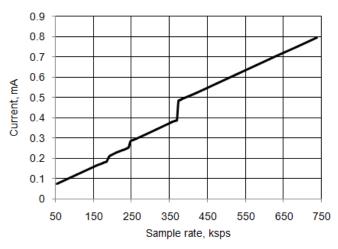

Figure 11-28. SAR ADC  $I_{\rm DD}$  vs sps,  $V_{\rm DDA}$  = 5 V, Continuous Sample Mode, External Reference Mode

Table 11-26. SAR ADC AC Specifications

| Parameter | Description                               | Conditions                                                                                                        | Min | Тур | Max | Units |

|-----------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

|           | Sample rate <sup>[39]</sup>               | With bypass capacitor                                                                                             | -   | _   | 700 | ksps  |

|           |                                           | Without bypass capacitor                                                                                          | -   | _   | 100 |       |

|           | Startup time <sup>[39]</sup>              |                                                                                                                   | -   | _   | 10  | μs    |

| SINAD     | Signal-to-noise ratio <sup>[39]</sup>     | $V_{DDA} \le 3.6 \text{ V}, V_{REF} \le 3.6 \text{ V}$                                                            | 57  | _   | _   | dB    |

|           |                                           | $3.6 \text{ V} < \text{V}_{\text{DDA}} \le 5.5 \text{ V}$<br>V <sub>REF</sub> < 1.3 V or V <sub>REF</sub> > 1.8 V | 57  | -   | -   |       |

| THD       | Total harmonic distortion <sup>[39]</sup> | $V_{DDA} \le 3.6 \text{ V}, V_{REF} \le 3.6 \text{ V}$                                                            | _   | _   | 0.1 | %     |

|           |                                           | $3.6 \text{ V} < \text{V}_{\text{DDA}} \le 5.5 \text{ V}$<br>V <sub>REF</sub> < 1.3 V or V <sub>REF</sub> > 1.8 V | -   | _   | 0.1 |       |

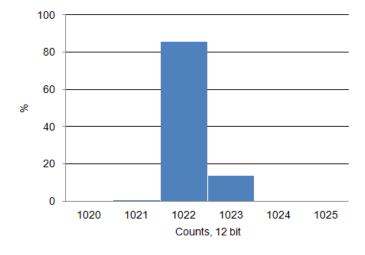

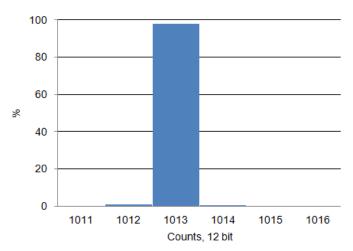

Figure 11-29. SAR ADC Noise Histogram, 1000 samples, 700 ksps, Internal Reference No Bypass,  $V_{\text{IN}}$  = VREF/2

Figure 11-30. SAR ADC Noise Histogram, 1000 samples, 700 ksps, Internal Reference Bypassed,  $V_{IN} = VREF/2$

#### Note

39. Based on device characterization (Not production tested).

Table 11-33. VDAC AC Specifications

| Parameter        | Description                            | Conditions                                                | Min | Тур  | Max  | Units     |

|------------------|----------------------------------------|-----------------------------------------------------------|-----|------|------|-----------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                                                 | _   | _    | 1000 | ksps      |

|                  |                                        | 4 V scale                                                 | _   | -    | 250  | ksps      |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF                                  | _   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                  | _   | 0.8  | 4    | μs        |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF                                  | _   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                  | _   | 0.7  | 4    | μs        |

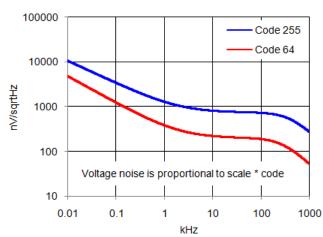

|                  | Voltage noise                          | Range = 1 V, fast mode,<br>V <sub>DDA</sub> = 5 V, 10 kHz | _   | 750  | _    | nV/sqrtHz |

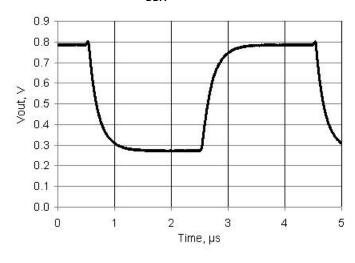

Figure 11-54. VDAC Step Response, Codes 0x40 - 0xC0, 1 V Mode, Fast Mode,  $V_{DDA} = 5$  V

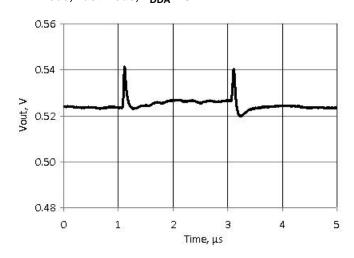

Figure 11-56. VDAC Glitch Response, Codes 0x7F - 0x80, 1 V Mode, Fast Mode,  $V_{DDA}$  = 5 V

Figure 11-55. VDAC PSRR vs Frequency

Figure 11-57. VDAC Voltage Noise, 1 V Mode, Fast Mode,  $V_{DDA}$  = 5 V

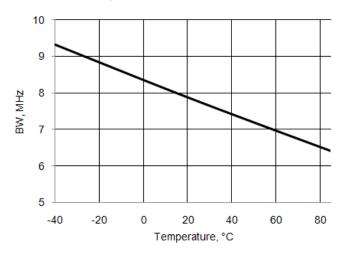

Figure 11-58. Bandwidth vs. Temperature, Gain = 1, Power Mode = High

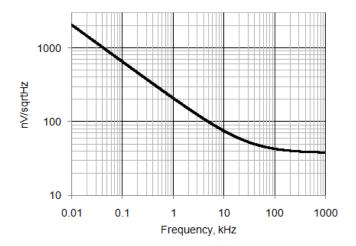

Figure 11-59. Noise vs. Frequency,  $V_{DDA} = 5 V$ , Power Mode = High

11.5.12 LCD Direct Drive

Table 11-40. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                  | Min  | Тур  | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| I <sub>CC</sub>     | LCD system operating current                                                        | Bus clock = 3 MHz, V <sub>DDIO</sub> = V <sub>DDA</sub> = 3 V, 4 commons, 16 segments, 1/4 duty cycle, 50 Hz frame rate, no glass connected | -    | 63   | _    | μА    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          |                                                                                                                                             | _    | 148  | _    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $3 \text{ V} \le V_{BIAS} \le V_{DDIO}$ for the drive pin                                                                                   | 2.09 | _    | 5.2  | V     |

|                     | LCD bias step size                                                                  | $3 \text{ V} \le \text{V}_{BIAS} \le \text{V}_{DDIO}$ for the drive pin                                                                     | -    | 25.8 | -    | mV    |

|                     | LCD capacitance per segment/common driver                                           | Drivers may be combined                                                                                                                     | -    | 500  | 5000 | pF    |

|                     | Long term segment offset                                                            | $V_{BIAS} \le V_{DDA} - 0.5 \text{ V}$                                                                                                      | -    | -    | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver                                             | V <sub>DDIO</sub> = 5.5 V                                                                                                                   | 90   | -    | 165  | μA    |

Table 11-41. LCD Direct Drive AC Specifications

| Parameter | Description    | Conditions | Min | Тур | Max | Units |

|-----------|----------------|------------|-----|-----|-----|-------|

| $f_{LCD}$ | LCD frame rate |            | 10  | 50  | 150 | Hz    |

## 11.7 Memory

Specifications are valid for  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$  and  $T_J \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 2.7 V to 5.5 V, except where noted.

11.7.1 Flash

## Table 11-54. Flash DC Specifications

| Parameter | Description               | Conditions       | Min | Тур | Max | Units |

|-----------|---------------------------|------------------|-----|-----|-----|-------|

|           | Erase and program voltage | $V_{ m DDD}$ pin | 2.7 | _   | 5.5 | V     |

#### Table 11-55. Flash AC Specifications

| Parameter          | Description                                                                | Conditions                                                                       | Min | Тур | Max  | Units   |

|--------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|-----|------|---------|

| T <sub>WRITE</sub> | Row write time (erase + program)                                           |                                                                                  | _   | 8.3 | 32   | ms      |

| T <sub>BULK</sub>  | Bulk erase time (256 KB)                                                   | 10 °C < average ambient temp.<br>T <sub>A</sub> < 40 °C                          | -   | 117 | 440  | ms      |

|                    | Sector erase time (16 KB)                                                  | 10 °C < average ambient temp.<br>T <sub>A</sub> < 40 °C                          | -   | 6.3 | 26   | ms      |

| T <sub>PROG</sub>  | Total device programming time                                              | No overhead <sup>[42]</sup>                                                      | -   | 9   | 32.5 | seconds |

|                    | Flash data retention time, retention period measured from last erase cycle | Average ambient temp. $T_A \le 55~^{\circ}\text{C}$ , 100 K erase/program cycles | 20  | _   | _    | years   |

|                    |                                                                            | Average ambient temp. $T_A \le 70 ^{\circ}\text{C}$ , 10 K erase/program cycles  | 10  | _   | _    |         |

## 11.7.2 EEPROM

## Table 11-56. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min | Тур | Max | Units |

|-----------|---------------------------|------------|-----|-----|-----|-------|

|           | Erase and program voltage |            | 2.7 | -   | 5.5 | V     |

## Table 11-57. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |            | _   | 8.3 | 32  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle |            | 20  | -   | _   | years |

#### Note

<sup>42.</sup> See application note AN64359 for a description of a low-overhead method of programming PSoC 5 flash.

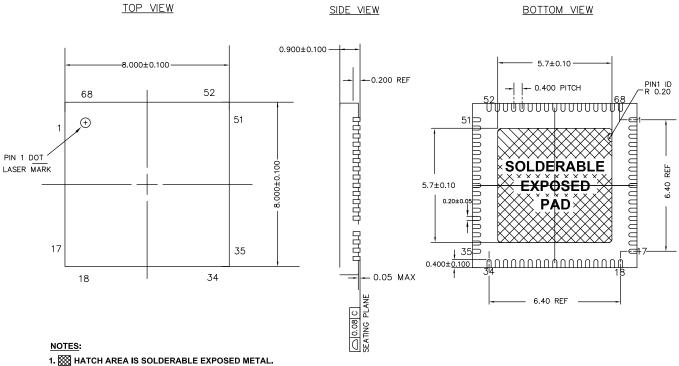

## 13. Packaging

## Table 13-1. Package Characteristics

| Parameter      | Description                    | Conditions | Min | Тур | Max | Units   |

|----------------|--------------------------------|------------|-----|-----|-----|---------|

| T <sub>A</sub> | Operating ambient temperature  |            | -40 | 25  | 85  | °C      |

| T <sub>J</sub> | Operating junction temperature |            | -40 | _   | 100 | °C      |

| Tja            | Package θJA (68-pin QFN)       |            | _   | 15  | -   | °C/Watt |

| Tja            | Package θJA (100-pin TQFP)     |            | -   | 34  | -   | °C/Watt |

| Tjc            | Package θJC (68-pin QFN)       |            | _   | 13  | -   | °C/Watt |

| Tjc            | Package θJC (100-pin TQFP)     |            | _   | 10  | -   | °C/Watt |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at<br>Peak Temperature |

|--------------|-----------------------------|-------------------------------------|

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

Figure 13-1. 68-pin QFN 8 × 8 with 0.4 mm Pitch Package Outline (Sawn Version)

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: 0.17g

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-09618 \*D

16.00±0.25 SQ 1. JEDEC STD REF MS-026 14.00±0.05 SQ 76 2. BODY LENGTH DIMENSION DOES NOT INCLUDE MOLD PROTRUSION/END FLASH 100 MOLD PROTRUSION/END FLASH SHALL NOT EXCEED 0.0098 in (0.25 mm) PER SIDE BODY LENGTH DIMENSIONS ARE MAX PLASTIC BODY SIZE INCLUDING MOLD MISMATCH 3. DIMENSIONS IN MILLIMETERS 75 R 0.08 MIN. 0° MIN. 0.20 MAX. STAND-OFF 0.05 MIN. 0.15 MAX. 0.25 GAUGE PLANE R 0.08 MIN. 0.7 0.20 MAX. DETAILA 0.60±0.15 0.20 MIN. 1.00 REF. NOTE: PKG. CAN HAVE SEATING PLANE 12°±1°  $\square R$ (8X) 1.60 MAX. TOP LEFT CORNER CHAMFER 4 CORNERS CHAMFER 1.40±0.05 0.08 0.20 MAX. 51-85048 \*E L SEE DETAIL A

Figure 13-2. 100-pin TQFP (14 x 14 x 1.4 mm) Package Outline

## 16. Document Conventions

## 16.1 Units of Measure

Table 16-1. Units of Measure

| Table 16-1. Units of Measure |                        |  |  |

|------------------------------|------------------------|--|--|

| Symbol                       | Unit of Measure        |  |  |

| °C                           | degrees Celsius        |  |  |

| dB                           | decibels               |  |  |

| fF                           | femtofarads            |  |  |

| Hz                           | hertz                  |  |  |

| KB                           | 1024 bytes             |  |  |

| kbps                         | kilobits per second    |  |  |

| Khr                          | kilohours              |  |  |

| kHz                          | kilohertz              |  |  |

| kΩ                           | kilohms                |  |  |

| ksps                         | kilosamples per second |  |  |

| LSB                          | least significant bit  |  |  |

| Mbps                         | megabits per second    |  |  |

| MHz                          | megahertz              |  |  |

| ΜΩ                           | megaohms               |  |  |

| Msps                         | megasamples per second |  |  |

| μΑ                           | microamperes           |  |  |

| μF                           | microfarads            |  |  |

| μH                           | microhenrys            |  |  |

| μs                           | microseconds           |  |  |

| μV                           | microvolts             |  |  |

| μW                           | microwatts             |  |  |

| mA                           | milliamperes           |  |  |

| ms                           | milliseconds           |  |  |

| mV                           | millivolts             |  |  |

| nA                           | nanoamperes            |  |  |

| ns                           | nanoseconds            |  |  |

| nV                           | nanovolts              |  |  |

| Ω                            | ohms                   |  |  |

| pF                           | picofarads             |  |  |

| ppm                          | parts per million      |  |  |

| ps                           | picoseconds            |  |  |

| s                            | seconds                |  |  |

| sps                          | samples per second     |  |  |

| sqrtHz                       | square root of hertz   |  |  |

| V                            | volts                  |  |  |

|                              |                        |  |  |