Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                                |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 48MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus SBC, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 512 x 8                                                                         |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 0V ~ 3.8V                                                                       |

| Data Converters            | A/D 13x12b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 115°C (TC)                                                              |

| Mounting Type              | Surface Mount, Wettable Flank                                                   |

| Package / Case             | 48-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 48-VQFN (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamha0g14a-mzt-bvao |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Configuration Summary**

|                       | SAMHA0/1 |

|-----------------------|----------|

| Event System channels | 12       |

| SW Debug Interface    | Yes      |

| Watchdog Timer (WDT)  | Yes      |

#### 12.3.2 NVM Software Calibration Area Mapping

The NVM Software Calibration Area contains calibration data that are measured and written during production test. These calibration values should be read by the application software and written back to the corresponding register.

The NVM Software Calibration Area can be read at address 0x806020.

The NVM Software Calibration Area can not be written.

| Table 12-5. NVM Software Calibration Area Mappin | ng |

|--------------------------------------------------|----|

|--------------------------------------------------|----|

| Bit Position | Name               | Description                                                                      |  |  |  |  |  |

|--------------|--------------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| 2:0          | Reserved           |                                                                                  |  |  |  |  |  |

| 14:3         | Reserved           |                                                                                  |  |  |  |  |  |

| 26:15        | Reserved           |                                                                                  |  |  |  |  |  |

| 34:27        | ADC LINEARITY      | ADC Linearity Calibration. Should be written to ADC CALIB register.              |  |  |  |  |  |

| 37:35        | ADC BIASCAL        | ADC Bias Calibration. Should be written to ADC CALIB register.                   |  |  |  |  |  |

| 44:38        | OSC32K CAL         | OSC32KCalibration. Should be written to SYSCTRL OSC32K register.                 |  |  |  |  |  |

| 49:45        | Reserved           |                                                                                  |  |  |  |  |  |

| 54:50        | Reserved           |                                                                                  |  |  |  |  |  |

| 57:55        | Reserved           |                                                                                  |  |  |  |  |  |

| 63:58        | DFLL48M COARSE CAL | DFLL48M Coarse calibration value. Should be written to SYSCTRL DFLLVAL register. |  |  |  |  |  |

| 73:64        | Reserved           |                                                                                  |  |  |  |  |  |

| 127:74       | Reserved           |                                                                                  |  |  |  |  |  |

#### 12.3.3 Serial Number

Each device has a unique 128-bit serial number which is a concatenation of four 32-bit words contained at the following addresses:

Word 0: 0x0080A00C

Word 1: 0x0080A040

Word 2: 0x0080A044

Word 3: 0x0080A048

The uniqueness of the serial number is guaranteed only when using all 128 bits.

**Processor And Architecture**

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 16 – ADC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bits 11, 12, 13, 14, 15 – TC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bits 8, 9, 10 – TCC

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bits 7:2 - SERCOM[5:0]

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

#### Bit 1 – EVSYS

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Write-protection is disabled. |

| 1     | Write-protection is enabled.  |

PM – Power Manager

| Peripheral Clock | Default State |

|------------------|---------------|

| CLK_EIC_APB      | Enabled       |

| CLK_PAC1_APB     | Enabled       |

| CLK_DSU_APB      | Enabled       |

| CLK_NVMCTRL_APB  | Enabled       |

| CLK_PORT_APB     | Enabled       |

| CLK_HMATRIX_APB  | Enabled       |

| CLK_PAC2_APB     | Disabled      |

| CLK_SERCOMx_APB  | Disabled      |

| CLK_TCx_APB      | Disabled      |

| CLK_ADC_APB      | Enabled       |

| CLK_AC_APB       | Disabled      |

| CLK_DAC_APB      | Disabled      |

| CLK_PTC_APB      | Disabled      |

| CLK_DMAC_APB     | Enabled       |

| CLK_TCCx_APB     | Disabled      |

When the APB clock for a module is not provided its registers cannot be read or written. The module can be re-enabled later by writing the corresponding mask bit to one.

A module may be connected to several clock domains (for instance, AHB and APB), in which case it will have several mask bits.

**Note:** Clocks should only be switched off if it is certain that the module will not be used. Switching off the clock for the NVM Controller (NVMCTRL) will cause a problem if the CPU needs to read from the flash memory. Switching off the clock to the Power Manager (PM), which contains the mask registers, or the corresponding APBx bridge, will make it impossible to write the mask registers again. In this case, they can only be re-enabled by a system reset.

#### 18.6.2.7 Reset Controller

The latest reset cause is available in RCAUSE, and can be read during the application boot sequence in order to determine proper action.

There are two groups of reset sources:

- Power Reset: Resets caused by an electrical issue.

- User Reset: Resets caused by the application.

The table below lists the parts of the device that are reset, depending on the reset type.

Exception for APBASEL, APBBSEL and APBCSEL: These registers must only be accessed with 8-bit access.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

#### 3. Start DFLL close loop

This procedure will reduce DFLL Lock time to DFLL Fine lock time.

#### **Related Links**

GCLK - Generic Clock Controller NVM Software Calibration Area Mapping

#### **Frequency Locking**

The locking of the frequency in closed-loop mode is divided into two stages. In the first, coarse stage, the control logic quickly finds the correct value for DFLLVAL.COARSE and sets the output frequency to a value close to the correct frequency. On coarse lock, the DFLL Locked on Coarse Value bit (PCLKSR.DFLLLOCKC) in the Power and Clocks Status register will be set.

In the second, fine stage, the control logic tunes the value in DFLLVAL.FINE so that the output frequency is very close to the desired frequency. On fine lock, the DFLL Locked on Fine Value bit (PCLKSR.DFLLLOCKF) in the Power and Clocks Status register will be set.

Interrupts are generated by both PCLKSR.DFLLLOCKC and PCLKSR.DFLLLOCKF if INTENSET.DFLLOCKC or INTENSET.DFLLOCKF are written to one.

CLK\_DFLL48M is ready to be used when the DFLL Ready bit (PCLKSR.DFLLRDY) in the Power and Clocks Status register is set, but the accuracy of the output frequency depends on which locks are set. For lock times, refer to the *Electrical Characteristics*.

#### **Related Links**

Electrical Characteristics

#### **Frequency Error Measurement**

The ratio between CLK\_DFLL48M\_REF and CLK48M\_DFLL is measured automatically when the DFLL48M is in closed-loop mode. The difference between this ratio and the value in DFLLMUL.MUL is stored in the DFLL Multiplication Ratio Difference bit group(DFLLVAL.DIFF) in the DFLL Value register. The relative error on CLK\_DFLL48M compared to the target frequency is calculated as follows:

$ERROR = \frac{DIFF}{MUL}$

#### **Drift Compensation**

If the Stable DFLL Frequency bit (DFLLCTRL.STABLE) in the DFLL Control register is zero, the frequency tuner will automatically compensate for drift in the CLK\_DFLL48M without losing either of the locks. This means that DFLLVAL.FINE can change after every measurement of CLK\_DFLL48M.

The DFLLVAL.FINE value overflows or underflows can occur in close loop mode when the clock source reference drifts or is unstable. This will set the DFLL Out Of Bounds bit (PCLKSR.DFLLOOB) in the Power and Clocks Status register.

To avoid this error, the reference clock in close loop mode must be stable, an external oscillator is recommended and internal oscillator forbidden. The better choice is to use an XOSC32K.

#### **Reference Clock Stop Detection**

If CLK\_DFLL48M\_REF stops or is running at a very low frequency (slower than CLK\_DFLL48M/(2 \* MUL<sub>MAX</sub>)), the DFLL Reference Clock Stopped bit (PCLKSR.DFLLRCS) in the Power and Clocks Status register will be set. Detecting a stopped reference clock can take a long time, on the order of 217 CLK\_DFLL48M cycles. When the reference clock is stopped, the DFLL48M will operate as if in open-loop mode. Closed-loop mode operation will automatically resume if the CLK\_DFLL48M\_REF is restarted. An

#### 22.8.14 Active Channel and Levels

|        | Name:<br>Offset:<br>Reset:<br>Property: | ACTIVE<br>0x30<br>0x00000000<br>- |    |       |        |         |        |        |

|--------|-----------------------------------------|-----------------------------------|----|-------|--------|---------|--------|--------|

| Bit    | 31                                      | 30                                | 29 | 28    | 27     | 26      | 25     | 24     |

|        |                                         |                                   |    | BTCNT | [15:8] |         |        |        |

| Access | R                                       | R                                 | R  | R     | R      | R       | R      | R      |

| Reset  | 0                                       | 0                                 | 0  | 0     | 0      | 0       | 0      | 0      |

|        |                                         |                                   |    |       |        |         |        |        |

| Bit    | 23                                      | 22                                | 21 | 20    | 19     | 18      | 17     | 16     |

|        | BTCNT[7:0]                              |                                   |    |       |        |         |        |        |

| Access | R                                       | R                                 | R  | R     | R      | R       | R      | R      |

| Reset  | 0                                       | 0                                 | 0  | 0     | 0      | 0       | 0      | 0      |

|        |                                         |                                   |    |       |        |         |        |        |

| Bit    |                                         | 14                                | 13 | 12    | 11     | 10      | 9      | 8      |

|        | ABUSY                                   |                                   |    |       |        | ID[4:0] |        |        |

| Access | R                                       |                                   |    | R     | R      | R       | R      | R      |

| Reset  | 0                                       |                                   |    | 0     | 0      | 0       | 0      | 0      |

|        |                                         |                                   |    |       |        |         |        |        |

| Bit    | 7                                       | 6                                 | 5  | 4     | 3      | 2       | 1      | 0      |

|        |                                         |                                   |    |       | LVLEXx | LVLEXx  | LVLEXx | LVLEXx |

| Access |                                         |                                   |    |       | R      | R       | R      | R      |

| Reset  |                                         |                                   |    |       | 0      | 0       | 0      | 0      |

#### Bits 31:16 - BTCNT[15:0] Active Channel Block Transfer Count

These bits hold the 16-bit block transfer count of the ongoing transfer. This value is stored in the active channel and written back in the corresponding Write-Back channel memory location when the arbiter grants a new channel access. The value is valid only when the active channel active busy flag (ABUSY) is set.

#### Bit 15 - ABUSY Active Channel Busy

This bit is cleared when the active transfer count is written back in the write-back memory section.

This bit is set when the next descriptor transfer count is read from the write-back memory section.

#### Bits 12:8 - ID[4:0] Active Channel ID

These bits hold the channel index currently stored in the active channel registers. The value is updated each time the arbiter grants a new channel transfer access request.

**Bits 3,2,1,0 – LVLEXx** Level x Channel Trigger Request Executing [x=3..0]

This bit is set when a level-x channel trigger request is executing or pending.

This bit is cleared when no request is pending or being executed.

|        | Offset:<br>Reset:<br>Property: | 0x34<br>0x00000000<br>PAC Write-Pr | otection, Enal | ble-Protected |    |    |    |    |

|--------|--------------------------------|------------------------------------|----------------|---------------|----|----|----|----|

| Bit    | 31                             | 30                                 | 29             | 28            | 27 | 26 | 25 | 24 |

|        |                                |                                    |                |               |    |    |    |    |

| Access |                                |                                    |                |               |    |    |    |    |

| Reset  |                                |                                    |                |               |    |    |    |    |

|        |                                |                                    |                |               |    |    |    |    |

| Bit    | 23                             | 22                                 | 21             | 20            | 19 | 18 | 17 | 16 |

|        |                                |                                    |                |               |    |    |    |    |

| Access |                                |                                    |                |               |    |    |    |    |

| Reset  |                                |                                    |                |               |    |    |    |    |

| Bit    | 15                             | 14                                 | 13             | 12            | 11 | 10 | 9  | 8  |

| 2.0    |                                |                                    |                |               |    |    |    |    |

| Access |                                |                                    |                |               |    |    |    |    |

| Reset  |                                |                                    |                |               |    |    |    |    |

|        |                                |                                    |                |               |    |    |    |    |

| Bit    | 7                              | 6                                  | 5              | 4             | 3  | 2  | 1  | 0  |

|        |                                |                                    |                |               |    |    |    |    |

| Access |                                |                                    |                |               |    |    |    |    |

| Reset  |                                |                                    |                |               |    |    |    |    |

#### 22.8.15 Descriptor Memory Section Base Address

BASEADDR

Name:

• and 16x sample rate using fractional baud rate generation (CTRLA.SAMPR = 1).

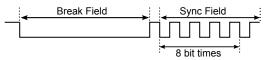

The USART uses a break detection threshold of greater than 11 nominal bit times at the configured baud rate. At any time, if more than 11 consecutive dominant bits are detected on the bus, the USART detects a Break Field. When a Break Field has been detected, the Receive Break interrupt flag (INTFLAG.RXBRK) is set and the USART expects the Sync Field character to be 0x55. This field is used to update the actual baud rate in order to stay synchronized. If the received Sync character is not 0x55, then the Inconsistent Sync Field error flag (STATUS.ISF) is set along with the Error interrupt flag (INTFLAG.ERROR), and the baud rate is unchanged.

The auto-baud follows the LIN format. All LIN Frames start with a Break Field followed by a Sync Field.

#### Figure 28-12. LIN Break and Sync Fields

After a break field is detected and the start bit of the Sync Field is detected, a counter is started. The counter is then incremented for the next 8 bit times of the Sync Field. At the end of these 8 bit times, the counter is stopped. At this moment, the 13 most significant bits of the counter (value divided by 8) give the new clock divider (BAUD.BAUD), and the 3 least significant bits of this value (the remainder) give the new Fractional Part (BAUD.FP).

When the Sync Field has been received, the clock divider (BAUD.BAUD) and the Fractional Part (BAUD.FP) are updated after a synchronization delay. After the Break and Sync Fields are received, multiple characters of data can be received.

#### 28.6.3.5 Collision Detection

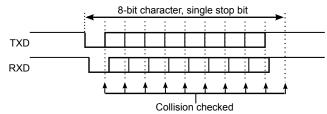

When the receiver and transmitter are connected either through pin configuration or externally, transmit collision can be detected after selecting the Collision Detection Enable bit in the CTRLB register (CTRLB.COLDEN=1). To detect collision, the receiver and transmitter must be enabled (CTRLB.RXEN=1 and CTRLB.TXEN=1).

Collision detection is performed for each bit transmitted by comparing the received value with the transmit value, as shown in the figure below. While the transmitter is idle (no transmission in progress), characters can be received on RxD without triggering a collision.

The next figure shows the conditions for a collision detection. In this case, the start bit and the first data bit are received with the same value as transmitted. The second received data bit is found to be different than the transmitted bit at the detection point, which indicates a collision.

## 28.7 Register Summary

| Offset                                           | Name     | Bit Pos. |          |            |       |        |           |        |             |           |

|--------------------------------------------------|----------|----------|----------|------------|-------|--------|-----------|--------|-------------|-----------|

|                                                  |          | 7:0      | RUNSTDBY |            |       |        | MODE[2:0] |        | ENABLE      | SWRST     |

| 0x00                                             | CTRLA    | 15:8     |          | SAMPR[2:0] |       |        |           |        |             | IBON      |

| 000                                              | CIRLA    | 23:16    | SAMF     | PA[1:0]    | RXP   | D[1:0] |           |        | TXP         | D[1:0]    |

|                                                  |          | 31:24    |          | DORD       | CPOL  | CMODE  |           | FOR    | M[3:0]      |           |

|                                                  |          | 7:0      |          | SBMODE     |       |        |           |        | CHSIZE[2:0] |           |

| 0.404                                            | CTRLB    | 15:8     |          |            | PMODE |        |           | ENC    | SFDE        | COLDEN    |

| 0x04                                             | CIRLB    | 23:16    |          |            |       |        |           |        | RXEN        | TXEN      |

|                                                  |          | 31:24    |          |            |       |        |           |        |             |           |

|                                                  |          | 7:0      |          |            |       |        |           |        |             |           |

| 0.00                                             |          | 15:8     |          |            |       |        |           |        |             |           |

| 0x08                                             | CTRLC    | 23:16    |          |            |       |        |           |        |             |           |

| 0x0C<br>0x0E<br>0x0F<br><br>0x13<br>0x14<br>0x15 |          | 31:24    |          |            |       |        |           |        |             |           |

| 0.00                                             | DALID    | 7:0      |          |            |       | BAU    | D[7:0]    |        |             |           |

| UXUC                                             | BAUD     | 15:8     |          |            |       | BAU    | D[15:8]   |        |             |           |

| 0x0E                                             | RXPL     | 7:0      |          |            |       | RXP    | L[7:0]    |        |             |           |

| 0x0F                                             |          |          |          |            |       |        |           |        |             |           |

|                                                  | Reserved |          |          |            |       |        |           |        |             |           |

|                                                  |          |          |          |            |       |        |           |        |             |           |

|                                                  | INTENCLR | 7:0      | ERROR    |            | RXBRK | CTSIC  | RXS       | RXC    | TXC         | DRE       |

|                                                  | Reserved |          |          |            |       |        |           |        |             |           |

| 0x16                                             | INTENSET | 7:0      | ERROR    |            | RXBRK | CTSIC  | RXS       | RXC    | TXC         | DRE       |

| 0x17                                             | Reserved |          |          |            |       |        |           |        |             |           |

| 0x18                                             | INTFLAG  | 7:0      | ERROR    |            | RXBRK | CTSIC  | RXS       | RXC    | TXC         | DRE       |

| 0x19                                             | Reserved |          |          |            |       |        |           |        |             |           |

| 0x1A                                             | STATUS   | 7:0      |          | TXE        | COLL  | ISF    | CTS       | BUFOVF | FERR        | PERR      |

|                                                  |          | 15:8     |          |            |       |        |           |        |             |           |

|                                                  |          | 7:0      |          |            |       |        |           | CTRLB  | ENABLE      | SWRST     |

| 0x1C                                             | SYNCBUSY | 15:8     |          |            |       |        |           |        |             |           |

|                                                  |          | 23:16    |          |            |       |        |           |        |             |           |

|                                                  |          | 31:24    |          |            |       |        |           |        |             |           |

| 0x20                                             |          |          |          |            |       |        |           |        |             |           |

|                                                  | Reserved |          |          |            |       |        |           |        |             |           |

| 0x27                                             |          |          |          |            |       |        |           |        |             |           |

| 0x28                                             | DATA     | 7:0      |          |            |       | DAT    | A[7:0]    |        |             |           |

|                                                  |          | 15:8     |          |            |       |        |           |        |             | DATA[8:8] |

| 0x2A                                             |          |          |          |            |       |        |           |        |             |           |

|                                                  | Reserved |          |          |            |       |        |           |        |             |           |

| 0x2F                                             |          |          |          |            |       |        |           |        |             |           |

| 0x30                                             | DBGCTRL  | 7:0      |          |            |       |        |           |        |             | DBGSTOP   |

transferred to the two-level receive buffer. The transfer takes place in the same clock cycle as the last data bit is shifted in. And the Receive Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) will be set. The received data can be retrieved by reading DATA.

When the last character has been transmitted and there is no valid data in DATA, the Transmit Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.TXC) will be set. When the transaction is finished, the master must pull the  $\overline{SS}$  line high to notify the slave. If Master Slave Select Enable (CTRLB.MSSEN) is set to '0', the software must pull the  $\overline{SS}$  line high.

#### Slave

In slave mode (CTRLA.MODE=0x2), the SPI interface will remain inactive with the MISO line tri-stated as long as the  $\overline{SS}$  pin is pulled high. Software may update the contents of DATA at any time as long as the Data Register Empty flag in the Interrupt Status and Clear register (INTFLAG.DRE) is set.

When  $\overline{SS}$  is pulled low and SCK is running, the slave will sample and shift out data according to the transaction mode set. When the content of TxDATA has been loaded into the shift register, INTFLAG.DRE will be set, and new data can be written to DATA.

Similar to the master, the slave will receive one character for each character transmitted. A character will be transferred into the two-level receive buffer within the same clock cycle its last data bit is received. The received character can be retrieved from DATA when the Receive Complete interrupt flag (INTFLAG.RXC) is set.

When the master pulls the  $\overline{SS}$  line high, the transaction is done and the Transmit Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.TXC) will be set.

After DATA is written it takes up to three SCK clock cycles until the content of DATA is ready to be loaded into the shift register on the next character boundary. As a consequence, the first character transferred in a SPI transaction will not be the content of DATA. This can be avoided by using the preloading feature. Refer to Preloading of the Slave Shift Register.

When transmitting several characters in one SPI transaction, the data has to be written into DATA register with at least three SCK clock cycles left in the current character transmission. If this criteria is not met, the previously received character will be transmitted.

Once the DATA register is empty, it takes three CLK\_SERCOM\_APB cycles for INTFLAG.DRE to be set.

#### 29.6.2.7 Receiver Error Bit

The SPI receiver has one error bit: the Buffer Overflow bit (BUFOVF), which can be read from the Status register (STATUS). Once an error happens, the bit will stay set until it is cleared by writing '1' to it. The bit is also automatically cleared when the receiver is disabled.

There are two methods for buffer overflow notification, selected by the immediate buffer overflow notification bit in the Control A register (CTRLA.IBON):

If CTRLA.IBON=1, STATUS.BUFOVF is raised immediately upon buffer overflow. Software can then empty the receive FIFO by reading RxDATA until the receiver complete interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) goes low.

If CTRLA.IBON=0, the buffer overflow condition travels with data through the receive FIFO. After the received data is read, STATUS.BUFOVF and INTFLAG.ERROR will be set along with INTFLAG.RXC, and RxDATA will be zero.

#### 31.8.13.1 Period Value, 8-bit Mode

Name:PEROffset:0x14Reset:0xFFProperty:Write-Synchronized

| Bit    | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-------|-----|-----|-----|

|        |     |     |     | PER | [7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 1   |

#### Bits 7:0 – PER[7:0] Period Value

These bits hold the value of the Period Buffer register PERBUF. The value is copied to PER register on UPDATE condition.

#### 31.8.14 Compare/Capture

#### 31.8.14.1 Channel x Compare/Capture Value, 8-bit Mode

Name:CCxOffset:0x18+i\*0x1 [i=0..1]Reset:0x00Property:Write-Synchronized

| Bit    | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|------|-----|-----|-----|

|        |     |     |     | CC[ | 7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0    | 0   | 0   | 0   |

Bits 7:0 – CC[7:0] Channel x Compare/Capture Value

These bits contain the compare/capture value in 8-bit TC mode. In Match frequency (MFRQ) or Match PWM (MPWM) waveform operation (CTRLA.WAVEGEN), the CC0 register is used as a period register.

### 32.7 Register Summary

| Offset       | Name                 | Bit Pos.     |               |              |             |             |            |                     |             |        |  |

|--------------|----------------------|--------------|---------------|--------------|-------------|-------------|------------|---------------------|-------------|--------|--|

|              |                      | 7:0          |               | RESOLU       | JTION[1:0]  |             |            |                     | ENABLE      | SWRST  |  |

| 0.00         | CTRLA                | 15:8         |               | ALOCK        | PRESC       | YNC[1:0]    | RUNSTDBY   | Р                   | RESCALER[2: | 0]     |  |

| 0x00         |                      | 23:16        |               |              |             |             |            |                     |             |        |  |

|              |                      | 31:24        |               |              |             |             | CPTEN3     | CPTEN2              | CPTEN1      | CPTEN0 |  |

| 0x04         | CTRLBCLR             | 7:0          |               | CMD[2:0]     |             | IDXCI       | MD[1:0]    | ONESHOT             | LUPD        | DIR    |  |

| 0x05         | CTRLBSET             | 7:0          |               | CMD[2:0]     |             | IDXCI       | MD[1:0]    | ONESHOT             | LUPD        | DIR    |  |

| 0x06         |                      |              |               |              |             |             |            |                     |             |        |  |

|              | Reserved             |              |               |              |             |             |            |                     |             |        |  |

| 0x07         |                      |              |               |              |             |             |            |                     |             |        |  |

|              |                      | 7:0          | PER           | WAVE         | PATT        | COUNT       | STATUS     | CTRLB               | ENABLE      | SWRST  |  |

| 0.00         | SYNCBUSY             | 15:8         |               |              |             |             | CC3        | CC2                 | CC1         | CC0    |  |

| 0x08         | STINCBUST            | 23:16        |               | CCB3         | CCB2        | CCB1        | CCB0       | PERB                | WAVEB       | PATTB  |  |

|              |                      | 31:24        |               |              |             |             |            |                     |             |        |  |

|              |                      | 7:0          | RESTART       | BLAN         | IK[1:0]     | QUAL        | KEEP       |                     | SRC         | [1:0]  |  |

|              |                      | 15:8         |               |              | CAPTURE[2:0 | ]           | CHSE       | EL[1:0]             | HAL         | F[1:0] |  |

| 0x0C         | FCTRLA               | 23:16        |               |              |             | BLANK       | (VAL[7:0]  |                     |             |        |  |

|              |                      | 31:24        |               |              |             |             |            | FILTER'             | VAL[3:0]    |        |  |

|              |                      | 7:0          | RESTART       | BLAN         | IK[1:0]     | QUAL        | KEEP       |                     | SRC         | [1:0]  |  |

|              |                      | 15:8         |               | CAPTURE[2:0] |             |             | CHSE       | HSEL[1:0] HALT[1:0] |             |        |  |

| 0x10         | FCTRLB 23:16         |              | BLANKVAL[7:0] |              |             |             |            |                     |             |        |  |

|              |                      | 31:24        |               |              |             |             |            | FILTER'             | 'AL[3:0]    |        |  |

|              |                      | 7:0          |               |              |             |             |            |                     | OTM         | X[1:0] |  |

|              |                      | 15:8         |               |              |             |             | DTIENx     | DTIENx              | DTIENx      | DTIENx |  |

| 0x14         | WEXCTRL              | 23:16        |               |              |             | DTL         | .S[7:0]    |                     |             |        |  |

|              |                      | 31:24        |               |              |             | DTH         | IS[7:0]    |                     |             |        |  |

|              |                      | 7:0          | NREx          | NREx         | NREx        | NREx        | NREx       | NREx                | NREx        | NREx   |  |

|              |                      | 15:8         | NRVx          | NRVx         | NRVx        | NRVx        | NRVx       | NRVx                | NRVx        | NRVx   |  |

| 0x18         | DRVCTRL              | 23:16        | INVENx        | INVENx       | INVENx      | INVENx      | INVENx     | INVENx              | INVENx      | INVENx |  |

|              |                      | 31:24        |               | FILTER       | VAL1[3:0]   |             |            | FILTER\             | /AL0[3:0]   |        |  |

| 0x1C         |                      |              |               |              |             |             |            |                     |             |        |  |

|              | Reserved             |              |               |              |             |             |            |                     |             |        |  |

| 0x1D         |                      |              |               |              |             |             |            |                     |             |        |  |

| 0x1E         | DBGCTRL              | 7:0          |               |              |             |             |            | FDDBD               |             | DBGRUN |  |

| 0x1F         | Reserved             |              |               |              |             |             |            |                     |             |        |  |

|              |                      | 7:0          | CNTSI         | EL[1:0]      |             | EVACT1[2:0] |            |                     | EVACT0[2:0] |        |  |

|              |                      | 15:8         | TCEIx         | TCEIx        | TCINVx      | TCINVx      |            | CNTEO               | TRGEO       | OVFEO  |  |

| 0x20         | EVCTRL               | 23:16        |               |              |             |             | MCEIx      | MCEIx               | MCEIx       | MCEIx  |  |

|              |                      | 31:24        |               |              |             |             | MCEOx      | MCEOx               | MCEOx       | MCEOx  |  |

|              |                      | 7:0          |               |              |             |             | ERR        | CNT                 | TRG         | OVF    |  |

| 0x24         | INTENCLR             | 15:8         | FAULTx        | FAULTx       | FAULTB      | FAULTA      | DFS        |                     | -           |        |  |

|              |                      |              |               |              |             |             |            | MCx                 | MCx         | MCx    |  |

| 0x27         | Reserved             |              |               |              |             |             |            |                     |             | inox   |  |

|              |                      | 7.0          |               |              |             |             | FRR        | CNT                 | TRG         | OVF    |  |

| 0x27<br>0x28 | Reserved<br>INTENSET | 23:16<br>7:0 |               |              |             |             | MCx<br>ERR | MCx<br>CNT          | MCx<br>TRG  |        |  |

TCC – Timer/Counter for Control Applications

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | Non-recoverable fault tri-state the output.          |

| 1     | Non-recoverable faults set the output to NRVx level. |

TCC – Timer/Counter for Control Applications

| CTRLA.RESOLUTION | Bits [n:0]     |

|------------------|----------------|

| 0x0 - NONE       | -              |

| 0x1 - DITH4      | 3:0            |

| 0x2 - DITH5      | 4:0            |

| 0x3 - DITH6      | 5:0 (depicted) |

#### 35.8.3 Event Control

| Name:     | EVCTRL               |

|-----------|----------------------|

| Offset:   | 0x02                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0       |

|--------|---|---|---|---|---|---|---------|---------|

|        |   |   |   |   |   |   | EMPTYEO | STARTEI |

| Access |   |   |   |   |   |   | R/W     | R/W     |

| Reset  |   |   |   |   |   |   | 0       | 0       |

#### Bit 1 – EMPTYEO Data Buffer Empty Event Output

This bit indicates whether or not the Data Buffer Empty event is enabled and will be generated when the Data Buffer register is empty.

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | Data Buffer Empty event is disabled and will not be generated. |

| 1     | Data Buffer Empty event is enabled and will be generated.      |

#### Bit 0 – STARTEI Start Conversion Event Input

This bit indicates whether or not the Start Conversion event is enabled and data are loaded from the Data Buffer register to the Data register upon event reception.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | A new conversion will not be triggered on any incoming event. |

| 1     | A new conversion will be triggered on any incoming event.     |

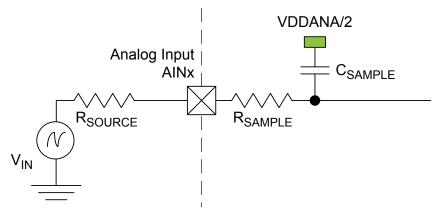

a capacitor ( $C_{\text{SAMPLE}}$ ). In addition, the source resistance ( $R_{\text{SOURCE}}$ ) must be taken into account when calculating the required sample and hold time. The next figure shows the ADC input channel equivalent circuit.

#### Figure 37-5. ADC Input

To achieve n bits of accuracy, the  $C_{SAMPLE}$  capacitor must be charged at least to a voltage of

$V_{\text{CSAMPLE}} \ge V_{\text{IN}} \times \left(1 + -2^{-(n+1)}\right)$

The minimum sampling time  $t_{\text{SAMPLEHOLD}}$  for a given  $R_{\text{SOURCE}}$  can be found using this formula:

$t_{\text{SAMPLEHOLD}} \ge (R_{\text{SAMPLE}} + R_{\text{SOURCE}}) \times (C_{\text{SAMPLE}}) \times (n+1) \times \ln(2)$

for a 12 bits accuracy:  $t_{\text{SAMPLEHOLD}} \ge (R_{\text{SAMPLE}} + R_{\text{SOURCE}}) \times (C_{\text{SAMPLE}}) \times 9.02$

where

$$t_{\text{SAMPLEHOLD}} = \frac{1}{2 \times f_{\text{ADC}}}$$

# 37.11.5 Digital-to-Analog Converter (DAC) Characteristics Table 37-31. Operating Conditions<sup>(1)</sup>

| Symbol             | Parameter                        | Conditions            | Min. | Тур.               | Max.               | Unit |

|--------------------|----------------------------------|-----------------------|------|--------------------|--------------------|------|

| V <sub>DDANA</sub> | Analog supply voltage            |                       | 2.7  | -                  | 3.63               | V    |

| AV <sub>REF</sub>  | External reference voltage       |                       | 1.0  | -                  | $V_{DDANA} - 0.6$  | V    |

|                    | Internal reference voltage 1     |                       | -    | 1                  | -                  | V    |

|                    | Internal reference voltage 2     |                       | -    | V <sub>DDANA</sub> | -                  | V    |

|                    | Linear output voltage range      |                       | 0.05 | -                  | $V_{DDANA} - 0.05$ | V    |

|                    | Minimum resistive load           |                       | 5    | -                  | -                  | kΩ   |

|                    | Maximum capacitance load         |                       | -    | -                  | 100                | pF   |

| I <sub>DD</sub>    | DC supply current <sup>(2)</sup> | Voltage pump disabled | -    | 175                | 256                | μA   |

- 1. These values are based on specifications otherwise noted.

- 2. These values are based on characterization. These values are not covered by test limits in production.

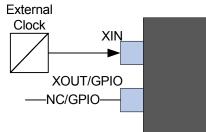

#### 38.5.1 External Clock Source

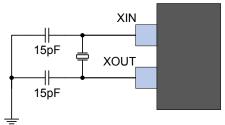

Figure 38-5. External Clock Source Example Schematic

#### Table 38-4. External Clock Source Connections

| Signal Name | Recommended Pin Connection                        | Description                        |

|-------------|---------------------------------------------------|------------------------------------|

| XIN         | XIN is used as input for an external clock signal | Input for inverting oscillator pin |

| XOUT/GPIO   | Can be left unconnected or used as normal GPIO    |                                    |

#### 38.5.2 Crystal Oscillator

#### Figure 38-6. Crystal Oscillator Example Schematic

The crystal should be located as close to the device as possible. Long signal lines may cause a load too high to operate the crystal, and cause crosstalk to other parts of the system.

#### Table 38-5. Crystal Oscillator Checklist

| Signal Name | Recommended Pin Connection            | Description                           |

|-------------|---------------------------------------|---------------------------------------|

| XIN         | Load capacitor 15pF <sup>(1)(2)</sup> | External crystal between 0.4 to 30MHz |

| XOUT        | Load capacitor 15pF <sup>(1)(2)</sup> |                                       |

- 1. These values are given only as typical examples.

- 2. Decoupling capacitor should be placed close to the device for each supply pin pair in the signal group.

#### 38.5.3 External Real Time Oscillator

The low frequency crystal oscillator is optimized for use with a 32.768kHz watch crystal. When selecting crystals, load capacitance and crystal's Equivalent Series Resistance (ESR) must be taken into consideration. Both values are specified by the crystal vendor.

The SAMHA0/1 oscillator is optimized for very low power consumption, so pay close attention when selecting crystals. See the table below for maximum ESR recommendations on 9pF and 12.5pF crystals.

The low-frequency crystal oscillator provides an internal load capacitance of typical values available in Table , *32kHz Crystal Oscillator Characteristics*. This internal load capacitance and PCB capacitance can

© 2017 Microchip Technology Inc.

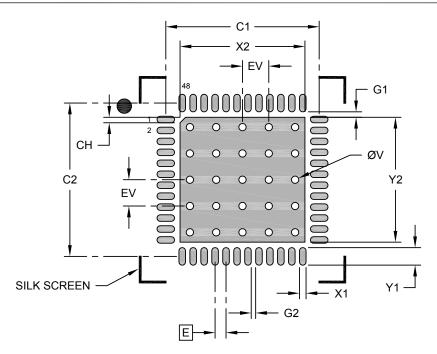

#### 48-Lead Very Thin Plastic Quad Flat, No Lead Package (SLB) - 7x7 mm Body [VQFN] With 5.6x5.6 mm Exposed Pad and Stepped Wettable Flanks

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                  | MILLIMETERS |          |      |      |

|----------------------------------|-------------|----------|------|------|

| Dimension                        | MIN         | NOM      | MAX  |      |

| Contact Pitch                    | Е           | 0.50 BSC |      |      |

| Optional Center Pad Width        | X2          |          |      | 5.70 |

| Optional Center Pad Length       | Y2          |          |      | 5.70 |

| Center Pad Corner Chamfer        | СН          |          | 0.25 |      |

| Contact Pad Spacing              | C1          |          | 7.00 |      |

| Contact Pad Spacing              | C2          |          | 7.00 |      |

| Contact Pad Width (X48)          | X1          |          |      | 0.30 |

| Contact Pad Length (X48)         | Y1          |          |      | 0.80 |

| Contact Pad to Center Pad (X48)  | G1          | 0.25     |      |      |

| Contact Pad to Contact Pad (X44) | G2          | 0.20     |      |      |

| Thermal Via Diameter             | V           |          | 0.33 |      |

| Thermal Via Pitch                | EV          |          | 1.20 |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-23413 Rev A