Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

⊡XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                                |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 48MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus SBC, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 0V ~ 3.8V                                                                       |

| Data Converters            | A/D 13x12b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 115°C (TC)                                                              |

| Mounting Type              | Surface Mount, Wettable Flank                                                   |

| Package / Case             | 48-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 48-VQFN (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamha0g16a-mzt-bvao |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 12.3.2 NVM Software Calibration Area Mapping

The NVM Software Calibration Area contains calibration data that are measured and written during production test. These calibration values should be read by the application software and written back to the corresponding register.

The NVM Software Calibration Area can be read at address 0x806020.

The NVM Software Calibration Area can not be written.

| Table 12-5. NVM Software Calibration Area Mappin | ng |

|--------------------------------------------------|----|

|--------------------------------------------------|----|

| Bit Position | Name               | Description                                                                      |

|--------------|--------------------|----------------------------------------------------------------------------------|

| 2:0          | Reserved           |                                                                                  |

| 14:3         | Reserved           |                                                                                  |

| 26:15        | Reserved           |                                                                                  |

| 34:27        | ADC LINEARITY      | ADC Linearity Calibration. Should be written to ADC CALIB register.              |

| 37:35        | ADC BIASCAL        | ADC Bias Calibration. Should be written to ADC CALIB register.                   |

| 44:38        | OSC32K CAL         | OSC32KCalibration. Should be written to SYSCTRL OSC32K register.                 |

| 49:45        | Reserved           |                                                                                  |

| 54:50        | Reserved           |                                                                                  |

| 57:55        | Reserved           |                                                                                  |

| 63:58        | DFLL48M COARSE CAL | DFLL48M Coarse calibration value. Should be written to SYSCTRL DFLLVAL register. |

| 73:64        | Reserved           |                                                                                  |

| 127:74       | Reserved           |                                                                                  |

### 12.3.3 Serial Number

Each device has a unique 128-bit serial number which is a concatenation of four 32-bit words contained at the following addresses:

Word 0: 0x0080A00C

Word 1: 0x0080A040

Word 2: 0x0080A044

Word 3: 0x0080A048

The uniqueness of the serial number is guaranteed only when using all 128 bits.

### 18.6.2.2 Enabling, Disabling and Resetting

The PM module is always enabled and can not be reset.

### 18.6.2.3 Selecting the Main Clock Source

Refer to GCLK – Generic Clock Controller for details on how to configure the main clock source.

### **Related Links**

GCLK - Generic Clock Controller

### 18.6.2.4 Selecting the Synchronous Clock Division Ratio

The main clock feeds an 8-bit prescaler, which can be used to generate the synchronous clocks. By default, the synchronous clocks run on the undivided main clock. The user can select a prescaler division for the CPU clock by writing the CPU Prescaler Selection bits in the CPU Select register (CPUSEL.CPUDIV), resulting in a CPU clock frequency determined by this equation:

$$f_{\rm CPU} = \frac{f_{\rm main}}{2^{\rm CPUDIV}}$$

Similarly, the clock for the APBx can be divided by writing their respective registers (APBxSEL.APBxDIV). To ensure correct operation, frequencies must be selected so that  $f_{CPU} \ge f_{APBx}$ . Also, frequencies must never exceed the specified maximum frequency for each clock domain.

Note: The AHB clock is always equal to the CPU clock.

CPUSEL and APBxSEL can be written without halting or disabling peripheral modules. Writing CPUSEL and APBxSEL allows a new clock setting to be written to all synchronous clocks at the same time. It is possible to keep one or more clocks unchanged. This way, it is possible to, for example, scale the CPU speed according to the required performance, while keeping the APBx frequency constant.

### 21.8.10 Interrupt Enable Clear - MODE2

| Name:     | INTENCLR        |  |  |  |

|-----------|-----------------|--|--|--|

| Offset:   | 0x06            |  |  |  |

| Reset:    | 0x00            |  |  |  |

| Property: | Write-Protected |  |  |  |

| Bit    | 7   | 6       | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|-----|---------|---|---|---|---|---|--------|

|        | OVF | SYNCRDY |   |   |   |   |   | ALARM0 |

| Access | R/W | R/W     |   |   |   |   |   | R/W    |

| Reset  | 0   | 0       |   |   |   |   |   | 0      |

**Bit 7 – OVF** Overflow Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Overflow Interrupt Enable bit and disable the corresponding interrupt.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The Overflow interrupt is disabled.                                                    |

| 1     | The Overflow interrupt is enabled, and an interrupt request will be generated when the |

|       | Overflow interrupt flag is set.                                                        |

### Bit 6 – SYNCRDY Synchronization Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Synchronization Ready Interrupt Enable bit and disable the corresponding interrupt.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The synchronization ready interrupt is disabled.                                           |

| 1     | The synchronization ready interrupt is enabled, and an interrupt request will be generated |

|       | when the Synchronization Ready interrupt flag is set.                                      |

### Bit 0 – ALARMO Alarm 0 Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit disables the Alarm 0 interrupt.

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | The Alarm 0 interrupt is disabled.                                                          |

| 1     | The Alarm 0 interrupt is enabled, and an interrupt request will be generated when the Alarm |

|       | 0 interrupt flag is set.                                                                    |

### 22.6.2.6 Transfer Triggers and Actions

A DMA transfer through a DMA channel can be started only when a DMA transfer request is detected, and the DMA channel has been granted access to the DMA. A transfer request can be triggered from software, from a peripheral, or from an event. There are dedicated Trigger Source selections for each DMA Channel Control B (CHCTRLB.TRIGSRC).

The trigger actions are available in the Trigger Action bit group in the Channel Control B register (CHCTRLB.TRIGACT). By default, a trigger generates a request for a block transfer operation. If a single descriptor is defined for a channel, the channel is automatically disabled when a block transfer has been completed. If a list of linked descriptors is defined for a channel, the channel is automatically disabled when the last descriptor in the list is executed. If the list still has descriptors to execute, the channel will be waiting for the next block transfer trigger. When enabled again, the channel will wait for the next block transfer trigger. The trigger actions can also be configured to generate a request for a beat transfer (CHCTRLB.TRIGACT=0x2) or transaction transfer (CHCTRLB.TRIGACT=0x3) instead of a block transfer (CHCTRLB.TRIGACT=0x0).

Figure 22-7 shows an example where triggers are used with two linked block descriptors.

### **Beat Trigger Action** CHENn Trigger Lost Trigger PENDCHn **BUSYCHn** Block Transfer Block Transfer Data Transfe BEAT BEAT REAT BEAT BEAT REAT **Block Trigger Action** CHENn Trigger Lost Triager PENDCHn **BUSYCHn** Block Transfer Block Transfe Data Transfer BEAT REAT BEAT BEAT BEAT BEAT **Transaction Trigger Action** CHENn Trigger Lost Trigger PENDCHn **BUSYCHn** Block Transfer Block Transfer Data Transfer BEAT BEAT BEAT BEAT BEAT BEAT

Figure 22-7. Trigger Action and Transfers

If the trigger source generates a transfer request for a channel during an ongoing transfer, the new transfer request will be kept pending (CHSTATUS.PEND=1), and the new transfer can start after the

### 22.10.3 Block Transfer Source Address

Name:SRCADDROffset:0x04Property:-

The SRCADDR register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

| Bit    | 31 | 30 | 29 | 28     | 27        | 26 | 25 | 24 |

|--------|----|----|----|--------|-----------|----|----|----|

| Γ      |    |    |    | SRCADE | DR[31:24] |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 23 | 22 | 21 | 20     | 19        | 18 | 17 | 16 |

|        |    |    |    | SRCADE | DR[23:16] |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 15 | 14 | 13 | 12     | 11        | 10 | 9  | 8  |

|        |    |    |    | SRCAD  | DR[15:8]  |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 7  | 6  | 5  | 4      | 3         | 2  | 1  | 0  |

| Γ      |    |    |    | SRCAD  | DR[7:0]   |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

### Bits 31:0 - SRCADDR[31:0] Transfer Source Address

This bit group holds the source address corresponding to the last beat transfer address in the block transfer.

| 22.10.4 | Block | Transfer | Destination | Address |

|---------|-------|----------|-------------|---------|

|         |       |          |             |         |

Name:DSTADDROffset:0x08Property:-

The DSTADDR register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

| Bit    | 31             | 30 | 29 | 28     | 27        | 26 | 25 | 24 |

|--------|----------------|----|----|--------|-----------|----|----|----|

|        | DSTADDR[31:24] |    |    |        |           |    |    |    |

| Access |                |    |    |        |           |    |    |    |

| Reset  |                |    |    |        |           |    |    |    |

|        |                |    |    |        |           |    |    |    |

| Bit    | 23             | 22 | 21 | 20     | 19        | 18 | 17 | 16 |

|        |                |    |    | DSTADE | DR[23:16] |    |    |    |

| Access |                |    |    |        |           |    |    |    |

| Reset  |                |    |    |        |           |    |    |    |

|        |                |    |    |        |           |    |    |    |

| Bit    | 15             | 14 | 13 | 12     | 11        | 10 | 9  | 8  |

|        |                |    |    | DSTAD  | DR[15:8]  |    |    |    |

| Access |                |    |    |        |           |    |    |    |

| Reset  |                |    |    |        |           |    |    |    |

|        |                |    |    |        |           |    |    |    |

| Bit    | 7              | 6  | 5  | 4      | 3         | 2  | 1  | 0  |

|        |                |    |    | DSTAD  | DR[7:0]   |    |    |    |

| Access |                |    |    |        |           |    |    |    |

| Reset  |                |    |    |        |           |    |    |    |

### Bits 31:0 – DSTADDR[31:0] Transfer Destination Address

This bit group holds the destination address corresponding to the last beat transfer address in the block transfer.

### 23.5.5 Interrupts

There are several interrupt request lines, at least one for the external interrupts (EXTINT) and one for non-maskable interrupt (NMI).

The EXTINT interrupt request line is connected to the interrupt controller. Using the EIC interrupt requires the interrupt controller to be configured first.

The NMI interrupt request line is also connected to the interrupt controller, but does not require the interrupt to be configured.

### **Related Links**

Nested Vector Interrupt Controller

### 23.5.6 Events

The events are connected to the Event System. Using the events requires the Event System to be configured first.

### **Related Links**

EVSYS – Event System

### 23.5.7 Debug Operation

When the CPU is halted in debug mode, the EIC continues normal operation. If the EIC is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

### 23.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

- Interrupt Flag Status and Clear register (INTFLAG)

- Non-Maskable Interrupt Flag Status and Clear register (NMIFLAG)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

# **Related Links**

PAC - Peripheral Access Controller

### 23.5.9 Analog Connections

Not applicable.

### 23.6 Functional Description

### 23.6.1 Principle of Operation

The EIC detects edge or level condition to generate interrupts to the CPU interrupt controller or events to the Event System. Each external interrupt pin (EXTINT) can be filtered using majority vote filtering, clocked by GCLK\_EIC

### 23.6.2 Basic Operation

### 23.6.2.1 Initialization

The EIC must be initialized in the following order:

- 1. Enable CLK\_EIC\_APB

- 2. If edge detection or filtering is required, GCLK\_EIC must be enabled

- 3. Write the EIC configuration registers (EVCTRL, WAKEUP, CONFIGy)

- 4. Enable the EIC

To use NMI, GCLK\_EIC must be enabled after EIC configuration (NMICTRL).

### 23.6.2.2 Enabling, Disabling and Resetting

The EIC is enabled by writing a '1' the Enable bit in the Control register (CTRL.ENABLE). The EIC is disabled by writing CTRL.ENABLE to '0'.

The EIC is reset by setting the Software Reset bit in the Control register (CTRL.SWRST). All registers in the EIC will be reset to their initial state, and the EIC will be disabled.

Refer to the CTRL register description for details.

### 23.6.3 External Pin Processing

Each external pin can be configured to generate an interrupt/event on edge detection (rising, falling or both edges) or level detection (high or low). The sense of external interrupt pins is configured by writing the Input Sense x bits in the Config n register (CONFIGn.SENSEx). The corresponding interrupt flag (INTFLAG.EXTINT[x]) in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition is met.

When the interrupt flag has been cleared in edge-sensitive mode, INTFLAG.EXTINT[x] will only be set if a new interrupt condition is met. In level-sensitive mode, when interrupt has been cleared, INTFLAG.EXTINT[x] will be set immediately if the EXTINTx pin still matches the interrupt condition.

Each external pin can be filtered by a majority vote filtering, clocked by GCLK\_EIC. Filtering is enabled if bit Filter Enable x in the Configuration n register (CONFIGn.FILTENx) is written to '1'. The majority vote filter samples the external pin three times with GCLK\_EIC and outputs the value when two or more samples are equal.

### Table 23-1. Majority Vote Filter

| Samples [0, 1, 2] | Filter Output |

|-------------------|---------------|

| [0,0,0]           | 0             |

| [0,0,1]           | 0             |

| [0,1,0]           | 0             |

| [0,1,1]           | 1             |

| [1,0,0]           | 0             |

| [1,0,1]           | 1             |

| [1,1,0]           | 1             |

| [1,1,1]           | 1             |

When an external interrupt is configured for level detection, or if filtering is disabled, detection is made asynchronously, and GCLK\_EIC is not required.

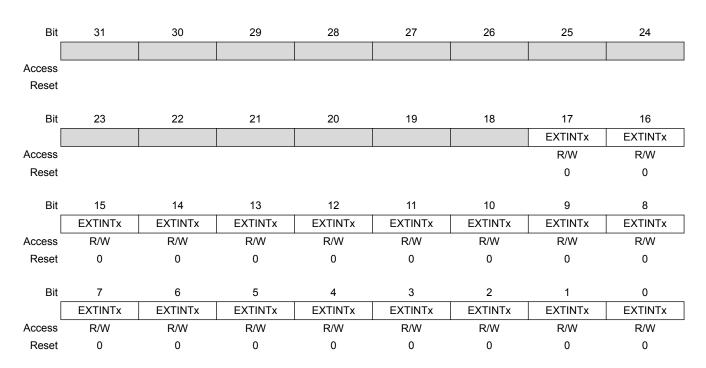

### 23.8.7 Interrupt Enable Set

| Name:     | INTENSET        |

|-----------|-----------------|

| Offset:   | 0x0C            |

| Reset:    | 0x0000000       |

| Property: | Write-Protected |

**Bits 17,16,15,14,13,12,11,10,9,8,7,6,5,4,3,2,1,0 – EXTINTx** External Interrupt x Enable [x=17..0] Writing a zero to this bit has no effect.

Writing a one to this bit will set the External Interrupt x Enable bit, which enables the external interrupt.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

### • Status register (STATUS)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

### **Related Links**

PAC - Peripheral Access Controller

### 24.5.6 Analog Connections

Not applicable.

### 24.6 Functional Description

### 24.6.1 Principle of Operation

The NVM Controller is a slave on the AHB and APB buses. It responds to commands, read requests and write requests, based on user configuration.

### 24.6.1.1 Initialization

After power up, the NVM Controller goes through a power-up sequence. During this time, access to the NVM Controller from the AHB bus is halted. Upon power-up completion, the NVM Controller is operational without any need for user configuration.

### 24.6.2 Memory Organization

Refer to the Physical Memory Map for memory sizes and addresses for each device.

The NVM is organized into rows, where each row contains four pages, as shown in the NVM Row Organization figure. The NVM has a row-erase granularity, while the write granularity is by page. In other words, a single row erase will erase all four pages in the row, while four write operations are used to write the complete row.

### Figure 24-2. NVM Row Organization

| Row n | Page (n*4) + 3 | Page (n*4) + 2 | Page (n*4) + 1 | Page (n*4) + 0 |  |

|-------|----------------|----------------|----------------|----------------|--|

|-------|----------------|----------------|----------------|----------------|--|

The NVM block contains a calibration and auxiliary space plus a dedicated EEPROM emulation space that are memory mapped. Refer to the NVM Organization figure below for details.

The calibration and auxiliary space contains factory calibration and system configuration information. These spaces can be read from the AHB bus in the same way as the main NVM main address space.

In addition, a boot loader section can be allocated at the beginning of the main array, and an EEPROM section can be allocated at the end of the NVM main address space.

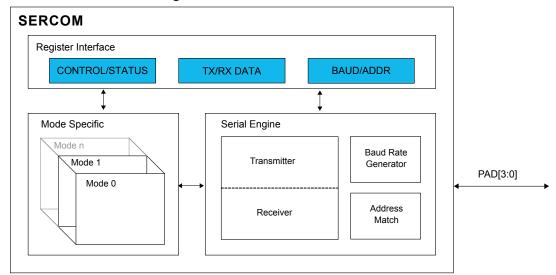

### 27.3 Block Diagram

Figure 27-1. SERCOM Block Diagram

### 27.4 Signal Description

See the respective SERCOM mode chapters for details.

## Related Links SERCOM USART SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit

## 27.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

### 27.5.1 I/O Lines

Using the SERCOM I/O lines requires the I/O pins to be configured using port configuration (PORT).

The SERCOM has four internal pads, PAD[3:0], and the signals from I2C, SPI and USART are routed through these SERCOM pads via a multiplexer. The configuration of the multiplexer is available from the different SERCOM modes. Refer to the mode specific chapters for details.

### **Related Links**

SERCOM USART SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit PORT: IO Pin Controller Block Diagram

### 27.5.2 Power Management

The SERCOM can operate in any Sleep mode provided the selected clock source is running. SERCOM interrupts can be configured to wake the device from Sleep modes.

This bit is not synchronized.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Asynchronous communication. |

| 1     | Synchronous communication.  |

### Bits 27:24 – FORM[3:0] Frame Format

These bits define the frame format.

These bits are not synchronized.

| FORM[3:0] | Description                                            |

|-----------|--------------------------------------------------------|

| 0x0       | USART frame                                            |

| 0x1       | USART frame with parity                                |

| 0x2-0x3   | Reserved                                               |

| 0x4       | Auto-baud (LIN Slave) - break detection and auto-baud. |

| 0x5       | Auto-baud - break detection and auto-baud with parity  |

| 0x6-0xF   | Reserved                                               |

### Bits 23:22 – SAMPA[1:0] Sample Adjustment

These bits define the sample adjustment.

These bits are not synchronized.

| SAMPA[1:0] | 16x Over-sampling (CTRLA.SAMPR=0 or 1) | 8x Over-sampling (CTRLA.SAMPR=2 or 3) |

|------------|----------------------------------------|---------------------------------------|

| 0x0        | 7-8-9                                  | 3-4-5                                 |

| 0x1        | 9-10-11                                | 4-5-6                                 |

| 0x2        | 11-12-13                               | 5-6-7                                 |

| 0x3        | 13-14-15                               | 6-7-8                                 |

### Bits 21:20 – RXPO[1:0] Receive Data Pinout

These bits define the receive data (RxD) pin configuration.

These bits are not synchronized.

| RXPO[1:0] | Name   | Description                              |

|-----------|--------|------------------------------------------|

| 0x0       | PAD[0] | SERCOM PAD[0] is used for data reception |

| 0x1       | PAD[1] | SERCOM PAD[1] is used for data reception |

| 0x2       | PAD[2] | SERCOM PAD[2] is used for data reception |

| 0x3       | PAD[3] | SERCOM PAD[3] is used for data reception |

### Bits 17:16 – TXPO[1:0] Transmit Data Pinout

These bits define the transmit data (TxD) and XCK pin configurations.

### 28.8.3 Control C

Name:CTRLCOffset:0x08Reset:0x0000000Property:PAC Write-Protection, Enable-Protected

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

# ATSAMHAXGXXA SERCOM I2C – Inter-Integrated Circuit

# Figure 30-7. SCL Timing

The following parameters are timed using the SCL low time period  $T_{LOW}$ . This comes from the Master Baud Rate Low bit group in the Baud Rate register (BAUD.BAUDLOW). When BAUD.BAUDLOW=0, or the Master Baud Rate bit group in the Baud Rate register (BAUD.BAUD) determines it.

- T<sub>LOW</sub> Low period of SCL clock

- T<sub>SU:STO</sub> Set-up time for stop condition

- T<sub>BUF</sub> Bus free time between stop and start conditions

- T<sub>HD:STA</sub> Hold time (repeated) start condition

- T<sub>SU;STA</sub> Set-up time for repeated start condition

- T<sub>HIGH</sub> is timed using the SCL high time count from BAUD.BAUD

- T<sub>RISE</sub> is determined by the bus impedance; for internal pull-ups. Refer to *Electrical Characteristics*.

- T<sub>FALL</sub> is determined by the open-drain current limit and bus impedance; can typically be regarded as zero. Refer to *Electrical Characteristics* for details.

The SCL frequency is given by:

$$f_{\rm SCL} = \frac{1}{T_{\rm LOW} + T_{\rm HIGH} + T_{\rm RISE}}$$

When BAUD.BAUDLOW is zero, the BAUD.BAUD value is used to time both SCL high and SCL low. In this case the following formula will give the SCL frequency:

$$f_{\rm SCL} = \frac{f_{\rm GCLK}}{10 + 2BAUD + f_{\rm GCLK} \cdot T_{\rm RISE}}$$

When BAUD.BAUDLOW is non-zero, the following formula determines the SCL frequency:

$$f_{\rm SCL} = \frac{f_{\rm GCLK}}{10 + BAUD + BAUDLOW + f_{\rm GCLK} \cdot T_{\rm RISE}}$$

The following formulas can determine the SCL  $T_{\text{LOW}}$  and  $T_{\text{HIGH}}$  times:

$$T_{\text{LOW}} = \frac{BAUDLOW + 5}{f_{\text{GCLK}}}$$

$$T_{\text{HIGH}} = \frac{BAUD + 5}{f_{\text{GCLK}}}$$

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

### 30.8.2 Control B

| Name:     | CTRLB                                                      |

|-----------|------------------------------------------------------------|

| Offset:   | 0x04                                                       |

| Reset:    | 0x0000000                                                  |

| Property: | PAC Write-Protection, Enable-Protected, Write-Synchronized |

| Bit    | 31   | 30      | 29 | 28 | 27 | 26     | 25   | 24     |

|--------|------|---------|----|----|----|--------|------|--------|

|        |      |         |    |    |    |        |      |        |

| Access |      |         |    |    |    |        |      |        |

| Reset  |      |         |    |    |    |        |      |        |

|        |      |         |    |    |    |        |      |        |

| Bit    | 23   | 22      | 21 | 20 | 19 | 18     | 17   | 16     |

|        |      |         |    |    |    | ACKACT | CME  | D[1:0] |

| Access |      | •       | •  |    |    | R/W    | W    | W      |

| Reset  |      |         |    |    |    | 0      | 0    | 0      |

|        |      |         |    |    |    |        |      |        |

| Bit    | 15   | 14      | 13 | 12 | 11 | 10     | 9    | 8      |

|        | AMOE | DE[1:0] |    |    |    | AACKEN | GCMD | SMEN   |

| Access | R/W  | R/W     |    |    |    | R/W    | R/W  | R/W    |

| Reset  | 0    | 0       |    |    |    | 0      | 0    | 0      |

|        |      |         |    |    |    |        |      |        |

| Bit    | 7    | 6       | 5  | 4  | 3  | 2      | 1    | 0      |

|        |      |         |    |    |    |        |      |        |

| Access |      |         |    |    |    | 1      |      |        |

Access Reset

### Bit 18 – ACKACT Acknowledge Action

This bit defines the slave's acknowledge behavior after an address or data byte is received from the master. The acknowledge action is executed when a command is written to the CMD bits. If smart mode is enabled (CTRLB.SMEN=1), the acknowledge action is performed when the DATA register is read.

This bit is not enable-protected.

| Value | Description |

|-------|-------------|

| 0     | Send ACK    |

| 1     | Send NACK   |

### Bits 17:16 – CMD[1:0] Command

This bit field triggers the slave operation as the below. The CMD bits are strobe bits, and always read as zero. The operation is dependent on the slave interrupt flags, INTFLAG.DRDY and INTFLAG.AMATCH, in addition to STATUS.DIR.

All interrupt flags (INTFLAG.DRDY, INTFLAG.AMATCH and INTFLAG.PREC) are automatically cleared when a command is given.

This bit is not enable-protected.

In both cases, the request is cleared by hardware on DMA acknowledge.

| Channel                     | A DMA request is set only on a compare match if CTRLA.DMAOS=0. The request is cleared by hardware on DMA acknowledge.                                                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Match (MCx)                 | When CTRLA.DMAOS=1, the DMA requests are not generated.                                                                                                                                               |

| Channel<br>Capture<br>(MCx) | For a capture channel, the request is set when valid data is present in the CCx register, and cleared once the CCx register is read.<br>In this operation mode, the CTRLA.DMAOS bit value is ignored. |

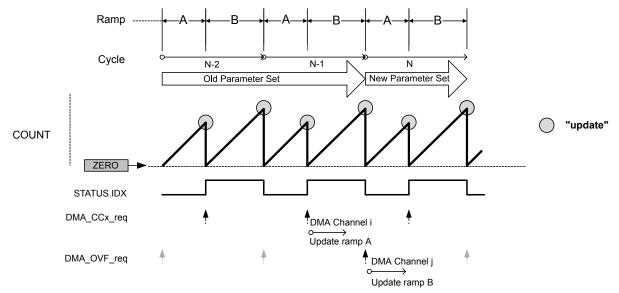

### DMA Operation with Circular Buffer

When circular buffer operation is enabled, the buffer registers must be written in a correct order and synchronized to the update times of the timer. The DMA triggers of the TCC provide a way to ensure a safe and correct update of circular buffers.

**Note:** Circular buffer are intended to be used with RAMP2, RAMP2A and DSBOTH operation only.

### DMA Operation with Circular Buffer in RAMP2 and RAMP2A Mode

When a CCx channel is selected as a circular buffer, the related DMA request is not set on a compare match detection, but on start of ramp B.

If at least one circular buffer is enabled, the DMA overflow request is conditioned to the start of ramp A with an effective DMA transfer on previous ramp B (DMA acknowledge).

The update of all circular buffer values for ramp A can be done through a DMA channel triggered on a MC trigger. The update of all circular buffer values for ramp B, can be done through a second DMA channel triggered by the overflow DMA request.

### Figure 32-35. DMA Triggers in RAMP and RAMP2 Operation Mode and Circular Buffer Enabled

DMA Operation with Circular Buffer in DSBOTH Mode

When a CC channel is selected as a circular buffer, the related DMA request is not set on a compare match detection, but on start of down-counting phase.

If at least one circular buffer is enabled, the DMA overflow request is conditioned to the start of upcounting phase with an effective DMA transfer on previous down-counting phase (DMA acknowledge). **TCC – Timer/Counter for Control Applications**

| Value | Description                                                          |

|-------|----------------------------------------------------------------------|

| 0     | The TCC will count continuously.                                     |

| 1     | The TCC will stop counting on the next underflow/overflow condition. |

### Bit 1 – LUPD Lock Update

This bit controls the update operation of the TCC buffered registers.

When CTRLB.LUPD is set, no any update of the registers with value of its buffered register is performed on hardware UPDATE condition. Locking the update ensures that all buffer registers are valid before an hardware update is performed. After all the buffer registers are loaded correctly, the buffered registers can be unlocked.

This bit has no effect when input capture operation is enabled.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will lock updating.

| Value | Description                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The CCBx, PERB, PGVB, PGOB, and SWAPBx buffer registers values are copied into the                                                                             |

|       | corresponding CCx, PER, PGV, PGO and SWAPx registers on hardware update condition.                                                                             |

| 1     | The CCBx, PERB, PGVB, PGOB, and SWAPBx buffer registers values are <i>not</i> copied into CCx, PER, PGV, PGO and SWAPx registers on hardware update condition. |

### Bit 0 – DIR Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

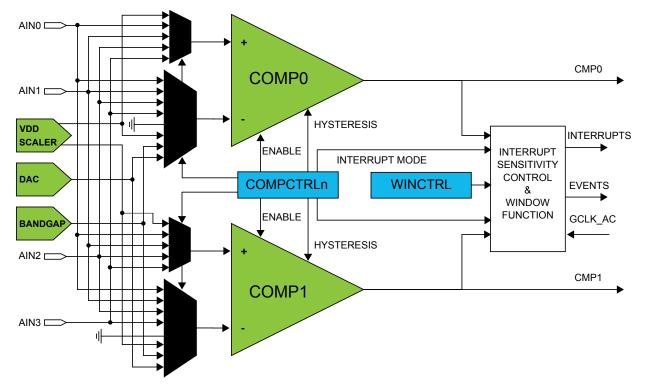

### 34.3 Block Diagram

Figure 34-1. Analog Comparator Block Diagram

### 34.4 Signal Description

| Signal  | Description    | Туре               |

|---------|----------------|--------------------|

| AIN[30] | Analog input   | Comparator inputs  |

| CMP[10] | Digital output | Comparator outputs |

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

### **Related Links**

I/O Multiplexing and Considerations

### 34.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

### 34.5.1 I/O Lines

Using the AC's I/O lines requires the I/O pins to be configured. Refer to *PORT - I/O Pin Controller* for details.

### **Related Links**

PORT - I/O Pin Controller

# **ATSAMHAXGXXA**

### **Electrical Characteristics**

| Parameter                 | Conditions               | Symbol | Min. | Тур. | Max. | Unit |

|---------------------------|--------------------------|--------|------|------|------|------|

| Total Harmonic Distortion | A <sub>IN</sub> = 95%FSR | THD    | -75  | -71  | -67  | dB   |

| Noise RMS                 | T = 25°C                 |        | 0.6  | 1    | 2.5  | mV   |

- 1. Maximum numbers are based on characterization and not tested in production, and valid for 5% to 95% of the input voltage range.

- 2. Dynamic parameter numbers are based on characterization and not tested in production.

- Respect the input common mode voltage through the following equations (where VCM\_IN is the Input channel common mode voltage): If |VIN| > VREF/4

VCM\_IN < 0.95 × VDDANA + VREF/4 – 0.75V

VCM\_IN > VREF/4 -0.05 × VDDANA - 0.1V

If |VIN| < VREF/4

VCM\_IN < 1.2 × VDDANA – 0.75V

$VCM_IN > 0.2 \times VDDANA - 0.1V$

- 4. The ADC channels on pins PA08, PA09, PA10, PA11 are powered from the VDDIO power supply. The ADC performance of these pins will not be the same as all the other ADC channels on pins powered from the VDDANA power supply.

- 5. The gain accuracy represents the gain error expressed in percent. Gain accuracy (%) = (Gain Error in V × 100) / (2 × Vref/GAIN)

| Parameter                      | Conditions                                                                   | Symbol | Min. | Тур.  | Max.  | Unit |

|--------------------------------|------------------------------------------------------------------------------|--------|------|-------|-------|------|

| Effective Number of Bits       | With gain compensation                                                       | ENOB   | -    | 9.6   | 10.1  | Bits |

| Total Unadjusted Error         | 1x gain                                                                      | TUE    | 3    | 11    | 74    | LSB  |

| Integral Nonlinearity          | 1x gain                                                                      | INL    | 1    | 4     | 11    | LSB  |

| Differential Nonlinearity      | 1x gain                                                                      | DNL    | -    | ±0.5  | ±0.95 | LSB  |

| Gain Error                     | Ext. Ref. 1x                                                                 |        | -    | ±0.9  | ±10   | mV   |

| Gain Accuracy <sup>(4)</sup>   | Ext. Ref. 0.5x                                                               |        | -    | ±0.2  | ±0.5  | %    |

|                                | Ext. Ref. 2x to 16X                                                          |        | -    | ±0.15 | ±0.3  | %    |

| Offset Error                   | Ext. Ref. 1x                                                                 |        | -    | ±3    | ±40   | mV   |

| Spurious Free Dynamic Range    | 1x Gain<br>$F_{CLK\_ADC} = 2.1MHz$<br>$F_{IN} = 40kHz$<br>$A_{IN} = 95\%FSR$ | SFDR   | 63   | 68    | 70.1  | dB   |

| Signal-to-Noise and Distortion |                                                                              | SINAD  | 55   | 60.1  | 62.5  | dB   |

| Signal-to-Noise Ratio          |                                                                              | SNR    | 54   | 61    | 64    | dB   |

| Total Harmonic Distortion      |                                                                              | THD    | -70  | -68   | -65   | dB   |

| Noise RMS                      | T = 25°C                                                                     |        | -    | 1     | 5     | mV   |

### Table 37-28. Single-Ended Mode

### Note: