Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | ARM® Cortex®-M0+                                                                |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 48MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus SBC, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 1K x 8                                                                          |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 0V ~ 3.8V                                                                       |

| Data Converters            | A/D 13x12b; D/A 1x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TC)                                                              |

| Mounting Type              | Surface Mount, Wettable Flank                                                   |

| Package / Case             | 48-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 48-VQFN (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamha1g15a-mbt-bvao |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

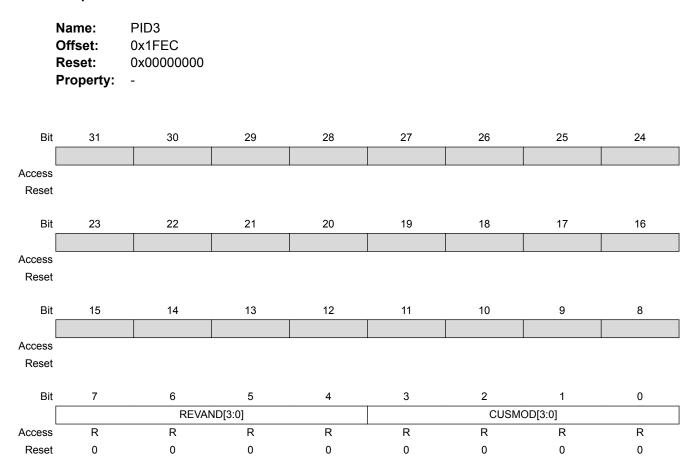

#### 15.13.18 Peripheral Identification 3

**Bits 7:4 – REVAND[3:0]** Revision Number These bits will always return 0x0 when read.

Bits 3:0 - CUSMOD[3:0] ARM CUSMOD

These bits will always return 0x0 when read.

## 15.13.19 Component Identification 0

|        | Name:<br>Offset:<br>Reset:<br>Property: | CID0<br>0x1FF0<br>0x0000000D<br>- |    |        |           |    |    |    |

|--------|-----------------------------------------|-----------------------------------|----|--------|-----------|----|----|----|

| Bit    | 31                                      | 30                                | 29 | 28     | 27        | 26 | 25 | 24 |

|        |                                         |                                   |    |        |           |    |    |    |

| Access |                                         |                                   |    |        |           |    |    |    |

| Reset  |                                         |                                   |    |        |           |    |    |    |

|        |                                         |                                   |    |        |           |    |    |    |

| Bit    | 23                                      | 22                                | 21 | 20     | 19        | 18 | 17 | 16 |

|        |                                         |                                   |    |        |           |    |    |    |

| Access |                                         |                                   |    |        |           |    |    |    |

| Reset  |                                         |                                   |    |        |           |    |    |    |

| Bit    | 15                                      | 14                                | 13 | 12     | 11        | 10 | 9  | 8  |

| DI     | 15                                      | 14                                | 15 | 12     | 11        | 10 | 3  | 0  |

| Access |                                         |                                   |    |        |           |    |    |    |

| Reset  |                                         |                                   |    |        |           |    |    |    |

| Reber  |                                         |                                   |    |        |           |    |    |    |

| Bit    | 7                                       | 6                                 | 5  | 4      | 3         | 2  | 1  | 0  |

|        |                                         |                                   |    | PREAMB | LEB0[7:0] |    |    |    |

| Access | R                                       | R                                 | R  | R      | R         | R  | R  | R  |

| Reset  |                                         | 0                                 | 0  | 0      | 1         | 1  | 0  | 1  |

|        |                                         |                                   |    |        |           |    |    |    |

**Bits 7:0 – PREAMBLEB0[7:0]** Preamble Byte 0 These bits will always return 0x000000D when read.

### 18.5.3 Clocks

The PM bus clock (CLK\_PM\_APB) can be enabled and disabled in the Power Manager, and the default state of CLK\_PM\_APB can be found in *Peripheral Clock Default State* table in the *Peripheral Clock Masking* section. If this clock is disabled in the Power Manager, it can only be re-enabled by a reset.

A generic clock (GCLK\_MAIN) is required to generate the main clock. The clock source for GCLK\_MAIN is configured by default in the Generic Clock Controller, and can be reconfigured by the user if needed. Refer to *GCLK* – *Generic Clock Controller* for details.

### **Related Links**

Peripheral Clock Masking GCLK - Generic Clock Controller

### 18.5.3.1 Main Clock

The main clock (CLK\_MAIN) is the common source for the synchronous clocks. This is fed into the common 8-bit prescaler that is used to generate synchronous clocks to the CPU, AHB and APBx modules.

### 18.5.3.2 CPU Clock

The CPU clock (CLK\_CPU) is routed to the CPU. Halting the CPU clock inhibits the CPU from executing instructions.

### 18.5.3.3 AHB Clock

The AHB clock (CLK\_AHB) is the root clock source used by peripherals requiring an AHB clock. The AHB clock is always synchronous to the CPU clock and has the same frequency, but may run even when the CPU clock is turned off. A clock gate is inserted from the common AHB clock to any AHB clock of a peripheral.

### 18.5.3.4 APBx Clocks

The APBx clock (CLK\_APBX) is the root clock source used by modules requiring a clock on the APBx bus. The APBx clock is always synchronous to the CPU clock, but can be divided by a prescaler, and will run even when the CPU clock is turned off. A clock gater is inserted from the common APB clock to any APBx clock of a module on APBx bus.

### 18.5.4 DMA

Not applicable.

### 18.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the PM interrupt requires the Interrupt Controller to be configured first. Refer to *Nested Vector Interrupt Controller* for details.

### **Related Links**

Nested Vector Interrupt Controller

### 18.5.6 Events

Not applicable.

### 18.5.7 Debug Operation

When the CPU is halted in debug mode, the PM continues normal operation. In sleep mode, the clocks generated from the PM are kept running to allow the debugger accessing any modules. As a consequence, power measurements are not possible in debug mode.

# ATSAMHAXGXXA WDT – Watchdog Timer

NVM User Row Mapping

| Name:     | INTENCLR        |

|-----------|-----------------|

| Offset:   | 0x06            |

| Reset:    | 0x00            |

| Property: | Write-Protected |

| Bit    | 7   | 6       | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|-----|---------|---|---|---|---|---|------|

|        | OVF | SYNCRDY |   |   |   |   |   | CMP0 |

| Access | R/W | R/W     |   |   |   |   |   | R/W  |

| Reset  | 0   | 0       |   |   |   |   |   | 0    |

**Bit 7 – OVF** Overflow Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Overflow Interrupt Enable bit and disable the corresponding interrupt.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The Overflow interrupt is disabled.                                                    |

| 1     | The Overflow interrupt is enabled, and an interrupt request will be generated when the |

|       | Overflow interrupt flag is set.                                                        |

### Bit 6 – SYNCRDY Synchronization Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Synchronization Ready Interrupt Enable bit and disable the corresponding interrupt.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The Synchronization Ready interrupt is disabled.                                           |

| 1     | The Synchronization Ready interrupt is enabled, and an interrupt request will be generated |

|       | when the Synchronization Ready interrupt flag is set.                                      |

Bit 0 – CMP0 Compare 0 Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Compare 0 Interrupt Enable bit and disable the corresponding interrupt.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The Compare 0 interrupt is disabled.                                                    |

| 1     | The Compare 0 interrupt is enabled, and an interrupt request will be generated when the |

|       | Compare x interrupt flag is set.                                                        |

#### 21.8.26 Alarm 0 Value - MODE2

Name:ALARM0Offset:0x18Reset:0x0000000Property:Write-Protected, Write-Synchronized

The 32-bit value of ALARM0 is continuously compared with the 32-bit CLOCK value, based on the masking set by MASKn.SEL. When a match occurs, the Alarm 0 interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.ALARMn) is set on the next counter cycle, and the counter is cleared if CTRL.MATCHCLR is one.

| Bit    | 31   | 30        | 29     | 28  | 27          | 26      | 25  | 24        |

|--------|------|-----------|--------|-----|-------------|---------|-----|-----------|

|        |      | YEAR[5:0] |        |     |             |         |     | ITH[3:2]  |

| Access | R/W  | R/W       | R/W    | R/W | R/W         | R/W     | R/W | R/W       |

| Reset  | 0    | 0         | 0      | 0   | 0           | 0       | 0   | 0         |

|        |      |           |        |     |             |         |     |           |

| Bit    | 23   | 22        | 21     | 20  | 19          | 18      | 17  | 16        |

|        | MON  | TH[1:0]   |        |     | DAY[4:0]    |         |     | HOUR[4:4] |

| Access | R/W  | R/W       | R/W    | R/W | R/W         | R/W     | R/W | R/W       |

| Reset  | 0    | 0         | 0      | 0   | 0           | 0       | 0   | 0         |

|        |      |           |        |     |             |         |     |           |

| Bit    | 15   | 14        | 13     | 12  | 11          | 10      | 9   | 8         |

|        |      | HOU       | R[3:0] |     | MINUTE[5:2] |         |     |           |

| Access | R/W  | R/W       | R/W    | R/W | R/W         | R/W     | R/W | R/W       |

| Reset  | 0    | 0         | 0      | 0   | 0           | 0       | 0   | 0         |

|        |      |           |        |     |             |         |     |           |

| Bit    | 7    | 6         | 5      | 4   | 3           | 2       | 1   | 0         |

|        | MINU | TE[1:0]   |        |     | SECO        | ND[5:0] |     |           |

| Access | R/W  | R/W       | R/W    | R/W | R/W         | R/W     | R/W | R/W       |

| Reset  | 0    | 0         | 0      | 0   | 0           | 0       | 0   | 0         |

### Bits 31:26 - YEAR[5:0] Year

The alarm year. Years are only matched if MASKn.SEL is 6.

### Bits 25:22 - MONTH[3:0] Month

The alarm month. Months are matched only if MASKn.SEL is greater than 4.

### Bits 21:17 - DAY[4:0] Day

The alarm day. Days are matched only if MASKn.SEL is greater than 3.

#### Bits 16:12 – HOUR[4:0] Hour

The alarm hour. Hours are matched only if MASKn.SEL is greater than 2.

### Bits 11:6 - MINUTE[5:0] Minute

The alarm minute. Minutes are matched only if MASKn.SEL is greater than 1.

### Bits 5:0 - SECOND[5:0] Second

The alarm second. Seconds are matched only if MASKn.SEL is greater than 0.

© 2017 Microchip Technology Inc.

**DMAC – Direct Memory Access Controller**

| Offset | Name       | Bit Pos. |       |         |        |      |         |         |            |        |

|--------|------------|----------|-------|---------|--------|------|---------|---------|------------|--------|

|        |            | 31:24    |       |         |        |      |         |         |            |        |

|        |            | 7:0      |       |         |        |      | LVLEXx  | LVLEXx  | LVLEXx     | LVLEXx |

| 020    |            | 15:8     | ABUSY |         |        |      |         | ID[4:0] |            | 1      |

| 0x30   | ACTIVE     | 23:16    |       |         |        | BTCN | IT[7:0] |         |            |        |

|        |            | 31:24    |       |         |        | BTCN | T[15:8] |         |            |        |

|        |            | 7:0      |       |         |        |      |         |         |            |        |

| 024    |            | 15:8     |       |         |        |      |         |         |            |        |

| 0x34   | BASEADDR   | 23:16    |       |         |        |      |         |         |            |        |

|        |            | 31:24    |       |         |        |      |         |         |            |        |

|        |            | 7:0      |       |         |        |      |         |         |            |        |

| 0.00   |            | 15:8     |       |         |        |      |         |         |            |        |

| 0x38   | WRBADDR    | 23:16    |       |         |        |      |         |         |            |        |

|        |            | 31:24    |       |         |        |      |         |         |            |        |

| 0x3C   |            |          |       |         |        |      |         |         |            |        |

|        | Reserved   |          |       |         |        |      |         |         |            |        |

| 0x3E   |            |          |       |         |        |      |         |         |            |        |

| 0x3F   | CHID       | 7:0      |       |         |        |      |         | ID[     | 3:0]       |        |

| 0x40   | CHCTRLA    | 7:0      |       |         |        |      |         |         | ENABLE     | SWRST  |

| 0x41   |            |          |       |         |        |      |         |         |            |        |

|        | Reserved   |          |       |         |        |      |         |         |            |        |

| 0x43   |            |          |       |         |        |      |         |         |            |        |

|        |            | 7:0      |       | LV      | L[1:0] | EVOE | EVIE    |         | EVACT[2:0] |        |

| 0      |            | 15:8     |       |         |        |      | TRIGS   | RC[5:0] |            |        |

| 0x44   | CHCTRLB    | 23:16    | TRIGA | CT[1:0] |        |      |         |         |            |        |

|        |            | 31:24    | :24   |         |        |      |         |         | CME        | 0[1:0] |

| 0x48   |            |          |       |         |        |      |         |         |            |        |

|        | Reserved   |          |       |         |        |      |         |         |            |        |

| 0x4B   |            |          |       |         |        |      |         |         |            |        |

| 0x4C   | CHINTENCLR | 7:0      |       |         |        |      |         | SUSP    | TCMPL      | TERR   |

| 0x4D   | CHINTENSET | 7:0      |       |         |        |      |         | SUSP    | TCMPL      | TERR   |

| 0x4E   | CHINTFLAG  | 7:0      |       |         |        |      |         | SUSP    | TCMPL      | TERR   |

| 0x4F   | CHSTATUS   | 7:0      |       |         |        |      |         | FERR    | BUSY       | PEND   |

# 22.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description. Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

### 25.9.13 Pin Configuration

| Name:     | PINCFG                |

|-----------|-----------------------|

| Offset:   | 0x40 + n*0x01 [n=031] |

| Reset:    | 0x00                  |

| Property: | PAC Write-Protection  |

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

There are up to 32 Pin Configuration registers in each PORT group, one for each I/O line.

| Bit    | 7 | 6      | 5 | 4 | 3 | 2      | 1    | 0      |

|--------|---|--------|---|---|---|--------|------|--------|

|        |   | DRVSTR |   |   |   | PULLEN | INEN | PMUXEN |

| Access |   | RW     |   |   |   | RW     | RW   | RW     |

| Reset  |   | 0      |   |   |   | 0      | 0    | 0      |

### **Bit 6 – DRVSTR** Output Driver Strength Selection

This bit controls the output driver strength of an I/O pin configured as an output.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Pin drive strength is set to normal drive strength.   |

| 1     | Pin drive strength is set to stronger drive strength. |

### Bit 2 - PULLEN Pull Enable

This bit enables the internal pull-up or pull-down resistor of an I/O pin configured as an input.

| Value | Description                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| 0     | Internal pull resistor is disabled, and the input is in a high-impedance configuration.                               |

| 1     | Internal pull resistor is enabled, and the input is driven to a defined logic level in the absence of external input. |

### Bit 1 - INEN Input Enable

This bit controls the input buffer of an I/O pin configured as either an input or output.

Writing a zero to this bit disables the input buffer completely, preventing read-back of the physical pin state when the pin is configured as either an input or output.

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | Input buffer for the I/O pin is disabled, and the input value will not be sampled.          |

| 1     | Input buffer for the I/O pin is enabled, and the input value will be sampled when required. |

# EVSYS – Event System

| USER[7:0] User Multiplexer Description |            | Description          | Path Type              |  |

|----------------------------------------|------------|----------------------|------------------------|--|

| 0x1C                                   | PTC STCONV | PTC start conversion | Asynchronous path only |  |

| 0x1D-0x1F                              | Reserved   |                      | Reserved               |  |

transferred to the two-level receive buffer. The transfer takes place in the same clock cycle as the last data bit is shifted in. And the Receive Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) will be set. The received data can be retrieved by reading DATA.

When the last character has been transmitted and there is no valid data in DATA, the Transmit Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.TXC) will be set. When the transaction is finished, the master must pull the  $\overline{SS}$  line high to notify the slave. If Master Slave Select Enable (CTRLB.MSSEN) is set to '0', the software must pull the  $\overline{SS}$  line high.

### Slave

In slave mode (CTRLA.MODE=0x2), the SPI interface will remain inactive with the MISO line tri-stated as long as the  $\overline{SS}$  pin is pulled high. Software may update the contents of DATA at any time as long as the Data Register Empty flag in the Interrupt Status and Clear register (INTFLAG.DRE) is set.

When  $\overline{SS}$  is pulled low and SCK is running, the slave will sample and shift out data according to the transaction mode set. When the content of TxDATA has been loaded into the shift register, INTFLAG.DRE will be set, and new data can be written to DATA.

Similar to the master, the slave will receive one character for each character transmitted. A character will be transferred into the two-level receive buffer within the same clock cycle its last data bit is received. The received character can be retrieved from DATA when the Receive Complete interrupt flag (INTFLAG.RXC) is set.

When the master pulls the  $\overline{SS}$  line high, the transaction is done and the Transmit Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.TXC) will be set.

After DATA is written it takes up to three SCK clock cycles until the content of DATA is ready to be loaded into the shift register on the next character boundary. As a consequence, the first character transferred in a SPI transaction will not be the content of DATA. This can be avoided by using the preloading feature. Refer to Preloading of the Slave Shift Register.

When transmitting several characters in one SPI transaction, the data has to be written into DATA register with at least three SCK clock cycles left in the current character transmission. If this criteria is not met, the previously received character will be transmitted.

Once the DATA register is empty, it takes three CLK\_SERCOM\_APB cycles for INTFLAG.DRE to be set.

### 29.6.2.7 Receiver Error Bit

The SPI receiver has one error bit: the Buffer Overflow bit (BUFOVF), which can be read from the Status register (STATUS). Once an error happens, the bit will stay set until it is cleared by writing '1' to it. The bit is also automatically cleared when the receiver is disabled.

There are two methods for buffer overflow notification, selected by the immediate buffer overflow notification bit in the Control A register (CTRLA.IBON):

If CTRLA.IBON=1, STATUS.BUFOVF is raised immediately upon buffer overflow. Software can then empty the receive FIFO by reading RxDATA until the receiver complete interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) goes low.

If CTRLA.IBON=0, the buffer overflow condition travels with data through the receive FIFO. After the received data is read, STATUS.BUFOVF and INTFLAG.ERROR will be set along with INTFLAG.RXC, and RxDATA will be zero.

# SERCOM SPI – SERCOM Serial Peripheral Interface

| AMODE[1:0] | Name    | Description                                                                                                   |

|------------|---------|---------------------------------------------------------------------------------------------------------------|

| 0x0        | MASK    | ADDRMASK is used as a mask to the ADDR register                                                               |

| 0x1        | 2_ADDRS | The slave responds to the two unique addresses in ADDR and ADDRMASK                                           |

| 0x2        | RANGE   | The slave responds to the range of addresses between and including ADDR and ADDRMASK. ADDR is the upper limit |

| 0x3        | -       | Reserved                                                                                                      |

## Bit 13 – MSSEN Master Slave Select Enable

This bit enables hardware slave select  $(\overline{SS})$  control.

| Value | Description                      |

|-------|----------------------------------|

| 0     | Hardware SS control is disabled. |

| 1     | Hardware SS control is enabled.  |

## Bit 9 – SSDE Slave Select Low Detect Enable

This bit enables wake up when the slave select  $(\overline{SS})$  pin transitions from high to low.

| Value | Description                  |

|-------|------------------------------|

| 0     | SS low detector is disabled. |

| 1     | SS low detector is enabled.  |

### Bit 6 – PLOADEN Slave Data Preload Enable

Setting this bit will enable preloading of the slave shift register when there is no transfer in progress. If the SS line is high when DATA is written, it will be transferred immediately to the shift register.

### Bits 2:0 – CHSIZE[2:0] Character Size

| CHSIZE[2:0] | Name | Description |

|-------------|------|-------------|

| 0x0         | 8BIT | 8 bits      |

| 0x1         | 9BIT | 9 bits      |

| 0x2-0x7     | -    | Reserved    |

### 30.10.10 Data

|        | Name:<br>Offset:<br>Reset:<br>Property: | DATA<br>0x18<br>0x0000<br>Write-Synchro | onized, Read- | Synchronized | 1              |     |     |     |

|--------|-----------------------------------------|-----------------------------------------|---------------|--------------|----------------|-----|-----|-----|

| Bit    | 15                                      | 14                                      | 13            | 12           | 11             | 10  | 9   | 8   |

|        |                                         |                                         |               |              |                |     |     |     |

| Access |                                         |                                         |               |              |                |     |     |     |

| Reset  |                                         |                                         |               |              |                |     |     |     |

| Bit    | 7                                       | 6                                       | 5             | 4            | 3              | 2   | 1   | 0   |

|        |                                         |                                         |               | DATA         | <b>\</b> [7:0] |     |     |     |

| Access | R/W                                     | R/W                                     | R/W           | R/W          | R/W            | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                       | 0             | 0            | 0              | 0   | 0   | 0   |

### Bits 7:0 - DATA[7:0] Data

The master data register I/O location (DATA) provides access to the master transmit and receive data buffers. Reading valid data or writing data to be transmitted can be successfully done only when SCL is held low by the master (STATUS.CLKHOLD is set). An exception is reading the last data byte after the stop condition has been sent.

Accessing DATA.DATA auto-triggers I<sup>2</sup>C bus operations. The operation performed depends on the state of CTRLB.ACKACT, CTRLB.SMEN and the type of access (read/write).

Writing or reading DATA.DATA when not in smart mode does not require synchronization.

### 31.8.4 Control B Set

Name:CTRLBSETOffset:0x05Reset:0x00Property:PAC Write-Protection, Read-synchronized, Write-Synchronized

This register allows the user to set bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Clear register (CTRLBCLR).

| Bit    | 7   | 6      | 5 | 4 | 3 | 2       | 1 | 0   |

|--------|-----|--------|---|---|---|---------|---|-----|

|        | CM  | D[1:0] |   |   |   | ONESHOT |   | DIR |

| Access | R/W | R/W    |   |   |   | R/W     |   | R/W |

| Reset  | 0   | 0      |   |   |   | 0       |   | 0   |

### Bits 7:6 – CMD[1:0] Command

These bits are used for software control of the TC. The commands are executed on the next prescaled GCLK\_TC clock cycle. When a command has been executed, the CMD bit group will be read back as zero.

Writing 0x0 to these bits has no effect.

Writing a '1' to any of these bits will clear the pending command.

| Value | Name      | Description                         |

|-------|-----------|-------------------------------------|

| 0x0   | NONE      | No action                           |

| 0x1   | RETRIGGER | Force a start, restart or retrigger |

| 0x2   | STOP      | Force a stop                        |

| 0x3   | -         | Reserved                            |

### Table 31-9. Command

### Bit 2 - ONESHOT One-Shot on Counter

This bit controls one-shot operation of the TC.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will disable one-shot operation.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | The TC will wrap around and continue counting on an overflow/underflow condition. |

| 1     | The TC will wrap around and stop on the next underflow/overflow condition.        |

### Bit 0 – DIR Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the bit and make the counter count up.

TCC – Timer/Counter for Control Applications

| CTRLA.RESOLUTION | Bits [n:0]     |

|------------------|----------------|

| 0x0 - NONE       | -              |

| 0x1 - DITH4      | 3:0            |

| 0x2 - DITH5      | 4:0            |

| 0x3 - DITH6      | 5:0 (depicted) |

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

| 34.8.2 | Control B                               |                            |   |   |   |   |        |        |

|--------|-----------------------------------------|----------------------------|---|---|---|---|--------|--------|

|        | Name:<br>Offset:<br>Reset:<br>Property: | CTRLB<br>0x01<br>0x00<br>- |   |   |   |   |        |        |

| Bi     | t 7                                     | 6                          | 5 | 4 | 3 | 2 | 1      | 0      |

|        |                                         |                            |   |   |   |   | STARTx | STARTx |

| Access | S                                       |                            |   |   |   |   | R/W    | R/W    |

| Rese   | t                                       |                            |   |   |   |   | 0      | 0      |

|        |                                         |                            |   |   |   |   |        |        |

**Bits 1,0 – STARTx** Comparator x Start Comparison Writing a '0' to this field has no effect.

Writing a '1' to STARTx starts a single-shot comparison on COMPx if both the Single-Shot and Enable bits in the Comparator x Control Register are '1' (COMPCTRLx.SINGLE and COMPCTRLx.ENABLE). If comparator x is not implemented, or if it is not enabled in single-shot mode, Writing a '1' has no effect.

This bit always reads as zero.

## **Electrical Characteristics**

| Parameter                                             | Conditions                     | Symbol                                                | Min.                        | Тур.                  | Max.                    | Unit |

|-------------------------------------------------------|--------------------------------|-------------------------------------------------------|-----------------------------|-----------------------|-------------------------|------|

| Internal ratiometric reference 1 <sup>(2)</sup>       | VDDANA > 2.0V                  | $V_{\text{REFINT}} V_{\text{CC1}}$                    | -                           | V <sub>DDANA</sub> /2 | -                       | V    |

| Internal ratiometric reference 1 <sup>(2)</sup> error | 2.0V < VDDANA <<br>3.63V       | V <sub>REFINT</sub> V <sub>CC1</sub><br>Voltage Error | -1                          | -                     | 1                       | %    |

| Conversion range <sup>(1)</sup>                       | Differential mode              |                                                       | -V <sub>ref</sub> /<br>Gain | -                     | +V <sub>REF</sub> /GAIN | V    |

|                                                       | Single-ended mode              |                                                       | 0                           | -                     | +V <sub>REF</sub> /GAIN | V    |

| Sampling capacitance <sup>(2)</sup>                   |                                | C <sub>SAMPLE</sub>                                   | -                           | 3.5                   | -                       | pF   |

| Input channel source resistance <sup>(2)</sup>        |                                | R <sub>SAMPLE</sub>                                   | -                           | -                     | 3.5                     | kΩ   |

| DC supply current <sup>(1)</sup>                      | $f_{CLK\_ADC} = 2.1 MHz^{(3)}$ | I <sub>DD</sub>                                       | -                           | 2.9                   | 4.1                     | mA   |

- 1. These values are based on characterization. These values are not covered by test limits in production.

- 2. These values are based on simulation. These values are not covered by test limits in production or characterization.

- 3. In this condition and for a sample rate of 350ksps, 1 Conversion at gain 1x takes 6 clock cycles of the ADC clock.

| Parameter                      | Conditions                                 | Symbol | Min. | Тур. | Max.  | Unit |

|--------------------------------|--------------------------------------------|--------|------|------|-------|------|

| Effective Number Of Bits       | With gain compensation                     | ENOB   | -    | 10.4 | 10.8  | bits |

| Total Unadjusted Error         | 1x Gain                                    | TUE    | 1.2  | 7.0  | 38.0  | LSB  |

| Integral Nonlinearity          | 1x Gain                                    | INL    | 0.7  | 1.30 | 5.6   | LSB  |

| Differential Nonlinearity      | 1x Gain                                    | DNL    | -    | ±0.7 | ±0.95 | LSB  |

|                                | Ext. Ref 1x                                |        | -    | ±3   | ±13   | mV   |

| Gain Error                     | $V_{REF} = V_{DDANA}/1.48$                 |        | -    | ±11  | ±55   | mV   |

|                                | Bandgap                                    |        | -    | ±2   | ±35   | mV   |

| Gain Accuracy <sup>(5)</sup>   | Ext. Ref. 0.5x                             |        | -    | ±0.1 | ±0.8  | %    |

|                                | Ext. Ref. 2x to 16x                        |        | -    | ±0.6 | ±0.9  | %    |

|                                | Ext. Ref. 1x                               |        | -    | ±2   | ±35   | mV   |

| Offset Error                   | V <sub>REF</sub> =V <sub>DDANA</sub> /1.48 |        | -    | ±3   | ±40   | mV   |

|                                | Bandgap                                    |        | -    | ±3   | ±50   | mV   |

| Spurious Free Dynamic Range    | 1x Gain                                    | SFDR   | 65   | 71.5 | 76    | dB   |

| Signal-to-Noise and Distortion | F <sub>CLK_ADC</sub> = 2.1MHz              | SINAD  | 58   | 65   | 67    | dB   |

| Signal-to-Noise Ratio          | F <sub>IN</sub> = 40kHz                    | SNR    | 60   | 66   | 68.6  | dB   |

### Table 37-27. Differential Mode

## **Electrical Characteristics**

| Parameter | Conditions             | Symbol | Min. | Тур. | Max. | Unit |

|-----------|------------------------|--------|------|------|------|------|

|           | AGC off                |        |      |      |      |      |

|           | f = 32MHz,             |        |      |      |      |      |

|           | C <sub>L</sub> = 18pF, |        |      | EEE  | 776  |      |

|           | XOSC.GAIN = 4,         |        | -    | 555  | 776  |      |

|           | AGC on                 |        |      |      |      |      |

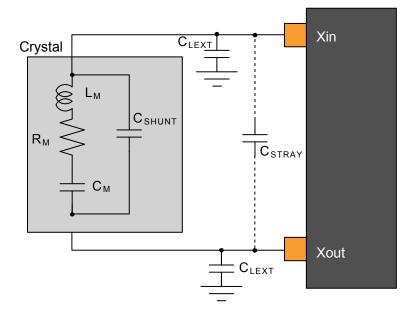

### Figure 37-6. Oscillator Connection

### 37.13.2 External 32 kHz Crystal Oscillator (XOSC32K) Characteristics

### 37.13.2.1 Digital Clock Characteristics

The following table describes the characteristics for the oscillator when a digital clock is applied on XIN32 pin.

### Table 37-42. Digital Clock Characteristics

| Parameter              | Conditions | Symbol               | Min. | Тур.   | Max. | Unit |

|------------------------|------------|----------------------|------|--------|------|------|

| XIN32 clock frequency  |            | f <sub>CPXIN32</sub> | -    | 32.768 | -    | kHz  |

| XIN32 clock duty cycle |            | DCxin                | -    | 50     | -    | %    |

### 37.13.2.2 XOSC32K Characteristics

Figure 37-6 and the equation in XOSC Characteristics also apply to the 32 kHz oscillator connection. The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the table. The exact value of  $C_L$  can be found in the crystal datasheet.

# Conventions

| Symbol | Description                                   |

|--------|-----------------------------------------------|

| MHz    | 1 MHz = 10 <sup>6</sup> Hz = 1,000,000 Hz     |

| GHz    | 1 GHz = 10 <sup>9</sup> Hz = 1,000,000,000 Hz |

| s      | second                                        |

| ms     | millisecond                                   |

| μs     | microsecond                                   |

| ns     | nanosecond                                    |

# 41.4 Registers and Bits

# Table 41-4. Register and Bit Mnemonics

| Symbol      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W         | Read/Write accessible register bit. The user can read from and write to this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R           | Read-only accessible register bit. The user can only read this bit. Writes will be ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| W           | Write-only accessible register bit. The user can only write this bit. Reading this bit will return an undefined value.                                                                                                                                                                                                                                                                                                                                                                                                        |

| BIT         | Bit names are shown in uppercase. (Example ENABLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FIELD[n:m]  | A set of bits from bit n down to m. (Example: PINA[3:0] = {PINA3, PINA2, PINA1, PINA0}                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Reserved    | Reserved bits are unused and reserved for future use. For compatibility with future devices, always write reserved bits to zero when the register is written. Reserved bits will always return zero when read.                                                                                                                                                                                                                                                                                                                |

|             | Reserved bit field values must not be written to a bit field. A reserved value won't be read from a read-only bit field.                                                                                                                                                                                                                                                                                                                                                                                                      |

| PERIPHERALi | If several instances of a peripheral exist, the peripheral name is followed by a number to indicate the number of the instance in the range 0-n. PERIPHERAL0 denotes one specific instance.                                                                                                                                                                                                                                                                                                                                   |

| Reset       | Value of a register after a power Reset. This is also the value of registers in a peripheral after performing a software Reset of the peripheral, except for the Debug Control registers.                                                                                                                                                                                                                                                                                                                                     |

| SET/CLR     | Registers with SET/CLR suffix allows the user to clear and set bits in a register without doing a read-modify-write operation. These registers always come in pairs. Writing a '1' to a bit in the CLR register will clear the corresponding bit in both registers, while writing a '1' to a bit in the SET register will set the corresponding bit in both registers. Both registers will return the same value when read. If both registers are written simultaneously, the write to the CLR register will take precedence. |