Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | A/D 13x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f042c6u7  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| USART modes/features <sup>(1)</sup> | USART1 | USART2 |

|-------------------------------------|--------|--------|

| Modbus communication                | Х      | -      |

| Auto baud rate detection            | Х      | -      |

| Driver Enable                       | Х      | Х      |

Table 10. STM32F042x4/x6 USART implementation (continued)

1. X = supported.

# 3.16 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

Up to two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in fullduplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

One standard I<sup>2</sup>S interface (multiplexed with SPI1) supporting four different audio standards can operate as master or slave at half-duplex communication mode. It can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, it can output a clock for an external audio component at 256 times the sampling frequency.

| SPI features <sup>(1)</sup> | SPI features <sup>(1)</sup> SPI1 SI |      |  |  |  |  |  |  |

|-----------------------------|-------------------------------------|------|--|--|--|--|--|--|

| SFIleatures                 | 3511                                | SPI2 |  |  |  |  |  |  |

| Hardware CRC calculation    | Х                                   | Х    |  |  |  |  |  |  |

| Rx/Tx FIFO                  | Х                                   | Х    |  |  |  |  |  |  |

| NSS pulse mode              | Х                                   | Х    |  |  |  |  |  |  |

| I <sup>2</sup> S mode       | Х                                   | -    |  |  |  |  |  |  |

| TI mode                     | Х                                   | Х    |  |  |  |  |  |  |

Table 11. STM32F042x4/x6 SPI/I<sup>2</sup>S implementation

1. X = supported.

# 3.17 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

# 3.18 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames

DocID025832 Rev 5

with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

# 3.19 Universal serial bus (USB)

The STM32F042x4/x6 embeds a full-speed USB device peripheral compliant with the USB specification version 2.0. The internal USB PHY supports USB FS signaling, embedded DP pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up-to 1 KB (the last 256 byte are used for CAN peripheral if enabled) and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use an HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal-less operation.

## 3.20 Clock recovery system (CRS)

The STM32F042x4/x6 embeds a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.21 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

|                 |         | Pin nı | umbe     | rs       |          |                                      |             |               |            | Pin function                                        | าร                                         |

|-----------------|---------|--------|----------|----------|----------|--------------------------------------|-------------|---------------|------------|-----------------------------------------------------|--------------------------------------------|

| LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | UFQFPN28 | TSSPOP20 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate function                                  | Additional<br>functions                    |

| 1               | -       | -      | -        | -        | -        | VBAT                                 | S           | -             | -          | Backup power s                                      | upply                                      |

| 2               | A6      | -      | -        | -        | -        | PC13                                 | I/O         | тс            | (1)<br>(2) | -                                                   | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT |

| 3               | B6      | -      | -        | -        | -        | PC14-<br>OSC32_IN<br>(PC14)          | I/O         | тс            | (1)<br>(2) | -                                                   | OSC32_IN                                   |

| 4               | C6      | -      | -        | -        | -        | PC15-<br>OSC32_OUT<br>(PC15)         | I/O         | тс            | (1)<br>(2) | -                                                   | OSC32_OUT                                  |

| 5               | B5      | 2      | 2        | 2        | 2        | PF0-OSC_IN<br>(PF0)                  | I/O         | FTf           | -          | CRS_SYNC<br>I2C1_SDA                                | OSC_IN                                     |

| 6               | C5      | 3      | 3        | 3        | 3        | PF1-OSC_OUT<br>(PF1)                 | I/O         | FTf           | -          | I2C1_SCL                                            | OSC_OUT                                    |

| 7               | D5      | 4      | 4        | 4        | 4        | NRST                                 | I/O         | RST           | -          | Device reset input / interr<br>(active low          |                                            |

| 8               | D6      | 32     | 0        | 16       | 15       | VSSA                                 | S           |               | (3)        | Analog grou                                         | nd                                         |

| 9               | E5      | 5      | 5        | 5        | 5        | VDDA                                 | S           |               | -          | Analog power s                                      | upply                                      |

| 10              | F6      | 6      | 6        | 6        | 6        | PA0                                  | I/O         | ТТа           | -          | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1          | RTC_<br>TAMP2,<br>WKUP1,<br>ADC_IN0,       |

| 11              | D4      | 7      | 7        | 7        | 7        | PA1                                  | I/O         | ТТа           | -          | USART2_RTS,<br>TIM2_CH2,<br>TSC_G1_IO2,<br>EVENTOUT | ADC_IN1                                    |

| 12              | E4      | 8      | 8        | 8        | 8        | PA2                                  | I/O         | ТТа           | -          | USART2_TX,<br>TIM2_CH3,<br>TSC_G1_IO3               | ADC_IN2,<br>WKUP4                          |

| 13              | F5      | 9      | 9        | 9        | 9        | PA3                                  | I/O         | ТТа           | -          | USART2_RX,<br>TIM2_CH4,<br>TSC_G1_IO4               | ADC_IN3                                    |

Table 13. STM32F042x pin definitions

|                 |         | Pin ni | umbe     | rs       |          |                                      |             |               |       | Pin functions                                                               |                         |  |

|-----------------|---------|--------|----------|----------|----------|--------------------------------------|-------------|---------------|-------|-----------------------------------------------------------------------------|-------------------------|--|

| LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | UFQFPN28 | TSSPOP20 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate function                                                          | Additional<br>functions |  |

| 38              | A2      | 25     | 25       | 23       | -        | PA15                                 | I/O         | FT            | (4)   | SPI1_NSS, I2S1_WS,<br>USART2_RX,<br>TIM2_CH1_ETR,<br>EVENTOUT,<br>USB_NOE   | -                       |  |

| 39              | В3      | 26     | 26       | 24       | -        | PB3                                  | I/O         | FT            | -     | SPI1_SCK, I2S1_CK,<br>TIM2_CH2,<br>TSC_G5_IO1,<br>EVENTOUT                  | -                       |  |

| 40              | A3      | 27     | 27       | 25       | -        | PB4                                  | I/O         | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM17_BKIN,<br>TIM3_CH1,<br>TSC_G5_IO2,<br>EVENTOUT | -                       |  |

| 41              | E6      | 28     | 28       | 26       | -        | PB5                                  | I/O         | FT            | -     | SPI1_MOSI, I2S1_SD,<br>I2C1_SMBA,<br>TIM16_BKIN,<br>TIM3_CH2                | WKUP6                   |  |

| 42              | C4      | 29     | 29       | 27       | -        | PB6                                  | I/O         | FTf           | -     | I2C1_SCL,<br>USART1_TX,<br>TIM16_CH1N,<br>TSC_G5_I03                        | -                       |  |

| 43              | A4      | 30     | 30       | 28       | -        | PB7                                  | I/O         | FTf           | -     | I2C1_SDA,<br>USART1_RX,<br>TIM17_CH1N,<br>TSC_G5_IO4                        | -                       |  |

| 44              | -       | -      | 31       | -        | -        | PF11-BOOT0                           | I/O         | FT            | -     | -                                                                           | Boot memory selection   |  |

| -               | B4      | 31     | -        | 1        | 1        | PB8-BOOT0                            | I/O         | FTf           | -     | I2C1_SCL, CEC,<br>TIM16_CH1,<br>TSC_SYNC,<br>CAN_RX                         | Boot memory selection   |  |

| 45              | -       | -      | 32       | -        | -        | PB8                                  | I/O         | FTf           | -     | I2C1_SCL, CEC,<br>TIM16_CH1,<br>TSC_SYNC,<br>CAN_RX                         | -                       |  |

Table 13. STM32F042x pin definitions (continued)

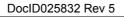

# 6.1.7 Current consumption measurement

#### Figure 14. Current consumption measurement scheme

| Symbol                               | Ratings                                                                         | Max.                 | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|----------------------|------|

| ΣI <sub>VDD</sub>                    | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| $\Sigma I_{VSS}$                     | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

|                                      | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                                | -25                  |      |

|                                      | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                                      | Total output current sourced by sum of all I/Os supplied by VDDIO2              | -40                  |      |

|                                      | Injected current on FT and FTf pins                                             | -5/+0 <sup>(4)</sup> |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                              | ± 5                  |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  | 1    |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 | 1    |

#### Table 19. Current characteristics

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

3. A positive injection is induced by  $V_{IN} > V_{DDIOx}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 18: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. On these I/Os, a positive injection is induced by  $V_{IN} > V_{DDA}$ . Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 56: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 20. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

| . <u> </u>        | Table 22. Operating conditions at power-up / power-uowin |            |     |     |      |  |  |  |  |

|-------------------|----------------------------------------------------------|------------|-----|-----|------|--|--|--|--|

| Symbol            | Parameter                                                | Conditions | Min | Мах | Unit |  |  |  |  |

| +                 | V <sub>DD</sub> rise time rate                           |            | 0   | 8   |      |  |  |  |  |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate                           | -          | 20  | 8   | μs/V |  |  |  |  |

| +                 | V <sub>DDA</sub> rise time rate                          |            | 0   | 8   | μ5/ν |  |  |  |  |

| t <sub>VDDA</sub> | V <sub>DDA</sub> fall time rate                          | -          | 20  | 8   |      |  |  |  |  |

Table 22. Operating conditions at power-up / power-down

## 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 23* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

Table 23. Embedded reset and power control block characteristics

| Symbol                               | Parameter           | Conditions                  | Min                 | Тур  | Мах                 | Unit |

|--------------------------------------|---------------------|-----------------------------|---------------------|------|---------------------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup>  |                     | Falling edge <sup>(2)</sup> | 1.80                | 1.88 | 1.96 <sup>(3)</sup> | V    |

| * POR/PDR                            | reset threshold     | Rising edge                 | 1.84 <sup>(3)</sup> | 1.92 | 2.00                | V    |

| V <sub>PDRhyst</sub>                 | PDR hysteresis      | -                           | -                   | 40   | -                   | mV   |

| t <sub>RSTTEMPO</sub> <sup>(4)</sup> | Reset temporization | -                           | 1.50                | 2.50 | 4.50                | ms   |

1. The PDR detector monitors  $V_{DD}$  and also  $V_{DDA}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{DD}.$

2. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

3. Data based on characterization results, not tested in production.

4. Guaranteed by design, not tested in production.

| Symbol            | Parameter       | Conditions   | Min  | Тур  | Max  | Unit |

|-------------------|-----------------|--------------|------|------|------|------|

| V                 | DVD throshold 0 | Rising edge  | 2.1  | 2.18 | 2.26 | V    |

| V <sub>PVD0</sub> | PVD threshold 0 | Falling edge | 2    | 2.08 | 2.16 | V    |

| M                 | DVD throshold 1 | Rising edge  | 2.19 | 2.28 | 2.37 | V    |

| V <sub>PVD1</sub> | PVD threshold 1 | Falling edge | 2.09 | 2.18 | 2.27 | V    |

| M                 | PVD threshold 2 | Rising edge  | 2.28 | 2.38 | 2.48 | V    |

| V <sub>PVD2</sub> |                 | Falling edge | 2.18 | 2.28 | 2.38 | V    |

| M                 | PVD threshold 3 | Rising edge  | 2.38 | 2.48 | 2.58 | V    |

| V <sub>PVD3</sub> |                 | Falling edge | 2.28 | 2.38 | 2.48 | V    |

| M                 | DVD throshold 4 | Rising edge  | 2.47 | 2.58 | 2.69 | V    |

| V <sub>PVD4</sub> | PVD threshold 4 | Falling edge | 2.37 | 2.48 | 2.59 | V    |

| M                 | PVD threshold 5 | Rising edge  | 2.57 | 2.68 | 2.79 | V    |

| V <sub>PVD5</sub> |                 | Falling edge | 2.47 | 2.58 | 2.69 | V    |

#### Table 24. Programmable voltage detector characteristics

| Tabl                                | Table 24. Programmable voltage delector characteristics (continued) |              |      |      |                     |      |  |

|-------------------------------------|---------------------------------------------------------------------|--------------|------|------|---------------------|------|--|

| Symbol                              | Parameter                                                           | Conditions   | Min  | Тур  | Max                 | Unit |  |

| V                                   | PVD threshold 6                                                     | Rising edge  | 2.66 | 2.78 | 2.9                 | V    |  |

| V <sub>PVD6</sub>                   |                                                                     | Falling edge | 2.56 | 2.68 | 2.8                 | V    |  |

| M                                   | PVD threshold 7                                                     | Rising edge  | 2.76 | 2.88 | 3                   | V    |  |

| V <sub>PVD7</sub>                   |                                                                     | Falling edge | 2.66 | 2.78 | 2.9                 | V    |  |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis                                                      | -            | -    | 100  | -                   | mV   |  |

| I <sub>DD(PVD)</sub>                | PVD current consumption                                             | -            | -    | 0.15 | 0.26 <sup>(1)</sup> | μA   |  |

Table 24. Programmable voltage detector characteristics (continued)

1. Guaranteed by design, not tested in production.

## 6.3.4 Embedded reference voltage

The parameters given in *Table 25* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

|                        |                                                                     |                                   |                      | -    |                    |        |

|------------------------|---------------------------------------------------------------------|-----------------------------------|----------------------|------|--------------------|--------|

| Symbol                 | Parameter                                                           | Conditions                        | Min                  | Тур  | Max                | Unit   |

| V <sub>REFINT</sub>    | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.2                  | 1.23 | 1.25               | V      |

| t <sub>start</sub>     | ADC_IN17 buffer startup time                                        | -                                 | -                    | -    | 10 <sup>(1)</sup>  | μs     |

| t <sub>S_vrefint</sub> | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | 4 <sup>(1)</sup>     | -    | -                  | μs     |

| ΔV <sub>REFINT</sub>   | Internal reference voltage<br>spread over the<br>temperature range  | V <sub>DDA</sub> = 3 V            | -                    | -    | 10 <sup>(1)</sup>  | mV     |

| T <sub>Coeff</sub>     | Temperature coefficient                                             | -                                 | - 100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |

Table 25. Embedded internal reference voltage

1. Guaranteed by design, not tested in production.

## 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

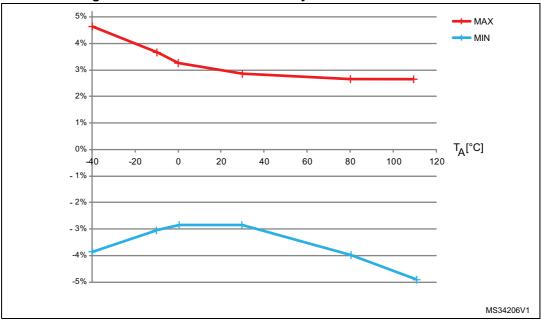

## High-speed internal 48 MHz (HSI48) RC oscillator

| Symbol                  | Parameter                                                | Conditions                     | Min                 | Тур  | Мах                | Unit |  |

|-------------------------|----------------------------------------------------------|--------------------------------|---------------------|------|--------------------|------|--|

| f <sub>HSI48</sub>      | Frequency                                                | -                              | -                   | 48   | -                  | MHz  |  |

| TRIM                    | HSI48 user-trimming step                                 | -                              | 0.09 <sup>(2)</sup> | 0.14 | 0.2 <sup>(2)</sup> | %    |  |

| DuCy <sub>(HSI48)</sub> | Duty cycle                                               | -                              | 45 <sup>(2)</sup>   | -    | 55 <sup>(2)</sup>  | %    |  |

|                         | Accuracy of the HSI48<br>oscillator (factory calibrated) | T <sub>A</sub> = -40 to 105 °C | -4.9 <sup>(3)</sup> | -    | 4.7 <sup>(3)</sup> | %    |  |

| ACC                     |                                                          | T <sub>A</sub> = −10 to 85 °C  | -4.1 <sup>(3)</sup> | -    | 3.7 <sup>(3)</sup> | %    |  |

| ACC <sub>HSI48</sub>    |                                                          | T <sub>A</sub> = 0 to 70 °C    | -3.8 <sup>(3)</sup> | -    | 3.4 <sup>(3)</sup> | %    |  |

|                         |                                                          | T <sub>A</sub> = 25 °C         | -2.8                | -    | 2.9                | %    |  |

| t <sub>su(HSI48)</sub>  | HSI48 oscillator startup time                            | -                              | -                   | -    | 6 <sup>(2)</sup>   | μs   |  |

| I <sub>DDA(HSI48)</sub> | HSI48 oscillator power consumption                       | -                              | -                   | 312  | 350 <sup>(2)</sup> | μA   |  |

## Table 40. HSI48 oscillator characteristics<sup>(1)</sup>

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

#### Figure 21. HSI48 oscillator accuracy characterization results

## Low-speed internal (LSI) RC oscillator

| Table 41. LSI oscillator | characteristics <sup>(1)</sup> |

|--------------------------|--------------------------------|

|--------------------------|--------------------------------|

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

## 6.3.9 PLL characteristics

The parameters given in *Table 42* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Symbol                | Parameter                      |                   | Unit |                    |      |

|-----------------------|--------------------------------|-------------------|------|--------------------|------|

|                       | Faranieler                     | Min               | Тур  | Max                | Onic |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0  | 24 <sup>(2)</sup>  | MHz  |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %    |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 48                 | MHz  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs   |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps   |

Table 42. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

## 6.3.10 Memory characteristics

## **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

Table 43. Flash memory characteristics

| Symbol                         | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>              | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub>             | Page (1 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>                | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

|                                | Supply current          | Write mode                       | -   | -    | 10                 | mA   |

| I <sub>DD</sub> Supply current | Erase mode              | -                                | -   | 12   | mA                 |      |

1. Guaranteed by design, not tested in production.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 18: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 18: Voltage characteristics*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                              | Min                     | Max | Unit |  |

|-----------------------------------|------------------------------------------------------------|---------------------------------------------------------|-------------------------|-----|------|--|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | CMOS port <sup>(2)</sup>                                | -                       | 0.4 |      |  |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | V <sub>DDIOx</sub> -0.4 | -   | V    |  |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | TTL port <sup>(2)</sup>                                 | -                       | 0.4 |      |  |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | 2.4                     | -   | V    |  |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 20 mA                               | -                       | 1.3 | V    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2.7 V                              | V <sub>DDIOx</sub> -1.3 | -   | V    |  |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 6 mA                                | -                       | 0.4 | v    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2 V                                | V <sub>DDIOx</sub> -0.4 | -   | v    |  |

| V <sub>OL</sub> <sup>(4)</sup>    | Output low level voltage for an I/O pin                    | 11 J = 4 m 4                                            | -                       | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 4 mA                                | V <sub>DDIOx</sub> -0.4 | -   | V    |  |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | I <sub>IO</sub>   = 20 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V | -                       | 0.4 | V    |  |

| OLI III.                          |                                                            | I <sub>IO</sub>   = 10 mA                               | -                       | 0.4 | V    |  |

### Table 51. Output voltage characteristics<sup>(1)</sup>

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 18: Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. Data based on characterization results. Not tested in production.

4. Data based on characterization results. Not tested in production.

| Symbol                                 | Parameter                          | Conditions                                            | Min                                                                        | Тур  | Max                                               | Unit                       |

|----------------------------------------|------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|------|---------------------------------------------------|----------------------------|

| f <sub>TRIG</sub> <sup>(2)</sup>       | External trigger frequency         | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | -                                                                          | -    | 823                                               | kHz                        |

|                                        |                                    | 12-bit resolution                                     | -                                                                          | -    | 17                                                | 1/f <sub>ADC</sub>         |

| V <sub>AIN</sub>                       | Conversion voltage range           | -                                                     | 0                                                                          | -    | V <sub>DDA</sub>                                  | V                          |

| R <sub>AIN</sub> <sup>(2)</sup>        | External input impedance           | See <i>Equation 1</i> and <i>Table 55</i> for details | -                                                                          | -    | 50                                                | kΩ                         |

| $R_{ADC}^{(2)}$                        | Sampling switch resistance         | -                                                     | -                                                                          | -    | 1                                                 | kΩ                         |

| C <sub>ADC</sub> <sup>(2)</sup>        | Internal sample and hold capacitor | -                                                     | -                                                                          | -    | 8                                                 | pF                         |

| t <sub>CAL</sub> <sup>(2)(3)</sup>     | Calibration time                   | f <sub>ADC</sub> = 14 MHz                             |                                                                            | 5.9  |                                                   | μs                         |

| 'CAL` /` /                             |                                    | -                                                     |                                                                            | 83   |                                                   | 1/f <sub>ADC</sub>         |

| W <sub>LATENCY</sub> <sup>(2)(4)</sup> | 4) ADC_DR register ready latency   | ADC clock = HSI14                                     | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -    | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

|                                        |                                    | ADC clock = PCLK/2                                    | -                                                                          | 4.5  | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                    | ADC clock = PCLK/4                                    | -                                                                          | 8.5  | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                    | $f_{ADC} = f_{PCLK}/2 = 14 \text{ MHz}$               | 0.196                                                                      |      | μs                                                |                            |

|                                        |                                    | f <sub>ADC</sub> = f <sub>PCLK</sub> /2               |                                                                            | 5.5  |                                                   | 1/f <sub>PCLK</sub>        |

| t <sub>latr</sub> (2)                  | Trigger conversion latency         | $f_{ADC} = f_{PCLK}/4 = 12 \text{ MHz}$               | 0.219                                                                      |      |                                                   | μs                         |

|                                        |                                    | $f_{ADC} = f_{PCLK}/4$                                |                                                                            | 10.5 |                                                   | 1/f <sub>PCLK</sub>        |

|                                        |                                    | f <sub>ADC</sub> = f <sub>HSI14</sub> = 14 MHz        | 0.179                                                                      | -    | 0.250                                             | μs                         |

| Jitter <sub>ADC</sub>                  | ADC jitter on trigger conversion   | f <sub>ADC</sub> = f <sub>HSI14</sub>                 | -                                                                          | 1    | -                                                 | 1/f <sub>HSI14</sub>       |

| ts <sup>(2)</sup>                      | Sampling time                      | f <sub>ADC</sub> = 14 MHz                             | 0.107                                                                      | -    | 17.1                                              | μs                         |

| 0                                      |                                    | -                                                     | 1.5                                                                        | -    | 239.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>STAB</sub> <sup>(2)</sup>       | Stabilization time                 | -                                                     | 14                                                                         |      | 1/f <sub>ADC</sub>                                |                            |

|                                        | Total conversion time              | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution       | 1                                                                          | -    | 18                                                | μs                         |

| t <sub>CONV</sub> <sup>(2)</sup>       | (including sampling time)          | 12-bit resolution                                     | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |      | 1/f <sub>ADC</sub>                                |                            |

Table 54. ADC characteristics (continued)

1. During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100  $\mu$ A on I<sub>DDA</sub> and 60  $\mu$ A on I<sub>DD</sub> should be taken into account.

2. Guaranteed by design, not tested in production.

3. Specified value includes only ADC timing. It does not include the latency of the register access.

4. This parameter specify latency for transfer of the conversion result to the ADC\_DR register. EOC flag is set at this time.

## Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| Та                      | Table 55. R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz |                                          |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------|------------------------------------------|--|--|--|--|--|

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs)                                          | R <sub>AIN</sub> max (kΩ) <sup>(1)</sup> |  |  |  |  |  |

| 1.5                     | 0.11                                                         | 0.4                                      |  |  |  |  |  |

| 7.5                     | 0.54                                                         | 5.9                                      |  |  |  |  |  |

| 13.5                    | 0.96                                                         | 11.4                                     |  |  |  |  |  |

| 28.5                    | 2.04                                                         | 25.2                                     |  |  |  |  |  |

| 41.5                    | 2.96                                                         | 37.2                                     |  |  |  |  |  |

| 55.5                    | 3.96                                                         | 50                                       |  |  |  |  |  |

| 71.5                    | 5.11                                                         | NA                                       |  |  |  |  |  |

| 239.5                   | 17.1                                                         | NA                                       |  |  |  |  |  |

1. Guaranteed by design, not tested in production.

## Table 56. ADC accuracy<sup>(1)(2)(3)</sup>

| Symbol | Parameter                    | Test conditions                                                                            | Тур  | Max <sup>(4)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                            | ±1.3 | ±2                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                                | ±1   | ±1.5               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 3 V to 3.6 V     | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | $T_A = 25 \text{ °C}$                                                                      | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     |                                                                                            | ±0.8 | ±1.5               |      |

| ET     | Total unadjusted error       |                                                                                            | ±3.3 | ±4                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                                | ±1.9 | ±2.8               |      |

| EG     | Gain error                   | — f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 2.7 V to 3.6 V | ±2.8 | ±3                 | LSB  |

| ED     | Differential linearity error | $T_A = -40$ to 105 °C                                                                      | ±0.7 | ±1.3               |      |

| EL     | Integral linearity error     |                                                                                            | ±1.2 | ±1.7               |      |

| ET     | Total unadjusted error       |                                                                                            | ±3.3 | ±4                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                                | ±1.9 | ±2.8               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 2.4 V to 3.6 V   | ±2.8 | ±3                 | LSB  |

| ED     | Differential linearity error | $T_A = 25 \text{°C}$                                                                       | ±0.7 | ±1.3               | 1    |

| EL     | Integral linearity error     |                                                                                            | ±1.2 | ±1.7               | ]    |

1. ADC DC accuracy values are measured after internal calibration.

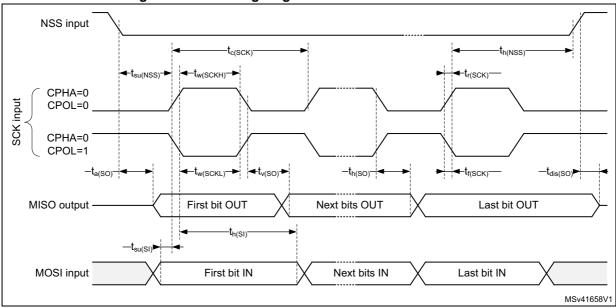

Figure 28. SPI timing diagram - slave mode and CPHA = 0

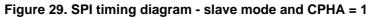

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

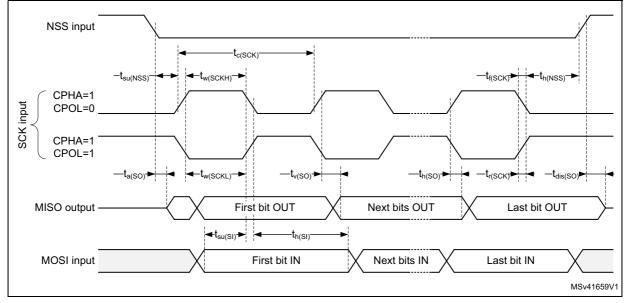

Figure 30. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

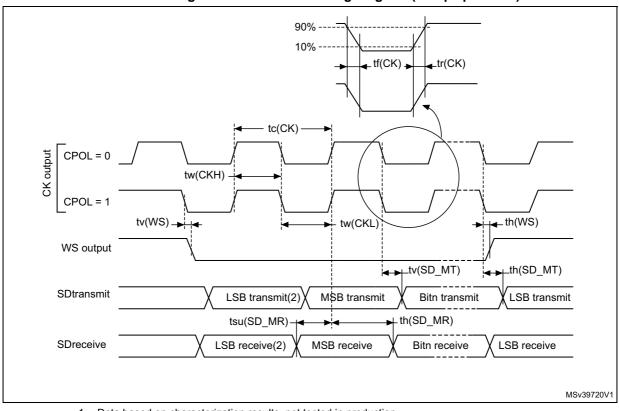

| Table 6 | 4. I <sup>2</sup> S | characteristics <sup>(1)</sup> |  |

|---------|---------------------|--------------------------------|--|

|---------|---------------------|--------------------------------|--|

| Symbol               | Parameter                                     | Conditions                                               | Min   | Мах   | Unit |

|----------------------|-----------------------------------------------|----------------------------------------------------------|-------|-------|------|

| f <sub>CK</sub>      | I <sup>2</sup> S clock frequency              | Master mode (data: 16 bits, Audio<br>frequency = 48 kHz) | 1.597 | 1.601 | MHz  |

| 1/t <sub>c(CK)</sub> |                                               | Slave mode                                               | 0     | 6.5   |      |

| t <sub>r(CK)</sub>   | I <sup>2</sup> S clock rise time              | Conscitive load C = 15 pE                                | -     | 10    |      |

| t <sub>f(CK)</sub>   | I <sup>2</sup> S clock fall time              | Capacitive load C <sub>L</sub> = 15 pF                   | -     | 12    |      |

| t <sub>w(CKH)</sub>  | I <sup>2</sup> S clock high time              | Master f <sub>PCLK</sub> = 16 MHz, audio                 | 306   | -     |      |

| t <sub>w(CKL)</sub>  | I <sup>2</sup> S clock low time               | frequency = 48 kHz                                       | 312   | -     | ns   |

| t <sub>v(WS)</sub>   | WS valid time                                 | Master mode                                              | 2     | -     | 115  |

| t <sub>h(WS)</sub>   | WS hold time                                  | Master mode                                              | 2     | -     |      |

| t <sub>su(WS)</sub>  | WS setup time                                 | Slave mode                                               | 7     | -     |      |

| t <sub>h(WS)</sub>   | WS hold time                                  | Slave mode                                               | 0     | -     |      |

| DuCy(SCK)            | I <sup>2</sup> S slave input clock duty cycle | Slave mode                                               | 25    | 75    | %    |

## Figure 32. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

### **USB** characteristics

The STM32F042x4/x6 USB interface is fully compliant with the USB specification version 2.0 and is USB-IF certified (for Full-speed device operation).

| Symbol                              | Parameter                                      | Conditions              | Min.               | Тур  | Max. | Unit |  |

|-------------------------------------|------------------------------------------------|-------------------------|--------------------|------|------|------|--|

| V <sub>DDIO2</sub>                  | USB transceiver operating voltage              | -                       | 3.0 <sup>(1)</sup> | -    | 3.6  | V    |  |

| t <sub>STARTUP</sub> <sup>(2)</sup> | USB transceiver startup time                   | -                       | -                  | -    | 1.0  | μs   |  |

| R <sub>PUI</sub>                    | Embedded USB_DP pull-up value during idle      | -                       | 1.1                | 1.26 | 1.5  | 24   |  |

| R <sub>PUR</sub>                    | Embedded USB_DP pull-up value during reception | -                       | 2.0                | 2.26 | 2.6  | kΩ   |  |

| Z <sub>DRV</sub> <sup>(2)</sup>     | Output driver impedance <sup>(3)</sup>         | Driving high<br>and low | 28                 | 40   | 44   | Ω    |  |

| Table 65. USB electrical characterist | ics |

|---------------------------------------|-----|

|---------------------------------------|-----|

1. The STM32F042x4/x6 USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V voltage range.

2. Guaranteed by design, not tested in production.

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-); the matching impedance is already included in the embedded driver.

## CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

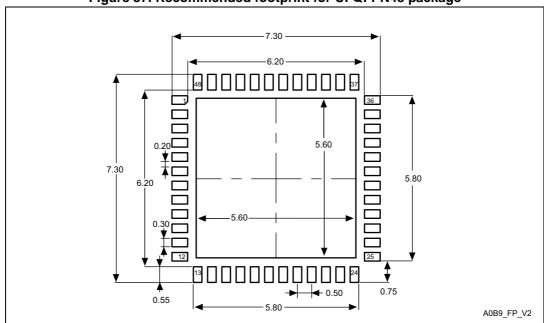

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |  |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |

| D      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |

| E      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |  |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

Table 67. UFQFPN48 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

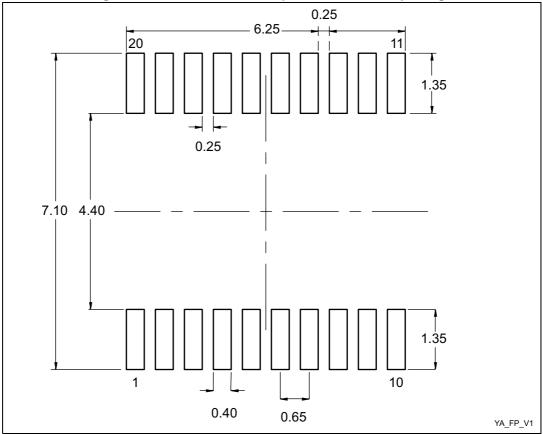

## Figure 37. Recommended footprint for UFQFPN48 package

1. Dimensions are expressed in millimeters.

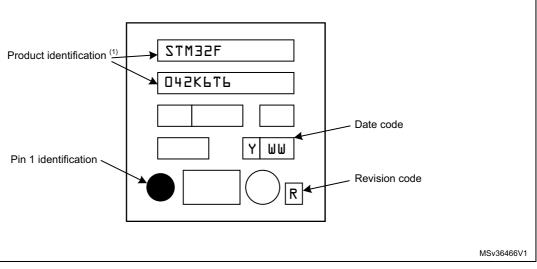

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 7.5 UFQFPN32 package information

UFQFPN32 is a 32-pin, 5x5 mm, 0.5 mm pitch ultra-thin fine-pitch quad flat package.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| k      | 0°          | -     | 8°    | 0°                    | -      | 8°     |  |

| aaa    | -           | -     | 0.100 | -                     | -      | 0.0039 |  |

Table 73. TSSOP20 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to four decimal digits.

2. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

3. Dimension "E1" does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side.

#### Figure 52. Recommended footprint for TSSOP20 package

1. Dimensions are expressed in millimeters.