Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | A/D 13x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-UFQFN                                                               |

| Supplier Device Package    | 28-UFQFPN (4x4)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f042g6u6  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F042x4/x6 microcontrollers.

This document should be read in conjunction with the STM32F0xxxx reference manual (RM0091). The reference manual is available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core, please refer to the Cortex<sup>®</sup>-M0 Technical Reference Manual, available from the www.arm.com website.

threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 3.5.3 Voltage regulator

The regulator has two operating modes and it is always enabled after reset.

- Main (MR) is used in normal operating mode (Run).

- Low power (LPR) can be used in Stop mode where the power demand is reduced.

In Standby mode, it is put in power down mode. In this mode, the regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost).

#### 3.5.4 Low-power modes

The STM32F042x4/x6 microcontrollers support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, the PVD output, RTC, I2C1 USART1, USB or the CEC.

The CEC, USART1 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data. If this is used when the voltage regulator is put in low power mode, the regulator is first switched to normal mode before the clock is provided to the given peripheral.

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the RTC domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pins, or an RTC event occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop and Standby mode capability

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- two anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

The RTC clock sources can be:

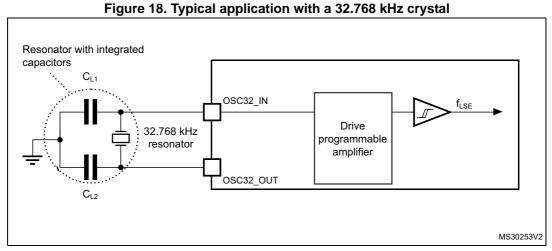

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.14 Inter-integrated circuit interface (I<sup>2</sup>C)

The I<sup>2</sup>C interface (I2C1) can operate in multimaster or slave modes. It can support Standard mode (up to 100 kbit/s), Fast mode (up to 400 kbit/s) and Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive.

It supports 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). It also includes programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |

| Table 8. Comparison of I <sup>2</sup> C analog and dig | igital filters |

|--------------------------------------------------------|----------------|

|--------------------------------------------------------|----------------|

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent

with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

# 3.19 Universal serial bus (USB)

The STM32F042x4/x6 embeds a full-speed USB device peripheral compliant with the USB specification version 2.0. The internal USB PHY supports USB FS signaling, embedded DP pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up-to 1 KB (the last 256 byte are used for CAN peripheral if enabled) and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use an HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal-less operation.

## 3.20 Clock recovery system (CRS)

The STM32F042x4/x6 embeds a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.21 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

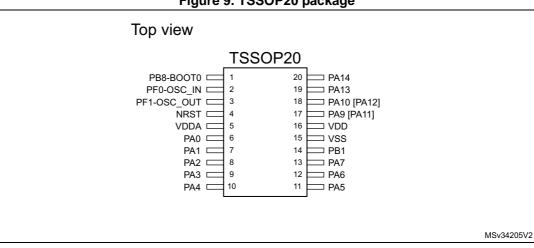

#### Figure 9. TSSOP20 package

1. Pin pair PA11/12 can be remapped in place of pin pair PA9/10 using the SYSCFG\_CFGR1 register.

#### Table 12. Legend/abbreviations used in the pinout table

| Na                                                                                                                                       | me                     | Abbreviation              | Definition                                                                |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------|---------------------------------------------------------------------------|--|--|--|--|--|

| Pin name Unless otherwise specified in brackets below the pin name, the pin function duri after reset is the same as the actual pin name |                        |                           |                                                                           |  |  |  |  |  |

|                                                                                                                                          |                        | S                         | Supply pin                                                                |  |  |  |  |  |

| Pin                                                                                                                                      | type                   | I/O                       | Input / output pin                                                        |  |  |  |  |  |

|                                                                                                                                          |                        | FT                        | 5 V-tolerant I/O                                                          |  |  |  |  |  |

|                                                                                                                                          |                        | FTf                       | 5 V-tolerant I/O, FM+ capable                                             |  |  |  |  |  |

|                                                                                                                                          |                        | ТТа                       | 3.3 V-tolerant I/O directly connected to ADC                              |  |  |  |  |  |

| I/O str                                                                                                                                  | ucture                 | TC Standard 3.3 V I/O     |                                                                           |  |  |  |  |  |

|                                                                                                                                          |                        | RST                       | Bidirectional reset pin with embedded weak pull-up resistor               |  |  |  |  |  |

| No                                                                                                                                       | tes                    | Unless otherwise s reset. | specified by a note, all I/Os are set as floating inputs during and after |  |  |  |  |  |

| Pin                                                                                                                                      | Alternate<br>functions | Functions selected        | through GPIOx_AFR registers                                               |  |  |  |  |  |

| functions                                                                                                                                | Additional functions   | Functions directly        | selected/enabled through peripheral registers                             |  |  |  |  |  |

|                 |         | Pin nı | umbe     | rs       |          |                                      |             |               |            | Pin functions                                       |                                            |  |

|-----------------|---------|--------|----------|----------|----------|--------------------------------------|-------------|---------------|------------|-----------------------------------------------------|--------------------------------------------|--|

| LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | UFQFPN28 | TSSPOP20 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate function                                  | Additional<br>functions                    |  |

| 1               | -       | -      | -        | -        | -        | VBAT                                 | S           | -             | -          | Backup power s                                      | upply                                      |  |

| 2               | A6      | -      | -        | -        | -        | PC13                                 | I/O         | тс            | (1)<br>(2) | -                                                   | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT |  |

| 3               | B6      | -      | -        | -        | -        | PC14-<br>OSC32_IN<br>(PC14)          | I/O         | тс            | (1)<br>(2) | -                                                   | OSC32_IN                                   |  |

| 4               | C6      | -      | -        | -        | -        | PC15-<br>OSC32_OUT<br>(PC15)         | I/O         | тс            | (1)<br>(2) | -                                                   | OSC32_OUT                                  |  |

| 5               | B5      | 2      | 2        | 2        | 2        | PF0-OSC_IN<br>(PF0)                  | I/O         | FTf           | -          | CRS_SYNC<br>I2C1_SDA                                | OSC_IN                                     |  |

| 6               | C5      | 3      | 3        | 3        | 3        | PF1-OSC_OUT<br>(PF1)                 | I/O         | FTf           | -          | I2C1_SCL                                            | OSC_OUT                                    |  |

| 7               | D5      | 4      | 4        | 4        | 4        | NRST                                 | I/O         | RST           | -          | Device reset input / interr<br>(active low          |                                            |  |

| 8               | D6      | 32     | 0        | 16       | 15       | VSSA                                 | S           |               | (3)        | Analog grou                                         | nd                                         |  |

| 9               | E5      | 5      | 5        | 5        | 5        | VDDA                                 | S           |               | -          | Analog power s                                      | upply                                      |  |

| 10              | F6      | 6      | 6        | 6        | 6        | PA0                                  | I/O         | ТТа           | -          | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1          | RTC_<br>TAMP2,<br>WKUP1,<br>ADC_IN0,       |  |

| 11              | D4      | 7      | 7        | 7        | 7        | PA1                                  | I/O         | ТТа           | -          | USART2_RTS,<br>TIM2_CH2,<br>TSC_G1_IO2,<br>EVENTOUT | ADC_IN1                                    |  |

| 12              | E4      | 8      | 8        | 8        | 8        | PA2                                  | I/O         | ТТа           | -          | USART2_TX,<br>TIM2_CH3,<br>TSC_G1_IO3               | ADC_IN2,<br>WKUP4                          |  |

| 13              | F5      | 9      | 9        | 9        | 9        | PA3                                  | I/O         | ТТа           | -          | USART2_RX,<br>TIM2_CH4,<br>TSC_G1_IO4               | ADC_IN3                                    |  |

Table 13. STM32F042x pin definitions

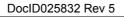

## 6.1.6 Power supply scheme

Figure 13. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

| Tabl                                | Table 24. Frogrammable voltage detector characteristics (continued) |              |      |      |                     |      |  |  |  |

|-------------------------------------|---------------------------------------------------------------------|--------------|------|------|---------------------|------|--|--|--|

| Symbol                              | Parameter                                                           | Conditions   | Min  | Тур  | Max                 | Unit |  |  |  |

| V                                   | PVD threshold 6                                                     | Rising edge  | 2.66 | 2.78 | 2.9                 | V    |  |  |  |

| V <sub>PVD6</sub>                   |                                                                     | Falling edge | 2.56 | 2.68 | 2.8                 | V    |  |  |  |

| M                                   | PVD threshold 7                                                     | Rising edge  | 2.76 | 2.88 | 3                   | V    |  |  |  |

| V <sub>PVD7</sub>                   |                                                                     | Falling edge | 2.66 | 2.78 | 2.9                 | V    |  |  |  |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis                                                      | -            | -    | 100  | -                   | mV   |  |  |  |

| I <sub>DD(PVD)</sub>                | PVD current consumption                                             | -            | -    | 0.15 | 0.26 <sup>(1)</sup> | μA   |  |  |  |

Table 24. Programmable voltage detector characteristics (continued)

1. Guaranteed by design, not tested in production.

## 6.3.4 Embedded reference voltage

The parameters given in *Table 25* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Symbol                 | Parameter                                                           | Parameter Conditions              |                      | Тур  | Max                | Unit   |  |  |

|------------------------|---------------------------------------------------------------------|-----------------------------------|----------------------|------|--------------------|--------|--|--|

| V <sub>REFINT</sub>    | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.2                  | 1.23 | 1.25               | V      |  |  |

| t <sub>start</sub>     | ADC_IN17 buffer startup time                                        | -                                 | -                    | -    | 10 <sup>(1)</sup>  | μs     |  |  |

| t <sub>S_vrefint</sub> | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | 4 <sup>(1)</sup>     | -    | -                  | μs     |  |  |

| ΔV <sub>REFINT</sub>   | Internal reference voltage<br>spread over the<br>temperature range  | e V <sub>DDA</sub> = 3 V          |                      | -    | 10 <sup>(1)</sup>  | mV     |  |  |

| T <sub>Coeff</sub>     | Temperature coefficient                                             | -                                 | - 100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |  |  |

Table 25. Embedded internal reference voltage

1. Guaranteed by design, not tested in production.

## 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 26* to *Table 28* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Table 26. Typical and maximum current consumption from $\rm V_{\rm DD}$ supply | at V <sub>DD</sub> = 3.6 V |

|--------------------------------------------------------------------------------|----------------------------|

|--------------------------------------------------------------------------------|----------------------------|

| _ 5             |                                 |                       | All        | peripher          | als enab | led <sup>(1)</sup> | All                  | periphe | rals disa | abled |                     |     |      |

|-----------------|---------------------------------|-----------------------|------------|-------------------|----------|--------------------|----------------------|---------|-----------|-------|---------------------|-----|------|

| Symbol          | mbol                            | Parameter             | Conditions | f <sub>HCLK</sub> |          | N                  | lax @ T <sub>A</sub> | (2)     |           | м     | ax @ T <sub>A</sub> | (2) | Unit |

| ŝ               | Par                             |                       |            | Тур               | 25 °C    | 85 °C              | 105 °C               | Тур     | 25 °C     | 85 °C | 105 °C              |     |      |

|                 |                                 | HSI48                 | 48 MHz     | 20.3              | 23.2     | 23.4               | 24.6                 | 12.7    | 14.4      | 14.4  | 14.7                |     |      |

|                 | ory                             |                       | 48 MHz     | 20.2              | 22.9     | 23.0               | 23.9                 | 12.6    | 14.1      | 14.3  | 14.4                |     |      |

|                 | node,<br>memory                 | HSE bypass,<br>PLL on | 32 MHz     | 14.0              | 16.0     | 16.1               | 16.7                 | 8.7     | 9.5       | 9.7   | 10.3                |     |      |

|                 | Run mode,<br>Flash mem          |                       | 24 MHz     | 11.0              | 13.5     | 13.7               | 13.8                 | 6.9     | 7.6       | 7.8   | 8.2                 |     |      |

|                 | n RL<br>n Fl                    | HSE bypass,           | 8 MHz      | 3.9               | 5.2      | 5.3                | 5.6                  | 2.6     | 3.1       | 3.2   | 3.3                 |     |      |

| I <sub>DD</sub> | upply current in executing from | PLL off               | 1 MHz      | 0.9               | 1.3      | 1.5                | 1.8                  | 0.7     | 1.0       | 1.1   | 1.3                 | mA  |      |

|                 | curr<br>uting                   |                       | 48 MHz     | 20.5              | 23.1     | 23.3               | 23.6                 | 12.8    | 14.6      | 14.6  | 15.0                |     |      |

|                 | Supply<br>le exect              | HSI clock,<br>PLL on  | 32 MHz     | 14.3              | 15.6     | 15.9               | 17.0                 | 8.6     | 9.5       | 9.7   | 10.0                |     |      |

|                 | Sul<br>code e                   |                       | 24 MHz     | 11.2              | 13.6     | 13.8               | 14.8                 | 6.9     | 7.4       | 7.5   | 7.7                 |     |      |

|                 | 8                               | HSI clock,<br>PLL off | 8 MHz      | 4.1               | 5.2      | 5.3                | 5.6                  | 2.6     | 3.1       | 3.1   | 3.3                 |     |      |

| Symbol           | Parameter                       | 4                 | Typical con<br>Run i   | sumption in<br>node     |                        | sumption in mode        | Unit |  |

|------------------|---------------------------------|-------------------|------------------------|-------------------------|------------------------|-------------------------|------|--|

| Symbol           | Falameter                       | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Peripherals<br>enabled | Peripherals<br>disabled | Unit |  |

|                  |                                 | 48 MHz            | 20.7                   | 12.8                    | 12.3                   | 3.4                     |      |  |

|                  |                                 | 36 MHz            | 15.9                   | 9.9                     | 9.5                    | 2.7                     |      |  |

|                  |                                 | 32 MHz            | 14.3                   | 9.0                     | 8.5                    | 2.5                     |      |  |

|                  | Current                         | 24 MHz            | 11.0                   | 7.1                     | 6.6                    | 2.1                     |      |  |

| 1                | consumption                     | 16 MHz            | 7.7                    | 5.0                     | 4.7                    | 1.6                     | mA   |  |

| I <sub>DD</sub>  | from V <sub>DD</sub><br>supply  | 8 MHz             | 4.3                    | 3.0                     | 2.7                    | 1.2                     | ША   |  |

|                  | Suppry                          | 4 MHz             | 2.6                    | 2.0                     | 1.7                    | 0.9                     |      |  |

|                  |                                 | 2 MHz             | 1.8                    | 1.5                     | 1.2                    | 0.8                     |      |  |

|                  |                                 | 1 MHz             | 1.4                    | 1.2                     | 1.0                    | 0.8                     |      |  |

|                  |                                 | 500 kHz           | 1.2                    | 1.1                     | 0.8                    | 0.7                     |      |  |

|                  |                                 | 48 MHz            |                        | 16                      | 3.3                    |                         |      |  |

|                  |                                 | 36 MHz            |                        | 12                      | 4.3                    |                         |      |  |

|                  |                                 | 32 MHz            |                        | 11                      | 1.9                    |                         |      |  |

|                  | Current                         | 24 MHz            |                        | 87                      | 7.1                    |                         |      |  |

| I <sub>DDA</sub> | consumption                     | 16 MHz            |                        | 62                      | 2.5                    |                         |      |  |

| 'DDA             | from V <sub>DDA</sub><br>supply | 8 MHz             |                        | 2                       | .5                     |                         | μA   |  |

|                  | Supply                          | 4 MHz             | 2.5                    |                         |                        |                         |      |  |

|                  |                                 | 2 MHz             |                        | 2                       | .5                     |                         |      |  |

|                  |                                 | 1 MHz             |                        | 2                       | .5                     |                         |      |  |

|                  |                                 | 500 kHz           |                        | 2                       | .5                     |                         |      |  |

#### Table 30. Typical current consumption, code executing from Flash memory, running from HSE 8 MHz crystal

## I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 50: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 32*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in *Table 18: Voltage characteristics*

|     | Peripheral               | Typical consumption at 25 °C | Unit   |

|-----|--------------------------|------------------------------|--------|

|     | BusMatrix <sup>(1)</sup> | 2.2                          |        |

|     | CRC                      | 1.9                          |        |

|     | DMA                      | 5.1                          |        |

|     | Flash memory interface   | 15.0                         |        |

|     | GPIOA                    | 8.2                          |        |

| AHB | GPIOB                    | 7.7                          | µA/MHz |

|     | GPIOC                    | 2.1                          |        |

|     | GPIOF                    | 1.8                          |        |

|     | SRAM                     | 1.1                          |        |

|     | TSC                      | 4.9                          |        |

|     | All AHB peripherals      | 49.8                         |        |

#### Table 32. Peripheral current consumption

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Note: An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

## 6.3.8 Internal clock source characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*. The provided curves are characterization results, not tested in production.

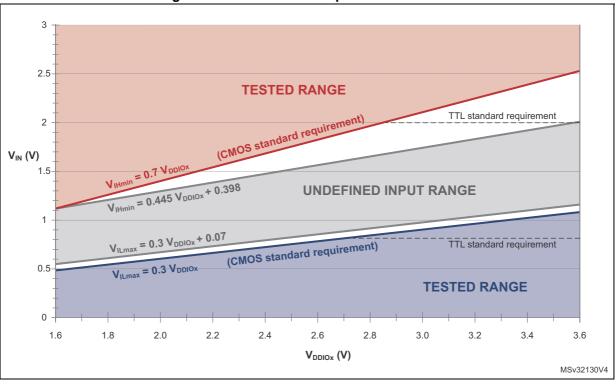

Figure 22. TC and TTa I/O input characteristics

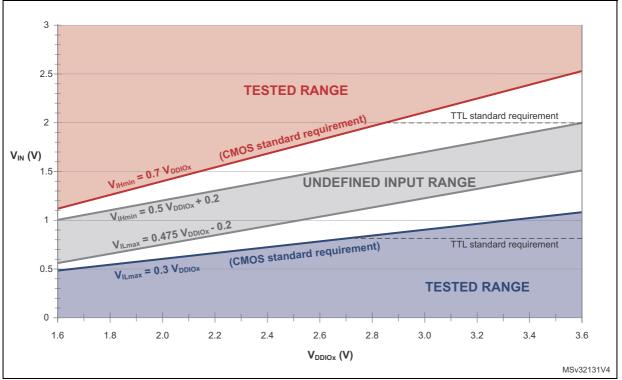

Figure 23. Five volt tolerant (FT and FTf) I/O input characteristics

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

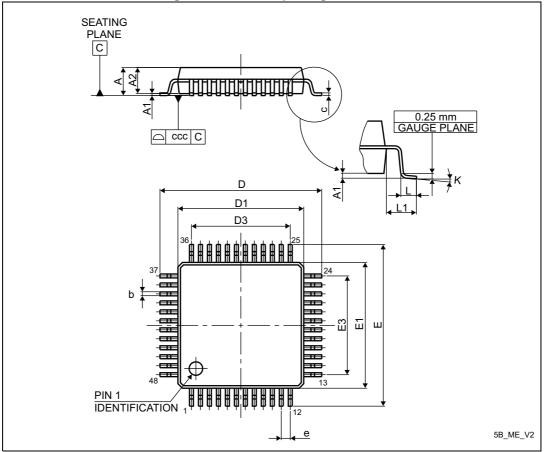

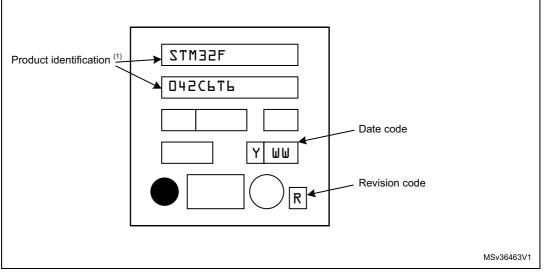

# 7.1 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package.

Figure 33. LQFP48 package outline

1. Drawing is not to scale.

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

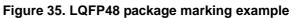

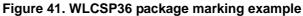

# 7.3 WLCSP36 package information

WLCSP36 is a 36-ball, 2.605 x 2.703 mm, 0.4 mm pitch wafer-level chip-scale package.

Figure 39. WLCSP36 package outline

1. Drawing is not to scale.

| Symbol            |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |  |

|-------------------|-------|-------------|-------|-----------------------|--------|--------|--|--|

| Symbol            | Min   | Тур         | Мах   | Min                   | Тур    | Max    |  |  |

| А                 | 0.525 | 0.555       | 0.585 | 0.0207                | 0.0219 | 0.0230 |  |  |

| A1                | -     | 0.175       | -     | -                     | 0.0069 | -      |  |  |

| A2                | -     | 0.380       | -     | -                     | 0.0150 | -      |  |  |

| A3 <sup>(2)</sup> | -     | 0.025       | -     | -                     | 0.0010 | -      |  |  |

| b <sup>(3)</sup>  | 0.220 | 0.250       | 0.280 | 0.0087                | 0.0098 | 0.0110 |  |  |

| D                 | 2.570 | 2.605       | 2.640 | 0.1012                | 0.1026 | 0.1039 |  |  |

| E                 | 2.668 | 2.703       | 2.738 | 0.1050                | 0.1064 | 0.1078 |  |  |

| е                 | -     | 0.400       | -     | -                     | 0.0157 | -      |  |  |

| e1                | -     | 2.000       | -     | -                     | 0.0787 | -      |  |  |

| e2                | -     | 2.000       | -     | -                     | 0.0787 | -      |  |  |

### Table 68. WLCSP36 package mechanical data

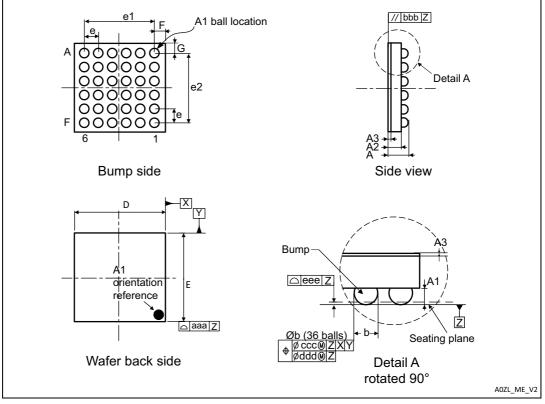

### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

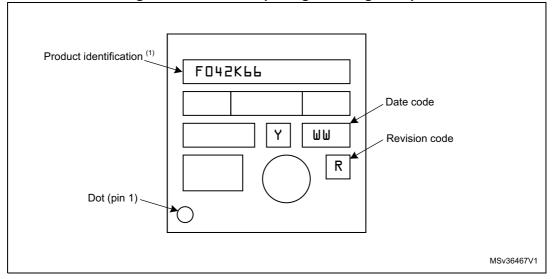

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 7.7 TSSOP20 package information

TSSOP20 is a 20-lead thin shrink small-outline, 6.5 x 4.4 mm, 0.65 mm pitch, package.

Figure 51.TSSOP20 package outline

1. Drawing is not to scale.

| Symbol            | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------------|-------|-------|-----------------------|--------|--------|

|                   | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| А                 | -           | -     | 1.200 | -                     | -      | 0.0472 |

| A1                | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2                | 0.800       | 1.000 | 1.050 | 0.0315                | 0.0394 | 0.0413 |

| b                 | 0.190       | -     | 0.300 | 0.0075                | -      | 0.0118 |

| с                 | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D <sup>(2)</sup>  | 6.400       | 6.500 | 6.600 | 0.2520                | 0.2559 | 0.2598 |

| E                 | 6.200       | 6.400 | 6.600 | 0.2441                | 0.2520 | 0.2598 |

| E1 <sup>(3)</sup> | 4.300       | 4.400 | 4.500 | 0.1693                | 0.1732 | 0.1772 |

| е                 | -           | 0.650 | -     | -                     | 0.0256 | -      |

| L                 | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

Table 73. TSSOP20 package mechanical data

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved