Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 26                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | A/D 13x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f042k4t6  |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Introd | luction                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Descr  | ription .                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Funct  | tional o                                                                                                      | verview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1    | ARM <sup>®</sup> -0                                                                                           | Cortex <sup>®</sup> -M0 core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2    | Memori                                                                                                        | es 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3    | Boot mo                                                                                                       | odes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.4    | Cyclic re                                                                                                     | edundancy check calculation unit (CRC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.5    | Power r                                                                                                       | nanagement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        | 3.5.1                                                                                                         | Power supply schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        | 3.5.2                                                                                                         | Power supply supervisors14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        | 3.5.3                                                                                                         | Voltage regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 3.5.4                                                                                                         | Low-power modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.6    | Clocks a                                                                                                      | and startup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.7    | General                                                                                                       | I-purpose inputs/outputs (GPIOs) 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.8    | Direct m                                                                                                      | nemory access controller (DMA) 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.9    | Interrup                                                                                                      | ts and events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | 3.9.1                                                                                                         | Nested vectored interrupt controller (NVIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | 3.9.2                                                                                                         | Extended interrupt/event controller (EXTI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.10   | Analog-                                                                                                       | to-digital converter (ADC) 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | 3.10.1                                                                                                        | Temperature sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|        | 3.10.2                                                                                                        | Internal voltage reference (V <sub>REFINT</sub> )19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|        | 3.10.3                                                                                                        | V <sub>BAT</sub> battery voltage monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.11   | Touch s                                                                                                       | ensing controller (TSC) 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.12   | Timers a                                                                                                      | and watchdogs 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 3.12.1                                                                                                        | Advanced-control timer (TIM1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | 3.12.2                                                                                                        | General-purpose timers (TIM2, 3, 14, 16, 17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|        | 3.12.3                                                                                                        | Independent watchdog (IWDG) 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | 3.12.4                                                                                                        | System window watchdog (WWDG)23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        |                                                                                                               | SysTick timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                                                                                                               | ne clock (RTC) and backup registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.14   | Inter-int                                                                                                     | egrated circuit interface (I <sup>2</sup> C) 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        | Desci<br>Funct<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.10<br>3.11<br>3.12 | <b>Functional or</b> 3.1       ARM®-0         3.2       Memori         3.2       Memori         3.3       Boot model         3.4       Cyclic re         3.5       Power re         3.5.1       3.5.2         3.5.3       3.5.4         3.6       Clocks at         3.7       Generat         3.8       Direct re         3.9       Interrup         3.9.1       3.9.2         3.10       Analog-         3.10.1       3.10.2         3.10.1       3.10.2         3.10.3       3.11         Touch st       3.12.1         3.12.1       3.12.3         3.12.4       3.12.4         3.12.5       3.13 |

DocID025832 Rev 5

|   |      | 6.3.13   | I/O current injection characteristics       |     |

|---|------|----------|---------------------------------------------|-----|

|   |      | 6.3.14   | I/O port characteristics                    |     |

|   |      | 6.3.15   | NRST pin characteristics                    |     |

|   |      | 6.3.16   | 12-bit ADC characteristics                  |     |

|   |      | 6.3.17   | Temperature sensor characteristics          |     |

|   |      | 6.3.18   | V <sub>BAT</sub> monitoring characteristics |     |

|   |      | 6.3.19   | Timer characteristics                       |     |

|   |      | 6.3.20   | Communication interfaces                    |     |

| 7 | Pack | age info | ormation                                    |     |

|   | 7.1  | LQFP4    | 48 package information                      |     |

|   | 7.2  | UFQFF    | PN48 package information                    |     |

|   | 7.3  | WLCS     | P36 package information                     |     |

|   | 7.4  | LQFP3    | 2 package information                       |     |

|   | 7.5  | UFQFF    | PN32 package information                    | 101 |

|   | 7.6  | UFQFF    | PN28 package information                    | 105 |

|   | 7.7  | TSSOF    | 20 package information                      | 108 |

|   | 7.8  | Therma   | al characteristics                          |     |

|   |      | 7.8.1    | Reference document                          |     |

|   |      | 7.8.2    | Selecting the product temperature range     | 111 |

| 8 | Ord  | ering in | formation                                   |     |

| 9 | Revi | sion his | tory                                        |     |

# 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

Additionally, also the internal RC 48 MHz oscillator can be selected for system clock or PLL input source. This oscillator can be automatically fine-trimmed by the means of the CRS peripheral using the external synchronization.

|                                          | Number of capacitive sensing channels       |     |                                  |                        |                        |  |  |  |  |

|------------------------------------------|---------------------------------------------|-----|----------------------------------|------------------------|------------------------|--|--|--|--|

| Analog I/O group                         | STM32F042Cx<br>LQPF48<br>UQFPN48<br>WLCSP36 |     | STM32F042Kx<br>LQFP32<br>UQFPN32 | STM32F042Gx<br>UQFPN28 | STM32F042Fx<br>TSSOP20 |  |  |  |  |

| G1                                       | 3                                           | 3 3 |                                  | 3                      | 3                      |  |  |  |  |

| G2                                       | 3                                           | 3   | 3                                | 3                      | 3                      |  |  |  |  |

| G3                                       | 2                                           | 2   | 1<br>2                           | 1                      | 0                      |  |  |  |  |

| G4                                       | 3                                           | 3   | 3                                | 1                      | 1                      |  |  |  |  |

| G5                                       | 3                                           | 3   | 3                                | 3                      | 0                      |  |  |  |  |

| Number of capacitive<br>sensing channels | 14                                          | 14  | 13<br>14                         | 11                     | 7                      |  |  |  |  |

#### Table 6. No. of capacitive sensing channels available on STM32F042x devices

# 3.12 Timers and watchdogs

The STM32F042x4/x6 devices include up to five general-purpose timers and an advanced control timer.

Table 7 compares the features of the different timers.

| Timer<br>type      | Timer          | Counter resolution | Counter<br>type      |                            |     | Capture/compare<br>channels | Complementary<br>outputs |  |  |  |  |

|--------------------|----------------|--------------------|----------------------|----------------------------|-----|-----------------------------|--------------------------|--|--|--|--|

| Advanced control   | TIM1           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes | 4                           | 3                        |  |  |  |  |

|                    | TIM2           | 32-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes | 4                           | -                        |  |  |  |  |

| General<br>purpose | TIM3           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes | 4                           | -                        |  |  |  |  |

|                    | TIM14          | 16-bit             | Up                   | integer from<br>1 to 65536 | No  | 1                           | -                        |  |  |  |  |

|                    | TIM16<br>TIM17 | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes | 1                           | 1                        |  |  |  |  |

Table 7. Timer feature comparison

## 3.12.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop and Standby mode capability

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- two anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.14 Inter-integrated circuit interface (I<sup>2</sup>C)

The I<sup>2</sup>C interface (I2C1) can operate in multimaster or slave modes. It can support Standard mode (up to 100 kbit/s), Fast mode (up to 400 kbit/s) and Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive.

It supports 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). It also includes programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |

| Table 8. Comparison of I <sup>2</sup> C analog and dig | igital filters |

|--------------------------------------------------------|----------------|

|--------------------------------------------------------|----------------|

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent

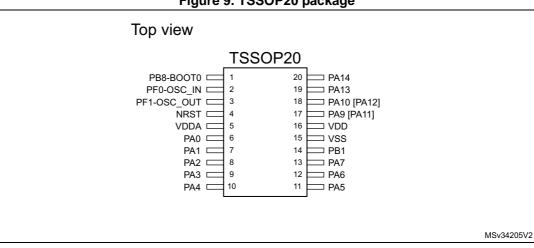

#### Figure 9. TSSOP20 package

1. Pin pair PA11/12 can be remapped in place of pin pair PA9/10 using the SYSCFG\_CFGR1 register.

#### Table 12. Legend/abbreviations used in the pinout table

| Na        | me                     | Abbreviation              | Abbreviation Definition                                                                          |  |  |  |  |  |

|-----------|------------------------|---------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin r     | name                   |                           | specified in brackets below the pin name, the pin function during and ame as the actual pin name |  |  |  |  |  |

|           |                        | S                         | Supply pin                                                                                       |  |  |  |  |  |

| Pin       | type                   | I/O                       | Input / output pin                                                                               |  |  |  |  |  |

|           |                        | FT                        | 5 V-tolerant I/O                                                                                 |  |  |  |  |  |

|           |                        | FTf                       | 5 V-tolerant I/O, FM+ capable                                                                    |  |  |  |  |  |

|           |                        | ТТа                       | 3.3 V-tolerant I/O directly connected to ADC                                                     |  |  |  |  |  |

| I/O str   | ucture                 | TC                        | Standard 3.3 V I/O                                                                               |  |  |  |  |  |

|           |                        | RST                       | RST Bidirectional reset pin with embedded weak pull-up resistor                                  |  |  |  |  |  |

| No        | tes                    | Unless otherwise s reset. | specified by a note, all I/Os are set as floating inputs during and after                        |  |  |  |  |  |

| Pin       | Alternate<br>functions | Functions selected        | through GPIOx_AFR registers                                                                      |  |  |  |  |  |

| functions | Additional functions   | Functions directly        | selected/enabled through peripheral registers                                                    |  |  |  |  |  |

|                 |         | Pin ni | umbe     | rs       |          |                                      |             |               |       | Pin functions                                                                                      |                         |  |

|-----------------|---------|--------|----------|----------|----------|--------------------------------------|-------------|---------------|-------|----------------------------------------------------------------------------------------------------|-------------------------|--|

| LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | UFQFPN28 | TSSPOP20 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate function                                                                                 | Additional<br>functions |  |

| 14              | C3      | 10     | 10       | 10       | 10       | PA4                                  | I/O         | ТТа           | -     | SPI1_NSS, I2S1_WS,<br>TIM14_CH1,<br>TSC_G2_IO1,<br>USART2_CK<br>USB_NOE                            | ADC_IN4                 |  |

| 15              | D3      | 11     | 11       | 11       | 11       | PA5                                  | I/O         | ТТа           | -     | SPI1_SCK, I2S1_CK,<br>CEC,<br>TIM2_CH1_ETR,<br>TSC_G2_IO2                                          | ADC_IN5                 |  |

| 16              | E3      | 12     | 12       | 12       | 12       | PA6                                  | I/O         | TTa           | -     | SPI1_MISO, I2S1_MCK,<br>TIM3_CH1, TIM1_BKIN,<br>TIM16_CH1,<br>TSC_G2_IO3,<br>EVENTOUT              | ADC_IN6                 |  |

| 17              | F4      | 13     | 13       | 13       | 13       | PA7                                  | I/O         | TTa           | -     | SPI1_MOSI, I2S1_SD,<br>TIM3_CH2, TIM14_CH1,<br>TIM1_CH1N,<br>TIM17_CH1,<br>TSC_G2_IO4,<br>EVENTOUT | ADC_IN7                 |  |

| 18              | F3      | 14     | 14       | 14       | -        | PB0                                  | I/O         | ТТа           | -     | TIM3_CH3,<br>TIM1_CH2N,<br>TSC_G3_IO2,<br>EVENTOUT                                                 | ADC_IN8                 |  |

| 19              | F2      | 15     | 15       | 15       | 14       | PB1                                  | I/O         | ТТа           | -     | TIM3_CH4, TIM14_CH1,<br>TIM1_CH3N,<br>TSC_G3_IO3                                                   | ADC_IN9                 |  |

| 20              | D2      | -      | 16       | -        | -        | PB2                                  | I/O         | FT            | -     | TSC_G3_IO4                                                                                         | -                       |  |

| 21              | -       | -      | -        | -        | -        | PB10                                 | I/O         | FTf           | -     | SPI2_SCK, CEC,<br>TSC_SYNC, TIM2_CH3,<br>I2C1_SCL                                                  | -                       |  |

| 22              | -       | -      | -        | -        | -        | PB11                                 | I/O         | FTf           | -     | TIM2_CH4,<br>EVENTOUT,<br>I2C1_SDA                                                                 | -                       |  |

| 23              | F1      | 16     | 0        | 16       | 15       | VSS                                  | S           | -             | -     | Ground                                                                                             |                         |  |

| 24              | -       | -      | -        | 17       | 16       | VDD                                  | S           | -             | I     | Digital power su                                                                                   | ipply                   |  |

| 25              | -       | -      | -        | -        | -        | PB12                                 | I/O         | FT            | -     | TIM1_BKIN, SPI2_NSS,<br>EVENTOUT                                                                   | -                       |  |

| Table | 13. STM32F042> | c pin d | lefinit | ions | (continued) |

|-------|----------------|---------|---------|------|-------------|

|       |                |         |         |      |             |

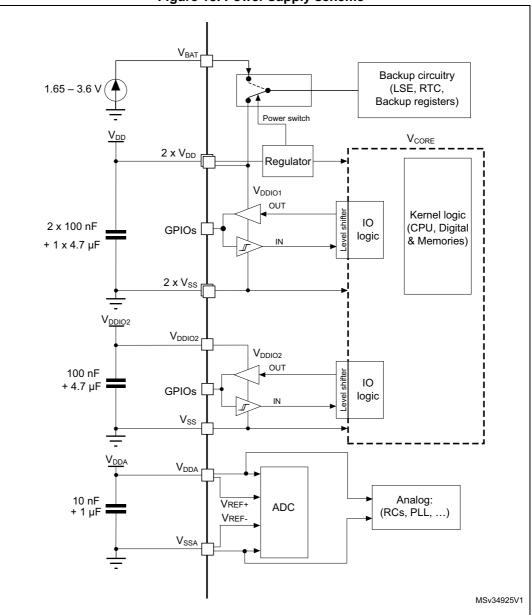

### 6.1.6 Power supply scheme

Figure 13. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

| Symbol   |                   |                                                                                  |        |       | Тур @ | V <sub>BAT</sub> |       |       |                           |                           |                            |      |

|----------|-------------------|----------------------------------------------------------------------------------|--------|-------|-------|------------------|-------|-------|---------------------------|---------------------------|----------------------------|------|

|          | Parameter         | Conditions                                                                       | 1.65 V | 1.8 V | 2.4 V | 2.7 V            | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|          | RTC<br>domain     | LSE & RTC ON; "Xtal<br>mode": lower driving<br>capability;<br>LSEDRV[1:0] = '00' | 0.5    | 0.5   | 0.6   | 0.7              | 0.9   | 1.1   | 1.2                       | 1.5                       | 2.0                        |      |

| IDD_VBAT | supply<br>current | LSE & RTC ON; "Xtal<br>mode" higher driving<br>capability;<br>LSEDRV[1:0] = '11' | 0.8    | 0.9   | 1.1   | 1.2              | 1.4   | 1.5   | 1.6                       | 2.0                       | 2.6                        | μA   |

Table 29. Typical and maximum current consumption from the  $\rm V_{BAT}$  supply

1. Data based on characterization results, not tested in production.

### Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins are in analog input configuration

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

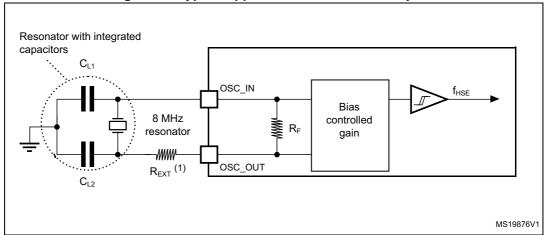

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 36*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                   | Conditions <sup>(1)</sup>                                   | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-----------------------------|-------------------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency        | -                                                           | 4                  | 8   | 32                 | MHz  |

| R <sub>F</sub>                      | Feedback resistor           | -                                                           | -                  | 200 | -                  | kΩ   |

|                                     |                             | During startup <sup>(3)</sup>                               | -                  | -   | 8.5                |      |

|                                     |                             | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@8 MHz  | -                  | 0.4 | -                  |      |

|                                     |                             | V <sub>DD</sub> = 3.3 V,<br>Rm = 45 Ω,<br>CL = 10 pF@8 MHz  | -                  | 0.5 | -                  |      |

| I <sub>DD</sub>                     | HSE current consumption     | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω,<br>CL = 5 pF@32 MHz  | -                  | 0.8 | -                  | mA   |

|                                     |                             | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω,<br>CL = 10 pF@32 MHz | -                  | 1   | -                  |      |

|                                     |                             | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω,<br>CL = 20 pF@32 MHz | -                  | 1.5 | -                  |      |

| 9 <sub>m</sub>                      | Oscillator transconductance | Startup                                                     | 10                 | -   | -                  | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                | V <sub>DD</sub> is stabilized                               | -                  | 2   | -                  | ms   |

|  | Table 36. | HSE | oscillator | characteristics |

|--|-----------|-----|------------|-----------------|

|--|-----------|-----|------------|-----------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by design, not tested in production.

3. This consumption level occurs during the first 2/3 of the  $t_{\mbox{SU(HSE)}}$  startup time

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 17*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

DocID025832 Rev 5

Figure 17. Typical application with an 8 MHz crystal

1.  $R_{EXT}$  value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 37*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                      | Conditions <sup>(1)</sup>                     | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|--------------------------------|-----------------------------------------------|--------------------|-----|--------------------|------|

|                                     |                                | low drive capability                          | -                  | 0.5 | 0.9                |      |

| I <sub>DD</sub>                     | LSE current consumption        | medium-low drive capability                   | -                  | -   | 1                  |      |

|                                     | LSE current consumption        | medium-high drive capability                  |                    | -   | 1.3                | μA   |

|                                     |                                | high drive capability                         | -                  | -   | 1.6                |      |

|                                     | Oscillator<br>transconductance | low drive capability                          | 5                  | -   | -                  |      |

| 9 <sub>m</sub>                      |                                | medium-low drive capability                   |                    | -   | -                  | µA/V |

|                                     |                                | transconductance medium-high drive capability |                    | -   | -                  |      |

|                                     | high drive capability          |                                               | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                   | V <sub>DDIOx</sub> is stabilized              | -                  | 2   | -                  | S    |

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |  |  |

|-------------------|--------------|--------------------------------|--------------------------------|------|--|--|

| /4                | 0            | 0.1                            | 409.6                          |      |  |  |

| /8                | 1            | 0.2                            | 819.2                          |      |  |  |

| /16               | 2            | 0.4                            | 1638.4                         |      |  |  |

| /32               | 3            | 0.8                            | 3276.8                         | ms   |  |  |

| /64               | 4            | 1.6                            | 6553.6                         |      |  |  |

| /128              | 5            | 3.2                            | 13107.2                        |      |  |  |

| /256              | 6 or 7       | 6.4                            | 26214.4                        |      |  |  |

Table 60. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

1. These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value | Max timeout value | Unit |

|-----------|-------|-------------------|-------------------|------|

| 1         | 0     | 0.0853            | 5.4613            |      |

| 2         | 1     | 0.1706            | 10.9226           | me   |

| 4         | 2     | 0.3413            | 21.8453           | ms   |

| 8         | 3     | 0.6826            | 43.6906           |      |

Table 61. WWDG min/max timeout value at 48 MHz (PCLK)

### 6.3.20 Communication interfaces

### I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol                               | Parameter              | Conditions         | Min | Мах | Unit |  |

|--------------------------------------|------------------------|--------------------|-----|-----|------|--|

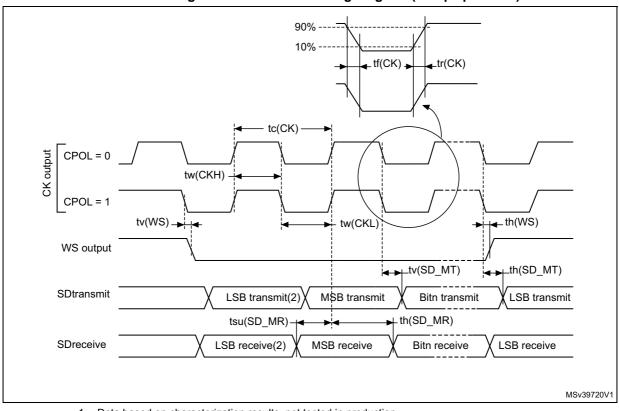

| t <sub>su(SD_MR)</sub>               | Data input setup time  | Master receiver    | 6   | -   |      |  |

| t <sub>su(SD_SR)</sub>               |                        | Slave receiver     | 2   | -   |      |  |

| t <sub>h(SD_MR)</sub> <sup>(2)</sup> | Data input hold time   | Master receiver    | 4   | -   |      |  |

| t <sub>h(SD_SR)</sub> <sup>(2)</sup> | Data input hold time   | Slave receiver     | 0.5 | -   |      |  |

| t <sub>v(SD_MT)</sub> <sup>(2)</sup> | Data output valid time | Master transmitter | -   | 4   | ns   |  |

| t <sub>v(SD_ST)</sub> <sup>(2)</sup> |                        | Slave transmitter  | -   | 20  |      |  |

| t <sub>h(SD_MT)</sub>                | Data output hold time  | Master transmitter | 0   | -   | ]    |  |

| t <sub>h(SD_ST)</sub>                |                        | Slave transmitter  | 13  | -   |      |  |

Table 64. I<sup>2</sup>S characteristics<sup>(1)</sup> (continued)

1. Data based on design simulation and/or characterization results, not tested in production.

2. Depends on  $f_{PCLK}$ . For example, if  $f_{PCLK}$  = 8 MHz, then  $T_{PCLK}$  = 1/ $f_{PLCLK}$  = 125 ns.

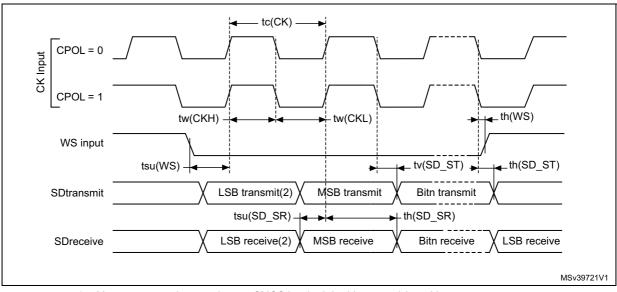

#### Figure 31. I<sup>2</sup>S slave timing diagram (Philips protocol)

1. Measurement points are done at CMOS levels: 0.3 ×  $V_{\text{DDIOx}}$  and 0.7 ×  $V_{\text{DDIOx}}$

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

### Figure 32. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

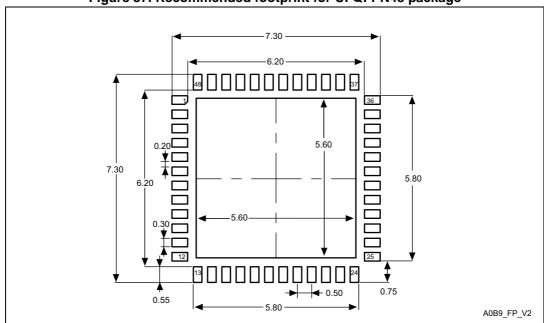

| Quarter at | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol     | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |  |

| А          | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| A1         | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |

| D          | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |

| E          | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |

| D2         | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |

| E2         | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |

| L          | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |

| Т          | -           | 0.152 | -     | -                     | 0.0060 | -      |  |

| b          | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |

| е          | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| ddd        | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

Table 67. UFQFPN48 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

### Figure 37. Recommended footprint for UFQFPN48 package

1. Dimensions are expressed in millimeters.

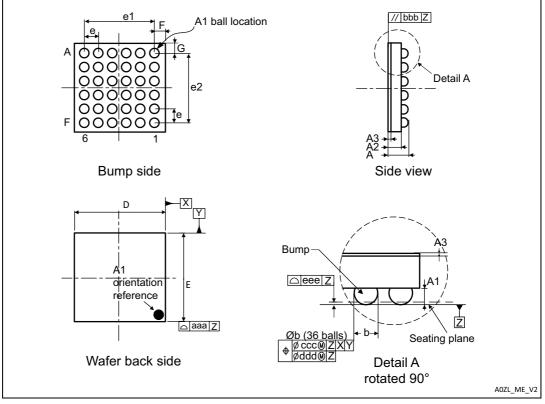

# 7.3 WLCSP36 package information

WLCSP36 is a 36-ball, 2.605 x 2.703 mm, 0.4 mm pitch wafer-level chip-scale package.

Figure 39. WLCSP36 package outline

1. Drawing is not to scale.

| Symbol            | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol            | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А                 | 0.525       | 0.555 | 0.585 | 0.0207                | 0.0219 | 0.0230 |

| A1                | -           | 0.175 | -     | -                     | 0.0069 | -      |

| A2                | -           | 0.380 | -     | -                     | 0.0150 | -      |

| A3 <sup>(2)</sup> | -           | 0.025 | -     | -                     | 0.0010 | -      |

| b <sup>(3)</sup>  | 0.220       | 0.250 | 0.280 | 0.0087                | 0.0098 | 0.0110 |

| D                 | 2.570       | 2.605 | 2.640 | 0.1012                | 0.1026 | 0.1039 |

| E                 | 2.668       | 2.703 | 2.738 | 0.1050                | 0.1064 | 0.1078 |

| е                 | -           | 0.400 | -     | -                     | 0.0157 | -      |

| e1                | -           | 2.000 | -     | -                     | 0.0787 | -      |

| e2                | -           | 2.000 | -     | -                     | 0.0787 | -      |

#### Table 68. WLCSP36 package mechanical data

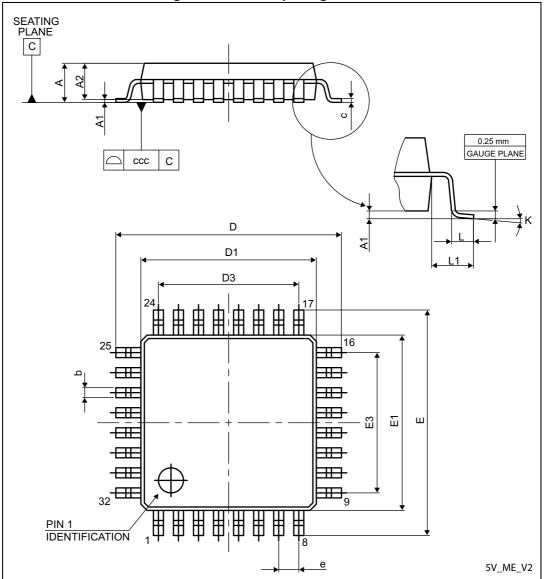

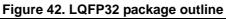

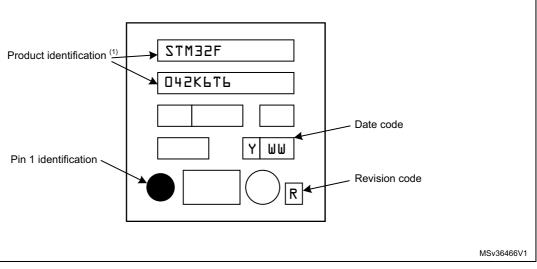

# 7.4 LQFP32 package information

LQFP32 is a 32-pin, 7 x 7 mm low-profile quad flat package.

1. Drawing is not to scale.

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

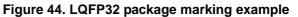

# 7.5 UFQFPN32 package information

UFQFPN32 is a 32-pin, 5x5 mm, 0.5 mm pitch ultra-thin fine-pitch quad flat package.

Figure 45. UFQFPN32 package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. This pad is used for the device ground and must be connected. It is referred to as pin 0 in *Table: Pin definitions*.

| Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | <ul> <li>Table 9: STM32F042x4/x6 I<sup>2</sup>C implementation - adding 20 mA</li> <li>Updates in Section 4: Pinouts and pin descriptions</li> <li>Table 12: Legend/abbreviations used in the pinout table - removing "I" pin type</li> <li>Updates in Section 5: Memory mapping:</li> <li>Figure 10: STM32F042x6 memory map, x4 difference described in text</li> <li>Updates in Section 6: Electrical characteristics:</li> <li>the condition "Regulator in run mode, all oscillators OFF" in Table 28: Typical and maximum consumption in Stop and Standby modes,</li> <li>footnote for V<sub>IN</sub> max value in Table 18: Voltage characteristics,</li> <li>footnote for max V<sub>IN</sub> in Table 21: General operating conditions,</li> <li>t<sub>START</sub> parameter definition in Table 25: Embedded internal reference voltage</li> <li>addition of t<sub>START</sub> parameter in Table 25: Embedded internal reference voltage, removal of -40°C to 85°C condition and the associated footnote</li> <li>Table 26: Typical and maximum current consumption from VDD supply at VDD = 3.6 V: removing "code executing from Flash or RAM"</li> <li>removal of the min value for t<sub>START</sub> parameter in Table 58: VBAT monitoring characteristics</li> <li>removal of Res<sub>TM</sub> parameter line from Table 59: TIMx characteristics and putting all values in new Typ column, substitution of t<sub>COUNTER</sub> with t<sub>MAX_COUNT</sub>, values defined as powers of two</li> <li>V<sub>ESD(CDM)</sub> class in Table 47: ESD absolute maximum ratings</li> <li>reorganization of Table 64: I<sup>2</sup>S characteristics and filling max value of t<sub>v(SD_ST)</sub></li> <li>adding definition of levels in Figure 32: I<sup>2</sup>S master timing diagram (Philips protocol)</li> <li>Updates in Section 7: Package information:</li> <li>heading and display of columns in Table 68: WLCSP36 package mechanical data.,</li> </ul> |

|          | <ul> <li>Updates in Section 7: Package information:</li> <li>heading and display of columns in Table 68: WLCSP36 package mechanical data.,</li> <li>Figure 38: UFQFPN48 package marking example</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          | <ul> <li>Figure 41: WLCSP36 package marking example</li> <li>Figure 50: UFQFPN28 package marking example</li> <li>Figure 41: WLCSP36 package marking example</li> <li>Figure 51: TSSOP20 package outline - correcting GAGE to GAUGE</li> <li>removing "die 445" from Table 74: Package thermal characteristics</li> <li>Updates in Section 8: Part numbering:</li> <li>adding tray packing to options</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Table 76. | Document | revision  | historv | (continued) | ) |

|-----------|----------|-----------|---------|-------------|---|

|           | Dogamon  | 101101011 |         | (ooninaoa)  | , |