Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>Details</b> Product Status | Active                                                                 |  |

|-------------------------------|------------------------------------------------------------------------|--|

| Core Processor                | ARM® Cortex®-M0                                                        |  |

| Core Size                     | 32-Bit Single-Core                                                     |  |

| Speed                         | 48MHz                                                                  |  |

| Connectivity                  | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |  |

| Peripherals                   | DMA, I²S, POR, PWM, WDT                                                |  |

| Number of I/O                 | 26                                                                     |  |

| Program Memory Size           | 16KB (16K x 8)                                                         |  |

| Program Memory Type           | FLASH                                                                  |  |

| EEPROM Size                   | -                                                                      |  |

| RAM Size                      | 6K x 8                                                                 |  |

| Voltage - Supply (Vcc/Vdd)    | 1.65V ~ 3.6V                                                           |  |

| Data Converters               | A/D 13x12b                                                             |  |

| Oscillator Type               | Internal                                                               |  |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                      |  |

| Mounting Type                 | Surface Mount                                                          |  |

| Package / Case                | 32-UFQFN Exposed Pad                                                   |  |

| Supplier Device Package       | 32-UFQFPN (5x5)                                                        |  |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f042k4u6  |  |

# **Contents**

| 1 | Intro | duction                                |                                                   | 9  |  |  |  |

|---|-------|----------------------------------------|---------------------------------------------------|----|--|--|--|

| 2 | Desc  | ription .                              |                                                   | 10 |  |  |  |

| 3 | Fund  | tional o                               | verview                                           | 13 |  |  |  |

|   | 3.1   | ARM®-                                  | Cortex <sup>®</sup> -M0 core                      | 13 |  |  |  |

|   | 3.2   | Memori                                 | ies                                               | 13 |  |  |  |

|   | 3.3   | Boot m                                 | odes                                              | 13 |  |  |  |

|   | 3.4   | Cyclic r                               | redundancy check calculation unit (CRC)           | 14 |  |  |  |

|   | 3.5   | Power                                  | management                                        | 14 |  |  |  |

|   |       | 3.5.1                                  | Power supply schemes                              | 14 |  |  |  |

|   |       | 3.5.2                                  | Power supply supervisors                          | 14 |  |  |  |

|   |       | 3.5.3                                  | Voltage regulator                                 | 15 |  |  |  |

|   |       | 3.5.4                                  | Low-power modes                                   | 15 |  |  |  |

|   | 3.6   | Clocks                                 | and startup                                       | 16 |  |  |  |

|   | 3.7   | General-purpose inputs/outputs (GPIOs) |                                                   |    |  |  |  |

|   | 3.8   | Direct r                               | memory access controller (DMA)                    | 18 |  |  |  |

| : | 3.9   | Interrup                               | ots and events                                    | 18 |  |  |  |

|   |       | 3.9.1                                  | Nested vectored interrupt controller (NVIC)       | 18 |  |  |  |

|   |       | 3.9.2                                  | Extended interrupt/event controller (EXTI)        | 18 |  |  |  |

|   | 3.10  | Analog-                                | -to-digital converter (ADC)                       | 18 |  |  |  |

|   |       | 3.10.1                                 | Temperature sensor                                | 19 |  |  |  |

|   |       | 3.10.2                                 | Internal voltage reference (V <sub>REFINT</sub> ) |    |  |  |  |

|   |       | 3.10.3                                 | V <sub>BAT</sub> battery voltage monitoring       | 20 |  |  |  |

|   | 3.11  | Touch s                                | sensing controller (TSC)                          | 20 |  |  |  |

|   | 3.12  | Timers                                 | and watchdogs                                     | 21 |  |  |  |

|   |       | 3.12.1                                 | Advanced-control timer (TIM1)                     | 21 |  |  |  |

|   |       | 3.12.2                                 | General-purpose timers (TIM2, 3, 14, 16, 17)      |    |  |  |  |

|   |       | 3.12.3                                 | Independent watchdog (IWDG)                       |    |  |  |  |

|   |       | 3.12.4                                 | System window watchdog (WWDG)                     |    |  |  |  |

|   |       | 3.12.5                                 | SysTick timer                                     |    |  |  |  |

|   | 3.13  |                                        | me clock (RTC) and backup registers               |    |  |  |  |

|   | 3.14  | Inter-int                              | tegrated circuit interface (I <sup>2</sup> C)     | 24 |  |  |  |

|   |       | 6.3.13   | I/O current injection characteristics       | 71  |

|---|-------|----------|---------------------------------------------|-----|

|   |       | 6.3.14   | I/O port characteristics                    | 72  |

|   |       | 6.3.15   | NRST pin characteristics                    | 77  |

|   |       | 6.3.16   | 12-bit ADC characteristics                  | 78  |

|   |       | 6.3.17   | Temperature sensor characteristics          | 82  |

|   |       | 6.3.18   | V <sub>BAT</sub> monitoring characteristics | 82  |

|   |       | 6.3.19   | Timer characteristics                       | 82  |

|   |       | 6.3.20   | Communication interfaces                    | 83  |

| 7 | Packa | age info | ormation                                    | 90  |

|   | 7.1   | LQFP4    | 48 package information                      | 90  |

|   | 7.2   | UFQFF    | PN48 package information                    | 93  |

|   | 7.3   | WLCSI    | ⊇36 package information                     | 96  |

|   | 7.4   | LQFP3    | 2 package information                       | 99  |

|   | 7.5   | UFQFF    | PN32 package information                    | 101 |

|   | 7.6   | UFQFF    | PN28 package information                    | 105 |

|   | 7.7   | TSSOF    | P20 package information                     |     |

|   | 7.8   | Therma   | al characteristics                          |     |

|   |       | 7.8.1    | Reference document                          | 111 |

|   |       | 7.8.2    | Selecting the product temperature range     | 111 |

| 8 | Orde  | ring in  | formation                                   | 113 |

| 9 | Revis | ion his  | tory                                        | 114 |

# 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

Additionally, also the internal RC 48 MHz oscillator can be selected for system clock or PLL input source. This oscillator can be automatically fine-trimmed by the means of the CRS peripheral using the external synchronization.

**577**

can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- input capture

- output compare

- PWM generation (edge or center-aligned modes)

- one-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard timers which have the same architecture. The advanced control timer can therefore work together with the other timers via the Timer Link feature for synchronization or event chaining.

### 3.12.2 General-purpose timers (TIM2, 3, 14, 16, 17)

There are five synchronizable general-purpose timers embedded in the STM32F042x4/x6 devices (see *Table 7* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

#### TIM2, TIM3

STM32F042x4/x6 devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advanced-control timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

#### **TIM14**

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

#### TIM16 and TIM17

Both timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

They each have a single channel for input capture/output compare, PWM or one-pulse mode output.

from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripheral can be served by the DMA controller.

Table 9. STM32F042x4/x6 I<sup>2</sup>C implementation

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 |

|--------------------------------------------------------------|------|

| 7-bit addressing mode                                        | X    |

| 10-bit addressing mode                                       | Х    |

| Standard mode (up to 100 kbit/s)                             | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    |

| Fast Mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | Х    |

| Independent clock                                            | Х    |

| SMBus                                                        | X    |

| Wakeup from STOP                                             | Х    |

<sup>1.</sup> X = supported.

# 3.15 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds two universal synchronous/asynchronous receivers/transmitters (USART1, USART2) which communicate at speeds of up to 6 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 supports also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and has a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interfaces can be served by the DMA controller.

Table 10. STM32F042x4/x6 USART implementation

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 |

|---------------------------------------------|--------|--------|

| Hardware flow control for modem             | Х      | X      |

| Continuous communication using DMA          | Х      | Х      |

| Multiprocessor communication                | Х      | X      |

| Synchronous mode                            | Х      | X      |

| Smartcard mode                              | Х      | -      |

| Single-wire half-duplex communication       | Х      | X      |

| IrDA SIR ENDEC block                        | Х      | -      |

| LIN mode                                    | Х      | -      |

| Dual clock domain and wakeup from Stop mode | Х      | -      |

| Receiver timeout interrupt                  | Х      | -      |

| USART modes/features <sup>(1)</sup> | USART1 | USART2 |

|-------------------------------------|--------|--------|

| Modbus communication                | Х      | -      |

| Auto baud rate detection            | X      | -      |

| Driver Enable                       | Х      | Х      |

Table 10. STM32F042x4/x6 USART implementation (continued)

# 3.16 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

Up to two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

One standard I<sup>2</sup>S interface (multiplexed with SPI1) supporting four different audio standards can operate as master or slave at half-duplex communication mode. It can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, it can output a clock for an external audio component at 256 times the sampling frequency.

Table 11. STM32F042x4/x6 SPI/I<sup>2</sup>S implementation

| SPI features <sup>(1)</sup> | SPI1 | SPI2 |

|-----------------------------|------|------|

| Hardware CRC calculation    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    |

| NSS pulse mode              | Х    | Х    |

| I <sup>2</sup> S mode       | Х    | -    |

| TI mode                     | Х    | Х    |

<sup>1.</sup> X = supported.

# 3.17 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

# 3.18 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames

<sup>1.</sup> X = supported.

# 4 Pinouts and pin descriptions

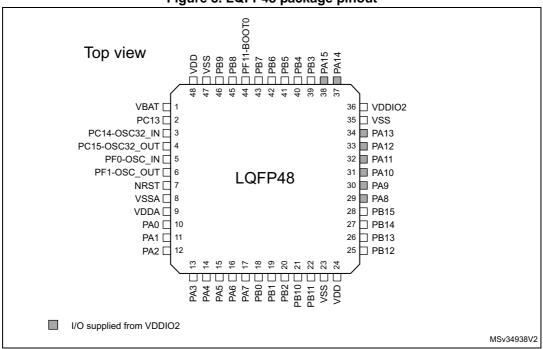

Figure 3. LQFP48 package pinout

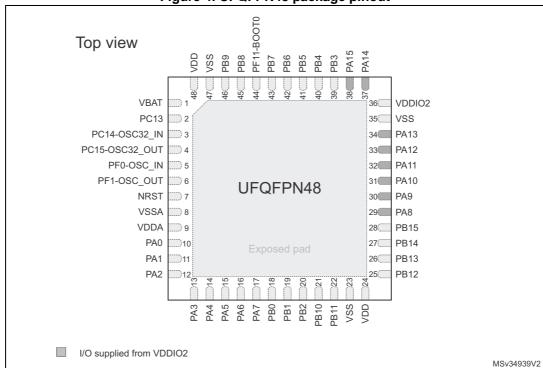

Figure 4. UFQFPN48 package pinout

57

Table 15. Alternate functions selected through GPIOB\_AFR registers for port B

| Pin name | AF0                 | AF1      | AF2        | AF3        | AF4    | AF5        |

|----------|---------------------|----------|------------|------------|--------|------------|

| PB0      | EVENTOUT            | TIM3_CH3 | TIM1_CH2N  | TSC_G3_IO2 | -      | -          |

| PB1      | TIM14_CH1           | TIM3_CH4 | TIM1_CH3N  | TSC_G3_IO3 | -      | -          |

| PB2      | -                   | -        | -          | TSC_G3_IO4 | -      | -          |

| PB3      | SPI1_SCK, I2S1_CK   | EVENTOUT | TIM2_CH2   | TSC_G5_IO1 | -      | -          |

| PB4      | SPI1_MISO, I2S1_MCK | TIM3_CH1 | EVENTOUT   | TSC_G5_IO2 | -      | TIM17_BKIN |

| PB5      | SPI1_MOSI, I2S1_SD  | TIM3_CH2 | TIM16_BKIN | I2C1_SMBA  | -      | -          |

| PB6      | USART1_TX           | I2C1_SCL | TIM16_CH1N | TSC_G5_IO3 | -      | -          |

| PB7      | USART1_RX           | I2C1_SDA | TIM17_CH1N | TSC_G5_IO4 | -      | -          |

| PB8      | CEC                 | I2C1_SCL | TIM16_CH1  | TSC_SYNC   | CAN_RX | -          |

| PB9      | IR_OUT              | I2C1_SDA | TIM17_CH1  | EVENTOUT   | CAN_TX | SPI2_NSS   |

| PB10     | CEC                 | I2C1_SCL | TIM2_CH3   | TSC_SYNC   | -      | SPI2_SCK   |

| PB11     | EVENTOUT            | I2C1_SDA | TIM2_CH4   | -          | -      | -          |

| PB12     | SPI2_NSS            | EVENTOUT | TIM1_BKIN  | -          | -      | -          |

| PB13     | SPI2_SCK            | -        | TIM1_CH1N  | -          | -      | I2C1_SCL   |

| PB14     | SPI2_MISO           | -        | TIM1_CH2N  | -          | -      | I2C1_SDA   |

| PB15     | SPI2_MOSI           | -        | TIM1_CH3N  | -          | -      | -          |

## Table 16. Alternate functions selected through GPIOF\_AFR registers for port F

| Pin name | AF0      | AF1      |

|----------|----------|----------|

| PF0      | CRS_SYNC | I2C1_SDA |

| PF1      | -        | I2C1_SCL |

# 6.1.7 Current consumption measurement

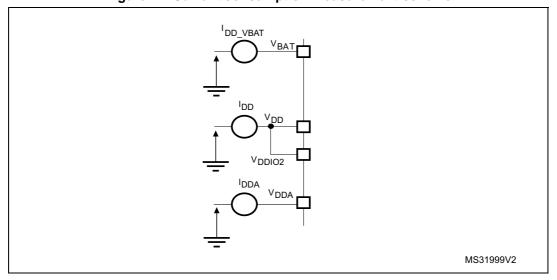

Figure 14. Current consumption measurement scheme

# 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 21. General operating conditions

| Symbol             | Parameter                                                                                | Conditions                                             | Min      | Max                                  | Unit    |  |

|--------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------|----------|--------------------------------------|---------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                             | -                                                      | 0        | 48                                   | MHz     |  |

| f <sub>PCLK</sub>  | Internal APB clock frequency                                                             | -                                                      | 0        | 48                                   | IVII IZ |  |

| V <sub>DD</sub>    | Standard operating voltage                                                               | -                                                      | 2.0      | 3.6                                  | V       |  |

| V <sub>DDIO2</sub> | I/O supply voltage                                                                       | Must not be supplied if V <sub>DD</sub> is not present | 1.65     | 3.6                                  | V       |  |

| $V_{\mathrm{DDA}}$ | Analog operating voltage (ADC not used)                                                  | Must have a potential equal                            | $V_{DD}$ | 3.6                                  | \/      |  |

|                    | Analog operating voltage (ADC used)                                                      | to or higher than V <sub>DD</sub>                      | 2.4      | 3.6                                  | V       |  |

| $V_{BAT}$          | Backup operating voltage                                                                 |                                                        | 1.65     | 3.6                                  | V       |  |

| V <sub>IN</sub>    | I/O input voltage                                                                        | TC and RST I/O                                         | -0.3     | V <sub>DDIOx</sub> +0.3              | V       |  |

|                    |                                                                                          | TTa I/O                                                | -0.3     | V <sub>DDA</sub> +0.3 <sup>(1)</sup> |         |  |

|                    |                                                                                          | FT and FTf I/O                                         | -0.3     | 5.5 <sup>(1)</sup>                   |         |  |

|                    | Power dissipation at $T_A$ = 85 °C for suffix 6 or $T_A$ = 105 °C for suffix $T_A^{(2)}$ | LQFP48                                                 | -        | 364                                  | mW      |  |

|                    |                                                                                          | UFQFPN48                                               | -        | 606                                  |         |  |

|                    |                                                                                          | WLCSP36                                                | -        | 313                                  |         |  |

| $P_{D}$            |                                                                                          | LQFP32                                                 | -        | 351                                  |         |  |

|                    |                                                                                          | UFQFPN32                                               | -        | 526                                  |         |  |

|                    |                                                                                          | UFQFPN28                                               | -        | 170                                  |         |  |

|                    | TSSOP20                                                                                  | TSSOP20                                                | -        | 263                                  |         |  |

|                    | suffix 6 version  Low power dissipation <sup>(3)</sup>                                   | Maximum power dissipation                              | -40      | 85                                   | 00      |  |

| т.                 |                                                                                          | Low power dissipation <sup>(3)</sup>                   | -40      | 105                                  | °C      |  |

| TA                 | Ambient temperature for the                                                              | Maximum power dissipation                              | -40      | 105                                  |         |  |

|                    | suffix 7 version                                                                         | Low power dissipation <sup>(3)</sup>                   | -40      | 125                                  | °C      |  |

| т.                 | lunction towns are true are a                                                            | Suffix 6 version                                       | -40      | 105                                  | °C      |  |

| TJ                 | Junction temperature range                                                               | Suffix 7 version                                       | -40      | 125                                  | °C      |  |

<sup>1.</sup> For operation with a voltage higher than  $V_{DDIOx}$  + 0.3 V, the internal pull-up resistor must be disabled.

### 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 22* are derived from tests performed under the ambient temperature condition summarized in *Table 21*.

<sup>2.</sup> If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ . See Section 7.8: Thermal characteristics.

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.8: Thermal characteristicsSection 7.8: Thermal characteristics).

Table 22. Operating conditions at power-up / power-down

| Symbol            | Parameter                       | Conditions | Min | Max | Unit  |

|-------------------|---------------------------------|------------|-----|-----|-------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate  | -          | 0   | 8   |       |

|                   | V <sub>DD</sub> fall time rate  |            | 20  | 8   | μs/V  |

|                   | V <sub>DDA</sub> rise time rate |            | 0   | 8   | μ5/ ν |

| t <sub>VDDA</sub> | V <sub>DDA</sub> fall time rate | -          | 20  | 8   |       |

## 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 23* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

Table 23. Embedded reset and power control block characteristics

| Symbol                               | Parameter                           | Conditions                  | Min                 | Тур  | Max                 | Unit |

|--------------------------------------|-------------------------------------|-----------------------------|---------------------|------|---------------------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup>  | Power on/power down reset threshold | Falling edge <sup>(2)</sup> | 1.80                | 1.88 | 1.96 <sup>(3)</sup> | ٧    |

|                                      |                                     | Rising edge                 | 1.84 <sup>(3)</sup> | 1.92 | 2.00                | V    |

| V <sub>PDRhyst</sub>                 | PDR hysteresis                      | -                           | -                   | 40   | -                   | mV   |

| t <sub>RSTTEMPO</sub> <sup>(4)</sup> | Reset temporization                 | -                           | 1.50                | 2.50 | 4.50                | ms   |

<sup>1.</sup> The PDR detector monitors  $V_{DD}$  and also  $V_{DDA}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{DD}$ .

Table 24. Programmable voltage detector characteristics

| Symbol            | Parameter          | Conditions        | Min       | Тур       | Max  | Unit |

|-------------------|--------------------|-------------------|-----------|-----------|------|------|

| V                 | PVD threshold 0    | Rising edge       | 2.1       | 2.18 2.26 | 2.26 | V    |

| V <sub>PVD0</sub> | F VD tillesiloid 0 | Falling edge      | 2         | 2.08      | 2.16 | V    |

| V                 | PVD threshold 1    | Rising edge       | 2.19      | 2.28      | 2.37 | V    |

| V <sub>PVD1</sub> | F VD tillesiloid 1 | Falling edge      | 2.09      | 2.18      | 2.27 | V    |

| V                 | PVD threshold 2    | Rising edge       | 2.28      | 2.38      | 2.48 | V    |

| V <sub>PVD2</sub> | PVD tillesiloid 2  | Falling edge      | 2.18 2.28 | 2.38      | V    |      |

| V                 | PVD threshold 3    | Rising edge       | 2.38      | 2.48      | 2.58 | V    |

| V <sub>PVD3</sub> | F VD tillesiloid 3 | Falling edge      | 2.28 2.38 | 2.48      | V    |      |

| V                 | PVD threshold 4    | Rising edge       | 2.47      | 2.58      | 2.69 | V    |

| $V_{PVD4}$        | PVD tillesiloid 4  | Falling edge 2.37 | 2.48      | 2.59      | V    |      |

| V                 | PVD threshold 5    | Rising edge       | 2.57      | 2.68      | 2.79 | V    |

| V <sub>PVD5</sub> | F VD tillesilota 5 | Falling edge      | 2.47      | 2.58      | 2.69 | V    |

<sup>2.</sup> The product behavior is guaranteed by design down to the minimum  $V_{POR/PDR}$  value.

<sup>3.</sup> Data based on characterization results, not tested in production.

<sup>4.</sup> Guaranteed by design, not tested in production.

Table 31. Switching output I/O current consumption

| Symbol          | Parameter   | Conditions <sup>(1)</sup>                             | I/O toggling frequency (f <sub>SW</sub> ) | Тур   | Unit |

|-----------------|-------------|-------------------------------------------------------|-------------------------------------------|-------|------|

|                 |             |                                                       | 4 MHz                                     | 0.07  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                            | 8 MHz                                     |       |      |

|                 |             | $C = C_{INT}$                                         | 16 MHz                                    | 0.31  |      |

|                 |             |                                                       | 24 MHz                                    | 0.53  | 0.53 |

|                 |             |                                                       | 48 MHz                                    | 0.92  |      |

|                 |             |                                                       | 4 MHz                                     | 0.18  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                            | 8 MHz                                     | 0.37  |      |

|                 |             | C <sub>EXT</sub> = 0 pF                               | 16 MHz                                    | 0.76  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                       | 24 MHz                                    | 1.39  | mA   |

|                 |             |                                                       | 48 MHz                                    | 2.188 |      |

|                 |             |                                                       | 4 MHz                                     | 0.32  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                            | 8 MHz                                     | 0.64  |      |

|                 |             | C <sub>EXT</sub> = 10 pF                              | 16 MHz                                    | 1.25  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                       | 24 MHz                                    | 2.23  |      |

| I <sub>SW</sub> | I/O current |                                                       | 48 MHz                                    | 4.442 |      |

| '500            | consumption |                                                       | 4 MHz                                     | 0.49  | 1177 |

|                 |             | $V_{DDIOx} = 3.3 V$ $C_{EXT} = 22 pF$                 | 8 MHz                                     | 0.94  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                       | 16 MHz                                    | 2.38  |      |

|                 |             | INT EXT 0                                             | 24 MHz                                    | 3.99  |      |

|                 |             |                                                       | 4 MHz                                     | 0.64  |      |

|                 |             | $V_{DDIOx} = 3.3 \text{ V}$ $C_{EXT} = 33 \text{ pF}$ | 8 MHz 1.25                                | 1.25  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                       | 16 MHz                                    | 3.24  |      |

|                 |             | INT EXT 0                                             | 24 MHz 5.                                 | 5.02  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                            | 4 MHz                                     | 0.81  |      |

|                 |             | $C_{EXT} = 47 \text{ pF}$                             | 8 MHz                                     | 1.7   |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$ $C = C_{int}$         | 16 MHz                                    | 3.67  |      |

|                 |             | V <sub>DDIOx</sub> = 2.4 V                            | 4 MHz                                     | 0.66  |      |

|                 |             | $C_{EXT} = 47 \text{ pF}$                             | 8 MHz                                     | 1.43  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                       | 16 MHz                                    | 2.45  |      |

|                 |             | C = C <sub>int</sub>                                  | 24 MHz                                    | 4.97  |      |

<sup>1.</sup> C<sub>S</sub> = 7 pF (estimated value).

## High-speed internal (HSI) RC oscillator

Table 38. HSI oscillator characteristics<sup>(1)</sup>

| Symbol                | Parameter                        | Conditions                                  | Min                 | Тур | Max                | Unit |

|-----------------------|----------------------------------|---------------------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>      | Frequency                        | -                                           | -                   | 8   | -                  | MHz  |

| TRIM                  | HSI user trimming step           | -                                           | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI)</sub> | Duty cycle                       | -                                           | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

|                       |                                  | $T_A = -40 \text{ to } 105^{\circ}\text{C}$ | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |

|                       |                                  | T <sub>A</sub> = -10 to 85°C                | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> |      |

| ACC                   | Accuracy of the HSI              | T <sub>A</sub> = 0 to 85°C                  | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   | %    |

| ACC <sub>HSI</sub>    | oscillator                       | T <sub>A</sub> = 0 to 70°C                  | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   | 70   |

|                       |                                  | T <sub>A</sub> = 0 to 55°C                  | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | $T_A = 25^{\circ}C^{(4)}$                   | -1                  | -   | 1                  |      |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time      | -                                           | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI)</sub> | HSI oscillator power consumption | -                                           | -                   | 80  | 100 <sup>(2)</sup> | μΑ   |

- 1.  $V_{DDA} = 3.3 \text{ V}$ ,  $T_A = -40 \text{ to } 105^{\circ}\text{C}$  unless otherwise specified.

- 2. Guaranteed by design, not tested in production.

- 3. Data based on characterization results, not tested in production.

- 4. Factory calibrated, parts not soldered.

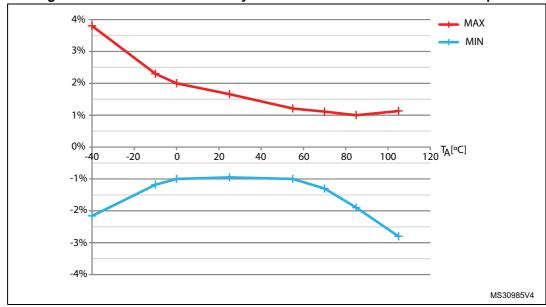

Figure 19. HSI oscillator accuracy characterization results for soldered parts

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (for example control registers)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

Max vs. [fHSE/fHCLK] **Monitored** Conditions Unit Symbol Parameter frequency band 8/48 MHz 0.1 to 30 MHz -9  $V_{DD} = 3.6 \text{ V}, T_A = 25 ^{\circ}\text{C},$ 30 to 130 MHz 9 dBuV LQFP48 package Peak level  $S_{EMI}$ compliant with 130 MHz to 1 GHz 17 IEC 61967-2 **EMI Level** 3

Table 46. EMI characteristics

#### 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol          | Parameter                                         | Conditions                             | Min | Тур | Мах | Unit |

|-----------------|---------------------------------------------------|----------------------------------------|-----|-----|-----|------|

| R <sub>PD</sub> | Weak pull-down equivalent resistor <sup>(3)</sup> | V <sub>IN</sub> = - V <sub>DDIOx</sub> | 25  | 40  | 55  | kΩ   |

| C <sub>IO</sub> | I/O pin capacitance                               | -                                      | -   | 5   | -   | pF   |

- 1. Data based on design simulation only. Not tested in production.

- The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 49: I/O current injection susceptibility.

- 3. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 22* for standard I/Os, and in *Figure 23* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOX</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 18: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see Table 18: Voltage characteristics).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

Table 51. Output voltage characteristics<sup>(1)</sup>

| Symbol                            | Parameter                                               | Conditions                                                 | Min                     | Max | Unit |

|-----------------------------------|---------------------------------------------------------|------------------------------------------------------------|-------------------------|-----|------|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                 | CMOS port <sup>(2)</sup>                                   | -                       | 0.4 | .,   |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                | $ I_{IO}  = 8 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$ | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                 | TTL port <sup>(2)</sup>                                    | -                       | 0.4 | .,   |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V     | 2.4                     | -   | V    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub>   = 20 mA                                  | -                       | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                | V <sub>DDIOx</sub> ≥ 2.7 V                                 | V <sub>DDIOx</sub> -1.3 | -   | V    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub>   = 6 mA                                   | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                | V <sub>DDIOx</sub> ≥ 2 V                                   | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OL</sub> <sup>(4)</sup>    | Output low level voltage for an I/O pin                 | II I = 4 m A                                               | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                | I <sub>IO</sub>   = 4 mA                                   | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in Fm+ mode | I <sub>IO</sub>   = 20 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V    | -                       | 0.4 | ٧    |

|                                   | Thir mode                                               | I <sub>IO</sub>   = 10 mA                                  | -                       | 0.4 | V    |

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in *Table 18:* Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

- 2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

- 3. Data based on characterization results. Not tested in production.

- 4. Data based on characterization results. Not tested in production.

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 24* and *Table 52*, respectively. Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

Table 52. I/O AC characteristics<sup>(1)(2)</sup>

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                  | Parameter                        | Conditions                                                              | Min                                                                            | Max  | Unit  |  |

|----------------------------------------|-------------------------|----------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|-------|--|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                         | -                                                                              |      | MHz   |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | C <sub>L</sub> = 50 pF, V <sub>DDIOX</sub> ≥ 2 V                        |                                                                                | 125  | ns    |  |

| <b>40</b>                              | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                         |                                                                                | 125  | 115   |  |

| x0                                     | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                         | -                                                                              | 1    | MHz   |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V                        | -                                                                              | 125  | ns    |  |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                         | -                                                                              | 125  | 115   |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                         | -                                                                              | 10   | MHz   |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2 \text{ V}$                        | -                                                                              | 25   | ne    |  |

| 01                                     | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                         |                                                                                | 25   | ns    |  |

| O1                                     | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                         | -                                                                              | 4    | MHz   |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V                        | -                                                                              | 62.5 | ns    |  |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                         | -                                                                              | 62.5 |       |  |

|                                        |                         |                                  | $C_L = 30 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                      | -                                                                              | 50   | - MHz |  |

|                                        | f                       | Maximum frequency <sup>(3)</sup> | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                      | -                                                                              | 30   |       |  |

|                                        | f <sub>max(IO)out</sub> |                                  | $C_L = 50 \text{ pF}, 2 \text{ V} \le \text{V}_{DDIOx} < 2.7 \text{ V}$ | -                                                                              | 20   |       |  |

|                                        |                         |                                  | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V                        | -                                                                              | 10   |       |  |

|                                        |                         |                                  | $C_L = 30 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                      | -                                                                              | 5    |       |  |

| 11                                     | t                       | Output fall time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                      | -                                                                              | 8    |       |  |

| 11                                     | t <sub>f(IO)out</sub>   | Output fail time                 | $C_L = 50 \text{ pF, } 2 \text{ V}$                                     | $C_L = 50 \text{ pF}, 2 \text{ V} \le \text{V}_{\text{DDIOx}} < 2.7 \text{ V}$ | -    | 12    |  |

|                                        |                         |                                  | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V                        |                                                                                | 25   | ns    |  |

|                                        |                         |                                  | $C_L = 30 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                      | -                                                                              | 5    | 113   |  |

|                                        | t and                   | Output rise time                 | $C_L$ = 50 pF, $V_{DDIOx} \ge 2.7 \text{ V}$                            |                                                                                | 8    |       |  |

|                                        | t <sub>r(IO)</sub> out  | Output 1130 tillio               | $C_L = 50 \text{ pF}, 2 \text{ V} \le \text{V}_{DDIOx} < 2.7 \text{ V}$ | -                                                                              | 12   | 1     |  |

|                                        |                         |                                  | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V                        | -                                                                              | 25   |       |  |

#### **USB** characteristics

The STM32F042x4/x6 USB interface is fully compliant with the USB specification version 2.0 and is USB-IF certified (for Full-speed device operation).

Table 65. USB electrical characteristics

| Symbol                          | Parameter                                      | Conditions           | Min.               | Тур  | Max. | Unit |

|---------------------------------|------------------------------------------------|----------------------|--------------------|------|------|------|

| V <sub>DDIO2</sub>              | USB transceiver operating voltage              | -                    | 3.0 <sup>(1)</sup> | -    | 3.6  | V    |

| t <sub>STARTUP</sub> (2)        | USB transceiver startup time                   | -                    | -                  | -    | 1.0  | μs   |

| R <sub>PUI</sub>                | Embedded USB_DP pull-up value during idle      | -                    | 1.1                | 1.26 | 1.5  | kΩ   |

| R <sub>PUR</sub>                | Embedded USB_DP pull-up value during reception | -                    | 2.0                | 2.26 | 2.6  | K22  |

| Z <sub>DRV</sub> <sup>(2)</sup> | Output driver impedance <sup>(3)</sup>         | Driving high and low | 28                 | 40   | 44   | Ω    |

The STM32F042x4/x6 USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V voltage range.

### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-); the matching impedance is already included in the embedded driver.

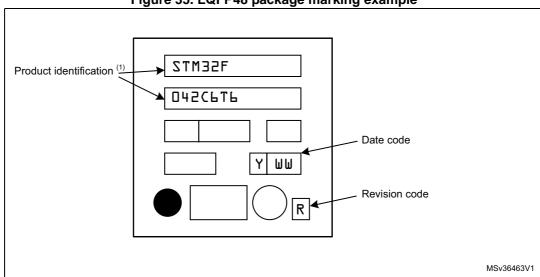

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 35. LQFP48 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

Table 70. LQFP32 package mechanical data

| Symbol |       | millimeters | 1     |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.300 | 0.370       | 0.450 | 0.0118 | 0.0146                | 0.0177 |

| С      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| D3     | -     | 5.600       | -     | -      | 0.2205                | -      |

| E      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| E3     | -     | 5.600       | -     | -      | 0.2205                | -      |

| е      | -     | 0.800       | -     | -      | 0.0315                | -      |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |

| k      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| ccc    | -     | -           | 0.100 | -      | -                     | 0.0039 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 43. Recommended footprint for LQFP32 package 9.70 5V\_FP\_V2

1. Dimensions are expressed in millimeters.