Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 26                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | A/D 13x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f042k6u6  |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | Block diagram                                                       | . 12 |

|------------|---------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                          | . 17 |

| Figure 3.  | LQFP48 package pinout                                               | . 28 |

| Figure 4.  | UFQFPN48 package pinout                                             | . 28 |

| Figure 5.  | WLCSP36 package pinout                                              | . 29 |

| Figure 6.  | LQFP32 package pinout                                               | . 29 |

| Figure 7.  | UFQFPN32 package pinout                                             | . 30 |

| Figure 8.  | UFQFPN28 package                                                    |      |

| Figure 9.  | TSSOP20 package                                                     |      |

| Figure 10. | STM32F042x6 memory map                                              |      |

| Figure 11. | Pin loading conditions                                              |      |

| Figure 12. | Pin input voltage                                                   |      |

| Figure 13. | Power supply scheme                                                 |      |

| Figure 14. | Current consumption measurement scheme                              |      |

| Figure 15. | High-speed external clock source AC timing diagram                  |      |

| Figure 16. | Low-speed external clock source AC timing diagram                   |      |

| Figure 17. | Typical application with an 8 MHz crystal                           |      |

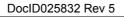

| Figure 18. | Typical application with a 32.768 kHz crystal                       |      |

| Figure 19. | HSI oscillator accuracy characterization results for soldered parts |      |

| Figure 20. | HSI14 oscillator accuracy characterization results                  |      |

| Figure 21. | HSI48 oscillator accuracy characterization results                  |      |

| Figure 22. | TC and TTa I/O input characteristics                                |      |

| Figure 23. | Five volt tolerant (FT and FTf) I/O input characteristics           |      |

| Figure 23. | I/O AC characteristics definition                                   |      |

|            |                                                                     |      |

| Figure 25. | Recommended NRST pin protection                                     |      |

| Figure 26. | ADC accuracy characteristics                                        |      |

| Figure 27. | Typical connection diagram using the ADC                            |      |

| Figure 28. | SPI timing diagram - slave mode and CPHA = 0                        |      |

| Figure 29. | SPI timing diagram - slave mode and CPHA = 1                        |      |

| Figure 30. | SPI timing diagram - master mode                                    |      |

| Figure 31. | I <sup>2</sup> S slave timing diagram (Philips protocol)            |      |

| Figure 32. | I <sup>2</sup> S master timing diagram (Philips protocol).          |      |

| Figure 33. | LQFP48 package outline                                              |      |

| Figure 34. | Recommended footprint for LQFP48 package                            |      |

| Figure 35. | LQFP48 package marking example                                      |      |

| Figure 36. | UFQFPN48 package outline                                            |      |

| Figure 37. | Recommended footprint for UFQFPN48 package                          |      |

| Figure 38. | UFQFPN48 package marking example                                    |      |

| Figure 39. | WLCSP36 package outline                                             |      |

| Figure 40. | Recommended pad footprint for WLCSP36 package                       | . 97 |

| Figure 41. | WLCSP36 package marking example                                     |      |

| Figure 42. | LQFP32 package outline                                              |      |

| Figure 43. | Recommended footprint for LQFP32 package                            | 100  |

| Figure 44. | LQFP32 package marking example                                      | 101  |

| Figure 45. | UFQFPN32 package outline                                            | 102  |

| Figure 46. | Recommended footprint for UFQFPN32 package                          |      |

| Figure 47. | UFQFPN32 package marking example                                    | 104  |

| Figure 48. | UFQFPN28 package outline                                            |      |

## 2 Description

The STM32F042x4/x6 microcontrollers incorporate the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0 32-bit RISC core operating at up to 48 MHz frequency, high-speed embedded memories (up to 32 Kbytes of Flash memory and 6 Kbytes of SRAM), and an extensive range of enhanced peripherals and I/Os. All devices offer standard communication interfaces (one I<sup>2</sup>C, two SPIs/one I<sup>2</sup>S, one HDMI CEC and two USARTs), one USB Full-speed device (crystal-less), one CAN, one 12-bit ADC, four 16-bit timers, one 32-bit timer and an advanced-control PWM timer.

The STM32F042x4/x6 microcontrollers operate in the -40 to +85 °C and -40 to +105 °C temperature ranges, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

The STM32F042x4/x6 microcontrollers include devices in seven different packages ranging from 20 pins to 48 pins with a die form also available upon request. Depending on the device chosen, different sets of peripherals are included.

These features make the STM32F042x4/x6 microcontrollers suitable for a wide range of applications such as application control and user interfaces, hand-held equipment, A/V receivers and digital TV, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms and HVACs.

## 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a CRC-32 (Ethernet) polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

### 3.5 **Power management**

#### 3.5.1 Power supply schemes

- $V_{DD} = V_{DDIO1} = 2.0$  to 3.6 V: external power supply for I/Os ( $V_{DDIO1}$ ) and the internal regulator. It is provided externally through VDD pins.

- $V_{DDA}$  = from  $V_{DD}$  to 3.6 V: external analog power supply for ADC, Reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 2.4 V when the ADC is used). It is provided externally through VDDA pin. The  $V_{DDA}$  voltage level must be always greater or equal to the  $V_{DD}$  voltage level and must be established first.

- V<sub>DDIO2</sub> = 1.65 to 3.6 V: external power supply for marked I/Os. V<sub>DDIO2</sub> is provided externally through the VDDIO2 pin. The V<sub>DDIO2</sub> voltage level is completely independent from V<sub>DD</sub> or V<sub>DDA</sub>, but it must not be provided without a valid supply on V<sub>DD</sub>. The V<sub>DDIO2</sub> supply is monitored and compared with the internal reference voltage (V<sub>REFINT</sub>). When the V<sub>DDIO2</sub> is below this threshold, all the I/Os supplied from this rail are disabled by hardware. The output of this comparator is connected to EXTI line 31 and it can be used to generate an interrupt. Refer to the pinout diagrams or tables for concerned I/Os list.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 13: Power supply scheme*.

#### 3.5.2 Power supply supervisors

The device has integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$

## 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

Additionally, also the internal RC 48 MHz oscillator can be selected for system clock or PLL input source. This oscillator can be automatically fine-trimmed by the means of the CRS peripheral using the external synchronization.

sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

#### 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{\scriptsize SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |  |  |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |  |  |

Table 3. Temperature sensor calibration values

#### 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Table 4. Internal voltage reference calibration | values |

|-------------------------------------------------|--------|

|-------------------------------------------------|--------|

| Calibration value name | Description                                                                              | Memory address            |

|------------------------|------------------------------------------------------------------------------------------|---------------------------|

|                        | Raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |

TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

#### 3.12.3 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.12.4 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.12.5 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

## 3.13 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, or at wake up from Standby mode.

|                 |         | Pin ni | umbe     | rs       |          |                                      |             |               |            | Pin function                                              | าร                                         |

|-----------------|---------|--------|----------|----------|----------|--------------------------------------|-------------|---------------|------------|-----------------------------------------------------------|--------------------------------------------|

| LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | UFQFPN28 | TSSPOP20 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate function                                        | Additional<br>functions                    |

| 1               | -       | -      | -        | -        | -        | VBAT                                 | S           | -             | -          | Backup power s                                            | upply                                      |

| 2               | A6      | -      | -        | -        | -        | PC13                                 | I/O         | тс            | (1)<br>(2) | -                                                         | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT |

| 3               | B6      | -      | -        | -        | -        | PC14-<br>OSC32_IN<br>(PC14)          | I/O         | тс            | (1)<br>(2) | -                                                         | OSC32_IN                                   |

| 4               | C6      | -      | -        | -        | -        | PC15-<br>OSC32_OUT<br>(PC15)         | I/O         | тс            | (1)<br>(2) | -                                                         | OSC32_OUT                                  |

| 5               | B5      | 2      | 2        | 2        | 2        | PF0-OSC_IN<br>(PF0)                  | I/O         | FTf           | -          | CRS_SYNC<br>I2C1_SDA                                      | OSC_IN                                     |

| 6               | C5      | 3      | 3        | 3        | 3        | PF1-OSC_OUT<br>(PF1)                 | I/O         | FTf           | -          | I2C1_SCL                                                  | OSC_OUT                                    |

| 7               | D5      | 4      | 4        | 4        | 4        | NRST                                 | I/O         | RST           | -          | Device reset input / internal reset outpu<br>(active low) |                                            |

| 8               | D6      | 32     | 0        | 16       | 15       | VSSA                                 | S           |               | (3)        | Analog grou                                               | nd                                         |

| 9               | E5      | 5      | 5        | 5        | 5        | VDDA                                 | S           |               | -          | Analog power s                                            | upply                                      |

| 10              | F6      | 6      | 6        | 6        | 6        | PA0                                  | I/O         | ТТа           | -          | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1                | RTC_<br>TAMP2,<br>WKUP1,<br>ADC_IN0,       |

| 11              | D4      | 7      | 7        | 7        | 7        | PA1                                  | I/O         | ТТа           | -          | USART2_RTS,<br>TIM2_CH2,<br>TSC_G1_IO2,<br>EVENTOUT       | ADC_IN1                                    |

| 12              | E4      | 8      | 8        | 8        | 8        | PA2                                  | I/O         | ТТа           | -          | USART2_TX,<br>TIM2_CH3,<br>TSC_G1_IO3                     | ADC_IN2,<br>WKUP4                          |

| 13              | F5      | 9      | 9        | 9        | 9        | PA3                                  | I/O         | ТТа           | -          | USART2_RX,<br>TIM2_CH4,<br>TSC_G1_IO4                     | ADC_IN3                                    |

Table 13. STM32F042x pin definitions

|                 |         | Pin nı | umbe     | rs       |          |                                      |             |     |                                                               | Pin functions                                                               |                         |  |

|-----------------|---------|--------|----------|----------|----------|--------------------------------------|-------------|-----|---------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------|--|

| LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | UFQFPN28 | TSSPOP20 | Pin name<br>(function upon<br>reset) | Pin<br>type |     |                                                               | Alternate function                                                          | Additional<br>functions |  |

| 38              | A2      | 25     | 25       | 23       | -        | PA15                                 | I/O         | FT  | (4)                                                           | SPI1_NSS, I2S1_WS,<br>USART2_RX,<br>TIM2_CH1_ETR,<br>EVENTOUT,<br>USB_NOE   | -                       |  |

| 39              | В3      | 26     | 26       | 24       | -        | PB3                                  | I/O         | FT  | -                                                             | SPI1_SCK, I2S1_CK,<br>TIM2_CH2,<br>TSC_G5_IO1,<br>EVENTOUT                  | -                       |  |

| 40              | A3      | 27     | 27       | 25       | -        | PB4                                  | I/O         | FT  | -                                                             | SPI1_MISO, I2S1_MCK,<br>TIM17_BKIN,<br>TIM3_CH1,<br>TSC_G5_IO2,<br>EVENTOUT | -                       |  |

| 41              | E6      | 28     | 28       | 26       | -        | PB5                                  | I/O         | FT  | -                                                             | SPI1_MOSI, I2S1_SD,<br>I2C1_SMBA,<br>TIM16_BKIN,<br>TIM3_CH2                | WKUP6                   |  |

| 42              | C4      | 29     | 29       | 27       | -        | PB6                                  | I/O         | FTf | -                                                             | I2C1_SCL,<br>USART1_TX,<br>TIM16_CH1N,<br>TSC_G5_I03                        | -                       |  |

| 43              | A4      | 30     | 30       | 28       | -        | PB7                                  | I/O         | FTf | FTf -<br>I2C1_SDA,<br>USART1_RX,<br>TIM17_CH1N,<br>TSC G5 IO4 |                                                                             | -                       |  |

| 44              | -       | -      | 31       | -        | -        | PF11-BOOT0                           | I/O         | FT  | -                                                             | -                                                                           | Boot memory selection   |  |

| -               | B4      | 31     | -        | 1        | 1        | PB8-BOOT0                            | I/O         | FTf | -                                                             | I2C1_SCL, CEC,<br>TIM16_CH1,<br>TSC_SYNC,<br>CAN_RX                         | Boot memory selection   |  |

| 45              | -       | -      | 32       | -        | -        | PB8                                  | I/O         | FTf | -                                                             | I2C1_SCL, CEC,<br>TIM16_CH1,<br>TSC_SYNC,<br>CAN_RX                         | -                       |  |

Table 13. STM32F042x pin definitions (continued)

|                 |         | Pin ni | umbe     | rs       |          |                                      |             |               | Pin functions |                                                                     |                         |  |  |

|-----------------|---------|--------|----------|----------|----------|--------------------------------------|-------------|---------------|---------------|---------------------------------------------------------------------|-------------------------|--|--|

| LQFP48/UFQFPN48 | WLCSP36 | LQFP32 | UFQFPN32 | NFQFPN28 | TSSPOP20 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes         | Alternate function                                                  | Additional<br>functions |  |  |

| 46              | -       | -      | -        | -        | -        | PB9                                  | I/O         | FTf           | -             | SPI2_NSS,<br>I2C1_SDA, IR_OUT,<br>TIM17_CH1,<br>EVENTOUT,<br>CAN_TX | -                       |  |  |

| 47              | -       | 32     | 0        | -        | -        | VSS                                  | S           | -             | -             | Ground                                                              |                         |  |  |

| 48              | A5      | 1      | 1        | -        | -        | VDD                                  | S           | -             | -             | Digital power supply                                                |                         |  |  |

Table 13. STM32F042x pin definitions (continued)

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

- These GPIOs must not be used as current sources (e.g. to drive an LED).

After the first RTC domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the RTC domain and RTC register descriptions in the reference manual.

3. Distinct VSSA pin is only available on 48-pin packages. On all other packages, the pin number corresponds to the VSS pin to which VSSA pad of the silicon die is connected.

4. PA8, PA9, PA10, PA11, PA12, PA13, PA14 and PA15 I/Os are supplied by VDDIO2.

5. Pin pair PA11/12 can be remapped in place of pin pair PA9/10 using SYSCFG\_CFGR1 register.

6. After reset, these pins are configured as SWDIO and SWCLK alternate functions, and the internal pull-up on the SWDIO pin and the internal pull-down on the SWCLK pin are activated.

#### Table 14. Alternate functions selected through GPIOA\_AFR registers for port A

| Pin name | AF0                 | AF1        | AF2          | AF3        | AF4       | AF5       | AF6      | AF7 |

|----------|---------------------|------------|--------------|------------|-----------|-----------|----------|-----|

| PA0      | -                   | USART2_CTS | TIM2_CH1_ETR | TSC_G1_IO1 | -         | -         | -        | -   |

| PA1      | EVENTOUT            | USART2_RTS | TIM2_CH2     | TSC_G1_IO2 | -         | -         | -        | -   |

| PA2      | -                   | USART2_TX  | TIM2_CH3     | TSC_G1_IO3 | -         | -         | -        | -   |

| PA3      | -                   | USART2_RX  | TIM2_CH4     | TSC_G1_IO4 | -         | -         | -        | -   |

| PA4      | SPI1_NSS, I2S1_WS   | USART2_CK  | USB_NOE      | TSC_G2_IO1 | TIM14_CH1 | -         | -        | -   |

| PA5      | SPI1_SCK, I2S1_CK   | CEC        | TIM2_CH1_ETR | TSC_G2_IO2 | -         | -         | -        | -   |

| PA6      | SPI1_MISO, I2S1_MCK | TIM3_CH1   | TIM1_BKIN    | TSC_G2_IO3 | -         | TIM16_CH1 | EVENTOUT | -   |

| PA7      | SPI1_MOSI, I2S1_SD  | TIM3_CH2   | TIM1_CH1N    | TSC_G2_IO4 | TIM14_CH1 | TIM17_CH1 | EVENTOUT | -   |

| PA8      | МСО                 | USART1_CK  | TIM1_CH1     | EVENTOUT   | CRS_SYNC  | -         | -        | -   |

| PA9      | -                   | USART1_TX  | TIM1_CH2     | TSC_G4_IO1 | I2C1_SCL  | MCO       | -        | -   |

| PA10     | TIM17_BKIN          | USART1_RX  | TIM1_CH3     | TSC_G4_IO2 | I2C1_SDA  | -         | -        | -   |

| PA11     | EVENTOUT            | USART1_CTS | TIM1_CH4     | TSC_G4_IO3 | CAN_RX    | I2C1_SCL  | -        | -   |

| PA12     | EVENTOUT            | USART1_RTS | TIM1_ETR     | TSC_G4_IO4 | CAN_TX    | I2C1_SDA  | -        | -   |

| PA13     | SWDIO               | IR_OUT     | USB_NOE      | -          | -         | -         | -        | -   |

| PA14     | SWCLK               | USART2_TX  | -            | -          | -         | -         | -        | -   |

| PA15     | SPI1_NSS, I2S1_WS   | USART2_RX  | TIM2_CH1_ETR | EVENTOUT   | -         | USB_NOE   | -        | -   |

DocID025832 Rev 5

Pinouts and pin descriptions

37/117

| Bus | Boundary address           | Size | Peripheral  |  |

|-----|----------------------------|------|-------------|--|

|     | 0x4000 7C00 - 0x4000 7FFF  | 1 KB | Reserved    |  |

|     | 0x4000 7800 - 0x4000 7BFF  | 1 KB | CEC         |  |

|     | 0x4000 7400 - 0x4000 77FF  | 1 KB | Reserved    |  |

|     | 0x4000 7000 - 0x4000 73FF  | 1 KB | PWR         |  |

|     | 0x4000 6C00 - 0x4000 6FFF  | 1 KB | CRS         |  |

|     | 0x4000 6800 - 0x4000 6BFF0 | 1 KB | Reserved    |  |

|     | 0x4000 6400 - 0x4000 67FF  | 1 KB | BxCAN       |  |

|     | 0x4000 6000 - 0x4000 63FF  | 1 KB | USB/CAN RAM |  |

|     | 0x4000 5C00 - 0x4000 5FFF  | 1 KB | USB         |  |

|     | 0x4000 5800 - 0x4000 5BFF  | 1 KB | Reserved    |  |

|     | 0x4000 5400 - 0x4000 57FF  | 1 KB | I2C1        |  |

|     | 0x4000 4800 - 0x4000 53FF  | 3 KB | Reserved    |  |

|     | 0x4000 4400 - 0x4000 47FF  | 1 KB | USART2      |  |

| APB | 0x4000 3C00 - 0x4000 43FF  | 2 KB | Reserved    |  |

|     | 0x4000 3800 - 0x4000 3BFF  | 1 KB | SPI2        |  |

|     | 0x4000 3400 - 0x4000 37FF  | 1 KB | Reserved    |  |

|     | 0x4000 3000 - 0x4000 33FF  | 1 KB | IWDG        |  |

|     | 0x4000 2C00 - 0x4000 2FFF  | 1 KB | WWDG        |  |

|     | 0x4000 2800 - 0x4000 2BFF  | 1 KB | RTC         |  |

|     | 0x4000 2400 - 0x4000 27FF  | 1 KB | Reserved    |  |

|     | 0x4000 2000 - 0x4000 23FF  | 1 KB | TIM14       |  |

|     | 0x4000 0800 - 0x4000 1FFF  | 6 KB | Reserved    |  |

|     | 0x4000 0400 - 0x4000 07FF  | 1 KB | TIM3        |  |

|     | 0x4000 0000 - 0x4000 03FF  | 1 KB | TIM2        |  |

| Tab | le 17. STM32F042x4/x6 peripheral register | boundary add | resses (continued) |

|-----|-------------------------------------------|--------------|--------------------|

|     |                                           |              |                    |

| . <u> </u>        |                                 | conditions at power-u | P / P01101 |     |      |

|-------------------|---------------------------------|-----------------------|------------|-----|------|

| Symbol            | Parameter                       | Conditions            | Min        | Мах | Unit |

| +                 | V <sub>DD</sub> rise time rate  |                       | 0          | 8   |      |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate  | -                     | 20         | 8   | μs/V |

| +                 | V <sub>DDA</sub> rise time rate |                       | 0          | 8   | μ5/ν |

| t <sub>VDDA</sub> | V <sub>DDA</sub> fall time rate | -                     | 20         | 8   |      |

Table 22. Operating conditions at power-up / power-down

### 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 23* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

Table 23. Embedded reset and power control block characteristics

| Symbol                               | Parameter                  | Conditions                  | Min                 | Тур  | Мах                 | Unit |

|--------------------------------------|----------------------------|-----------------------------|---------------------|------|---------------------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup>  |                            | Falling edge <sup>(2)</sup> | 1.80                | 1.88 | 1.96 <sup>(3)</sup> | V    |

| * POR/PDR                            | VPOR/PDR`´ reset threshold |                             | 1.84 <sup>(3)</sup> | 1.92 | 2.00                | V    |

| V <sub>PDRhyst</sub>                 | PDR hysteresis             | -                           | -                   | 40   | -                   | mV   |

| t <sub>RSTTEMPO</sub> <sup>(4)</sup> | Reset temporization        | -                           | 1.50                | 2.50 | 4.50                | ms   |

1. The PDR detector monitors  $V_{DD}$  and also  $V_{DDA}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{DD}.$

2. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

3. Data based on characterization results, not tested in production.

4. Guaranteed by design, not tested in production.

| Symbol            | Parameter                          | Conditions   | Min  | Тур  | Max  | Unit |

|-------------------|------------------------------------|--------------|------|------|------|------|

| V                 | PVD threshold 0                    | Rising edge  | 2.1  | 2.18 | 2.26 | V    |

| V <sub>PVD0</sub> |                                    | Falling edge | 2    | 2.08 | 2.16 | V    |

| M                 | DVD throshold 1                    | Rising edge  | 2.19 | 2.28 | 2.37 | V    |

| V <sub>PVD1</sub> | PVD threshold 1<br>PVD threshold 2 | Falling edge | 2.09 | 2.18 | 2.27 | V    |

| M                 | DVD threshold 2                    | Rising edge  | 2.28 | 2.38 | 2.48 | V    |

| VPVD2             | V <sub>PVD2</sub> PVD threshold 2  | Falling edge | 2.18 | 2.28 | 2.38 | V    |

| M                 | PVD threshold 3                    | Rising edge  | 2.38 | 2.48 | 2.58 | V    |

| V <sub>PVD3</sub> |                                    | Falling edge | 2.28 | 2.38 | 2.48 | V    |

| M                 | PVD threshold 4                    | Rising edge  | 2.47 | 2.58 | 2.69 | V    |

| V <sub>PVD4</sub> |                                    | Falling edge | 2.37 | 2.48 | 2.59 | V    |

| M                 | PVD threshold 5                    | Rising edge  | 2.57 | 2.68 | 2.79 | V    |

| V <sub>PVD5</sub> |                                    | Falling edge | 2.47 | 2.58 | 2.69 | V    |

#### Table 24. Programmable voltage detector characteristics

trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 32: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{\text{DDIOx}}$  is the I/O supply voltage

$V_{\rm DDIO_X}$  is the NO supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C = C<sub>INT</sub> + C<sub>EXT</sub> + C<sub>S</sub>

$\mathsf{C}_\mathsf{S}$  is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

#### 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 33* are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop or Standby mode, SYSCLK takes the default setting: HSI 8 MHz.

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode. The wakeup source from Standby mode is the WKUP1 pin (PA0).

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*..

| Symbol       | Parameter                   | Conditions               |         | Тур     | Typ @Vdd = Vdda |       |         |   |      |  |

|--------------|-----------------------------|--------------------------|---------|---------|-----------------|-------|---------|---|------|--|

| Symbol       | Farameter                   | Conditions               | = 2.0 V | = 2.4 V | = 2.7 V         | = 3 V | = 3.3 V | 5 | Unit |  |

| +            | Wakeup from Stop            | Regulator in run<br>mode | 3.2     | 3.1     | 2.9             | 2.9   | 2.8     | 5 |      |  |

| twustop mode | Regulator in low power mode | 7.0                      | 5.8     | 5.2     | 4.9             | 4.6   | 9       |   |      |  |

| twustandby   | Wakeup from<br>Standby mode | -                        | 60.4    | 55.6    | 53.5            | 52    | 51      | - | μs   |  |

| twusleep     | Wakeup from Sleep<br>mode   | -                        |         | 4 S)    | /SCLK cy        | cles  |         | - |      |  |

Table 33. Low-power mode wakeup timings

### 6.3.7 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in *Figure 15: High-speed external clock source AC timing diagram*.

| Symbol                                       | Parameter <sup>(1)</sup>             | Min                    | Тур | Max                    | Unit |

|----------------------------------------------|--------------------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source frequency | -                      | 8   | 32                     | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage  | 0.7 V <sub>DDIOx</sub> | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage   | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time              | 15                     | -   | -                      | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time             | -                      | -   | 20                     | 115  |

| Table 24  | Ligh speed | ovtornal | ucor   | alaak | oborootoriction |

|-----------|------------|----------|--------|-------|-----------------|

| Table 34. | Hign-speed | external | user ( | CIOCK | characteristics |

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Note: An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### 6.3.8 Internal clock source characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*. The provided curves are characterization results, not tested in production.

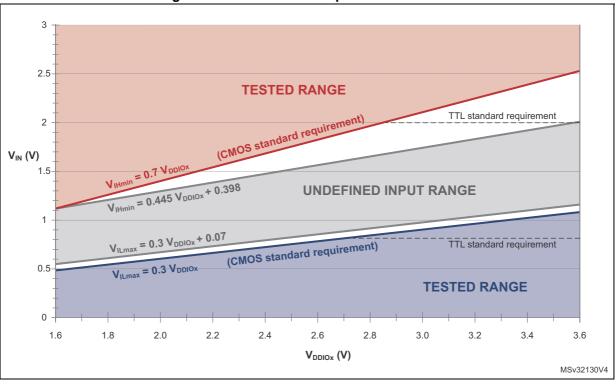

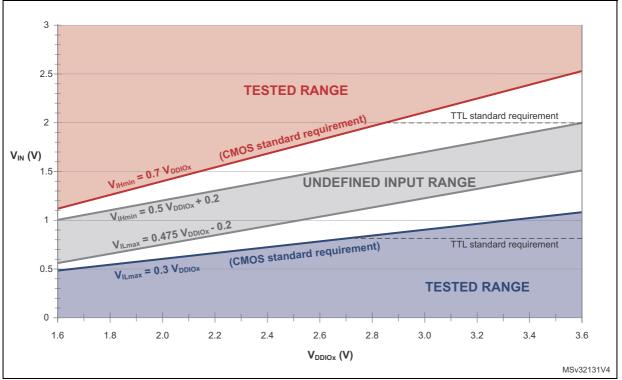

Figure 22. TC and TTa I/O input characteristics

Figure 23. Five volt tolerant (FT and FTf) I/O input characteristics

DocID025832 Rev 5

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 24* and *Table 52*, respectively. Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                  | Parameter                        | Conditions                                                                       | Min | Max  | Unit |

|----------------------------------------|-------------------------|----------------------------------|----------------------------------------------------------------------------------|-----|------|------|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                                  | -   | 2    | MHz  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2 V                                 | -   | 125  | ns   |

| x0                                     | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                                  | -   | 125  | 115  |

| X0                                     | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                                  | -   | 1    | MHz  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V                                 | -   | 125  | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                                  | -   | 125  | 115  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                                  | -   | 10   | MHz  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2 \text{ V}$                                 | -   | 25   | ns   |

| 01                                     | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                                  | -   | 25   | 115  |

| 01                                     | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                                  | -   | 4    | MHz  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V                                 | -   | 62.5 | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                                  | -   | 62.5 | 115  |

|                                        |                         |                                  | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$                                             | -   | 50   |      |

|                                        | f                       | Maximum frequency <sup>(3)</sup> | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2.7 V                               | -   | 30   | MHz  |

|                                        | f <sub>max(IO)out</sub> |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V                                         | -   | 20   |      |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                                                 | -   | 10   |      |

|                                        |                         |                                  | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$                                             | -   | 5    |      |

| 11                                     | +                       | Output fall time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$                               | -   | 8    |      |

|                                        | t <sub>f(IO)out</sub>   |                                  | $C_L$ = 50 pF, 2 V $\leq$ V <sub>DDIOx</sub> $<$ 2.7 V                           | -   | 12   |      |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                                                 | -   | 25   | ns   |

|                                        |                         |                                  | C <sub>L</sub> = 30 pF, V <sub>DDIOx</sub> ≥ 2.7 V                               | -   | 5    | 611  |

|                                        | t                       | Output rise time                 | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2.7 V                               | -   | 8    |      |

|                                        | t <sub>r(IO)out</sub>   |                                  | $C_{L} = 50 \text{ pF}, 2 \text{ V} \le \text{V}_{\text{DDIOx}} < 2.7 \text{ V}$ | -   | 12   |      |

|                                        |                         |                                  | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V                                 | -   | 25   |      |

| Table 52. | I/O AC | characteristics <sup>(1)(2)</sup> |

|-----------|--------|-----------------------------------|

|-----------|--------|-----------------------------------|

#### **USB** characteristics

The STM32F042x4/x6 USB interface is fully compliant with the USB specification version 2.0 and is USB-IF certified (for Full-speed device operation).

| Symbol                              | Parameter                                      | Conditions              | Min.               | Тур  | Max. | Unit |

|-------------------------------------|------------------------------------------------|-------------------------|--------------------|------|------|------|

| V <sub>DDIO2</sub>                  | USB transceiver operating voltage              | -                       | 3.0 <sup>(1)</sup> | -    | 3.6  | V    |

| t <sub>STARTUP</sub> <sup>(2)</sup> | USB transceiver startup time                   | -                       | -                  | -    | 1.0  | μs   |

| R <sub>PUI</sub>                    | Embedded USB_DP pull-up value during idle      | -                       | 1.1                | 1.26 | 1.5  | kΩ   |

| R <sub>PUR</sub>                    | Embedded USB_DP pull-up value during reception | -                       | 2.0                | 2.26 | 2.6  | K32  |

| Z <sub>DRV</sub> <sup>(2)</sup>     | Output driver impedance <sup>(3)</sup>         | Driving high<br>and low | 28                 | 40   | 44   | Ω    |

| Table 65. USB electrical characterist | ics |

|---------------------------------------|-----|

|---------------------------------------|-----|

1. The STM32F042x4/x6 USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V voltage range.

2. Guaranteed by design, not tested in production.

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-); the matching impedance is already included in the embedded driver.

#### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

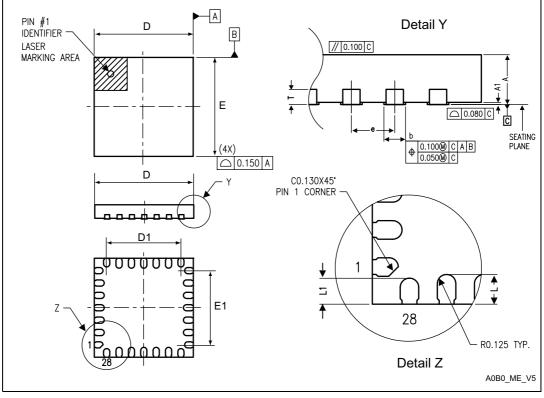

## 7.6 UFQFPN28 package information

UFQFPN28 is a 28-lead, 4x4 mm, 0.5 mm pitch, ultra-thin fine-pitch quad flat package.

1. Drawing is not to scale.

|        |       | millimeters |       |        | inches |        |  |

|--------|-------|-------------|-------|--------|--------|--------|--|

| Symbol | Min   | Тур         | Мах   | Min    | Тур    | Max    |  |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217 | 0.0236 |  |

| A1     | -     | 0.000       | 0.050 | -      | 0.0000 | 0.0020 |  |

| D      | 3.900 | 4.000       | 4.100 | 0.1535 | 0.1575 | 0.1614 |  |

| D1     | 2.900 | 3.000       | 3.100 | 0.1142 | 0.1181 | 0.1220 |  |

| E      | 3.900 | 4.000       | 4.100 | 0.1535 | 0.1575 | 0.1614 |  |

| E1     | 2.900 | 3.000       | 3.100 | 0.1142 | 0.1181 | 0.1220 |  |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157 | 0.0197 |  |

| L1     | 0.250 | 0.350       | 0.450 | 0.0098 | 0.0138 | 0.0177 |  |

| Т      | -     | 0.152       | -     | -      | 0.0060 | -      |  |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098 | 0.0118 |  |

| е      | -     | 0.500       | -     | -      | 0.0197 | -      |  |

Table 72. UFQFPN28 package mechanical data<sup>(1)</sup>

DocID025832 Rev 5

## 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Table 75. Order                          | -    |     |      |   |   |   |   |    |

|------------------------------------------|------|-----|------|---|---|---|---|----|

| Example:                                 | STM3 | 2 F | 042  | C | 6 | T | 6 | XX |

| Device family                            |      |     |      |   |   |   |   |    |

| STM32 = ARM-based 32-bit microcontroller |      |     |      |   |   |   |   |    |

|                                          |      |     |      |   |   |   |   |    |

| Product type                             |      |     |      |   |   |   |   |    |

| F = General-purpose                      |      |     |      |   |   |   |   |    |

| Sub-family                               |      |     |      |   |   |   |   |    |

| 042 = STM32F042xx                        |      |     |      |   |   |   |   |    |

| Pin count                                |      |     |      |   |   |   |   |    |

| F = 20 pins                              |      |     |      | ] |   |   |   |    |

| G = 28 pins                              |      |     |      |   |   |   |   |    |

| K = 32 pins                              |      |     |      |   |   |   |   |    |

| T = 36 pins                              |      |     |      |   |   |   |   |    |

| C = 48 pins                              |      |     |      |   |   |   |   |    |

| User code memory size                    |      |     |      |   |   |   |   |    |

| 4 = 16 Kbyte                             |      |     |      |   |   |   |   |    |

| 6 = 32 Kbyte                             |      |     |      |   |   |   |   |    |

| Package                                  |      |     |      |   |   |   |   |    |

| P = TSSOP                                |      |     |      |   |   |   |   |    |

| T = LQFP                                 |      |     |      |   |   |   |   |    |

| U = UFQFPN                               |      |     |      |   |   |   |   |    |

| Y = WLCSP                                |      |     |      |   |   |   |   |    |

| Temperature range                        |      |     |      |   |   |   |   |    |

| 6 = -40 to 85 °C                         |      |     | <br> |   |   |   |   |    |

| 7 = -40 to 105 °C                        |      |     |      |   |   |   |   |    |

|                                          |      |     |      |   |   |   |   |    |

| Options                                  |      |     |      |   |   |   |   |    |

xxx = code ID of programmed parts (includes packing type) TR = tape and reel packing blank = tray packing