Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 100MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I²C, IrDA, LINbus, MMC/SDIO, QSPI, SAI, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                 |

| Number of I/O              | 60                                                                                |

| Program Memory Size        | 1.5MB (1.5M × 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 320K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 81-UFBGA, WLCSP                                                                   |

| Supplier Device Package    | 81-WLCSP (4.04x3.95)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f413mhy6tr           |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.22 Timers and watchdogs

The devices embed two advanced-control timer, ten general-purpose timers, two basic timers, one low-power timer, two watchdog timers and a SysTick timer.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control and general-purpose timers.

| Timer<br>type        | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max.<br>interface<br>clock<br>(MHz) | Max.<br>timer<br>clock<br>(MHz) |

|----------------------|-----------------|-----------------------|-------------------------|---------------------------------------------|------------------------------|---------------------------------|---------------------------|-------------------------------------|---------------------------------|

| Advance<br>d-control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | Yes                       | 100                                 | 100                             |

|                      | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                        | 50                                  | 100                             |

|                      | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                        | 50                                  | 100                             |

| General              | TIM9            | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                        | 100                                 | 100                             |

| purpose              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                        | 100                                 | 100                             |

|                      | TIM12           | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                        | 50                                  | 100                             |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                        | 50                                  | 100                             |

Table 5. Timer feature comparison

| Timer<br>type          | Timer         | Counter<br>resolution | Counter<br>type | Prescaler<br>factor                         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max.<br>interface<br>clock<br>(MHz) | Max.<br>timer<br>clock<br>(MHz) |

|------------------------|---------------|-----------------------|-----------------|---------------------------------------------|------------------------------|---------------------------------|---------------------------|-------------------------------------|---------------------------------|

| Basic<br>timers        | TIM6,<br>TIM7 | 16-bit                | Up              | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 0                               | No                        | 50                                  | 100                             |

| Low-<br>power<br>timer | LPTIM1        | 16-bit                | Up              | Between<br>1 and 128                        | No                           | 2                               | No                        | 50                                  | 100                             |

Table 5. Timer feature comparison (continued)

# 3.22.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1/8) can be seen as three-phase PWM generator multiplexed on 4 independent channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as a 16-bit PWM generator, they have full modulation capability (0-100%).

The advanced-control timers can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

# 3.22.2 General-purpose timers (TIMx)

There are elven synchronizable general-purpose timers embedded in the STM32F413xG/H (see *Table 5* for differences).

## • TIM2, TIM3, TIM4, TIM5

The STM32F413xG/H devices include 4 full-featured general-purpose timers: TIM2. TIM3, TIM4 and TIM5. TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler while TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter plus a 16-bit prescaler. They all features four

independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 15 input capture/output compare/PWMs

TIM2. TIM3, TIM4 and TIM5 general-purpose timers can operate together or in conjunction with the other general-purpose timers and TIM1 advanced-control timer via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM output.

TIM2. TIM3, TIM4 and TIM5 channels have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### • TIM9, TIM10, TIM11, TIM12, TIM13 and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13 and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or onepulse mode output. They can be synchronized with TIM2. TIM3, TIM4 and TIM5 fullfeatured general-purpose timers or used as simple time bases.

#### 3.22.3 Basic timer (TIM6, TIM7)

TIM6 and TIM7 timers are basic 16-bit timers. They support independent DMA request generation.

#### 3.22.4 Low-power timer (LPTIM1)

The low-power timer (LPTIM1) features an independent clock and runs in Stop mode if it is clocked by LSE, LSI or by an external clock. LPTIM1 is able to wakeup the devices from Stop mode.

The low-power timer main features are the following:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one shot mode

- Selectable software / hardware input trigger

- Selectable clock source

- Internal clock source: LSE, LSI, HSI or APB1 clock

- External clock source over LPTIM1 input (working even with no internal clock source running, used by the pulse counter application)

- Programmable digital glitch filter

- Encoder mode

- Active in Stop mode.

## 3.22.5 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

DocID029162 Rev 4

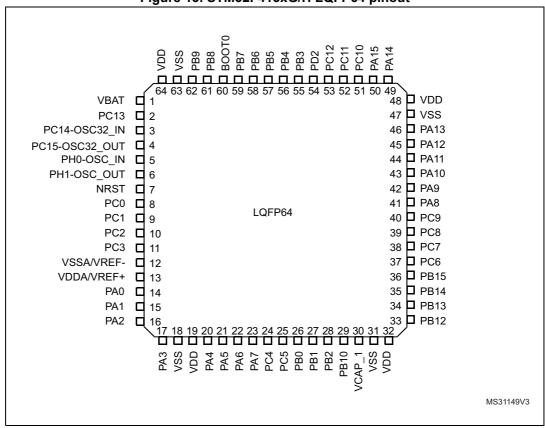

Figure 13. STM32F413xG/H LQFP64 pinout

1. The above figure shows the package top view.

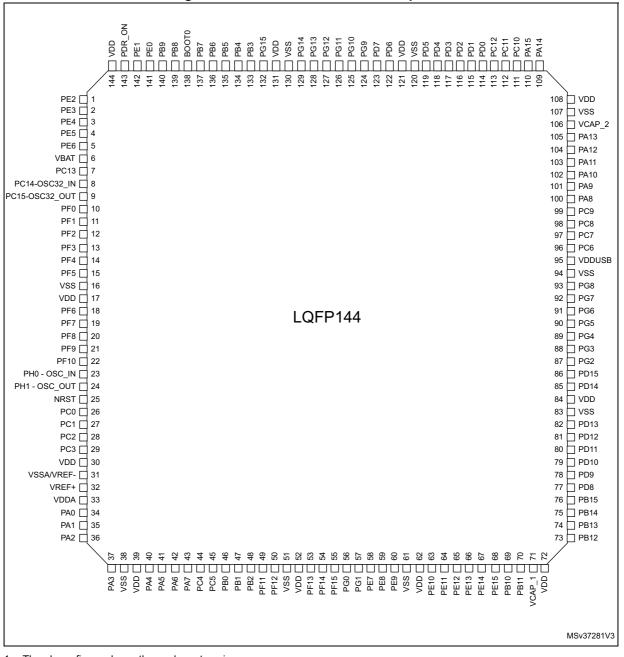

#### Figure 15. STM32F413xG/H LQFP144 pinout

1. The above figure shows the package top view.

|   |                    |      | -   |     |                |      |        |      |        |      |        |         |

|---|--------------------|------|-----|-----|----------------|------|--------|------|--------|------|--------|---------|

|   | 1                  | 2    | 3   | 4   | 5              | 6    | 7      | 8    | 9      | 10   | 11     | 12      |

| Α | PC13               | PE3  | PE2 | PE1 | PE0            | PB4  | PB3    | PD6  | PD7    | PA15 | PA14   | PA13    |

| в | PC14-<br>OSC32_IN  | PE4  | PE5 | PE6 | PB9            | PB5  | PG15   | PG12 | PD5    | PC11 | PC10   | PA12    |

| с | PC15-<br>OSC32_OUT | VBAT | PF0 | PF1 | PB8            | PB6  | PG14   | PG11 | PD4    | PC12 | VDDUSB | PA11    |

| D | PH0 -<br>OSC_IN    | vss  | VDD | PF2 | BOOTO          | PB7  | PG13   | PG10 | PD3    | PD1  | PA10   | PA9     |

| E | PH1 -<br>OSC_OUT   | PF3  | PF4 | PF5 | PDR_ON         | vss  | vss    | PG9  | PD2    | PD0  | PC9    | PA8     |

| F | NRST               | PF7  | PF6 | VDD | VDD            | VDD  | VDD    | VDD  | VDD    | VDD  | PC8    | PC7     |

| G | PF10               | PF9  | PF8 | VSS | VDD            | VDD  | VDD    | vss  | VCAP_2 | vss  | PG8    | PC6     |

| н | PC0                | PC1  | PC2 | PC3 | BYPASS_<br>REG | VSS  | VCAP_1 | PE11 | PD11   | PG7  | PG6    | PG5     |

| J | VSSA               | PA0  | PA4 | PC4 | PB2            | PG1  | PE10   | PE12 | PD10   | PG4  | PG3    | PG2     |

| к | VREF-              | PA1  | PA5 | PC5 | PF13           | PG0  | PE9    | PE13 | PD9    | PD13 | PD14   | PD15    |

| L | VREF+              | PA2  | PA6 | PB0 | PF12           | PF15 | PE8    | PE14 | PD8    | PD12 | PB14   | PB15    |

| м | VDDA               | PA3  | PA7 | PB1 | PF11           | PF14 | PE7    | PE15 | PB10   | PB11 | PB12   | PB13    |

|   |                    |      |     |     |                |      |        | •    |        |      |        | MSv3728 |

#### Figure 17. STM32F413xG/H UFBGA144 pinout

1. The above figure shows the package top view.

#### Table 9. Legend/abbreviations used in the pinout table

| Name                   | Abbreviation       | Definition                                                                                         |  |  |  |  |  |

|------------------------|--------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin name               |                    | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |  |

|                        | S                  | Supply pin                                                                                         |  |  |  |  |  |

| Pin type               | I                  | Input only pin                                                                                     |  |  |  |  |  |

|                        | I/O                | Input/ output pin                                                                                  |  |  |  |  |  |

|                        | FT                 | 5 V tolerant I/O                                                                                   |  |  |  |  |  |

|                        | FTf                | 5 V tolerant I/O, I2C FM+ option                                                                   |  |  |  |  |  |

| I/O structure          | TC                 | Standard 3.3 V I/O                                                                                 |  |  |  |  |  |

| NO STRUCTURE           | ТТа                | 3.3 V tolerant I/O directly connected to DAC                                                       |  |  |  |  |  |

|                        | В                  | Dedicated BOOT0 pin                                                                                |  |  |  |  |  |

|                        | NRST               | Bidirectional reset pin with embedded weak pull-up resistor                                        |  |  |  |  |  |

| Notes                  | Unless otherwise   | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |  |

| Alternate<br>functions | Functions selected | d through GPIOx_AFR registers                                                                      |  |  |  |  |  |

| Additional functions   | Functions directly | selected/enabled through peripheral registers                                                      |  |  |  |  |  |

|          |        | Ρ       | in Nu   | mber     |          |         |                                                         |             |                  |       |                     |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|---------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP81 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions | Additional<br>functions |

| -        | -      | B8      | -       | H3       | E5       | 143     | PDR_ON                                                  | Ι           | FT               | -     | -                   | -                       |

| 48       | 64     | A9      | 100     | C4       | F5       | 144     | VDD                                                     | S           | -                | -     | -                   | -                       |

Table 10. STM32F413xG/H pin definition (continued)

1. Function availability depends on the chosen device.

NC (Not Connected) pins are not bonded. They must be configured by software to output push-pull and forced to 0 in the output data register to avoid extra power consumption in low power mode. 2.

Compatibility issue on alternate function pin PE4 SAI1\_SD\_A and PE6 SAI1\_FS\_A: Pins have been swapped versus other 3. MCUs supporting those alternate SAI functions on those pins

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

These I/Os must not be used as a current source (e.g. to drive an LED).

Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F413xG/Hreference manual.

6. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

Incompatibility issue on alternate function with other MCUs supporting UART4: UART4\_TX wrongly mapped to PD10 instead of PC10

|      | FSMC                   |                  |         |         |          |          |  |  |  |  |  |

|------|------------------------|------------------|---------|---------|----------|----------|--|--|--|--|--|

| Pins | LCD/NOR/<br>PSRAM/SRAM | NOR/PSRAM<br>Mux | 64 pins | 81 pins | 100 pins | 144 pins |  |  |  |  |  |

| PE2  | A23                    | A23              | -       | -       | Yes      | Yes      |  |  |  |  |  |

| PE3  | A19                    | A19              | -       | -       | Yes      | Yes      |  |  |  |  |  |

| PE4  | A20                    | A20              | -       | -       | Yes      | Yes      |  |  |  |  |  |

| PE5  | A21                    | A21              | -       | -       | Yes      | Yes      |  |  |  |  |  |

| PE6  | A22                    | A22              | -       | -       | Yes      | Yes      |  |  |  |  |  |

| PF0  | A0                     | -                | -       | -       | -        | Yes      |  |  |  |  |  |

| PF1  | A1                     | -                | -       | -       | -        | Yes      |  |  |  |  |  |

| PF2  | A2                     | -                | -       | -       | -        | Yes      |  |  |  |  |  |

| PF3  | A3                     | -                | -       | -       | -        | Yes      |  |  |  |  |  |

| PF4  | A4                     | -                | -       | -       | -        | Yes      |  |  |  |  |  |

| PF5  | A5                     | -                | -       | -       | -        | Yes      |  |  |  |  |  |

| PC2  | NWE                    | NWE              | Yes     | Yes     | Yes      | Yes      |  |  |  |  |  |

| PC3  | A0                     | -                | Yes     | Yes     | Yes      | Yes      |  |  |  |  |  |

| PA2  | D4                     | DA4              | Yes     | Yes     | Yes      | Yes      |  |  |  |  |  |

| Table | 11. | FSMC | pin | definition |

|-------|-----|------|-----|------------|

|-------|-----|------|-----|------------|

STM32F413xG/H

Pinouts and pin description

| Table 12. STM32F413xG/H alternate functions ( | continued) |

|-----------------------------------------------|------------|

|-----------------------------------------------|------------|

|          |            |                   |          | -                       | Table 12             | 2. STM32F                                           | 413xG/H                                                          | alternate                                                      | function                                 | is (continu                                                  | ued)                                                        |                                               |            |      |      |              |

|----------|------------|-------------------|----------|-------------------------|----------------------|-----------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|------------|------|------|--------------|

|          | AF0        | AF1               | AF2      | AF3                     | AF4                  | AF5                                                 | AF6                                                              | AF7                                                            | AF8                                      | AF9                                                          | AF10                                                        | AF11                                          | AF12       | AF13 | AF14 | AF15         |

| Port     | SYS_<br>AF | TIM1/2/<br>LPTIM1 | TIM3/4/5 | DFSDM2/<br>TIM8/9/10/11 | I2C1/2/3/<br>I2CFMP1 | SPI1/I2S1/<br>SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/I2S4 | SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/I2S4/<br>SPI5/I2S5/<br>DFSDM1/2 | SPI3/I2S3/<br>SAI1/<br>DFSDM2/<br>USART1/<br>USART2/<br>USART3 | DFSDM1/<br>USART3/4/<br>5/6/7/8/<br>CAN1 | I2C2/I2C3/<br>I2CFMP1/<br>CAN1/2/<br>TIM12/13/14/<br>QUADSPI | SAI1/<br>DFSDM1/<br>DFSDM2/<br>QUADSPI/<br>FSMC<br>/OTG1_FS | UART4/<br>UART5/<br>UART9/<br>UART10<br>/CAN3 | FSMC /SDIO | -    | RNG  | SYS_<br>AF   |

| 두<br>PHC | -          | -                 | -        | -                       | -                    | -                                                   | -                                                                | -                                                              | -                                        | -                                                            | -                                                           | -                                             | -          | -    | -    | EVENT<br>OUT |

| ₽<br>PH1 | -          | -                 | -        | -                       | -                    | -                                                   | -                                                                | -                                                              | -                                        | -                                                            | -                                                           | -                                             | -          | -    | -    | EVENT<br>OUT |

74/208

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3 \sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2 \sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 6.1.4 Loading capacitor

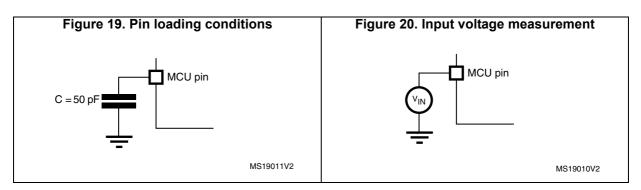

The loading conditions used for pin parameter measurement are shown in *Figure 19*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 20.

| (               |                | tor enabled with prefeto                       | iii) i uiiii               | -                         |                           | -                         |                            | 1.7 V                      | 1    |

|-----------------|----------------|------------------------------------------------|----------------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

|                 |                |                                                | f                          | Тур                       |                           | Ma                        | x <sup>(1)</sup>           |                            |      |

| Symbol          | Parameter      | Conditions                                     | f <sub>HCLK</sub><br>(MHz) | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                |                                                | 100                        | 42.9                      | 45.86                     | 45.76                     | 47.88                      | 51.71                      |      |

|                 |                |                                                | 84                         | 35.4                      | 37.90                     | 38.16                     | 40.01                      | 43.26                      |      |

|                 |                | External clock,                                | 64                         | 26.2                      | 28.19                     | 28.74                     | 30.37                      | 33.54                      |      |

|                 |                | PLL ON, all peripherals enabled <sup>(2)</sup> | 50                         | 20.7                      | 22.32                     | 22.50                     | 24.34                      | 27.73                      |      |

|                 |                |                                                | 25                         | 11.1                      | 11.87                     | 12.87                     | 14.72                      | 18.08                      |      |

|                 |                |                                                | 20                         | 9.4                       | 10.05                     | 11.26                     | 13.16                      | 16.46                      |      |

|                 |                | HSI, PLL OFF,<br>all peripherals enabled       | 16                         | 7.1                       | 7.72                      | 9.06                      | 10.90                      | 14.29                      |      |

|                 | Supply current |                                                | 1                          | 1.2                       | 1.84                      | 3.10                      | 4.84                       | 8.20                       | mA   |

| I <sub>DD</sub> | in Run mode    |                                                | 100                        | 25.4                      | 27.83                     | 27.84                     | 29.93                      | 33.66                      |      |

|                 |                |                                                | 84                         | 21.4                      | 23.44                     | 24.10                     | 25.77                      | 29.04                      |      |

|                 |                | External clock,<br>PLL ON <sup>(2)</sup>       | 64                         | 16.6                      | 18.31                     | 19.17                     | 20.72                      | 23.86                      |      |

|                 |                | all peripherals disabled                       | 50                         | 13.2                      | 15.10                     | 14.95                     | 16.71                      | 20.13                      |      |

|                 |                |                                                | 25                         | 7.2                       | 7.90                      | 9.01                      | 10.88                      | 14.25                      |      |

|                 |                |                                                | 20                         | 6.2                       | 6.83                      | 8.05                      | 9.88                       | 13.15                      | 1    |

|                 |                | HSI, PLL OFF,                                  | 16                         | 4.8                       | 5.37                      | 6.70                      | 8.52                       | 11.89                      |      |

|                 |                | all peripherals disabled                       | 1                          | 1.0                       | 1.62                      | 2.96                      | 4.67                       | 8.07                       |      |

# Table 30. Typical and maximum current consumption in run mode, code with data processing (ART accelerator enabled with prefetch) running from Flash memory - $V_{DD}$ = 1.7 V

1. Guaranteed by characterization results.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

The characteristics given in *Table 41* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 17*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                | Тур | Max             | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|-----|-----------------|------|

| f <sub>HSE_ext</sub>                       | External user clock source frequency <sup>(1)</sup> |                                  | 1                  | -   | 50              | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                  | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub> | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  |                                  | $V_{SS}$           | -   | $0.3V_{DD}$     | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5                  | -   | -               | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -                  | -   | 10              | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             |                                  | -                  | 5   | -               | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          |                                  | 45                 | -   | 55              | %    |

| ١L                                         | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -   | ±1              | μA   |

1. Guaranteed by design.

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 59*. However, the recommended clock input waveform is shown in *Figure 28*.

The characteristics given in *Table 42* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 17*.

| Symbol                                     | Parameter                                              | Conditions                     | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|--------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   |                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                | 450                | -      | -                  | ns   |

| $t_{r(LSE)} \\ t_{f(LSE)}$                 | OSC32_IN rise or fall time <sup>(1)</sup>              |                                | -                  | -      | 50                 | 113  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              |                                | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             |                                | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \le V_{IN} \le V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 42. Low-speed external user clock characteristics

1. Guaranteed by design.

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC code, is running. This emission test is compliant with IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol              | mbol Parameter Conditions |                                                                                                                   | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ]<br>8/100 MHz | Unit |

|---------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------|------|

| S <sub>EMI</sub> Pe |                           |                                                                                                                   | 0.1 to 30 MHz               | 13                                                            |      |

|                     |                           | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = 25 °C, LQFP144                                                          | 30 to 130 MHz               | 21                                                            | dBµV |

|                     | Peak level                | package, conforming to IEC 61967-2,<br>EEMBC, ART ON, all peripheral clocks<br>enabled, clock dithering disabled. | 130 MHz to 1 GHz            | 25                                                            | υσμν |

|                     |                           |                                                                                                                   | 1 GHz to 2 GHz              | 19                                                            |      |

|                     |                           |                                                                                                                   | EMI Level                   | 4                                                             | -    |

#### Table 55. EMI characteristics for LQFP144

# 6.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

#### SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 67* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                       | Parameter Conditions  |                                                                                    | Min                 | Тур               | Max                  | Unit |

|----------------------------------------------|-----------------------|------------------------------------------------------------------------------------|---------------------|-------------------|----------------------|------|

|                                              |                       | Master mode,<br>SPI1,4,5<br>3.0 V < V <sub>DD</sub> < 3.6 V                        | -                   | -                 | 50                   |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    |                       | Master mode,<br>SPI1,4,5<br>2.7 V < V <sub>DD</sub> < 3.6 V                        | -                   | -                 | 42                   |      |

|                                              |                       | Master mode<br>SPI1,4,5<br>1.7 V < V <sub>DD</sub> < 3.6 V                         | -                   | -                 | 25                   |      |

|                                              | SPI clock frequency   | Master transmitter mode<br>SPI1,4,5<br>1.71 V < V <sub>DD</sub> < 3.6 V            | -                   | -                 | 50                   | MHz  |

|                                              |                       | Slave receiver mode<br>SPI1,4,5<br>1.71 V < V <sub>DD</sub> < 3.6 V                | -                   | -                 | - 50                 |      |

|                                              |                       | Slave mode transmitter/full duplex<br>SPI1,4,5<br>2.7 V < V <sub>DD</sub> < 3.6 V  |                     | -                 | 40 <sup>(2)</sup>    |      |

|                                              |                       | Slave mode transmitter/full duplex<br>SPI1,4,5<br>1.71 V < V <sub>DD</sub> < 3.6 V | -                   | -                 | 26                   |      |

|                                              |                       | Master & Slave mode,<br>SPI2/3<br>1.71 V < V <sub>DD</sub> < 3.6 V                 | -                   | -                 | 25                   |      |

| t <sub>su(NSS)</sub>                         | NSS setup time        | Slave mode, SPI presc = 2                                                          | 4*T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>h(NSS)</sub>                          | NSS hold time         | Slave mode, SPI presc = 2                                                          | 2*T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time | v time Master mode                                                                 |                     | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2 | ns   |

| t <sub>su(MI)</sub>                          | Data input setup time | Master mode                                                                        | 2.5                 | -                 | -                    | ns   |

| t <sub>su(SI)</sub>                          |                       | Slave mode                                                                         | 4.5                 | -                 | -                    | 115  |

| t <sub>h(MI)</sub>                           | Data input hold time  | Master mode                                                                        | 5                   | -                 | -                    | ns   |

| t <sub>h(SI)</sub>                           |                       | Slave mode                                                                         | 2                   | -                 | -                    |      |

| Table 67. SPI dynamic characteristics | Table 67. | SPI d | vnamic | characteristics <sup>(1</sup> | ) |

|---------------------------------------|-----------|-------|--------|-------------------------------|---|

|---------------------------------------|-----------|-------|--------|-------------------------------|---|

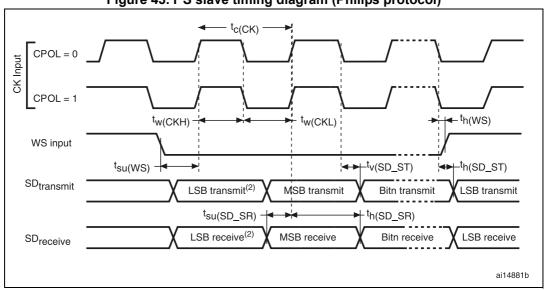

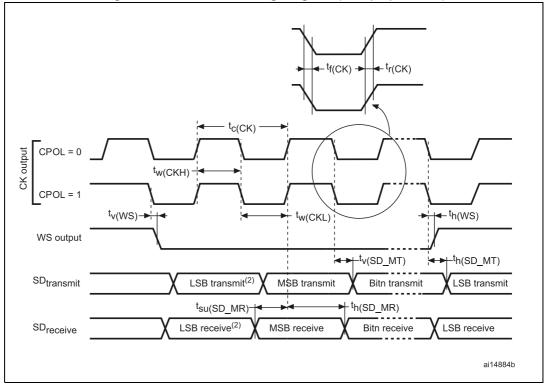

Figure 43. I<sup>2</sup>S slave timing diagram (Philips protocol)

LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Figure 44. I<sup>2</sup>S master timing diagram (Philips protocol)

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

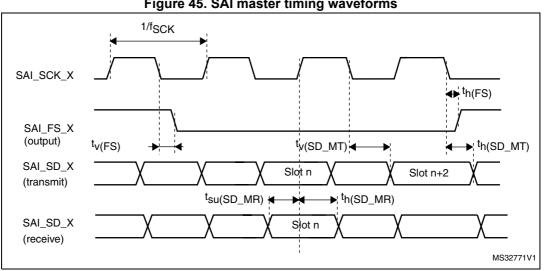

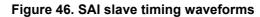

Figure 45. SAI master timing waveforms

- 1. C<sub>L</sub> = 30 pF.

- 2. Based on characterization.

# Table 91. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings^{(1)(2)}

| Symbol                    | ol Parameter                                                  |                             | Мах                         | Unit |

|---------------------------|---------------------------------------------------------------|-----------------------------|-----------------------------|------|

| t <sub>w(NE)</sub>        | t <sub>w(NE)</sub> FSMC_NE low time 8 * t <sub>HCLK</sub> - 1 |                             | 8 * t <sub>HCLK</sub> + 1   |      |

| t <sub>w(NWE)</sub>       | FSMC_NWE low time                                             | 6 * t <sub>HCLK</sub> - 1.5 | 6 * t <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FSMC_NWAIT valid before FSMC_NEx high                         | 6 * t <sub>HCLK</sub> - 1   | -                           | 115  |

| t <sub>h(NE_NWAIT)</sub>  | FSMC_NEx hold time after FSMC_NWAIT invalid                   | 4 * t <sub>HCLK</sub> + 2   | -                           |      |

1. C<sub>L</sub> = 30 pF.

2. Based on characterization.

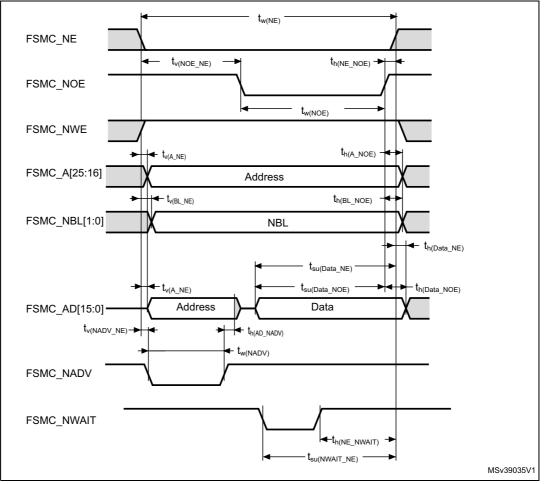

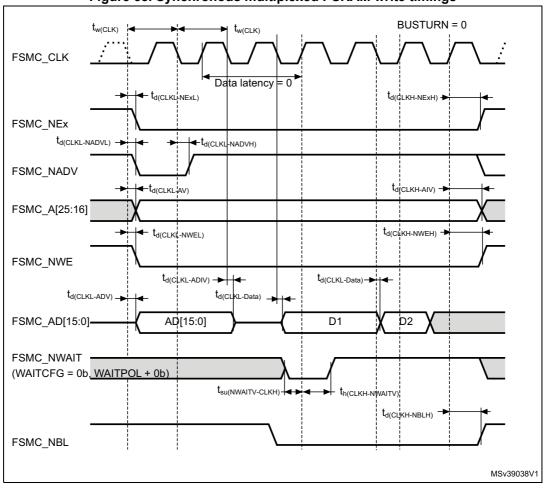

## Figure 55. Asynchronous multiplexed PSRAM/NOR read waveforms

| Symbol                                                 | Parameter                             | Conditions  | Min    | Тур  | Max  | Unit |  |  |

|--------------------------------------------------------|---------------------------------------|-------------|--------|------|------|------|--|--|

| f <sub>PP</sub>                                        | Clock frequency in data transfer mode | -           | 0      | -    | 50   | MHz  |  |  |

| -                                                      | SDIO_CK/fPCLK2 frequency ratio        | -           | -      | -    | 8/3  | -    |  |  |

| t <sub>W(CKL)</sub>                                    | Clock low time                        | fpp =50MHz  | 9.5    | 10.5 | -    |      |  |  |

| t <sub>W(CKH)</sub>                                    | Clock high time                       | fpp =50MHz  | 8.5    | 9.5  | -    | ns   |  |  |

| CMD, D inputs (referenced to CK) in MMC and SD HS mode |                                       |             |        |      |      |      |  |  |

| t <sub>ISU</sub>                                       | Input setup time HS                   | fpp =50MHz  | 5      | -    | -    |      |  |  |

| t <sub>IH</sub>                                        | Input hold time HS                    | fpp =50MHz  | 1      | -    | -    | – ns |  |  |

| CMD, D out                                             | tputs (referenced to CK) in MMC and S | SD HS mode  |        | •    | •    |      |  |  |

| t <sub>OV</sub>                                        | Output valid time HS                  | fpp =50MHz  | -      | 12   | 13.5 |      |  |  |

| t <sub>OH</sub>                                        | Output hold time HS                   | fpp =50MHz  | 10.5   | -    | -    | ns   |  |  |

| CMD, D inputs (referenced to CK) in SD default mode    |                                       |             |        |      |      |      |  |  |

| t <sub>ISUD</sub>                                      | Input setup time SD                   | fpp =25MHz  | 5      | -    | -    |      |  |  |

| t <sub>IHD</sub>                                       | Input hold time SD                    | fpp =25MHz  | 1      | -    | -    | ns   |  |  |

| CMD, D outputs (referenced to CK) in SD default mode   |                                       |             |        |      |      |      |  |  |

| t <sub>OVD</sub>                                       | Output valid default time SD          | fpp =25 MHz | -      | 2    | 3    |      |  |  |

| t <sub>OHD</sub>                                       | Output hold default time SD           | fpp =25 MHz | 1      | -    | -    | ns   |  |  |

| t <sub>OVD</sub>                                       | Output valid default time SD          | fpp =25 MHz | -<br>1 | 2    | 3    |      |  |  |

| Table 100 | . SD / | MMC | characteristics <sup>(1)(2)</sup> |

|-----------|--------|-----|-----------------------------------|

|-----------|--------|-----|-----------------------------------|

1. Guaranteed by characterization results.

2. V<sub>DD</sub> = 2.7 to 3.6 V.

# Table 101. eMMC characteristics $V_{DD}$ = 1.7 V to 1.9 V<sup>(1)(2)</sup>

| Symbol                                         | Parameter                             | Conditions | Min | Тур  | Max  | Unit       |  |

|------------------------------------------------|---------------------------------------|------------|-----|------|------|------------|--|

| f <sub>PP</sub>                                | Clock frequency in data transfer mode | -          | 0   | -    | 50   | MHz        |  |

| -                                              | SDIO_CK/fPCLK2 frequency ratio        | -          | -   | -    | 8/3  | -          |  |

| t <sub>W(CKL)</sub>                            | Clock low time                        | fpp =50MHz | 9.5 | 10.5 | -    | ne         |  |

| t <sub>W(CKH)</sub>                            | Clock high time                       | fpp =50MHz | 8.5 | 9.5  | -    | ns         |  |

| CMD, D inputs (referenced to CK) in eMMC mode  |                                       |            |     |      |      |            |  |

| t <sub>ISU</sub>                               | Input setup time HS                   | fpp =50MHz | 3   | -    | -    | <b>n</b> 0 |  |

| t <sub>IH</sub>                                | Input hold time HS                    | fpp =50MHz | 2.5 | -    | -    | ns         |  |

| CMD, D outputs (referenced to CK) in eMMC mode |                                       |            |     |      |      |            |  |

| t <sub>OV</sub>                                | Output valid time HS                  | fpp =50MHz | -   | 15   | 15.5 | 50         |  |

| t <sub>OH</sub>                                | Output hold time HS                   | fpp =50MHz | 13  | -    | -    | ns         |  |

1. Guaranteed by characterization results.

2. C<sub>LOAD</sub> = 20 pF.

| puoliago moonamour auta |       |             |       |        |                       |        |  |

|-------------------------|-------|-------------|-------|--------|-----------------------|--------|--|

| Cumb al                 |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

| Symbol                  | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |  |

| А                       | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |  |

| A1                      | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |  |

| D                       | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |  |

| E                       | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |  |

| D2                      | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| E2                      | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| L                       | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |  |

| Т                       | -     | 0.152       | -     | -      | 0.0060                | -      |  |

| b                       | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118 |  |

| е                       | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| ddd                     | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

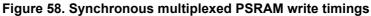

# Table 105. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### Figure 67. UFQFPN48 recommended footprint

1. Dimensions are in millimeters.

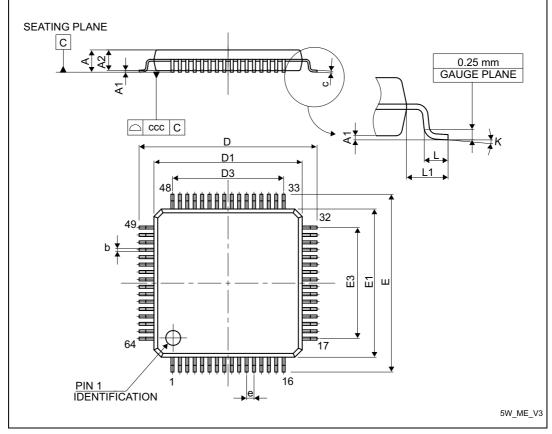

# 7.3 LQFP64 package information

Figure 69. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.