Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                         |

|----------------------------|------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Speed                      | 100MHz                                                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SDIO, QSPI, SAI, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                              |

| Number of I/O              | 50                                                                                             |

| Program Memory Size        | 1MB (1M x 8)                                                                                   |

| Program Memory Type        | FLASH                                                                                          |

| EEPROM Size                | -                                                                                              |

| RAM Size                   | 320K x 8                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                    |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                          |

| Oscillator Type            | Internal                                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                              |

| Mounting Type              | Surface Mount                                                                                  |

| Package / Case             | 64-LQFP                                                                                        |

| Supplier Device Package    | 64-LQFP (10x10)                                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f413rgt6tr                        |

|                            |                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.7 Embedded SRAM

All devices embed 320 Kbytes of system SRAM which can be accessed (read/write) at CPU clock speed with 0 wait states.

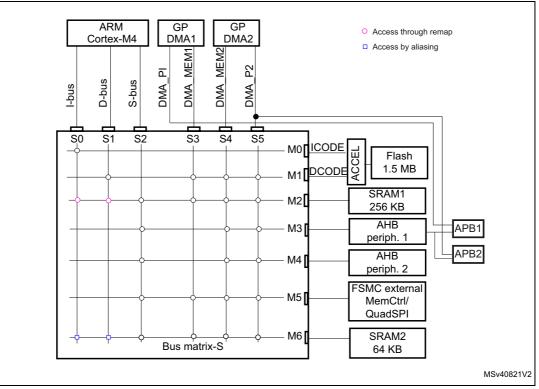

## 3.8 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs) and the slaves (Flash memory, RAM, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

Figure 5. Multi-AHB matrix

CPU can access SRAM1 memory via S-bus, when SRAM1 is mapped at the address range: 0x2000 0000 to 0x2003 FFFF.

CPU can access SRAM2 memory via S-bus, when SRAM2 is mapped at the address range: 0x2004 0000 to 0x2004 FFFF.

CPU can access SRAM1 memory via I-bus and D-bus, when SRAM1 is remapped at address 0x0000 0000 either by booting from RAM memory or by the remap mode.

CPU can access SRAM2 memory via I-bus and D-bus, when SRAM2 is mapped at the address range: 0x1000 0000 to 0x1000 FFFF.

Performance boosts up, when the CPU access SRAM memory via the I-bus.

buses and high-speed APB domains is 100 MHz. The maximum allowed frequency of the low-speed APB domain is 50 MHz.

The devices embed a dedicated PLL (PLLI2S) which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

## 3.15 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash memory

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using one of the interface listed in the *Table 3* or the USB OTG FS in device mode through DFU (device firmware upgrade).

| Package  | USART1<br>PA9/<br>PA10 | USART2<br>PD6/<br>PD5 | USART3<br>PB11/<br>PB10 | I2C1<br>PB6/<br>PB7 | I2C2<br>PF0/<br>PF1 | 12C3<br>PA8/<br>PB4 | I2C<br>FMP1<br>PB14/<br>PB15 | SPI1<br>PA4/<br>PA5/<br>PA6/<br>PA7 | SPI3<br>PA15/<br>PC10/<br>PC11/<br>PC12 | SPI4<br>PE11/<br>PE12/<br>PE13/<br>PE14 | CAN2<br>PB5/<br>PB13 | USB<br>PA11<br>/P12 |

|----------|------------------------|-----------------------|-------------------------|---------------------|---------------------|---------------------|------------------------------|-------------------------------------|-----------------------------------------|-----------------------------------------|----------------------|---------------------|

| UFQFPN48 | Y                      | -                     | -                       | Y                   | -                   | Y                   | Y                            | Y                                   | -                                       | -                                       | Y                    | Y                   |

| LQFP64   | Y                      | -                     | -                       | Y                   | -                   | Y                   | Y                            | Y                                   | Y                                       | -                                       | Y                    | Y                   |

| WLCSP81  | Y                      | -                     | -                       | Y                   | -                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

| LQFP100  | Y                      | Y                     | -                       | Y                   | -                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

| LQFP144  | Y                      | Y                     | Y                       | Y                   | Y                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

| UFBGA100 | Y                      | Y                     | Y                       | Y                   | -                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

| UFBGA144 | Y                      | Y                     | Y                       | Y                   | Y                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

For more detailed information on the bootloader, refer to Application Note: AN2606, *STM32™ microcontroller system memory boot mode*.

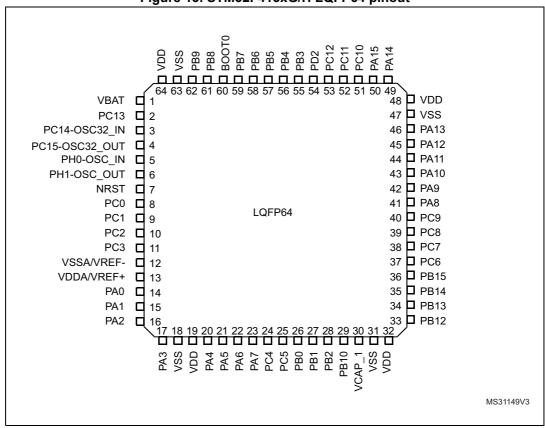

Figure 13. STM32F413xG/H LQFP64 pinout

1. The above figure shows the package top view.

|          |        | Ρ       | in Nu   | mber     |          |         |                                                         |                                 |     |                     |                                                                                                                                             |   |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|---------------------------------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|

| UFQFPN48 | LQFP64 | WLCSP81 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin I/O<br>type structure Notes |     | Alternate functions | Additional<br>functions                                                                                                                     |   |

| -        | -      | NC      | 62      | H10      | K12      | 86      | PD15                                                    | I/O                             | FTf | (2)                 | TIM4_CH4,<br>I2CFMP1_SDA,<br>DFSDM2_DATIN0,<br>UART9_TX,<br>FSMC_D1/FSMC_DA1,<br>EVENTOUT                                                   | - |

| -        | -      | -       | -       | -        | J12      | 87      | PG2 I/O FT - FSMC_A12,<br>EVENTOUT                      |                                 | -   |                     |                                                                                                                                             |   |

| -        | -      | -       | -       | -        | J11      | 88      | PG3 I/O FT - FSMC_A13,<br>EVENTOUT                      |                                 | -   |                     |                                                                                                                                             |   |

| -        | -      | -       | -       | -        | J10      | 89      | PG4                                                     | I/O                             | FT  | -                   | FSMC_A14,<br>EVENTOUT                                                                                                                       | - |

| -        | -      | -       | -       | -        | H12      | 90      | PG5                                                     | I/O                             | FT  | -                   | FSMC_A15,<br>EVENTOUT                                                                                                                       | - |

| -        | -      | -       | -       | -        | H11      | 91      | PG6                                                     | I/O                             | FT  | -                   | QUADSPI_BK1_NCS,<br>EVENTOUT                                                                                                                | - |

| -        | -      | -       | -       | -        | H10      | 92      | PG7 I/O FT - USART6_CK,<br>EVENTOUT                     |                                 | -   |                     |                                                                                                                                             |   |

| -        | -      | -       | -       | -        | G11      | 93      | PG8                                                     | I/O                             | FT  | -                   | USART6_RTS,<br>EVENTOUT                                                                                                                     | - |

| -        | -      | -       | -       | -        | -        | 94      | VSS                                                     | S                               | -   | -                   | -                                                                                                                                           | - |

| -        | -      | -       | -       | -        | F10      | -       | VDD                                                     | S                               | -   | -                   | -                                                                                                                                           | - |

| -        | -      | F1      | -       | -        | C11      | 95      | VDDUSB                                                  | S                               | -   | -                   | -                                                                                                                                           | - |

| -        | 37     | D5      | 63      | E12      | G12      | 96      | PC6                                                     | I/O                             | FTf | -                   | TIM3_CH1, TIM8_CH1,<br>I2CFMP1_SCL,<br>I2S2_MCK,<br>DFSDM1_CKIN3,<br>DFSDM2_DATIN6,<br>USART6_TX,<br>FSMC_D1/FSMC_DA1,<br>SDIO_D6, EVENTOUT | - |

| -        | 38     | D4      | 64      | E11      | F12      | 97      | PC7                                                     | I/O                             | FTf | -                   | TIM3_CH2, TIM8_CH2,<br>I2CFMP1_SDA,<br>SPI2_SCK/I2S2_CK,<br>I2S3_MCK,<br>DFSDM2_CKIN6,<br>USART6_RX,<br>DFSDM1_DATIN3,<br>SDIO_D7, EVENTOUT | - |

Table 10. STM32F413xG/H pin definition (continued)

| Bus  | Boundary address          | Peripheral |

|------|---------------------------|------------|

|      | 0x4001 6800- 0x4001 FFFF  | Reserved   |

|      | 0x4001 6400 - 0x4001 67FF | DFSDM2     |

|      | 0x4001 6000 - 0x4001 63FF | DFSDM1     |

|      | 0x4001 5C00 - 0x4001 5FFF | Reserved   |

|      | 0x4001 5800 - 0x4001 5BFF | SAI1       |

|      | 0x4001 5400 - 0x4001 57FF | Reserved   |

|      | 0x4001 5000 - 0x4001 53FF | SPI5/I2S5  |

|      | 0x4001 4C00 - 0x4001 4FFF | Reserved   |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11      |

|      | 0x4001 4400 - 0x4001 47FF | TIM10      |

|      | 0x4001 4000 - 0x4001 43FF | ТІМ9       |

|      | 0x4001 3C00 - 0x4001 3FFF | EXTI       |

| APB2 | 0x4001 3800 - 0x4001 3BFF | SYSCFG     |

|      | 0x4001 3400 - 0x4001 37FF | SPI4/I2S4  |

|      | 0x4001 3000 - 0x4001 33FF | SPI1/I2S1  |

|      | 0x4001 2C00 - 0x4001 2FFF | SDIO       |

|      | 0x4001 2400 - 0x4001 2BFF | Reserved   |

|      | 0x4001 2000 - 0x4001 23FF | ADC1/2/3   |

|      | 0x4001 1C00 - 0x4001 1FFF | UART10     |

|      | 0x4001 1800 - 0x4001 1BFF | UART9      |

|      | 0x4001 1400 - 0x4001 17FF | USART6     |

|      | 0x4001 1000 - 0x4001 13FF | USART1     |

|      | 0x4001 0800 - 0x4001 0FFF | Reserved   |

|      | 0x4001 0400 - 0x4001 07FF | ТІМ8       |

|      | 0x4001 0000 - 0x4001 03FF | TIM1       |

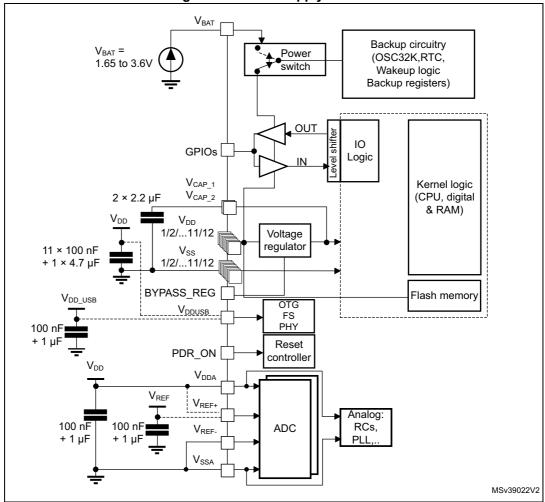

### 6.1.6 Power supply scheme

Figure 21. Power supply scheme

- 1. To connect PDR\_ON pin, refer to Section: Power supply supervisor.

- 2. The 4.7  $\mu F$  ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

- 3. VCAP\_2 pad is only available on 100-pin and 144-pin packages.

- 4.  $V_{DDA}=V_{DD}$  and  $V_{SSA}=V_{SS}$ .

- V<sub>DDUSB</sub> is a dedicated independent USB power supply for the on-chip full-speed OTG PHY module and associated DP/DM GPIOs. V<sub>DDUSB</sub> value does not depend on the V<sub>DD</sub> and V<sub>DDA</sub> values, but it must be the last supply to be provided and the first to disappear.

- **Caution:** Each power supply pair (for example V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub>) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure good operation of the device. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect operation of the device.

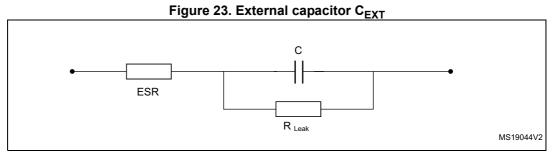

## 6.3.2 VCAP\_1/VCAP\_2 external capacitors

Stabilization for the main regulator is achieved by connecting the external capacitor  $C_{EXT}$  to the VCAP\_1 and VCAP\_2 pins. For packages supporting only 1 VCAP pin, the 2 CEXT capacitors are replaced by a single capacitor.

C<sub>EXT</sub> is specified in *Table 19*.

1. Legend: ESR is the equivalent series resistance.

#### Table 19. VCAP\_1/VCAP\_2 operating conditions<sup>(1)</sup>

| Symbol | Parameter                                                                      | Conditions |

|--------|--------------------------------------------------------------------------------|------------|

| CEXT   | Capacitance of external capacitor with the pins<br>VCAP_1 and VCAP_2 available | 2.2 µF     |

| ESR    | ESR of external capacitor with the pins VCAP_1 and VCAP_2 available            | < 2 Ω      |

| CEXT   | Capacitance of external capacitor with a single VCAP pin available             | 4.7 µF     |

| ESR    | ESR of external capacitor with a single VCAP pin available                     | < 1 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu F$  V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

## 6.3.3 Operating conditions at power-up/power-down (regulator ON)

Subject to general operating conditions for T<sub>A</sub>.

#### Table 20. Operating conditions at power-up / power-down (regulator ON)

| Symbol           | Parameter                      | Min | Мах | Unit  |

|------------------|--------------------------------|-----|-----|-------|

| t <sub>VDD</sub> | V <sub>DD</sub> rise time rate | 20  | ~   | µs/V  |

|                  | V <sub>DD</sub> fall time rate | 20  | ~   | μ5/ ν |

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

|                 |                        |                                                                          | /                 | -                         |                           |                           | (1)                        |                            |      |

|-----------------|------------------------|--------------------------------------------------------------------------|-------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

|                 |                        |                                                                          | f <sub>HCLK</sub> | Тур                       | Max <sup>(1)</sup>        |                           |                            |                            |      |

| Symbol          | Parameter              | Conditions                                                               | (MHz)             | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>85 °С | Т <sub>А</sub> =<br>105 °С | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                        |                                                                          | 100               | 33.3                      | 35.32 <sup>(3)</sup>      | 35.65                     | 37.65                      | 41.26 <sup>(3)</sup>       |      |

|                 |                        |                                                                          | 84                | 26.8                      | 28.45 <sup>(3)</sup>      | 28.97                     | 30.82                      | 34.39 <sup>(3)</sup>       |      |

|                 |                        | External clock,<br>PLL ON,                                               | 64                | 18.6                      | 19.74 <sup>(3)</sup>      | 20.35                     | 22.11                      | 25.35 <sup>(3)</sup>       |      |

|                 |                        | all peripherals enabled <sup>(2)</sup>                                   | 50                | 14.6                      | 15.57                     | 16.41                     | 18.21                      | 21.46                      |      |

|                 |                        |                                                                          | 25                | 7.8                       | 8.37                      | 9.64                      | 11.32                      | 14.68                      |      |

|                 |                        |                                                                          | 20                | 6.7                       | 7.25                      | 8.40                      | 10.25                      | 13.45                      |      |

|                 |                        | HSI, PLL OFF <sup>(4)</sup> , all peripherals enabled <sup>(2)</sup>     | 16                | 4.6                       | 4.96                      | 6.39                      | 8.20                       | 11.54                      |      |

|                 | Supply                 |                                                                          | 1                 | 0.8                       | 0.86                      | 2.51                      | 4.34                       | 7.65                       |      |

| I <sub>DD</sub> | current in<br>Run mode |                                                                          | 100               | 15.7                      | 16.74 <sup>(3)</sup>      | 17.62                     | 19.50                      | 23.16 <sup>(3)</sup>       | mA   |

|                 |                        | External algoly                                                          | 84                | 12.7                      | 13.57 <sup>(3)</sup>      | 14.60                     | 16.38                      | 19.98 <sup>(3)</sup>       |      |

|                 |                        | External clock,<br>PLL ON,<br>all peripherals<br>disabled <sup>(2)</sup> | 64                | 9.0                       | 9.62 <sup>(3)</sup>       | 10.60                     | 12.37                      | 15.58 <sup>(3)</sup>       |      |

|                 |                        |                                                                          | 50                | 7.1                       | 7.69                      | 8.79                      | 10.63                      | 13.79                      |      |

|                 |                        |                                                                          | 25                | 4.0                       | 4.52                      | 5.68                      | 7.44                       | 10.68                      |      |

|                 |                        |                                                                          | 20                | 3.4                       | 4.03                      | 5.23                      | 6.90                       | 10.27                      |      |

|                 |                        | HSI, PLL OFF,                                                            | 16                | 2.3                       | 2.44                      | 4.00                      | 5.81                       | 9.13                       |      |

|                 |                        | all peripherals<br>disabled <sup>(2)</sup>                               | 1                 | 0.6                       | 0.70                      | 2.35                      | 4.18                       | 7.49                       |      |

## Table 24. Typical and maximum current consumption, code with data processing (ARTaccelerator disabled) running from SRAM - V<sub>DD</sub> = 3.6 V

1. Guaranteed by characterization results.

2. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

3. Tested in production

4. When analog peripheral blocks such as ADC, HSE, LSE, HSI, or LSI are ON, an additional power consumption has to be considered

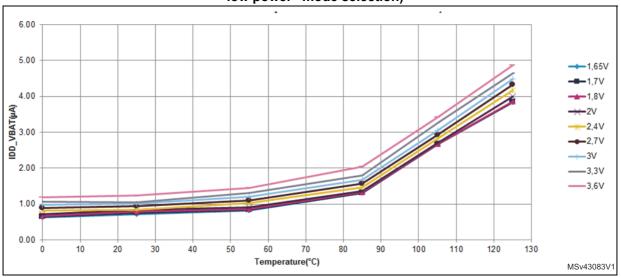

Figure 24. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/LSE oscillator "low power" mode selection)

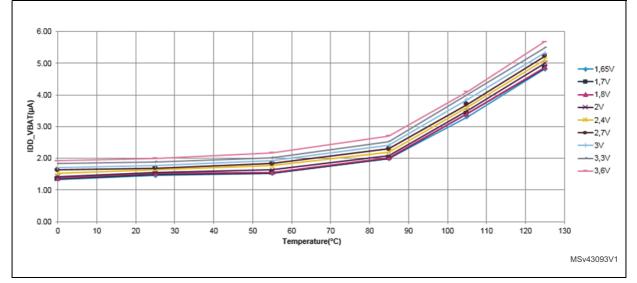

Figure 25. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/LSE oscillator "high drive" mode selection)

|      | ible 39. Peripheral cu |         | 11 14   |         |        |

|------|------------------------|---------|---------|---------|--------|

| Peri | pheral                 | Scale 1 | Scale 2 | Scale 3 | – Unit |

|      | AHB-APB1 bridge        | 0.90    | 0.88    | 0.81    |        |

|      | TIM2                   | 13.08   | 12.48   | 11.16   |        |

|      | TIM3                   | 9.98    | 9.50    | 8.50    |        |

|      | TIM4                   | 9.88    | 9.43    | 8.44    |        |

|      | TIM5                   | 13.14   | 12.52   | 11.19   |        |

|      | TIM6                   | 1.94    | 1.86    | 1.66    |        |

|      | TIM7                   | 1.86    | 1.79    | 1.56    |        |

|      | TIM12                  | 5.56    | 5.29    | 4.72    |        |

|      | TIM13                  | 3.44    | 3.29    | 2.94    |        |

|      | TIM14                  | 3.66    | 3.48    | 3.09    |        |

|      | LPTIM1                 | 7.34    | 7.00    | 6.25    |        |

|      | WWDG                   | 0.64    | 0.62    | 0.53    |        |

|      | SPI2/I2S2              | 3.02    | 2.88    | 2.56    |        |

|      | SPI3/I2S3              | 3.06    | 2.90    | 2.59    |        |

| APB1 | USART2                 | 3.30    | 3.14    | 2.81    | µA/MHz |

|      | USART3                 | 3.32    | 3.14    | 2.81    |        |

|      | UART4                  | 3.18    | 3.02    | 2.69    |        |

|      | UART5                  | 3.26    | 3.10    | 2.75    |        |

|      | I2C1                   | 3.20    | 3.05    | 2.72    |        |

|      | I2C2                   | 3.30    | 3.14    | 2.81    |        |

|      | I2C3                   | 3.26    | 3.10    | 2.78    |        |

|      | I2CFMP1                | 5.22    | 4.98    | 4.44    |        |

|      | CAN1                   | 5.58    | 5.31    | 4.75    |        |

|      | CAN2                   | 5.14    | 4.88    | 4.38    | 1      |

|      | CAN3                   | 5.70    | 5.43    | 4.84    | 1      |

|      | PWR                    | 0.90    | 0.86    | 0.75    | 1      |

|      | DAC1                   | 2.14    | 2.05    | 1.81    | 1      |

|      | UART7                  | 3.08    | 2.93    | 2.59    | 1      |

|      | UART8                  | 3.10    | 2.95    | 2.63    | 1      |

Table 39. Peripheral current consumption (continued)

## Low-speed internal (LSI) RC oscillator

| Table 46 | LSI oscillator | characteristics <sup>(1)</sup> |

|----------|----------------|--------------------------------|

|----------|----------------|--------------------------------|

| Symbol                              | Parameter                        | Min  | Тур  | Мах  | Unit |

|-------------------------------------|----------------------------------|------|------|------|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 16.1 | 32.0 | 47.0 | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -    | 15.0 | 40.0 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -    | 0.4  | 0.6  | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

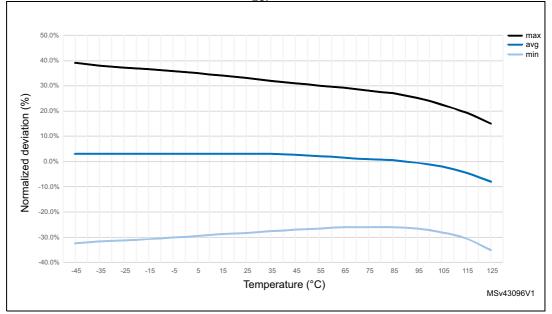

### Figure 32. $ACC_{LSI}$ versus temperature

| Symbol                                  | Parameter                                       | Conditions                                                              |                    | Min                 | Тур  | Max          | Unit |

|-----------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLL_IN</sub>                     | PLL input clock <sup>(1)</sup>                  | -                                                                       |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         |      |

| f <sub>PLLI2SQ_OUT</sub>                | 48 MHz PLLI2SQ<br>multiplier output clock       | -                                                                       |                    | -                   | 48   | 75           | MHz  |

| f <sub>PLLI2SR_OUT</sub>                | PLLI2SR multiplier output clock for I2S and SAI | -                                                                       | -                  |                     | -    | 216          |      |

| f <sub>VCO_OUT</sub>                    | PLLI2S VCO output                               | -                                                                       |                    |                     | -    | 432          |      |

| t                                       | PLLI2S lock time                                | VCO freq = 100 MHz                                                      |                    | 75                  | -    | 200          | μs   |

| t <sub>LOCK</sub>                       |                                                 | VCO freq = 432 MHz                                                      |                    | 100                 | -    | 300          |      |

|                                         |                                                 | Cycle to cycle at<br>12.288 MHz on<br>48 kHz period,<br>N=432, R=5      | RMS                | -                   | 90   | -            |      |

|                                         | Master I2S clock jitter                         |                                                                         | peak<br>to<br>peak | -                   | ±280 | -            |      |

| Jitter <sup>(3)</sup>                   |                                                 | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples |                    | -                   | 90   | -            | ps   |

|                                         | WS I2S clock jitter                             | Cycle to cycle at 48 KHz<br>on 1000 samples                             |                    | -                   | 400  | -            |      |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$            | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{DDA}$           | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 |      |

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

- The USB OTG FS functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V  $\rm V_{DD}$  voltage range. 2.

- 3. Guaranteed by design.

- 4. R<sub>I</sub> is the load connected on the USB OTG FS drivers.

When VBUS sensing feature is enabled, PA9 should be left at their default state (floating Note: input), not as alternate function. A typical 200 µA current consumption of the embedded sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 when the feature is enabled.

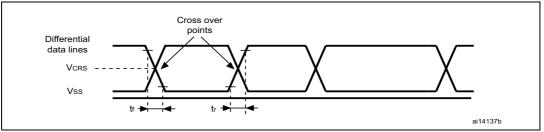

Figure 47. USB OTG FS timings: definition of data signal rise and fall time

#### Table 74. USB OTG FS electrical characteristics<sup>(1)</sup>

| Driver characteristics |                                 |                                |     |     |      |  |

|------------------------|---------------------------------|--------------------------------|-----|-----|------|--|

| Symbol                 | Parameter                       | Conditions                     | Min | Max | Unit |  |

| t <sub>r</sub>         | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |

| t <sub>f</sub>         | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |

| t <sub>rfm</sub>       | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |

| V <sub>CRS</sub>       | Output signal crossover voltage |                                | 1.3 | 2.0 | V    |  |

1. Guaranteed by design.

Measured from 10% to 90% of the data signal. For more detailed informations, refer to USB Specification -2. Chapter 7 (version 2.0).

#### CAN (controller area network) interface

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CANx TX and CANx RX).

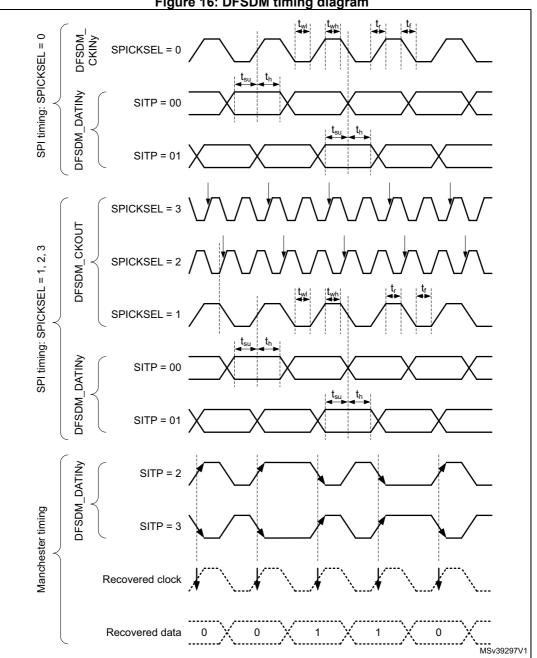

Figure 16: DFSDM timing diagram

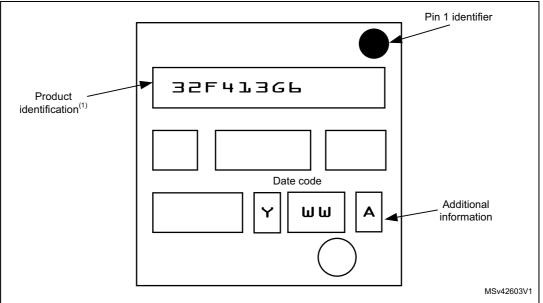

#### **Device marking for WLCSP81**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 65. WLCSP81 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Мах    |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |  |

| k      | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

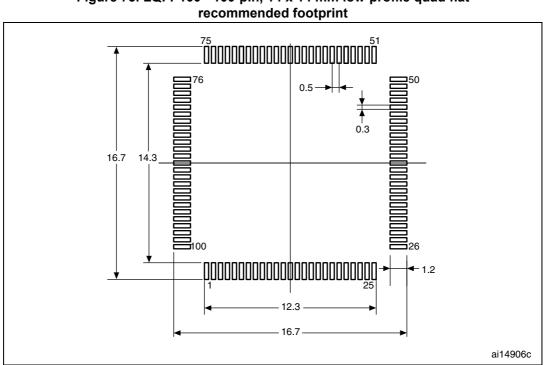

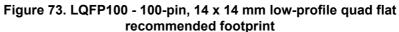

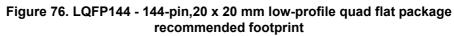

#### Table 107. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

1. Dimensions are expressed in millimeters.

# Table 111. UFBGA144 - 144-ball, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball gridarray package mechanical data (continued)

|        | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| F      | 0.550       | 0.600 | 0.650 | 0.0177                | 0.0197 | 0.0217 |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0039 |  |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |  |

| fff    | -           | -     | 0.080 | -                     | -      | 0.0020 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

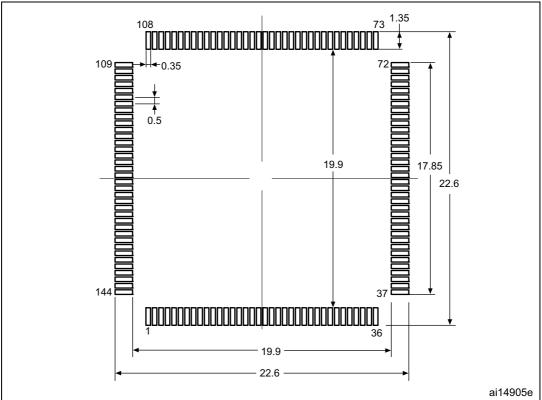

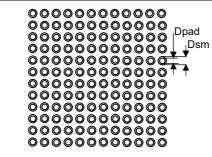

# Figure 82. UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball grid array recommended footprint

A02Y\_FP\_V1

#### Table 112. UFBGA144 recommended PCB design rules (0.80 mm pitch BGA)

| Dimension | Recommended values                                               |  |  |

|-----------|------------------------------------------------------------------|--|--|

| Pitch     | 0.80 mm                                                          |  |  |

| Dpad      | 0.400 mm                                                         |  |  |

| Dsm       | 0.550 mm typ. (depends on the soldermask registration tolerance) |  |  |

Note:

4 to 6 mils solder paste screen printing process. Stencil opening is 0.400 mm. Stencil thickness is between 0.100 mm and 0.125 mm. Pad trace width is 0.120 mm.

Non solder mask defined (NSMD) pads are recommended.

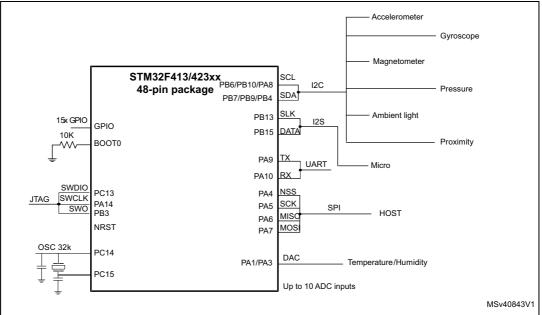

## Appendix B Application block diagrams

## B.1 Sensor Hub application example

#### Figure 84. Sensor Hub application example

## **Revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29-Aug-2016 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21-Oct-2016 | 2        | Updated:<br>– Table 10: STM32F413xG/H pin definition<br>– Section 7: Package information<br>– Figure 65: WLCSP81 marking example (package top<br>view)                                                                                                                                                                                                                                                                                                                                                         |

| 13-Dec-2016 | 3        | <ul> <li>Updated:</li> <li>Table 39: Peripheral current consumption</li> <li>Table 55: EMI characteristics for LQFP144</li> <li>Table 56: ESD absolute maximum ratings</li> <li>Table 70: QSPI dynamic characteristics in SDR mode</li> <li>Table 111: UFBGA144 - 144-ball, 10 x 10 mm,<br/>0.80 mm pitch, ultra fine pitch ball grid array package<br/>mechanical data</li> <li>Figure 81: UFBGA144 - 144-pin, 10 x 10 mm,<br/>0.80 mm pitch, ultra fine pitch ball grid array package<br/>outline</li> </ul> |

| 09-Mar-2017 | 4        | Updated:<br>– Table 2: STM32F413xG/H features and peripheral<br>counts<br>– Table 12: STM32F413xG/H alternate functions<br>Added:<br>– Table 11: FSMC pin definition                                                                                                                                                                                                                                                                                                                                           |