# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                         |

|----------------------------|------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Speed                      | 100MHz                                                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SDIO, QSPI, SAI, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                              |

| Number of I/O              | 81                                                                                             |

| Program Memory Size        | 1MB (1M x 8)                                                                                   |

| Program Memory Type        | FLASH                                                                                          |

| EEPROM Size                | -                                                                                              |

| RAM Size                   | 320K x 8                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                    |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                          |

| Oscillator Type            | Internal                                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                              |

| Mounting Type              | Surface Mount                                                                                  |

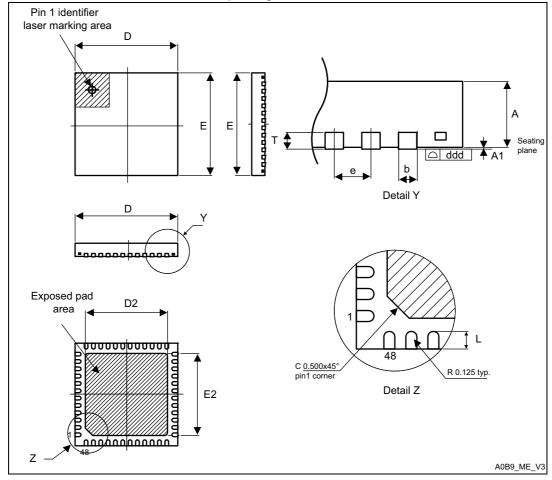

| Package / Case             | 100-LQFP                                                                                       |

| Supplier Device Package    | 100-LQFP (14x14)                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f413vgt6                          |

|                            |                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

The RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the VBAT pin.

#### 3.20 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

To further reduce the power consumption, the Flash memory can be switched off before entering in Sleep mode. Note that this requires a code execution from the RAM.

#### • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm/ wakeup/ tamper/ time stamp events).

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on one of the WKUP pins, or an RTC alarm/ wakeup/ tamper/time stamp event occurs.

Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

#### 3.21 V<sub>BAT</sub> operation

The VBAT pin allows to power the device  $V_{BAT}$  domain from an external battery, an external super-capacitor, or from  $V_{DD}$  when no external battery and an external super-capacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC and the backup registers.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR\_ON pin is not connected to  $V_{DD}$  (internal Reset OFF), the  $V_{BAT}$  functionality is no more available and VBAT pin should be connected to  $V_{DD}$ .

#### 3.22 Timers and watchdogs

The devices embed two advanced-control timer, ten general-purpose timers, two basic timers, one low-power timer, two watchdog timers and a SysTick timer.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control and general-purpose timers.

| Timer<br>type        | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max.<br>interface<br>clock<br>(MHz) | Max.<br>timer<br>clock<br>(MHz) |

|----------------------|-----------------|-----------------------|-------------------------|---------------------------------------------|------------------------------|---------------------------------|---------------------------|-------------------------------------|---------------------------------|

| Advance<br>d-control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | Yes                       | 100                                 | 100                             |

|                      | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                        | 50                                  | 100                             |

|                      | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                        | 50                                  | 100                             |

| General              | TIM9            | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                        | 100                                 | 100                             |

| purpose              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                        | 100                                 | 100                             |

|                      | TIM12           | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                        | 50                                  | 100                             |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                        | 50                                  | 100                             |

Table 5. Timer feature comparison

|          |        | Ρ       | in Nu   | mber     |          |         |                                                         |             |                  |       |                                                                                  |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|----------------------------------------------------------------------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP81 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                              | Additional<br>functions |

| -        | -      | -       | -       | -        | D4       | 12      | PF2                                                     | I/O         | FT               | -     | I2C2_SMBA, FSMC_A2,<br>EVENTOUT                                                  | -                       |

| -        | -      | -       | -       | -        | E2       | 13      | PF3                                                     | I/O         | FT               | -     | TIM5_CH1, FSMC_A3,<br>EVENTOUT                                                   | -                       |

| -        | -      | -       | -       | -        | E3       | 14      | PF4                                                     | I/O         | FT               | -     | TIM5_CH2, FSMC_A4,<br>EVENTOUT                                                   | -                       |

| -        | -      | -       | -       | -        | E4       | 15      | PF5                                                     | I/O         | FT               | -     | TIM5_CH3, FSMC_A5,<br>EVENTOUT                                                   | -                       |

| -        | -      | D8      | 10      | F2       | D2       | 16      | VSS                                                     | S           | -                | -     | -                                                                                | -                       |

| -        | -      | E8      | 11      | G2       | D3       | 17      | VDD                                                     | S           | -                | -     | -                                                                                | -                       |

| -        | -      | -       | -       | -        | F3       | 18      | PF6                                                     | I/O         | FT               | -     | TRACED0, TIM10_CH1,<br>SAI1_SD_B,<br>UART7_Rx,<br>QUADSPI_BK1_IO3,<br>EVENTOUT   | -                       |

| -        | -      | -       | -       | -        | F2       | 19      | PF7                                                     | I/O         | FT               | -     | TRACED1, TIM11_CH1,<br>SAI1_MCLK_B,<br>UART7_Tx,<br>QUADSPI_BK1_IO2,<br>EVENTOUT | -                       |

| -        | -      | -       | -       | -        | G3       | 20      | PF8                                                     | I/O         | FT               | -     | SAI1_SCK_B,<br>UART8_RX,<br>TIM13_CH1,<br>QUADSPI_BK1_IO0,<br>EVENTOUT           | -                       |

| -        | -      | -       | -       | -        | G2       | 21      | PF9                                                     | I/O         | FT               | -     | SAI1_FS_B,<br>UART8_TX,<br>TIM14_CH1,<br>QUADSPI_BK1_IO1,<br>EVENTOUT            | -                       |

| -        | -      | -       | -       | -        | G1       | 22      | PF10                                                    | I/O         | FT               | -     | TIM1_ETR, TIM5_CH4,<br>EVENTOUT                                                  | -                       |

| 5        | 5      | E9      | 12      | F1       | D1       | 23      | PH0 - OSC_IN                                            | I/O         | FT               | (6)   | EVENTOUT                                                                         | OSC_IN                  |

| 6        | 6      | F9      | 13      | G1       | E1       | 24      | PH1 -<br>OSC_OUT                                        | I/O         | FT               | (6)   | EVENTOUT                                                                         | OSC_OUT                 |

| 7        | 7      | G9      | 14      | H2       | F1       | 25      | NRST                                                    | I/O         | RST              | -     | -                                                                                | NRST                    |

| -        | 8      | F8      | 15      | H1       | H1       | 26      | PC0                                                     | I/O         | FT               | -     | LPTIM1_IN1,<br>DFSDM2_CKIN4,<br>SAI1_MCLK_B,<br>EVENTOUT                         | ADC1_IN10,<br>WKUP2     |

Table 10. STM32F413xG/H pin definition (continued)

|          |        | Ρ       | in Nu   | mber     |          |         |                                                         |             |                  |       |                                                                                                                                        |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP81 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                                                                    | Additional<br>functions |

| -        | 18     | H7      | 27      | -        | -        | 38      | VSS                                                     | S           | -                | -     | -                                                                                                                                      | -                       |

| -        | -      | F6      | -       | E3       | H5       | -       | BYPASS_<br>REG                                          | I           | FT               | -     | -                                                                                                                                      | -                       |

| -        | 19     | J8      | 28      | -        | F4       | 39      | VDD                                                     | S           | -                | -     | -                                                                                                                                      | -                       |

| 14       | 20     | E5      | 29      | М3       | J3       | 40      | PA4                                                     | I/O         | ТТа              | -     | SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK,<br>DFSDM1_DATIN1,<br>FSMC_D6/FSMC_DA6,<br>EVENTOUT                                | ADC1_IN4,<br>DAC_OUT1   |

| 15       | 21     | G6      | 30      | K4       | K3       | 41      | PA5                                                     | I/O         | ТТа              | -     | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK/I2S1_CK,<br>DFSDM1_CKIN1,<br>FSMC_D7/FSMC_DA7,<br>EVENTOUT                                | ADC1_IN5,<br>DAC_OUT2   |

| 16       | 22     | F5      | 31      | L4       | L3       | 42      | PA6                                                     | I/O         | FT               | -     | TIM1_BKIN, TIM3_CH1,<br>TIM8_BKIN,<br>SPI1_MISO, I2S2_MCK,<br>DFSDM2_CKIN1,<br>TIM13_CH1,<br>QUADSPI_BK2_IO0,<br>SDIO_CMD,<br>EVENTOUT | ADC1_IN6                |

| 17       | 23     | J7      | 32      | M4       | M3       | 43      | PA7                                                     | I/O         | FT               | -     | TIM1_CH1N,<br>TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI/I2S1_SD,<br>DFSDM2_DATIN1,<br>TIM14_CH1,<br>QUADSPI_BK2_IO1,<br>EVENTOUT            | ADC1_IN7                |

| -        | 24     | H6      | 33      | K5       | J4       | 44      | PC4                                                     | I/O         | FT               | -     | DFSDM2_CKIN2,<br>I2S1_MCK,<br>QUADSPI_BK2_IO2,<br>FSMC_NE4,<br>EVENTOUT                                                                | ADC1_IN14               |

| -        | 25     | J6      | 34      | L5       | K4       | 45      | PC5                                                     | I/O         | FT               | -     | DFSDM2_DATIN2,<br>I2CFMP1_SMBA,<br>USART3_RX,<br>QUADSPI_BK2_IO3,<br>FSMC_NOE,<br>EVENTOUT                                             | ADC1_IN15               |

Table 10. STM32F413xG/H pin definition (continued)

|          |        | Ρ       | in Nu   | mber     |          |         |                                                         |             |                  |       |                                                                                                                                             |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP81 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                                                                         | Additional<br>functions |

| -        | -      | NC      | 62      | H10      | K12      | 86      | PD15                                                    | I/O         | FTf              | (2)   | TIM4_CH4,<br>I2CFMP1_SDA,<br>DFSDM2_DATIN0,<br>UART9_TX,<br>FSMC_D1/FSMC_DA1,<br>EVENTOUT                                                   | -                       |

| -        | -      | -       | -       | -        | J12      | 87      | PG2                                                     | I/O         | FT               | -     | FSMC_A12,<br>EVENTOUT                                                                                                                       | -                       |

| -        | -      | -       | -       | -        | J11      | 88      | PG3                                                     | I/O         | FT               | -     | FSMC_A13,<br>EVENTOUT                                                                                                                       | -                       |

| -        | -      | -       | -       | -        | J10      | 89      | PG4                                                     | I/O         | FT               | -     | FSMC_A14,<br>EVENTOUT                                                                                                                       | -                       |

| -        | -      | -       | -       | -        | H12      | 90      | PG5                                                     | I/O         | FT               | -     | FSMC_A15,<br>EVENTOUT                                                                                                                       | -                       |

| -        | -      | -       | -       | -        | H11      | 91      | PG6                                                     | I/O         | FT               | -     | QUADSPI_BK1_NCS,<br>EVENTOUT                                                                                                                | -                       |

| -        | -      | -       | -       | -        | H10      | 92      | PG7                                                     | I/O         | FT               | -     | USART6_CK,<br>EVENTOUT                                                                                                                      | -                       |

| -        | -      | -       | -       | -        | G11      | 93      | PG8                                                     | I/O         | FT               | -     | USART6_RTS,<br>EVENTOUT                                                                                                                     | -                       |

| -        | -      | -       | -       | -        | -        | 94      | VSS                                                     | S           | -                | -     | -                                                                                                                                           | -                       |

| -        | -      | -       | -       | -        | F10      | -       | VDD                                                     | S           | -                | -     | -                                                                                                                                           | -                       |

| -        | -      | F1      | -       | -        | C11      | 95      | VDDUSB                                                  | S           | -                | -     | -                                                                                                                                           | -                       |

| -        | 37     | D5      | 63      | E12      | G12      | 96      | PC6                                                     | I/O         | FTf              | -     | TIM3_CH1, TIM8_CH1,<br>I2CFMP1_SCL,<br>I2S2_MCK,<br>DFSDM1_CKIN3,<br>DFSDM2_DATIN6,<br>USART6_TX,<br>FSMC_D1/FSMC_DA1,<br>SDI0_D6, EVENTOUT | -                       |

| -        | 38     | D4      | 64      | E11      | F12      | 97      | PC7                                                     | I/O         | FTf              | -     | TIM3_CH2, TIM8_CH2,<br>I2CFMP1_SDA,<br>SPI2_SCK/I2S2_CK,<br>I2S3_MCK,<br>DFSDM2_CKIN6,<br>USART6_RX,<br>DFSDM1_DATIN3,<br>SDIO_D7, EVENTOUT | -                       |

Table 10. STM32F413xG/H pin definition (continued)

|          |        | Ρ       | in Nu   | mber     |          |         |                                                         |             |                  |       |                                                                                                                                                       |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP81 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                                                                                   | Additional<br>functions |

| -        | -      | -       | -       | -        | D8       | 125     | PG10                                                    | I/O         | FT               | -     | FSMC_NE3,<br>EVENTOUT                                                                                                                                 | -                       |

| -        | -      | -       | -       | -        | C8       | 126     | PG11                                                    | I/O         | FT               | -     | CAN2_RX,<br>UART10_RX,<br>EVENTOUT                                                                                                                    | -                       |

| -        | -      | -       | -       | -        | B8       | 127     | PG12                                                    | I/O         | FT               | -     | USART6_RTS,<br>CAN2_TX, UART10_TX,<br>FSMC_NE4,<br>EVENTOUT                                                                                           | -                       |

| -        | -      | -       | -       | -        | D7       | 128     | PG13                                                    | I/O         | FT               | -     | TRACED2,<br>USART6_CTS,<br>FSMC_A24,<br>EVENTOUT                                                                                                      | -                       |

| -        | -      | -       | -       | -        | C7       | 129     | PG14                                                    | I/O         | FT               | -     | TRACED3,<br>USART6_TX,<br>QUADSPI_BK2_IO3,<br>FSMC_A25,<br>EVENTOUT                                                                                   | -                       |

| -        | -      | -       | -       | -        | -        | 130     | VSS                                                     | S           | -                | -     | -                                                                                                                                                     | -                       |

| -        | -      | -       | -       | -        | F6       | 131     | VDD                                                     | S           | -                | -     | -                                                                                                                                                     | -                       |

| -        | -      | -       | -       | -        | B7       | 132     | PG15                                                    | I/O         | FT               | -     | USART6_CTS,<br>EVENTOUT                                                                                                                               | -                       |

| 39       | 55     | A5      | 89      | A8       | A7       | 133     | PB3                                                     | I/O         | FTf              | -     | JTDO-SWO, TIM2_CH2,<br>I2CFMP1_SDA,<br>SPI1_SCK/I2S1_CK,<br>SPI3_SCK/I2S3_CK,<br>USART1_RX,<br>UART7_RX, I2C2_SDA,<br>SAI1_SD_A, CAN3_RX,<br>EVENTOUT | -                       |

| 40       | 56     | В5      | 90      | A7       | A6       | 134     | PB4                                                     | I/O         | FT               | -     | JTRST, TIM3_CH1,<br>SPI1_MISO,<br>SPI3_MISO,<br>I2S3ext_SD,<br>UART7_TX, I2C3_SDA,<br>SAI1_SCK_A,<br>CAN3_TX, SDI0_D0,<br>EVENTOUT                    | -                       |

Table 10. STM32F413xG/H pin definition (continued)

57

69/208

# DocID029162 Rev 4

|        |      | AF0        | AF1               | AF2          | AF3                     | AF4                  | AF5                                                 | AF6                                                              | AF7                                                            | AF8                                      | AF9                                                          | AF10                                                        | AF11                                          | AF12       | AF13 | AF14 | AF15         |

|--------|------|------------|-------------------|--------------|-------------------------|----------------------|-----------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|------------|------|------|--------------|

|        | Port | SYS_<br>AF | TIM1/2/<br>LPTIM1 | TIM3/4/5     | DFSDM2/<br>TIM8/9/10/11 | I2C1/2/3/<br>I2CFMP1 | SPI1/I2S1/<br>SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/I2S4 | SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/I2S4/<br>SPI5/I2S5/<br>DFSDM1/2 | SPI3/I2S3/<br>SAI1/<br>DFSDM2/<br>USART1/<br>USART2/<br>USART3 | DFSDM1/<br>USART3/4/<br>5/6/7/8/<br>CAN1 | I2C2/I2C3/<br>I2CFMP1/<br>CAN1/2/<br>TIM12/13/14/<br>QUADSPI | SAI1/<br>DFSDM1/<br>DFSDM2/<br>QUADSPI/<br>FSMC<br>/OTG1_FS | UART4/<br>UART5/<br>UART9/<br>UART10<br>/CAN3 | FSMC /SDIO | -    | RNG  | SYS_<br>AF   |

|        | PC0  | -          | LPTIM1_<br>IN1    | -            | DFSDM2_C<br>KIN4        | -                    | -                                                   | -                                                                | SAI1_MCL<br>K_B                                                | -                                        | -                                                            | -                                                           | -                                             | -          | -    | -    | EVENT<br>OUT |

|        | PC1  | -          | LPTIM1_<br>OUT    | -            | DFSDM2_D<br>ATIN4       | -                    | -                                                   | -                                                                | SAI1_SD_B                                                      | -                                        | -                                                            | -                                                           | -                                             | -          | -    | -    | EVENT<br>OUT |

|        | PC2  | -          | LPTIM1_I<br>N2    | -            | DFSDM2_D<br>ATIN7       | -                    | SPI2_MISO                                           | I2S2ext_SD                                                       | SAI1_SCK_<br>B                                                 | DFSDM1_<br>CKOUT                         | -                                                            | -                                                           | -                                             | FSMC_NWE   | -    | -    | EVENT<br>OUT |

|        | PC3  | -          | LPTIM1_<br>ETR    | -            | DFSDM2_C<br>KIN7        | -                    | SPI2_MOSI/<br>I2S2_SD                               | -                                                                | SAI1_FS_B                                                      | -                                        | -                                                            | -                                                           | -                                             | FSMC_A0    | -    | -    | EVENT<br>OUT |

|        | PC4  | -          | -                 | -            | DFSDM2_C<br>KIN2        | -                    | I2S1_MCK                                            | -                                                                | -                                                              | -                                        | -                                                            | QUADSPI_<br>BK2_IO2                                         | -                                             | FSMC_NE4   | -    | -    | EVENT<br>OUT |

|        | PC5  | -          | -                 | -            | DFSDM2_D<br>ATIN2       | I2CFMP1<br>_SMBA     | -                                                   | -                                                                | USART3_R<br>X                                                  | -                                        | -                                                            | QUADSPI_<br>BK2_IO3                                         | -                                             | FSMC_NOE   | -    | -    | EVENT<br>OUT |

|        | PC6  | -          | -                 | TIM3_<br>CH1 | TIM8_CH1                | I2CFMP1<br>_SCL      | I2S2_MCK                                            | DFSDM1_<br>CKIN3                                                 | DFSDM2_<br>DATIN6                                              | USART6_<br>TX                            | -                                                            | FSMC_D1/<br>FSMC_DA1                                        | -                                             | SDIO_D6    | -    | -    | EVENT<br>OUT |

| U<br>U | PC7  | -          | -                 | TIM3_<br>CH2 | TIM8_CH2                | I2CFMP1<br>_SDA      | SPI2_SCK/<br>I2S2_CK                                | I2S3_MCK                                                         | DFSDM2_<br>CKIN6                                               | USART6_<br>RX                            | -                                                            | DFSDM1_D<br>ATIN3                                           | -                                             | SDIO_D7    | -    | -    | EVENT<br>OUT |

| Port   | PC8  | -          | -                 | TIM3_<br>CH3 | TIM8_CH3                | -                    | -                                                   | -                                                                | DFSDM2_<br>CKIN3                                               | USART6_<br>CK                            | QUADSPI_<br>BK1_IO2                                          | -                                                           | -                                             | SDIO_D0    | -    | -    | EVENT<br>OUT |

|        | PC9  | MCO_2      | -                 | TIM3_<br>CH4 | TIM8_CH4                | I2C3_<br>SDA         | I2S2_CKIN                                           | -                                                                | DFSDM2_<br>DATIN3                                              | -                                        | QUADSPI_<br>BK1_IO0                                          | -                                                           | -                                             | SDIO_D1    | -    | -    | EVENT<br>OUT |

|        | PC10 | -          | -                 | -            | DFSDM2_<br>CKIN5        | -                    | -                                                   | SPI3_SCK/<br>I2S3_CK                                             | USART3_<br>TX                                                  | -                                        | QUADSPI_<br>BK1_IO1                                          | -                                                           | -                                             | SDIO_D2    | -    | -    | EVENT<br>OUT |

|        | PC11 | -          | -                 | -            | DFSDM2_<br>DATIN5       | -                    | I2S3ext_SD                                          | SPI3_MISO                                                        | USART3_<br>RX                                                  | UART4_<br>RX                             | QUADSPI_<br>BK2_NCS                                          | FSMC_D2/<br>FSMC_DA2                                        | -                                             | SDIO_D3    | -    | -    | EVENT<br>OUT |

|        | PC12 | -          | -                 | -            | -                       | -                    | -                                                   | SPI3_MOSI/<br>I2S3_SD                                            | USART3_<br>CK                                                  | UART5_<br>TX                             | -                                                            | FSMC_D3/<br>FSMC_DA3                                        | -                                             | SDIO_CK    | -    | -    | EVENT<br>OUT |

|        | PC13 | -          | -                 | -            | -                       | -                    | -                                                   | -                                                                | -                                                              | -                                        | -                                                            | -                                                           | -                                             | -          | -    | -    | EVENT<br>OUT |

|        | PC14 | -          | -                 | -            | -                       | -                    | -                                                   | -                                                                | -                                                              | -                                        | -                                                            | -                                                           | -                                             | -          | -    | -    | EVENT<br>OUT |

|        | PC15 | -          | -                 | -            | -                       | -                    | -                                                   | -                                                                | -                                                              | -                                        | -                                                            | -                                                           | -                                             | -          | -    | -    | EVENT<br>OUT |

Table 12. STM32F413xG/H alternate functions (continued)

# Pinouts and pin description

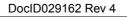

#### 6.1.7 Current consumption measurement

#### Figure 22. Current consumption measurement scheme

#### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 14: Voltage characteristics*, *Table 15: Current characteristics*, and *Table 16: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                                   | Min                                                      | Max                  | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|------|

| $V_{DD} - V_{SS}$                 | External main supply voltage (including $V_{DDA}, V_{DD}, V_{DDUSB}$ and $V_{BAT})^{(1)}$ | -0.3                                                     | 4.0                  |      |

|                                   | Input voltage on FT and TC pins <sup>(2)</sup>                                            | V <sub>SS</sub> -0.3                                     | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub>                   | Input voltage on TTa pins                                                                 | V <sub>SS</sub> -0.3                                     | 4.0                  |      |

|                                   | Input voltage on any other pin                                                            | V <sub>SS</sub> -0.3                                     | 4.0                  |      |

|                                   | Input voltage for BOOT0                                                                   | V <sub>SS</sub>                                          | 9.0                  |      |

| $ \Delta V_{DDx} $                | Variations between different V <sub>DD</sub> power pins                                   | -                                                        | 50                   |      |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins including $V_{\text{REF}\text{-}}$       | -                                                        | 50                   | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                                        | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum<br>ectrical  |      |

Table 14. Voltage characteristics

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2.  $V_{\rm IN}$  maximum value must always be respected. Refer to *Table 15* for the values of the maximum allowed injected current.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

| Typ Max <sup>(1)</sup> |                        |                                                                      |                   |                           |                           |                           |                            |                            |      |

|------------------------|------------------------|----------------------------------------------------------------------|-------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

|                        |                        |                                                                      | f <sub>HCLK</sub> | Тур                       |                           | Ma                        | IX <sup>(')</sup>          |                            |      |

| Symbol                 | Parameter              | Conditions                                                           | (MHz)             | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>25 °С | Т <sub>А</sub> =<br>85 °С | Т <sub>А</sub> =<br>105 °С | T <sub>A</sub> =<br>125 °C | Unit |

|                        |                        |                                                                      | 100               | 33.3                      | 35.32 <sup>(3)</sup>      | 35.65                     | 37.65                      | 41.26 <sup>(3)</sup>       |      |

|                        | Supply                 | External clock,<br>PLL ON,<br>all peripherals enabled <sup>(2)</sup> | 84                | 26.8                      | 28.45 <sup>(3)</sup>      | 28.97                     | 30.82                      | 34.39 <sup>(3)</sup>       |      |

|                        |                        |                                                                      | 64                | 18.6                      | 19.74 <sup>(3)</sup>      | 20.35                     | 22.11                      | 25.35 <sup>(3)</sup>       |      |

|                        |                        |                                                                      | 50                | 14.6                      | 15.57                     | 16.41                     | 18.21                      | 21.46                      |      |

|                        |                        |                                                                      | 25                | 7.8                       | 8.37                      | 9.64                      | 11.32                      | 14.68                      |      |

|                        |                        |                                                                      | 20                | 6.7                       | 7.25                      | 8.40                      | 10.25                      | 13.45                      |      |

|                        |                        | HSI, PLL OFF <sup>(4)</sup> , all peripherals enabled <sup>(2)</sup> | 16                | 4.6                       | 4.96                      | 6.39                      | 8.20                       | 11.54                      |      |

|                        |                        |                                                                      | 1                 | 0.8                       | 0.86                      | 2.51                      | 4.34                       | 7.65                       |      |

| I <sub>DD</sub>        | current in<br>Run mode |                                                                      | 100               | 15.7                      | 16.74 <sup>(3)</sup>      | 17.62                     | 19.50                      | 23.16 <sup>(3)</sup>       | mA   |

|                        |                        | External algoly                                                      | 84                | 12.7                      | 13.57 <sup>(3)</sup>      | 14.60                     | 16.38                      | 19.98 <sup>(3)</sup>       |      |

|                        |                        | External clock,<br>PLL ON,                                           | 64                | 9.0                       | 9.62 <sup>(3)</sup>       | 10.60                     | 12.37                      | 15.58 <sup>(3)</sup>       |      |

|                        |                        | all peripherals<br>disabled <sup>(2)</sup>                           | 50                | 7.1                       | 7.69                      | 8.79                      | 10.63                      | 13.79                      |      |

|                        |                        | uisableu. /                                                          | 25                | 4.0                       | 4.52                      | 5.68                      | 7.44                       | 10.68                      |      |

|                        |                        |                                                                      | 20                | 3.4                       | 4.03                      | 5.23                      | 6.90                       | 10.27                      |      |

|                        |                        | HSI, PLL OFF,                                                        | 16                | 2.3                       | 2.44                      | 4.00                      | 5.81                       | 9.13                       |      |

|                        |                        | all peripherals<br>disabled <sup>(2)</sup>                           | 1                 | 0.6                       | 0.70                      | 2.35                      | 4.18                       | 7.49                       |      |

# Table 24. Typical and maximum current consumption, code with data processing (ARTaccelerator disabled) running from SRAM - V<sub>DD</sub> = 3.6 V

1. Guaranteed by characterization results.

2. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

3. Tested in production

4. When analog peripheral blocks such as ADC, HSE, LSE, HSI, or LSI are ON, an additional power consumption has to be considered

|                 |                    | celerator disabled) run                                                    |                            |                           |                           |                           |                            |                            |     |

|-----------------|--------------------|----------------------------------------------------------------------------|----------------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|-----|

|                 |                    |                                                                            | fun                        | Тур                       |                           | Ma                        | x <sup>(1)</sup>           |                            |     |

| Symbol          | Parameter          | Conditions                                                                 | f <sub>HCLK</sub><br>(MHz) | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Uni |

|                 |                    | External clock,<br>PLL ON,<br>all peripherals<br>enabled <sup>(2)(3)</sup> | 100                        | 36.1                      | 38.48                     | 39.08                     | 40.91                      | 44.59                      |     |

|                 |                    |                                                                            | 84                         | 30.6                      | 32.60                     | 33.14                     | 35.10                      | 38.56                      |     |

|                 |                    |                                                                            | 64                         | 23.9                      | 25.67                     | 26.27                     | 27.94                      | 31.19                      |     |

|                 |                    |                                                                            | 50                         | 18.9                      | 20.32                     | 21.04                     | 22.85                      | 26.10                      |     |

|                 | Supply current     |                                                                            | 25                         | 10.8                      | 11.63                     | 12.75                     | 14.56                      | 17.87                      |     |

|                 |                    |                                                                            | 20                         | 9.2                       | 9.84                      | 11.06                     | 12.98                      | 16.23                      |     |

|                 |                    | HSI, PLL OFF,<br>all peripherals<br>enabled <sup>(2)(3)</sup>              | 16                         | 7.1                       | 7.69                      | 9.02                      | 10.87                      | 14.25                      |     |

| I <sub>DD</sub> |                    |                                                                            | 1                          | 1.2                       | 1.84                      | 3.10                      | 4.84                       | 8.20                       | mA  |

| 00              | in <b>Run mode</b> |                                                                            | 100                        | 18.6                      | 20.33                     | 21.23                     | 23.15                      | 26.71                      |     |

|                 |                    |                                                                            | 84                         | 16.5                      | 18.09                     | 19.01                     | 20.81                      | 24.29                      |     |

|                 |                    | External clock, PLL ON <sup>(3)</sup>                                      | 64                         | 14.3                      | 15.76                     | 16.67                     | 18.28                      | 21.50                      |     |

|                 |                    | all peripherals disabled                                                   | 50                         | 11.5                      | 12.57                     | 13.53                     | 15.33                      | 18.49                      |     |

|                 |                    |                                                                            | 25                         | 7.0                       | 7.67                      | 8.90                      | 10.76                      | 14.05                      |     |

|                 |                    |                                                                            | 20                         | 6.0                       | 6.68                      | 7.87                      | 9.65                       | 12.96                      | -   |

|                 |                    | HSI, PLL OFF,                                                              | 16                         | 4.8                       | 5.33                      | 6.66                      | 8.49                       | 11.86                      |     |

|                 |                    | all peripherals disabled <sup>(3)</sup>                                    | 1                          | 1.0                       | 1.62                      | 2.95                      | 4.66                       | 8.06                       |     |

|                 |                    |                                                                            |                            |                           | 1                         | 1                         | 1                          | 1                          |     |

# Table 28. Typical and maximum current consumption in run mode, code with data processing<br/>(ART accelerator disabled) running from Flash memory - $V_{DD}$ = 1.7 V

1. Guaranteed by characterization results.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 59: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 39: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$\mathrm{I}_{\mathrm{SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DD</sub> is the MCU supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

#### On-chip peripheral current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- The ART accelerator is ON.

- Voltage Scale 2 mode selected, internal digital voltage V12 = 1.26 V.

- HCLK is the system clock at 100 MHz. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off,

- with only one peripheral clocked on,

- scale 1 with f<sub>HCLK</sub> = 100 MHz,

- scale 2 with f<sub>HCLK</sub> = 84 MHz,

- scale 3 with  $f_{HCLK}$  = 64 MHz.

- Ambient operating temperature is 25 °C and V<sub>DD</sub>=3.3 V.

| Periph | orol                |              | I <sub>DD</sub> (Typ) |              | Unit      |

|--------|---------------------|--------------|-----------------------|--------------|-----------|

| Penpi  | erai                | Scale 1      | Scale 2               | Scale 3      | Unit      |

|        | GPIOA               | 1.89         | 1.82                  | 1.64         |           |

|        | GPIOB               | 1.75         | 1.68                  | 1.52         |           |

|        | GPIOC               | 1.70         | 1.64                  | 1.48         |           |

|        | GPIOD               | 1.72         | 1.65                  | 1.48         |           |

|        | GPIOE               | 1.78         | 1.71                  | 1.55         |           |

| AHB1   | GPIOF               | 1.68         | 1.62                  | 1.45         | µA/MHz    |

|        | GPIOG               | DG 1.66 1.61 |                       | 1.44         |           |

|        | GPIOH               | 0.72         | 0.69                  | 0.63         |           |

|        | CRC                 | 0.30         | 0.30                  | 0.28         |           |

|        | DMA1 <sup>(1)</sup> | 1.75N + 3.14 | 1.66N + 3.00          |              |           |

|        | DMA2 <sup>(1)</sup> | 1.79N + 3.29 | 1.71N + 3.14          | 1.53N + 2.82 |           |

| AHB2   | RNG                 | 0.72         | 0.70                  | 0.63         | µA/MHz    |

|        | USB_OTG_FS          | 19.26        | 18.37                 | 16.47        | μπνινιιίΖ |

| AHB3   | FSMC                | 5.42         | 5.18                  | 4.64         | µA/MHz    |

|        | QSPI                | 10.33        | 9.86                  | 8.84         | μητιντικά |

| Symbol                            | Parameter                                                                          | Conditions                                         | Min | Тур | Max  | Unit |

|-----------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|------|

|                                   |                                                                                    | 12-bit resolution<br>Single ADC                    | -   | -   | 2    | Msps |

| f <sub>S</sub> <sup>(2)</sup>     | Sampling rate<br>(f <sub>ADC</sub> = 30 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode   | -   | -   | 3.75 | Msps |

|                                   | (5 0 / 12 0 0) 0.00)                                                               | 12-bit resolution<br>Interleave Triple ADC<br>mode | -   | -   | 6    | Msps |

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode               | -                                                  | -   | 300 | 500  | μA   |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode               | -                                                  | -   | 1.6 | 1.8  | mA   |

#### Table 75. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is possible with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

2. Guaranteed by characterization results.

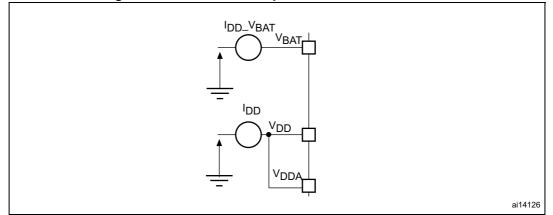

3.  $V_{\mathsf{REF}^+}$  is internally connected to  $V_{\mathsf{DDA}}$  and  $V_{\mathsf{REF}^-}$  is internally connected to  $V_{\mathsf{SSA}}.$

4.  $R_{ADC}$  maximum value is given for  $V_{DD}$ =1.7 V, and minimum value for  $V_{DD}$ =3.3 V.

5. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 75.

#### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} = \frac{(k-0.5)}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       | ( (0,0))                                                    | ±3  | ±4                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±2  | ±3                 |      |

| EG     | Gain error                   | $V_{\text{REF}}$ = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V                  | ±1  | ±2                 |      |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |

Table 76. ADC accuracy at f<sub>ADC</sub> = 18 MHz<sup>(1)</sup>

1. Better performance could be achieved in restricted  $V_{DD}$ , frequency and temperature ranges.

2. Guaranteed by characterization results.

Figure 51. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are both available on UFBGA100.  $V_{REF+}$  is also available on LQFP100. When  $V_{REF+}$  and  $V_{REF-}$  are not available, they are internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

#### 6.3.21 Temperature sensor characteristics

| Symbol                             | Parameter                                                      | Min | Тур  | Max | Unit  |

|------------------------------------|----------------------------------------------------------------|-----|------|-----|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -   | ±1   | ±2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                                  | -   | 2.5  | -   | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -   | 0.76 | -   | V     |

| t <sub>START</sub> <sup>(2)</sup>  | Startup time                                                   | -   | 6    | 10  | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10  | -    | -   | μs    |

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Symbol  | Parameter                                                            | Memory address            |

|---------|----------------------------------------------------------------------|---------------------------|

| TS_CAL1 | TS ADC raw data acquired at temperature of 30 °C, $V_{DDA}$ = 3.3 V  | 0x1FFF 7A2C - 0x1FFF 7A2D |

| TS_CAL2 | TS ADC raw data acquired at temperature of 110 °C, $V_{DDA}$ = 3.3 V | 0x1FFF 7A2E - 0x1FFF 7A2F |

#### 6.3.22 V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                            | Min | Тур | Max | Unit |

|---------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                 | -   | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                                | -   | 4   | -   |      |

| Er <sup>(1)</sup>                     | Error on Q                                                           | -1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1 mV accuracy | 5   | -   | -   | μs   |

Table 83. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

#### 6.3.23 Embedded reference voltage

The parameters given in *Table 84* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                                | Parameter                                                        | Conditions                        | Min  | Тур  | Max  | Unit   |

|---------------------------------------|------------------------------------------------------------------|-----------------------------------|------|------|------|--------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                       | –40 °C < T <sub>A</sub> < +125 °C | 1.18 | 1.21 | 1.24 | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the<br>internal reference voltage | -                                 | 10   | -    | -    | μs     |

| V <sub>RERINT_s</sub> <sup>(2)</sup>  | Internal reference voltage spread over the temperature range     | $V_{DD}$ = 3V $\pm$ 10mV          | -    | 3    | 5    | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                          | -                                 | -    | 30   | 50   | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                                     | -                                 | -    | 6    | 10   | μs     |

#### Table 84. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design

#### Table 85. Internal reference voltage calibration values

| Symbol                 | Parameter                                                          | Memory address            |

|------------------------|--------------------------------------------------------------------|---------------------------|

| V <sub>REFIN_CAL</sub> | Raw data acquired at temperature of 30 °C V <sub>DDA</sub> = 3.3 V | 0x1FFF 7A2A - 0x1FFF 7A2B |

#### 6.3.24 DAC electrical characteristics

| Symbol                            | Parameter                                          | Conc          | litions                                               | Min                | Тур | Max                            | Unit | Comments                                                                                                                |

|-----------------------------------|----------------------------------------------------|---------------|-------------------------------------------------------|--------------------|-----|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                  | Analog supply voltage                              | -             |                                                       | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    |                                                                                                                         |

| V <sub>REF+</sub>                 | Reference supply voltage                           | -             |                                                       | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub>                                                                                     |

| $V_{SSA}$                         | Ground                                             | -             |                                                       | 0                  | -   | 0                              | V    | -                                                                                                                       |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load                                     | DAC<br>output | R <sub>LOAD</sub><br>connected<br>to V <sub>SSA</sub> | 5                  | -   | -                              | kΩ   | -                                                                                                                       |

| NLOAD                             |                                                    | buffer ON     | R <sub>LOAD</sub><br>connected<br>to V <sub>DDA</sub> | 25                 | -   | -                              | kΩ   | -                                                                                                                       |

| R <sub>0</sub> <sup>(2)</sup>     | Impedance output<br>with buffer OFF                | -             |                                                       | -                  | -   | 15                             | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is $1.5\ M\Omega$ |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                    | -             |                                                       | -                  | -   | 50                             | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT<br>voltage with buffer<br>ON         |               | -                                                     | 0.2                | -   | -                              | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input                                  |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT<br>voltage with buffer<br>ON        |               | -                                                     | -                  | -   | V <sub>DDA</sub><br>- 0.2      | V    | code (0x0E0) to (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V and (0x1C7) to<br>(0xE38) at V <sub>REF+</sub> = 1.7 V          |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT<br>voltage with buffer<br>OFF        |               | -                                                     | -                  | 0.5 | _                              | mV   | It gives the maximum output                                                                                             |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT<br>voltage with buffer<br>OFF       |               | -                                                     | -                  | -   | V <sub>REF+</sub><br>_<br>1LSB | V    | excursion of the DAC.                                                                                                   |

| . (4)                             | DAC DC V <sub>REF</sub><br>current                 |               | -                                                     | -                  | 170 | 240                            |      | With no load, worst code (0x800)<br>at V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

| I <sub>VREF+</sub> <sup>(4)</sup> | consumption in<br>quiescent mode<br>(Standby mode) |               | -                                                     | -                  | 50  | 75                             | μA   | With no load, worst code (0xF1C)<br>at V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

|                                   | DAC DC VDDA<br>current                             |               | -                                                     | -                  | 280 | 380                            | μA   | With no load, middle code<br>(0x800) on the inputs                                                                      |

| I <sub>DDA</sub> <sup>(4)</sup>   | consumption in quiescent mode <sup>(3)</sup>       | -             |                                                       | -                  | 475 | 625                            | μA   | With no load, worst code (0xF1C)<br>at $V_{REF+}$ = 3.6 V in terms of DC<br>consumption on the inputs                   |

#### Table 86. DAC characteristics

#### **Electrical characteristics**

| Symbol                                                                                                                                                                 | Parameter                                                                                                                                                                | Table 86. DAC cha<br>Conditions | Min | Тур | Max  | Unit                                       | Comments                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|-----|------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| DNL <sup>(4)</sup>                                                                                                                                                     | Differential non<br>linearity Difference<br>between two                                                                                                                  | -                               | -   | -   | ±0.5 | LSB                                        | Given for the DAC in 10-bit configuration.                                                                        |

| DINE                                                                                                                                                                   | consecutive code-<br>1LSB)                                                                                                                                               | _                               | -   | _   | ±2   | LSB                                        | Given for the DAC in 12-bit configuration.                                                                        |

| Integral non<br>linearity (difference<br>between measured<br>value at Code i and<br>the value at Code i<br>on a line drawn<br>between Code 0<br>and last Code<br>1023) | -                                                                                                                                                                        | -                               | -   | ±1  | LSB  | Given for the DAC in 10-bit configuration. |                                                                                                                   |