Welcome to E-XFL.COM

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                         |

|----------------------------|------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Speed                      | 100MHz                                                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SDIO, QSPI, SAI, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                              |

| Number of I/O              | 114                                                                                            |

| Program Memory Size        | 1MB (1M x 8)                                                                                   |

| Program Memory Type        | FLASH                                                                                          |

| EEPROM Size                | -                                                                                              |

| RAM Size                   | 320K x 8                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                    |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                          |

| Oscillator Type            | Internal                                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                              |

| Mounting Type              | Surface Mount                                                                                  |

| Package / Case             | 144-UFBGA                                                                                      |

| Supplier Device Package    | 144-UFBGA (10x10)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f413zgj6                          |

|                            |                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 6.1.3    | Typical curves                                                   |

|-------|----------|------------------------------------------------------------------|

|       | 6.1.4    | Loading capacitor                                                |

|       | 6.1.5    | Pin input voltage                                                |

|       | 6.1.6    | Power supply scheme                                              |

|       | 6.1.7    | Current consumption measurement81                                |

| 6.2   | Absolut  | e maximum ratings                                                |

| 6.3   | Operati  | ng conditions                                                    |

|       | 6.3.1    | General operating conditions                                     |

|       | 6.3.2    | VCAP_1/VCAP_2 external capacitors                                |

|       | 6.3.3    | Operating conditions at power-up/power-down (regulator ON)       |

|       | 6.3.4    | Operating conditions at power-up / power-down (regulator OFF) 87 |

|       | 6.3.5    | Embedded reset and power control block characteristics           |

|       | 6.3.6    | Supply current characteristics                                   |

|       | 6.3.7    | Wakeup time from low-power modes                                 |

|       | 6.3.8    | External clock source characteristics                            |

|       | 6.3.9    | Internal clock source characteristics                            |

|       | 6.3.10   | PLL characteristics                                              |

|       | 6.3.11   | PLL spread spectrum clock generation (SSCG) characteristics 117  |

|       | 6.3.12   | Memory characteristics 118                                       |

|       | 6.3.13   | EMC characteristics                                              |

|       | 6.3.14   | Absolute maximum ratings (electrical sensitivity)                |

|       | 6.3.15   | I/O current injection characteristics                            |

|       | 6.3.16   | I/O port characteristics                                         |

|       | 6.3.17   | NRST pin characteristics 129                                     |

|       | 6.3.18   | TIM timer characteristics                                        |

|       | 6.3.19   | Communications interfaces                                        |

|       | 6.3.20   | 12-bit ADC characteristics                                       |

|       | 6.3.21   | Temperature sensor characteristics                               |

|       | 6.3.22   | V <sub>BAT</sub> monitoring characteristics                      |

|       | 6.3.23   | Embedded reference voltage                                       |

|       | 6.3.24   | DAC electrical characteristics                                   |

|       | 6.3.25   | DFSDM characteristics                                            |

|       | 6.3.26   | FSMC characteristics                                             |

|       | 6.3.27   | SD/SDIO MMC/eMMC card host interface (SDIO) characteristics 173  |

|       | 6.3.28   | RTC characteristics                                              |

| ь ·   |          |                                                                  |

| Packa | age info | ormation                                                         |

DocID029162 Rev 4

7

| 7.1                             | WLCSP81 package information 176                                                                                                                                                                         |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2                             | UFQFPN48 package information 180                                                                                                                                                                        |

| 7.3                             | LQFP64 package information 183                                                                                                                                                                          |

| 7.4                             | LQFP100 package information                                                                                                                                                                             |

| 7.5                             | LQFP144 package information                                                                                                                                                                             |

| 7.6                             | UFBGA100 package information 194                                                                                                                                                                        |

| 7.7                             | UFBGA144 package information 197                                                                                                                                                                        |

| 7.8                             | Thermal characteristics                                                                                                                                                                                 |

|                                 | 7.8.1 Reference document                                                                                                                                                                                |

|                                 |                                                                                                                                                                                                         |

| 8 Or                            | dering information                                                                                                                                                                                      |

|                                 | dering information                                                                                                                                                                                      |

|                                 |                                                                                                                                                                                                         |

| Appendix A                      | Recommendations when using the internal reset OFF 202                                                                                                                                                   |

| Appendix A<br>Appendix B        | Recommendations when using the internal reset OFF       202         Application block diagrams       203         Sensor Hub application example       203                                               |

| Appendix A<br>Appendix B<br>B.1 | Recommendations when using the internal reset OFF       202         Application block diagrams       203         Sensor Hub application example       203         Display application example       204 |

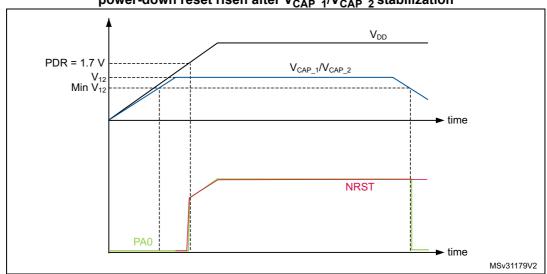

# Figure 9. Startup in regulator OFF: slow V<sub>DD</sub> slope power-down reset risen after V<sub>CAP 1</sub>/V<sub>CAP 2</sub> stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

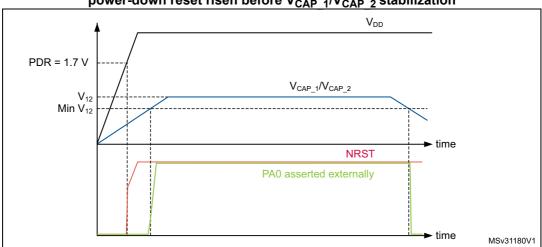

# Figure 10. Startup in regulator OFF mode: fast V<sub>DD</sub> slope power-down reset risen before $V_{CAP_1}/V_{CAP_2}$ stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

- 8-bit or 12-bit output mode

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

- Input voltage reference (V<sub>REF+</sub>)

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

#### 3.38 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value. Refer to the reference manual for additional information.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

### 3.39 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

### 3.40 Embedded Trace Macrocell<sup>™</sup>

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F413xG/H through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using any high-speed channel available. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at VDD or VSS (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to both f<sub>HCLK</sub> frequency and VDD ranges (refer to *Table 18: Features depending on the operating power supply range*).

- The voltage scaling is adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 64$  MHz

- Scale 2 for 64 MHz <  $f_{HCLK} \le 84$  MHz

- Scale 1 for 84 MHz <  $f_{HCLK} \le 100$  MHz

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/2$ , and  $f_{PCLK2} = f_{HCLK}$ .

- External clock is 4 MHz and PLL is ON except if it is explicitly mentioned.

- The maximum values are obtained for  $V_{DD}$  = 3.6 V and a maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

| Tab | Table 23. Typical and maximum current consumption, code with data processing (ARTaccelerator disabled) running from SRAM - V <sub>DD</sub> = 1.7 V |  |  |     |                    |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|-----|--------------------|--|--|

|     |                                                                                                                                                    |  |  | Typ | Max <sup>(1)</sup> |  |  |

| Question        | Parameter                               | eter Conditions                              | f <sub>HCLK</sub> | Тур                    | Max <sup>(1)</sup>     |                       |                        |                        | Unit |

|-----------------|-----------------------------------------|----------------------------------------------|-------------------|------------------------|------------------------|-----------------------|------------------------|------------------------|------|

| Symbol          | Parameter                               | Conditions                                   | (MHz)             | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 25 °C | T <sub>A</sub> =85 °C | T <sub>A</sub> =105 °C | T <sub>A</sub> =125 °C | Unit |

|                 |                                         |                                              | 100               | 32.9                   | 34.96                  | 35.30                 | 37.21                  | 40.79                  |      |

|                 |                                         |                                              | 84                | 26.5                   | 28.13                  | 28.58                 | 30.50                  | 33.96                  |      |

|                 |                                         | External clock,<br>PLL ON,                   | 64                | 18.3                   | 19.44                  | 20.11                 | 21.76                  | 25.03                  |      |

|                 |                                         | all peripherals<br>enabled <sup>(2)(3)</sup> | 50                | 14.4                   | 15.28                  | 16.12                 | 17.95                  | 21.11                  |      |

|                 |                                         | enabled                                      | 25                | 7.5                    | 8.10                   | 9.35                  | 11.09                  | 14.38                  |      |

|                 |                                         |                                              | 20                | 6.4                    | 6.99                   | 8.17                  | 9.96                   | 13.17                  |      |

|                 |                                         | HSI, PLL off, all                            | 16                | 4.6                    | 5.17                   | 6.42                  | 8.28                   | 11.46                  |      |

|                 | Supply<br>current in<br><b>Run mode</b> | peripherals<br>enabled <sup>(2)(3)</sup>     | 1                 | 0.7                    | 1.28                   | 2.64                  | 4.30                   | 7.66                   | mA   |

| I <sub>DD</sub> |                                         |                                              | 100               | 15.4                   | 16.43                  | 17.35                 | 19.17                  | 22.85                  | ШA   |

|                 |                                         |                                              | 84                | 12.4                   | 13.28                  | 14.32                 | 16.12                  | 19.67                  |      |

|                 |                                         |                                              | 64                | 8.7                    | 9.36                   | 10.38                 | 12.06                  | 15.31                  |      |

|                 |                                         |                                              | 50                | 6.9                    | 7.47                   | 8.54                  | 10.36                  | 13.49                  |      |

|                 |                                         |                                              | 25                | 3.7                    | 4.27                   | 5.47                  | 7.17                   | 10.45                  |      |

|                 |                                         |                                              | 20                | 3.2                    | 3.72                   | 5.01                  | 6.67                   | 10.02                  |      |

|                 |                                         | HSI, PLL off, all                            | 16                | 2.3                    | 2.80                   | 4.05                  | 5.90                   | 9.07                   |      |

|                 |                                         | peripherals<br>disabled <sup>(3)</sup>       | 1                 | 0.6                    | 1.14                   | 2.51                  | 4.16                   | 7.51                   |      |

1. Guaranteed by characterization results.

2. When analog peripheral blocks such as ADC, HSE, LSE, HSI, or LSI are ON, an additional power consumption has to be considered.

|                 |                                         |                                                      | £                          | Тур                       | Max <sup>(1)</sup>        |                           |                            |                            |      |

|-----------------|-----------------------------------------|------------------------------------------------------|----------------------------|---------------------------|---------------------------|---------------------------|----------------------------|----------------------------|------|

| Symbol          | Parameter                               | Conditions                                           | f <sub>HCLK</sub><br>(MHz) | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |                                         |                                                      | 100                        | 30.2                      | 32.03                     | 32.71                     | 34.69                      | 38.46                      |      |

|                 |                                         |                                                      | 84                         | 24.3                      | 25.77                     | 26.58                     | 28.47                      | 32.16                      |      |

|                 |                                         | External clock,                                      | 64                         | 16.8                      | 17.80                     | 18.66                     | 20.53                      | 23.85                      |      |

|                 |                                         | PLL ON, all peripherals enabled <sup>(2)(3)</sup>    | 50                         | 13.2                      | 14.05                     | 15.12                     | 16.85                      | 20.27                      |      |

|                 | Supply<br>current in<br><b>Run mode</b> |                                                      | 25                         | 7.1                       | 7.62                      | 8.92                      | 10.81                      | 14.11                      |      |

|                 |                                         |                                                      | 20                         | 6.1                       | 6.69                      | 7.95                      | 9.72                       | 13.09                      |      |

|                 |                                         | HSI, PLL OFF, all peripherals enabled <sup>(2)</sup> | 16                         | 4.4                       | 4.99                      | 6.28                      | 8.18                       | 11.45                      |      |

|                 |                                         |                                                      | 1                          | 0.9                       | 1.50                      | 2.88                      | 4.58                       | 8.00                       |      |

| I <sub>DD</sub> |                                         |                                                      | 100                        | 12.6                      | 13.46                     | 14.75                     | 16.68                      | 20.54                      | mA   |

|                 |                                         |                                                      | 84                         | 10.2                      | 10.90                     | 12.25                     | 14.10                      | 17.84                      |      |

|                 |                                         |                                                      | 64                         | 7.2                       | 7.70                      | 8.95                      | 10.81                      | 14.14                      |      |

|                 |                                         |                                                      | 50                         | 5.7                       | 6.26                      | 7.56                      | 9.26                       | 12.72                      |      |

|                 |                                         |                                                      | 25                         | 3.2                       | 3.77                      | 5.11                      | 6.82                       | 10.26                      | 1    |

|                 |                                         |                                                      | 20                         | 2.9                       | 3.41                      | 4.79                      | 6.49                       | 9.92                       | 1    |

|                 |                                         | HSI, PLL OFF, all                                    | 16                         | 2.1                       | 2.63                      | 3.91                      | 5.80                       | 9.06                       | 1    |

|                 |                                         | peripherals disabled <sup>(2)</sup>                  | 1                          | 0.8                       | 1.34                      | 2.72                      | 4.42                       | 7.86                       | 1    |

## Table 25. Typical and maximum current consumption in run mode, code with data processing (ART accelerator enabled except prefetch) running from Flash memory- V<sub>DD</sub> = 1.7 V

1. Guaranteed by characterization results..

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

4. Refer to Table 47 and RM0383 for the possible PLL VCO setting

| Symbol | Parameter                | Conditions <sup>(1)</sup>                                 | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit |

|--------|--------------------------|-----------------------------------------------------------|----------------------------------------------|-------|------|

|        |                          |                                                           | 2 MHz                                        | 0.05  |      |

| IDDIO  |                          |                                                           | 8 MHz                                        | 0.15  |      |

|        |                          |                                                           | 25 MHz                                       | 0.45  |      |

|        |                          | V <sub>DD</sub> = 3.3 V<br>C = C <sub>INT</sub>           | 50 MHz                                       | 0.85  |      |

|        |                          | C - CINT                                                  | 60 MHz                                       | 1.00  |      |

|        |                          |                                                           | 84 MHz                                       | 1.40  |      |

|        |                          |                                                           | 90 MHz                                       | 1.67  |      |

|        |                          |                                                           | 2 MHz                                        | 0.10  |      |

|        |                          |                                                           | 8 MHz                                        | 0.35  |      |

|        |                          | V <sub>DD</sub> = 3.3 V                                   | 25 MHz                                       | 1.05  |      |

|        | I/O switching<br>current | $C_{EXT} = 0 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_S$ | 50 MHz                                       | 2.20  | mA   |

|        |                          |                                                           | 60 MHz                                       | 2.40  |      |

|        |                          |                                                           | 84 MHz                                       | 3.55  |      |

|        |                          |                                                           | 90 MHz                                       | 4.23  |      |

|        |                          | V <sub>DD</sub> = 3.3 V                                   | 2 MHz                                        | 0.20  |      |

|        |                          |                                                           | 8 MHz                                        | 0.65  |      |

|        |                          |                                                           | 25 MHz                                       | 1.85  |      |

|        |                          | C <sub>EXT</sub> =10 pF                                   | 50 MHz                                       | 2.45  |      |

|        |                          | $C = C_{INT} + C_{EXT} + C_{S}$                           | 60 MHz                                       | 4.70  |      |

|        |                          |                                                           | 84 MHz                                       | 8.80  | -    |

|        |                          |                                                           | 90 MHz                                       | 10.47 |      |

|        |                          |                                                           | 2 MHz                                        | 0.25  |      |

|        |                          | V <sub>DD</sub> = 3.3 V                                   | 8 MHz                                        | 1.00  |      |

|        |                          | C <sub>EXT</sub> = 22 pF                                  | 25 MHz                                       | 3.45  |      |

|        |                          | $C = C_{INT} + C_{EXT} + C_{S}$                           | 50 MHz                                       | 7.15  |      |

|        |                          |                                                           | 60 MHz                                       | 11.55 |      |

|        |                          |                                                           | 2 MHz                                        | 0.32  |      |

|        |                          | V <sub>DD</sub> = 3.3 V<br>C <sub>EXT</sub> = 33 pF       | 8 MHz                                        | 1.27  |      |

|        |                          | $C = C_{INT} + C_{EXT} + C_S$                             | 25 MHz                                       | 3.88  |      |

|        |                          |                                                           | 50 MHz                                       | 12.34 |      |

Table 38. Switching output I/O current consumption

1. CS is the PCB board capacitance including the pad pin. CS = 7 pF (estimated value).

| Symbol                                  | Parameter                                       | Conditions                                                              |                    | Min                 | Тур  | Max          | Unit |

|-----------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLL_IN</sub>                     | PLL input clock <sup>(1)</sup>                  | -                                                                       |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         |      |

| f <sub>PLLI2SQ_OUT</sub>                | 48 MHz PLLI2SQ<br>multiplier output clock       | -                                                                       | -                  |                     | 48   | 75           | MHz  |

| f <sub>PLLI2SR_OUT</sub>                | PLLI2SR multiplier output clock for I2S and SAI | -                                                                       |                    | -                   | -    | 216          |      |

| f <sub>VCO_OUT</sub>                    | PLLI2S VCO output                               | -                                                                       |                    | 100                 | -    | 432          |      |

| +                                       | PLLI2S lock time                                | VCO freq = 100 MHz                                                      |                    | 75                  | -    | 200          | 110  |

| t <sub>LOCK</sub>                       |                                                 | VCO freq = 432 MHz                                                      |                    | 100                 | -    | 300          | μs   |

|                                         | Master I2S clock jitter                         | Cycle to cycle at                                                       | RMS                | -                   | 90   | -            |      |

|                                         |                                                 | 12.288 MHz on<br>48 kHz period,<br>N=432, R=5                           | peak<br>to<br>peak | -                   | ±280 | -            |      |

| Jitter <sup>(3)</sup>                   |                                                 | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples |                    | -                   | 90   | -            | ps   |

|                                         | WS I2S clock jitter                             | Cycle to cycle at 48 KHz<br>on 1000 samples                             |                    | -                   | 400  | -            |      |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$            | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{DDA}$           | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 |      |

| Table 48. PLLI2S | (audio PLL) | characteristics |

|------------------|-------------|-----------------|

|------------------|-------------|-----------------|

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

#### 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 55*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbo             | Parameter                                                                                                                         | Conditions                                                                                                      | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP144<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 100 MHz,<br>conforms to IEC 61000-4-2 | 1B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP144<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 100 MHz,<br>conforms to IEC 61000-4-4 | 3B              |

Table 54. EMS characteristics for LQFP144 package

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, on LQFP144 packages and PDR\_ON on WLCSP81.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$  maximum) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

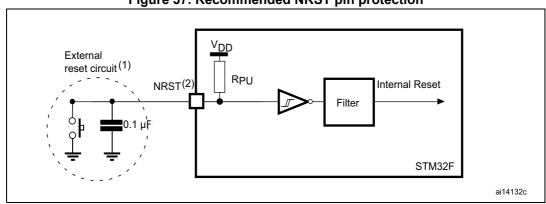

Figure 37. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 62. Otherwise the reset is not taken into account by the device.

#### 6.3.18 TIM timer characteristics

The parameters given in Table 63 are guaranteed by design.

Refer to Section 6.3.16: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                                         | Conditions <sup>(3)</sup>                    | Min    | Мах                     | Unit                 |

|------------------------|-------------------------------------------------------------------|----------------------------------------------|--------|-------------------------|----------------------|

|                        |                                                                   | AHB/APBx prescaler=1                         | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time                                             | or 2 or 4, f <sub>TIMxCLK</sub> =<br>100 MHz | 11.9   | -                       | ns                   |

| Hes(TIM)               |                                                                   | AHB/APBx prescaler>4,                        | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                                                   | f <sub>TIMxCLK</sub> = 100 MHz               | 11.9   | -                       | ns                   |

| f                      | Timer external clock                                              |                                              | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                                           | f <sub>TIMxCLK</sub> = 100 MHz               | 0      | 50                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                                  |                                              | -      | 16/32                   | bit                  |

| t <sub>COUNTER</sub>   | 16-bit counter clock<br>period when internal clock<br>is selected | f <sub>TIMxCLK</sub> = 100 MHz               | 0.0119 | 780                     | μs                   |

| t <sub>MAX_COUNT</sub> | Maximum possible count with 32-bit counter                        | -                                            | -      | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |

| _                      |                                                                   | f <sub>TIMxCLK</sub> = 100 MHz               | -      | 51.1                    | S                    |

Table 63. TIMx characteristics<sup>(1)(2)</sup>

1. TIMx is used as a general term to refer to the TIM1 to TIM11 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 is 50 MHz and on APB2 is up to 100 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCKL, otherwise TIMxCLK >= 4x PCLKx.

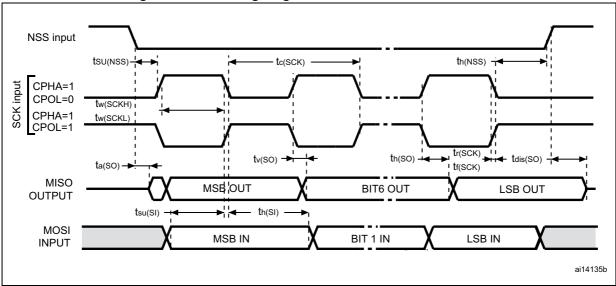

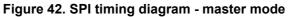

Figure 41. SPI timing diagram - slave mode and CPHA = 1

#### I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 68* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                      | Conditions                             | Min      | Max                     | Unit |

|------------------------|--------------------------------|----------------------------------------|----------|-------------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256 * 8K | 256 * Fs <sup>(2)</sup> | MHz  |

| f <sub>CK</sub>        | 128 clock froguency            | Master data: 32 bits                   | -        | 64 * Fs                 | MHz  |

|                        | I2S clock frequency            | Slave data: 32 bits                    | -        | 64 * Fs                 |      |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30       | 70                      | %    |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | -        | 3.5                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 1.5      | -                       |      |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 2.5      | -                       |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 0.5      | -                       |      |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 3        | -                       |      |

| $t_{su(SD\_SR)}$       |                                | Slave receiver                         | 2.5      | -                       | ns   |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 5        | -                       | 115  |

| t <sub>h(SD_SR)</sub>  | Data input noid time           | Slave receiver                         | 1.5      | -                       |      |

| t <sub>v(SD_ST)</sub>  | Data output valid timo         | Slave transmitter (after enable edge)  | -        | 15                      |      |

| t <sub>v(SD_MT)</sub>  | Data output valid time         | Master transmitter (after enable edge) | -        | 6                       |      |

| t <sub>h(SD_ST)</sub>  | Data output hold time          | Slave transmitter (after enable edge)  | 3.5      | -                       |      |

| t <sub>h(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | 1.5      | _                       |      |

| Table 68. I <sup>2</sup> S dynamic cha | racteristics <sup>(1)</sup> |

|----------------------------------------|-----------------------------|

|----------------------------------------|-----------------------------|

1. Guaranteed by characterization results.

2. The maximum value of 256xFs is 50 MHz (APB1 maximum frequency).

Note: Refer to the I2S section of RM0430 reference manual for more details on the sampling frequency ( $F_{S}$ ).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

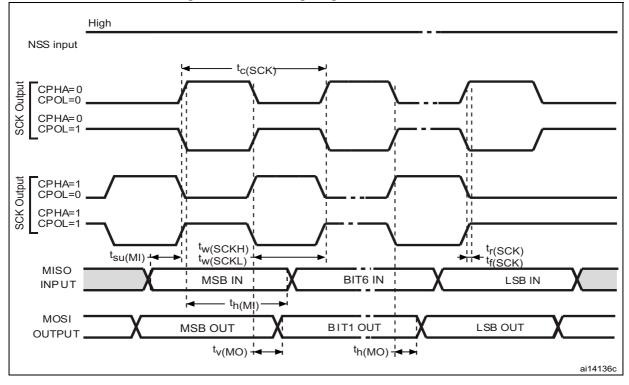

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ,                        | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,                                               | ±1.5 | ±4                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |

Table 77. ADC accuracy at  $f_{ADC} = 30 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $V_{\text{DD}}$ , frequency and temperature ranges.

2. Guaranteed by characterization results.

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |

### Table 78. ADC accuracy at $f_{ADC} = 36 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted V<sub>DD</sub>, frequency and temperature ranges.

2. Guaranteed by characterization results.

| Table 79. ADC dynamic accuracy at f <sub>ADC</sub> = 18 | MHz - limited test conditions <sup>(1)</sup> |

|---------------------------------------------------------|----------------------------------------------|

|---------------------------------------------------------|----------------------------------------------|

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz     | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$ | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 kHz     | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | -    | -72  | -67 |      |

1. Guaranteed by characterization results.

### Table 80. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> = 36 MHz    | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 kHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | -    | -72  | -70 |      |

1. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.16 does not affect the ADC accuracy.

Figure 48. ADC accuracy characteristics

- 1. See also Table 77.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4. End point correlation line.

- 5. E<sub>T</sub> = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

## 6.3.24 DAC electrical characteristics

| Symbol                            | Parameter                                          | Conc          | litions                                               | Min                | Тур | Max                            | Unit | Comments                                                                                                                |

|-----------------------------------|----------------------------------------------------|---------------|-------------------------------------------------------|--------------------|-----|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                  | Analog supply voltage                              | -             |                                                       | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    |                                                                                                                         |

| V <sub>REF+</sub>                 | Reference supply voltage                           |               | -                                                     |                    | -   | 3.6                            | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub>                                                                                     |

| $V_{SSA}$                         | Ground                                             |               | -                                                     | 0                  | -   | 0                              | V    | -                                                                                                                       |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load                                     | DAC<br>output | R <sub>LOAD</sub><br>connected<br>to V <sub>SSA</sub> | 5                  | -   | -                              | kΩ   | -                                                                                                                       |

| NLOAD                             |                                                    | buffer ON     | R <sub>LOAD</sub><br>connected<br>to V <sub>DDA</sub> | 25                 | -   | -                              | kΩ   | -                                                                                                                       |

| R <sub>0</sub> <sup>(2)</sup>     | Impedance output<br>with buffer OFF                | -             |                                                       | -                  | -   | 15                             | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is $1.5\ M\Omega$ |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                    | -             |                                                       | -                  | -   | 50                             | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT<br>voltage with buffer<br>ON         | -             |                                                       | 0.2                | -   | -                              | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input                                  |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT<br>voltage with buffer<br>ON        |               | -                                                     | -                  | -   | V <sub>DDA</sub><br>- 0.2      | V    | code (0x0E0) to (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V and (0x1C7) to<br>(0xE38) at V <sub>REF+</sub> = 1.7 V          |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT<br>voltage with buffer<br>OFF        |               | -                                                     | -                  | 0.5 | _                              | mV   | It gives the maximum output                                                                                             |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT<br>voltage with buffer<br>OFF       |               | -                                                     | -                  | -   | V <sub>REF+</sub><br>_<br>1LSB | V    | excursion of the DAC.                                                                                                   |

| . (4)                             | DAC DC V <sub>REF</sub><br>current                 | -             |                                                       | -                  | 170 | 240                            |      | With no load, worst code (0x800)<br>at V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

| I <sub>VREF+</sub> <sup>(4)</sup> | consumption in<br>quiescent mode<br>(Standby mode) |               |                                                       | -                  | 50  | 75                             | μA   | With no load, worst code (0xF1C)<br>at V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

|                                   | DAC DC VDDA<br>current                             | -             |                                                       | -                  | 280 | 380                            | μA   | With no load, middle code<br>(0x800) on the inputs                                                                      |

| I <sub>DDA</sub> <sup>(4)</sup>   | consumption in quiescent mode <sup>(3)</sup>       |               | -                                                     | -                  | 475 | 625                            | μA   | With no load, worst code (0xF1C)<br>at $V_{REF+}$ = 3.6 V in terms of DC<br>consumption on the inputs                   |

#### Table 86. DAC characteristics

| Symbol                                         | Parameter                                                | Conditions                                                                                                                      | Min                                       | Тур                   | Мах                                        | Unit |

|------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|--------------------------------------------|------|

| t <sub>wh(CKIN)</sub><br>t <sub>wl(CKIN)</sub> | Input clock high<br>and low time                         | SPI mode<br>(SITP[1:0] = 01),<br>External clock mode<br>(SPICKSEL[1:0] = 0)<br>1.71 < V <sub>DD</sub> < 3.6 V                   | t <sub>CKIN</sub> / 2 - 0.5               | t <sub>CKIN</sub> / 2 | -                                          |      |

| t <sub>su</sub>                                | Data input<br>setup time                                 | SPI mode<br>(SITP[1:0]=01),<br>External clock mode<br>(SPICKSEL[1:0] = 0)<br>1.71 < V <sub>DD</sub> < 3.6 V                     | 3.5                                       | -                     | -                                          |      |

| t <sub>n</sub>                                 | Data input hold<br>time                                  | SPI mode<br>(SITP[1:0]=01),<br>External clock mode<br>(SPICKSEL[1:0] = 0)<br>1.71 < V <sub>DD</sub> < 3.6 V                     | 2.5                                       | -                     | -                                          | ns   |

| T <sub>Manchester</sub>                        | Manchester<br>data period<br>(recovered<br>clock period) | Manchester mode<br>(SITP[1:0] = 10 or 11),<br>Internal clock mode<br>(SPICKSEL[1:0] $\neq$ 0)<br>1.71 < V <sub>DD</sub> < 3.6 V | (CKOUTDIV + 1)<br>* t <sub>DFBDMCLK</sub> | -                     | (2 * CKOUTDIV<br>) * t <sub>DFBDMCLK</sub> |      |

Table 87. DFSDM characteristics<sup>(1)</sup> (continued)

1. Data based on characterization results.

| puoliago moonamour auta |       |             |       |        |                       |                    |  |

|-------------------------|-------|-------------|-------|--------|-----------------------|--------------------|--|

| Cumb al                 |       | millimeters |       |        | inches <sup>(1)</sup> | 1es <sup>(1)</sup> |  |

| Symbol                  | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.               |  |

| А                       | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236             |  |

| A1                      | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020             |  |

| D                       | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795             |  |

| E                       | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795             |  |

| D2                      | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244             |  |

| E2                      | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244             |  |

| L                       | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197             |  |

| Т                       | -     | 0.152       | -     | -      | 0.0060                | -                  |  |

| b                       | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118             |  |

| е                       | -     | 0.500       | -     | -      | 0.0197                | -                  |  |

| ddd                     | -     | -           | 0.080 | -      | -                     | 0.0031             |  |

## Table 105. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

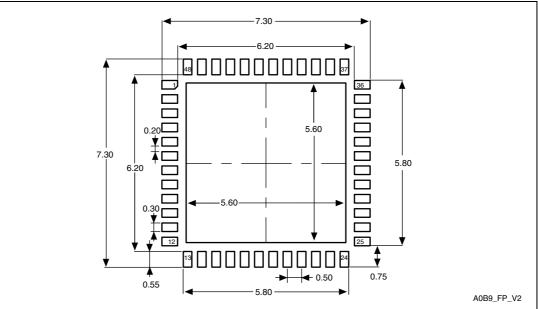

#### Figure 67. UFQFPN48 recommended footprint

1. Dimensions are in millimeters.

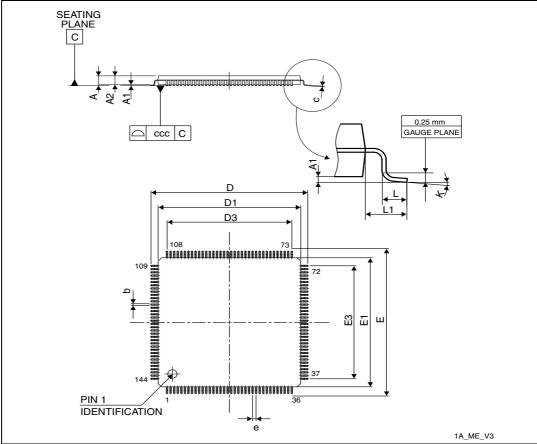

## 7.5 LQFP144 package information

Figure 75. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

## Table 111. UFBGA144 - 144-ball, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball gridarray package mechanical data (continued)

|        |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |

| F      | 0.550 | 0.600       | 0.650 | 0.0177 | 0.0197                | 0.0217 |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0039 |

| eee    | -     | -           | 0.150 | -      | -                     | 0.0059 |

| fff    | -     | -           | 0.080 | -      | -                     | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

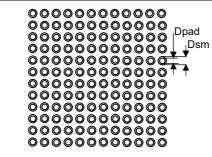

## Figure 82. UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball grid array recommended footprint

A02Y\_FP\_V1

#### Table 112. UFBGA144 recommended PCB design rules (0.80 mm pitch BGA)

| Dimension | Recommended values                                               |

|-----------|------------------------------------------------------------------|

| Pitch     | 0.80 mm                                                          |

| Dpad      | 0.400 mm                                                         |

| Dsm       | 0.550 mm typ. (depends on the soldermask registration tolerance) |

Note:

4 to 6 mils solder paste screen printing process. Stencil opening is 0.400 mm. Stencil thickness is between 0.100 mm and 0.125 mm. Pad trace width is 0.120 mm.

Non solder mask defined (NSMD) pads are recommended.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID029162 Rev 4