#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                         |

|----------------------------|------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Speed                      | 100MHz                                                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SDIO, QSPI, SAI, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                              |

| Number of I/O              | 114                                                                                            |

| Program Memory Size        | 1.5MB (1.5M × 8)                                                                               |

| Program Memory Type        | FLASH                                                                                          |

| EEPROM Size                | -                                                                                              |

| RAM Size                   | 320K x 8                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                    |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                          |

| Oscillator Type            | Internal                                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                  |

| Package / Case             | 144-LQFP                                                                                       |

| Supplier Device Package    | 144-LQFP (20x20)                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f413zht3                          |

|                            |                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.22  | Timers   | and watchdogs                                              | 33 |

|-------|----------|------------------------------------------------------------|----|

|       | 3.22.1   | Advanced-control timers (TIM1, TIM8)                       | 34 |

|       | 3.22.2   | General-purpose timers (TIMx)                              | 34 |

|       | 3.22.3   | Basic timer (TIM6, TIM7)                                   | 35 |

|       | 3.22.4   | Low-power timer (LPTIM1)                                   | 35 |

|       | 3.22.5   | Independent watchdog                                       |    |

|       | 3.22.6   | Window watchdog                                            |    |

|       | 3.22.7   | SysTick timer                                              |    |

| 3.23  | Inter-in | tegrated circuit interface (I2C)                           | 36 |

| 3.24  | Univers  | sal synchronous/asynchronous receiver transmitters (USART) | 36 |

| 3.25  | Serial p | peripheral interface (SPI)                                 | 38 |

| 3.26  | Inter-in | tegrated sound (I <sup>2</sup> S)                          | 38 |

| 3.27  | Serial / | Audio interface (SAI1)                                     | 38 |

| 3.28  | Audio I  | PLL (PLLI2S)                                               | 38 |

| 3.29  | Digital  | filter for sigma-delta modulators (DFSDM)                  | 39 |

| 3.30  | Dynam    | ic tuning of PDM delays for sound source localization      | 39 |

| 3.31  | Secure   | e digital input/output interface (SDIO)                    | 40 |

| 3.32  | Contro   | ller area network (bxCAN)                                  | 40 |

| 3.33  | Univers  | sal serial bus on-the-go full-speed (USB_OTG_FS)           | 40 |

| 3.34  | Rando    | m number generator (RNG)                                   | 41 |

| 3.35  | Genera   | al-purpose input/outputs (GPIOs)                           | 41 |

| 3.36  | Analog   | -to-digital converter (ADC)                                | 41 |

| 3.37  | Digital  | to analog converter (DAC)                                  | 41 |

| 3.38  | Tempe    | rature sensor                                              | 42 |

| 3.39  | Serial v | wire JTAG debug port (SWJ-DP)                              | 42 |

| 3.40  | Embed    | lded Trace Macrocell™                                      | 42 |

| Pinou | uts and  | pin description                                            | 43 |

| Memo  | ory ma   | oping                                                      | 75 |

| Elect | rical ch | aracteristics                                              | 79 |

| 6.1   | Param    | eter conditions                                            | 79 |

| -     | 6.1.1    | Minimum and maximum values                                 |    |

|       |          |                                                            |    |

4

5

6

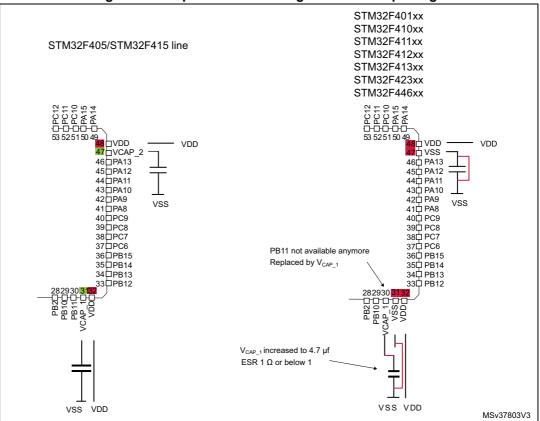

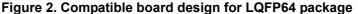

Figure 3. Compatible board design for LQFP144 package

A dedicated application note (AN4515) describes how to implement the STM32F413xG/H BAM to allow the best power efficiency.

# 3.4 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 byte and the whole 4 Gbyte of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

## 3.5 Embedded Flash memory

The devices embed up to 1.5 Mbytes of Flash memory available for storing programs and data, plus 512 bytes of one-time programmable (OTP) memory organized in 16 blocks of 32 bytes, each which can be independently locked.

The user Flash memory area can be protected against read operations by an entrusted code (read protection or RDP). Different protection levels are available. The user Flash memory is divided into sectors, which can be individually protected against write operation. Flash sectors can also be protected individually against D-bus read accesses by using the proprietary readout protection (PCROP).

Refer to the product line reference manual for additional information on OTP area and protection features.

To optimize the power consumption the Flash memory can also be switched off in Run or in Sleep mode (see Section 3.20: Low-power modes).

Two modes are available: Flash in Stop mode or in DeepSleep mode (trade off between power saving and startup time.

Before disabling the Flash, the code must be executed from the internal RAM.

# 3.6 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

Different sources can also be selected for the SAI. The different possible sources are the main PLL, the PLLI2S, HSE or HSI clocks or an external clock provided through a pin (external PLL or CODEC output).

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

## 3.29 Digital filter for sigma-delta modulators (DFSDM)

The device embeds two DFSDMs:

- DFSDM1 has 2 digital filters modules and 4 external input serial channels (transceivers) or alternately 2 internal parallel inputs support.

- DFSDM2 features 4 digital filters modules and 8 external input serial channels (transceivers) or alternately 4 internal parallel inputs support.

The DFSDM peripheral is dedicated to interface the external  $\Sigma\Delta$  modulators to microcontroller and then to perform digital filtering of the received data streams (which represent analog value on  $\Sigma\Delta$  modulators inputs). DFSDM can also interface PDM (Pulse Density Modulation) microphones and perform PDM to PCM conversion and filtering in hardware. It is also possible to introduce a programmable delay between different microphones (beamforming feature). DFSDM features optional parallel data stream inputs from microcontrollers memory (through DMA/CPU transfers into DFSDM).

DFSDM transceivers support several serial interface formats (to support various  $\Sigma\Delta$  modulators). DFSDM digital filter modules perform digital processing according user selected filter parameters with up to 24-bit final ADC resolution.

|                |                                | =                                |                 |

|----------------|--------------------------------|----------------------------------|-----------------|

| DFSDM instance | External input serial channels | External input parallel channels | Digital filters |

| DFSDM1         | 4                              | 2                                | 2               |

| DFSDM2         | 8                              | 4                                | 4               |

Table 8. DFSDM feature comparison

3.30 Dynamic tuning of PDM delays for sound source localization

A mechanism is implemented on top of the DFSDM allowing to dynamically tune PDM delays of each microphone without the need to add external delay lines.

Audio application with several microphones require strong microphones placement constraints, as the distance between the microphones must be a multiple of v/F where v is the speed of the sound and F is the PCM sampling frequency.

The designed mechanism removes this constraint by programming delays for each digital microphone with the granularity of the PDM clock rate prior to the conversion into PCM rate.

The tuning delay is performed by a clock skipping technique.

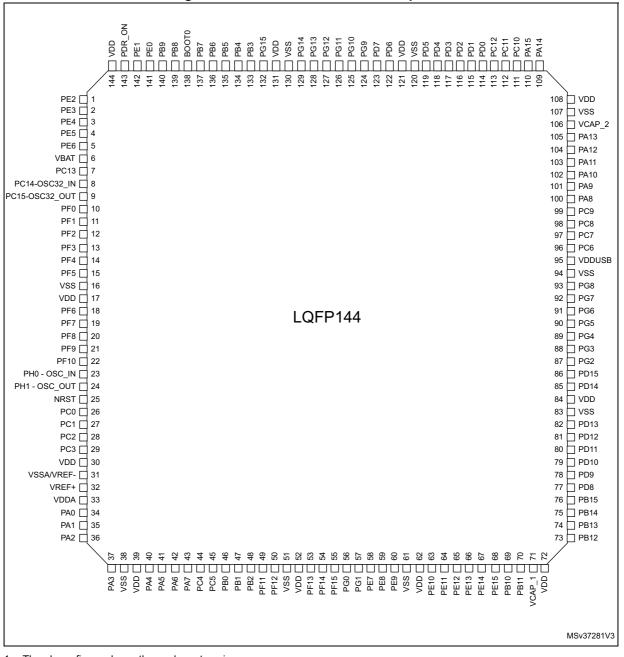

#### Figure 15. STM32F413xG/H LQFP144 pinout

1. The above figure shows the package top view.

|   |                    |      | -   |     |                |      |        |      |        |      |        |         |

|---|--------------------|------|-----|-----|----------------|------|--------|------|--------|------|--------|---------|

|   | 1                  | 2    | 3   | 4   | 5              | 6    | 7      | 8    | 9      | 10   | 11     | 12      |

| Α | PC13               | PE3  | PE2 | PE1 | PE0            | PB4  | PB3    | PD6  | PD7    | PA15 | PA14   | PA13    |

| в | PC14-<br>OSC32_IN  | PE4  | PE5 | PE6 | PB9            | PB5  | PG15   | PG12 | PD5    | PC11 | PC10   | PA12    |

| с | PC15-<br>OSC32_OUT | VBAT | PF0 | PF1 | PB8            | PB6  | PG14   | PG11 | PD4    | PC12 | VDDUSB | PA11    |

| D | PH0 -<br>OSC_IN    | vss  | VDD | PF2 | BOOTO          | PB7  | PG13   | PG10 | PD3    | PD1  | PA10   | PA9     |

| E | PH1 -<br>OSC_OUT   | PF3  | PF4 | PF5 | PDR_ON         | vss  | vss    | PG9  | PD2    | PD0  | PC9    | PA8     |

| F | NRST               | PF7  | PF6 | VDD | VDD            | VDD  | VDD    | VDD  | VDD    | VDD  | PC8    | PC7     |

| G | PF10               | PF9  | PF8 | VSS | VDD            | VDD  | VDD    | vss  | VCAP_2 | vss  | PG8    | PC6     |

| н | PC0                | PC1  | PC2 | PC3 | BYPASS_<br>REG | VSS  | VCAP_1 | PE11 | PD11   | PG7  | PG6    | PG5     |

| J | VSSA               | PA0  | PA4 | PC4 | PB2            | PG1  | PE10   | PE12 | PD10   | PG4  | PG3    | PG2     |

| к | VREF-              | PA1  | PA5 | PC5 | PF13           | PG0  | PE9    | PE13 | PD9    | PD13 | PD14   | PD15    |

| L | VREF+              | PA2  | PA6 | PB0 | PF12           | PF15 | PE8    | PE14 | PD8    | PD12 | PB14   | PB15    |

| м | VDDA               | PA3  | PA7 | PB1 | PF11           | PF14 | PE7    | PE15 | PB10   | PB11 | PB12   | PB13    |

|   |                    |      |     |     |                |      |        | •    |        |      |        | MSv3728 |

#### Figure 17. STM32F413xG/H UFBGA144 pinout

1. The above figure shows the package top view.

## Table 9. Legend/abbreviations used in the pinout table

| Name                   | Abbreviation       | Definition                                                                                         |  |  |  |

|------------------------|--------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| Pin name               |                    | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |

|                        | S                  | Supply pin                                                                                         |  |  |  |

| Pin type               | I                  | Input only pin                                                                                     |  |  |  |

|                        | I/O                | Input/ output pin                                                                                  |  |  |  |

|                        | FT                 | 5 V tolerant I/O                                                                                   |  |  |  |

|                        | FTf                | 5 V tolerant I/O, I2C FM+ option                                                                   |  |  |  |

| I/O structure          | TC                 | Standard 3.3 V I/O                                                                                 |  |  |  |

| NO STRUCTURE           | ТТа                | 3.3 V tolerant I/O directly connected to DAC                                                       |  |  |  |

|                        | В                  | Dedicated BOOT0 pin                                                                                |  |  |  |

|                        | NRST               | Bidirectional reset pin with embedded weak pull-up resistor                                        |  |  |  |

| Notes                  | Unless otherwise   | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |

| Alternate<br>functions | Functions selected | d through GPIOx_AFR registers                                                                      |  |  |  |

| Additional functions   | Functions directly | selected/enabled through peripheral registers                                                      |  |  |  |

| Pin Number |        |         |         |          |          |         |                                                         |             |                  |       |                                                                                                                                             |                         |

|------------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48   | LQFP64 | WLCSP81 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                                                                         | Additional<br>functions |

| -          | -      | NC      | 62      | H10      | K12      | 86      | PD15                                                    | I/O         | FTf              | (2)   | TIM4_CH4,<br>I2CFMP1_SDA,<br>DFSDM2_DATIN0,<br>UART9_TX,<br>FSMC_D1/FSMC_DA1,<br>EVENTOUT                                                   | -                       |

| -          | -      | -       | -       | -        | J12      | 87      | PG2                                                     | I/O         | FT               | -     | FSMC_A12,<br>EVENTOUT                                                                                                                       | -                       |

| -          | -      | -       | -       | -        | J11      | 88      | PG3                                                     | I/O         | FT               | -     | FSMC_A13,<br>EVENTOUT                                                                                                                       | -                       |

| -          | -      | -       | -       | -        | J10      | 89      | PG4                                                     | I/O         | FT               | -     | FSMC_A14,<br>EVENTOUT                                                                                                                       | -                       |

| -          | -      | -       | -       | -        | H12      | 90      | PG5                                                     | I/O         | FT               | -     | FSMC_A15,<br>EVENTOUT                                                                                                                       | -                       |

| -          | -      | -       | -       | -        | H11      | 91      | PG6                                                     | I/O         | FT               | -     | QUADSPI_BK1_NCS,<br>EVENTOUT                                                                                                                | -                       |

| -          | -      | -       | -       | -        | H10      | 92      | PG7                                                     | I/O         | FT               | -     | USART6_CK,<br>EVENTOUT                                                                                                                      | -                       |

| -          | -      | -       | -       | -        | G11      | 93      | PG8                                                     | I/O         | FT               | -     | USART6_RTS,<br>EVENTOUT                                                                                                                     | -                       |

| -          | -      | -       | -       | -        | -        | 94      | VSS                                                     | S           | -                | -     | -                                                                                                                                           | -                       |

| -          | -      | -       | -       | -        | F10      | -       | VDD                                                     | S           | -                | -     | -                                                                                                                                           | -                       |

| -          | -      | F1      | -       | -        | C11      | 95      | VDDUSB                                                  | S           | -                | -     | -                                                                                                                                           | -                       |

| -          | 37     | D5      | 63      | E12      | G12      | 96      | PC6                                                     | I/O         | FTf              | -     | TIM3_CH1, TIM8_CH1,<br>I2CFMP1_SCL,<br>I2S2_MCK,<br>DFSDM1_CKIN3,<br>DFSDM2_DATIN6,<br>USART6_TX,<br>FSMC_D1/FSMC_DA1,<br>SDIO_D6, EVENTOUT | -                       |

| -          | 38     | D4      | 64      | E11      | F12      | 97      | PC7                                                     | I/O         | FTf              | -     | TIM3_CH2, TIM8_CH2,<br>I2CFMP1_SDA,<br>SPI2_SCK/I2S2_CK,<br>I2S3_MCK,<br>DFSDM2_CKIN6,<br>USART6_RX,<br>DFSDM1_DATIN3,<br>SDIO_D7, EVENTOUT | -                       |

Table 10. STM32F413xG/H pin definition (continued)

| Pin Number |        |         |         |          |          |         |                                                         |             |                  |       |                                                                                                                                                 |                         |

|------------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48   | LQFP64 | WLCSP81 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                                                                             | Additional<br>functions |

| 41         | 57     | A6      | 91      | C5       | B6       | 135     | PB5                                                     | I/O         | FT               | -     | LPTIM1_IN1,<br>TIM3_CH2,<br>I2C1_SMBA,<br>SPI1_MOSI/I2S1_SD,<br>SPI3_MOSI/I2S3_SD,<br>CAN2_RX, SAI1_FS_A,<br>UART5_RX, SDI0_D3,<br>EVENTOUT     | -                       |

| 42         | 58     | B6      | 92      | B5       | C6       | 136     | PB6                                                     | I/O         | FT               | -     | LPTIM1_ETR,<br>TIM4_CH1, I2C1_SCL,<br>DFSDM2_CKIN7,<br>USART1_TX, CAN2_TX,<br>QUADSPI_BK1_NCS,<br>UART5_TX, SDI0_D0,<br>EVENTOUT                | -                       |

| 43         | 59     | B7      | 93      | B4       | D6       | 137     | PB7                                                     | I/O         | FT               | -     | LPTIM1_IN2,<br>TIM4_CH2, I2C1_SDA,<br>DFSDM2_DATIN7,<br>USART1_RX,<br>FSMC_NL, EVENTOUT                                                         | -                       |

| 44         | 60     | A7      | 94      | A4       | D5       | 138     | BOOT0                                                   | Т           | В                | -     | -                                                                                                                                               | VPP                     |

| 45         | 61     | C6      | 95      | A3       | C5       | 139     | PB8                                                     | I/O         | FT               | -     | LPTIM1_OUT,<br>TIM4_CH3, TIM10_CH1,<br>I2C1_SCL,<br>SPI5_MOSI/I2S5_SD,<br>DFSDM2_CKIN1,<br>CAN1_RX, I2C3_SDA,<br>UART5_RX, SDI0_D4,<br>EVENTOUT | -                       |

| 46         | 62     | D6      | 96      | В3       | В5       | 140     | PB9                                                     | I/O         | FT               | -     | TIM4_CH4, TIM11_CH1,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS,<br>DFSDM2_DATIN1,<br>CAN1_TX, I2C2_SDA,<br>UART5_TX, SDIO_D5,<br>EVENTOUT                | -                       |

| -          | -      | NC      | 97      | C3       | A5       | 141     | PE0                                                     | I/O         | FT               | (2)   | TIM4_ETR,<br>DFSDM2_CKIN4,<br>UART8_Rx,<br>FSMC_NBL0,<br>EVENTOUT                                                                               | -                       |

| -          | -      | NC      | 98      | A2       | A4       | 142     | PE1                                                     | I/O         | FT               | (2)   | DFSDM2_DATIN4,<br>UART8_Tx,<br>FSMC_NBL1,<br>EVENTOUT                                                                                           | -                       |

| 47         | 63     | A8      | 99      | D3       | E6       | -       | VSS                                                     | S           | -                | -     | -                                                                                                                                               | -                       |

Table 10. STM32F413xG/H pin definition (continued)

| Bus  | Boundary address          | Peripheral |

|------|---------------------------|------------|

|      | 0x4001 6800- 0x4001 FFFF  | Reserved   |

|      | 0x4001 6400 - 0x4001 67FF | DFSDM2     |

|      | 0x4001 6000 - 0x4001 63FF | DFSDM1     |

|      | 0x4001 5C00 - 0x4001 5FFF | Reserved   |

|      | 0x4001 5800 - 0x4001 5BFF | SAI1       |

|      | 0x4001 5400 - 0x4001 57FF | Reserved   |

|      | 0x4001 5000 - 0x4001 53FF | SPI5/I2S5  |

|      | 0x4001 4C00 - 0x4001 4FFF | Reserved   |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11      |

|      | 0x4001 4400 - 0x4001 47FF | TIM10      |

|      | 0x4001 4000 - 0x4001 43FF | ТІМ9       |

|      | 0x4001 3C00 - 0x4001 3FFF | EXTI       |

| APB2 | 0x4001 3800 - 0x4001 3BFF | SYSCFG     |

|      | 0x4001 3400 - 0x4001 37FF | SPI4/I2S4  |

|      | 0x4001 3000 - 0x4001 33FF | SPI1/I2S1  |

|      | 0x4001 2C00 - 0x4001 2FFF | SDIO       |

|      | 0x4001 2400 - 0x4001 2BFF | Reserved   |

|      | 0x4001 2000 - 0x4001 23FF | ADC1/2/3   |

|      | 0x4001 1C00 - 0x4001 1FFF | UART10     |

|      | 0x4001 1800 - 0x4001 1BFF | UART9      |

|      | 0x4001 1400 - 0x4001 17FF | USART6     |

|      | 0x4001 1000 - 0x4001 13FF | USART1     |

|      | 0x4001 0800 - 0x4001 0FFF | Reserved   |

|      | 0x4001 0400 - 0x4001 07FF | ТІМ8       |

|      | 0x4001 0000 - 0x4001 03FF | TIM1       |

| Symbol          | Parameter                                                     | Conditions                                                 | Min                    | Тур | Мах | Unit |  |  |  |  |

|-----------------|---------------------------------------------------------------|------------------------------------------------------------|------------------------|-----|-----|------|--|--|--|--|

|                 | Input voltage on                                              | $2 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ | -0.3                   | -   | 5.5 |      |  |  |  |  |

| V               | RST, FT and TC pins <sup>(7)</sup>                            | $V_{DD} \le 2 V$                                           | -0.3                   | -   | 5.2 | v    |  |  |  |  |

| V <sub>IN</sub> | Input voltage on TTa pins                                     | -                                                          | V <sub>DDA</sub> + 0.3 | v   |     |      |  |  |  |  |

|                 | Input voltage on BOOT0 pin                                    | -                                                          | 0                      | -   | 9   | 1    |  |  |  |  |

|                 |                                                               | UFQFPN48                                                   | -                      | -   | 625 |      |  |  |  |  |

| PD              |                                                               | WLCSP81                                                    | -                      | -   | 504 |      |  |  |  |  |

|                 | Power dissipation at                                          | LQFP64                                                     | -                      | -   | 426 |      |  |  |  |  |

|                 | TA = 85°C for range 6 or                                      | LQFP100                                                    | -                      | -   | 465 |      |  |  |  |  |

|                 | TA = $105^{\circ}$ C for range $7^{(8)}$                      | LQFP144                                                    |                        | -   | 571 |      |  |  |  |  |

|                 |                                                               | UFBGA100                                                   | -                      | -   | 351 |      |  |  |  |  |

|                 |                                                               | UFBGA144                                                   | -                      | -   | 417 |      |  |  |  |  |

|                 |                                                               | UFQFPN48                                                   | -                      | -   | 156 | mW   |  |  |  |  |

|                 |                                                               | WLCSP81                                                    | -                      | -   | 126 |      |  |  |  |  |

|                 |                                                               | LQFP64                                                     | -                      | -   | 106 |      |  |  |  |  |

|                 | Power dissipation at<br>TA = 125°C for range 3 <sup>(8)</sup> | LQFP100                                                    | -                      | -   | 116 |      |  |  |  |  |

|                 |                                                               | LQFP144                                                    | -                      | -   | 143 |      |  |  |  |  |

|                 |                                                               | UFBGA100                                                   | -                      | -   | 088 | _    |  |  |  |  |

|                 |                                                               | UFBGA144                                                   | -                      | -   | 104 |      |  |  |  |  |

|                 | Ambient temperature for                                       | Maximum power dissipation                                  | -40                    | -   | 85  |      |  |  |  |  |

|                 | range 6                                                       | Low power dissipation <sup>(9)</sup>                       | -40                    | -   | 105 |      |  |  |  |  |

| Τ.              | Ambient temperature for                                       | Maximum power dissipation                                  | -40                    | -   | 105 |      |  |  |  |  |

| ΤΑ              | range 7                                                       | Low power dissipation <sup>(9)</sup>                       | -40                    | -   | 125 | 1    |  |  |  |  |

|                 | Ambient temperature for                                       | Maximum power dissipation                                  | -40                    | -   | 125 | °C   |  |  |  |  |

|                 | range 3                                                       | Low power dissipation <sup>(9)</sup>                       | -40                    | -   | 130 | 1    |  |  |  |  |

|                 |                                                               | Range 6                                                    | -40                    | -   | 105 | 1    |  |  |  |  |

| TJ              | Junction temperature range                                    | Range 7                                                    | -40                    | -   | 125 | 1    |  |  |  |  |

|                 |                                                               | Range 3                                                    | -40                    | -   | 130 | 1    |  |  |  |  |

|                 |                                                               | -                                                          |                        |     |     |      |  |  |  |  |

1. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

2. When the ADC is used, refer to Table 75: ADC characteristics.

3. If  $V_{REF+}$  pin is present, it must respect the following condition:  $V_{DDA}-V_{REF}+ < 1.2$  V.

4. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and power-down operation.

Only the DM (P<sub>A11</sub>) and DP (P<sub>A12</sub>) pads are supplied through V<sub>DDUSB</sub>. For application where the V<sub>BUS</sub> (P<sub>A9</sub>) is directly connected to the chip, a minimum V<sub>DD</sub> supply of 2.7V is required. (some application examples are shown in appendix B)

6. Guaranteed by test in production

7. To sustain a voltage higher than  $V_{DD}$ +0.3, the internal Pull-up and Pull-Down resistors must be disabled

## Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at VDD or VSS (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to both f<sub>HCLK</sub> frequency and VDD ranges (refer to *Table 18: Features depending on the operating power supply range*).

- The voltage scaling is adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 64$  MHz

- Scale 2 for 64 MHz <  $f_{HCLK} \le 84$  MHz

- Scale 1 for 84 MHz <  $f_{HCLK} \le 100$  MHz

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/2$ , and  $f_{PCLK2} = f_{HCLK}$ .

- External clock is 4 MHz and PLL is ON except if it is explicitly mentioned.

- The maximum values are obtained for  $V_{DD}$  = 3.6 V and a maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

| Table 23. Typical and maximum current consumption, code with data processing (ART accelerator disabled) running from SRAM - V <sub>DD</sub> = 1.7 V |  |  |  |     |                    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|-----|--------------------|--|--|--|

|                                                                                                                                                     |  |  |  | Typ | Max <sup>(1)</sup> |  |  |  |

| Question        | Demonster                               | Conditions                                   | f <sub>HCLK</sub> | Тур                    |                        | Ma                    | ax <sup>(1)</sup>      |                        | Unit |

|-----------------|-----------------------------------------|----------------------------------------------|-------------------|------------------------|------------------------|-----------------------|------------------------|------------------------|------|

| Symbol          | Parameter                               | Conditions                                   | (MHz)             | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 25 °C | T <sub>A</sub> =85 °C | T <sub>A</sub> =105 °C | T <sub>A</sub> =125 °C | Unit |

|                 |                                         |                                              | 100               | 32.9                   | 34.96                  | 35.30                 | 37.21                  | 40.79                  |      |

|                 |                                         | External clock,                              | 84                | 26.5                   | 28.13                  | 28.58                 | 30.50                  | 33.96                  |      |

|                 |                                         | PLL ON,                                      | 64                | 18.3                   | 19.44                  | 20.11                 | 21.76                  | 25.03                  |      |

|                 |                                         | all peripherals<br>enabled <sup>(2)(3)</sup> | 50                | 14.4                   | 15.28                  | 16.12                 | 17.95                  | 21.11                  |      |

|                 |                                         |                                              | 25                | 7.5                    | 8.10                   | 9.35                  | 11.09                  | 96 13.17               |      |

|                 |                                         |                                              | 20                | 6.4                    | 6.99                   | 8.17                  | 9.96                   | 13.17                  |      |

|                 | Supply<br>current in<br><b>Run mode</b> | HSI, PLL off, all                            | 16                | 4.6                    | 5.17                   | 6.42                  | 8.28                   | 11.46                  |      |

|                 |                                         | peripherals<br>enabled <sup>(2)(3)</sup>     | 1                 | 0.7                    | 1.28                   | 2.64                  | 4.30                   | 7.66                   | m۸   |

| I <sub>DD</sub> |                                         |                                              | 100               | 15.4                   | 16.43                  | 17.35                 | 19.17                  | 22.85                  | ШA   |

|                 |                                         | External clock.                              | 84                | 12.4                   | 13.28                  | 14.32                 | 16.12                  | 19.67                  |      |

|                 |                                         | PLL ON, all                                  | 64                | 8.7                    | 9.36                   | 10.38                 | 12.06                  | 15.31                  |      |

|                 |                                         | peripherals<br>disabled <sup>(3)</sup>       | 50                | 6.9                    | 7.47                   | 8.54                  | 10.36                  | 13.49                  |      |

|                 |                                         | disabled                                     | 25                | 3.7                    | 4.27                   | 5.47                  | 7.17                   | 10.45                  | - mA |

|                 |                                         |                                              | 20                | 3.2                    | 3.72                   | 5.01                  | 6.67                   | 10.02                  |      |

|                 |                                         | HSI, PLL off, all                            | 16                | 2.3                    | 2.80                   | 4.05                  | 5.90                   | 9.07                   |      |

|                 |                                         | peripherals<br>disabled <sup>(3)</sup>       | 1                 | 0.6                    | 1.14                   | 2.51                  | 4.16                   | 7.51                   |      |

1. Guaranteed by characterization results.

2. When analog peripheral blocks such as ADC, HSE, LSE, HSI, or LSI are ON, an additional power consumption has to be considered.

|        |                                                          |                                                         | Typ <sup>(1)</sup>        | p <sup>(1)</sup> Max <sup>(2)</sup> |                          |                            |                            |      |

|--------|----------------------------------------------------------|---------------------------------------------------------|---------------------------|-------------------------------------|--------------------------|----------------------------|----------------------------|------|

| Symbol | Parameter                                                | Conditions                                              | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C           | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|        |                                                          | Low-speed oscillator (LSE in low drive mode) and RTC ON | 3.7                       | 5.2                                 | 20.6                     | 40.5                       | 82.7                       |      |

|        | Low-speed oscillator (LSE in high drive mode) and RTC ON | 4.5                                                     | 6.0                       | 21.4                                | 41.3                     | 83.5                       | μA                         |      |

|        |                                                          | RTC and LSE OFF                                         | 2.5                       | 4.0                                 | 19.4                     | 39.3                       | 81.5 <sup>(3)</sup>        |      |

## Table 36. Typical and maximum current consumption in Standby mode - $V_{\text{DD}}\text{=}$ 3.6 V

1. When the PDR is OFF (internal reset is OFF), the typical current consumption is reduced by 1.2  $\mu$ A.

2. Guaranteed by characterization, not tested in production unless otherwise specified.

3. Tested in production.

|                 |           |                                                            |                             | Ту                          | ур                          |                             | Max <sup>(2)</sup>       |                            |                            |      |

|-----------------|-----------|------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--------------------------|----------------------------|----------------------------|------|

| Symbol          | Parameter | Conditions <sup>(1)</sup>                                  |                             | T <sub>A</sub> =            | 25 °C                       |                             | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | T <sub>A</sub> =<br>125 °C | Unit |

|                 |           |                                                            | V <sub>BAT</sub> =<br>1.7 V | V <sub>BAT</sub> =<br>2.4 V | V <sub>BAT</sub> =<br>3.3 V | V <sub>BAT</sub> =<br>3.6 V | V <sub>E</sub>           | <sub>BAT</sub> = 3.6       | 6 V                        |      |

| Backup          |           | Low-speed oscillator (LSE in<br>low-drive mode) and RTC ON | 0.74                        | 0.84                        | 1.04                        | 1.24                        | 3.00                     | 5.00                       | 10.00                      |      |

| IDD_VBAT supply |           | Low-speed oscillator (LSE in high-drive mode) and RTC ON   | 1.51                        | 1.64                        | 1.89                        | 2.00                        | 3.80                     | 5.80                       | 11.60                      | μA   |

|                 |           | RTC and LSE OFF                                            | 0.03                        | 0.03                        | 0.04                        | 0.04                        | 2.00                     | 4.00                       | 8.00                       |      |

## Table 37. Typical and maximum current consumptions in $\mathrm{V}_{\mathrm{BAT}}$ mode

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a  $\rm C_L$  of 6 pF for typical values.

2. Guaranteed by characterization results.

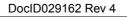

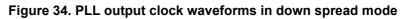

*Figure 33* and *Figure 34* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

$T_{mode}$  is the modulation period.

md is the modulation depth.

## 6.3.12 Memory characteristics

## **Flash memory**

The characteristics are given at  $T_A$  = -40 to 125 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Table 50. | Flash   | memory     | characteristics |

|-----------|---------|------------|-----------------|

|           | 1 10311 | Including. | Characteristics |

| Symbol                         | Parameter      | Conditions                                         | Min | Тур | Мах | Unit |

|--------------------------------|----------------|----------------------------------------------------|-----|-----|-----|------|

|                                |                | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V         | -   | 5   | -   |      |

| I <sub>DD</sub> Supply current | Supply current | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V        | -   | 8   | -   | mA   |

|                                |                | Write / Erase 32-bit mode, V <sub>DD</sub> = 3.3 V | -   | 12  | -   |      |

DocID029162 Rev 4

# FMPI<sup>2</sup>C characteristics

The following table presents FMPI<sup>2</sup>C characteristics.

Refer also to Section 6.3.16: I/O port characteristics for more details on the input/output function characteristics (SDA and SCL).

|                    |                                                                                                        | Standar | d mode | Fast | mode | Fast+ | mode               |      |

|--------------------|--------------------------------------------------------------------------------------------------------|---------|--------|------|------|-------|--------------------|------|

|                    | Parameter                                                                                              | Min     | Мах    | Min  | Max  | Min   | Max                | Unit |

| ffmpi2CC           | FMPI2CCLK frequency                                                                                    | 2       | -      | 8    | -    | 18    | -                  |      |

| tw(SCLL)           | SCL clock low time                                                                                     | 4.7     | -      | 1.3  | -    | 0.5   | -                  |      |

| tw(SCLH)           | SCL clock high time                                                                                    | 4.0     | -      | 0.6  | -    | 0.26  | -                  |      |

| tsu(SDA)           | SDA setup time                                                                                         | 0.25    | -      | 0.10 | -    | 0.05  | -                  |      |

| th(SDA)            | SDA data hold time                                                                                     | 0       | -      | 0    | -    | 0     | -                  |      |

| tv(SDA,ACK)        | Data, ACK valid time                                                                                   | -       | 3.45   | -    | 0.9  | -     | 0.45               |      |

| tr(SDA)<br>tr(SCL) | SDA and SCL rise time                                                                                  | -       | 1.0    | -    | 0.30 | -     | 0.12               |      |

| tf(SDA)<br>tf(SCL) | SDA and SCL fall time                                                                                  | -       | 0.30   | -    | 0.30 | -0    | 0.12               | μs   |

| th(STA)            | Start condition hold time                                                                              | 4       | -      | 0.6  | -    | 0.26  | -                  |      |

| tsu(STA)           | Repeated Start condition setup time                                                                    | 4.7     | -      | 0.6  | -    | 0.26  | -                  |      |

| tsu(STO)           | Stop condition setup time                                                                              | 4       | -      | 0.6  | -    | 0.26  | -                  |      |

| tw(STO:STA)        | Stop to Start condition time (bus free)                                                                | 4.7     | -      | 1.3  | -    | 0.5   | -                  |      |

| tsp                | Pulse width of the spikes that<br>are suppressed by the<br>analog filter for standard and<br>fast mode | -       | -      | 0.05 | 0.1  | 0.05  | 0.1                |      |

| Cb                 | Capacitive load for each bus<br>Line                                                                   | -       | 400    | -    | 400  | -     | 550 <sup>(2)</sup> | pF   |

| Table 66. FMPI | <sup>2</sup> C characteristics <sup>(1)</sup> |

|----------------|-----------------------------------------------|

|----------------|-----------------------------------------------|

1. Based on characterization results.

2. Can be limited. Maximum supported value can be retrieved by referring to the following formulas:  $t_{r(SDA/SCL)} = 0.8473 \text{ x R}_{p} \text{ x C}_{load} \text{ Rp(min)} = (V_{DD} - V_{OL(max)}) / I_{OL(max)}$

## **SAI characteristics**

Unless otherwise specified, the parameters given in *Table 69* for SAI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and VDD supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C=30 pF

- Measurement points are performed at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (SCK,SD,WS).

| Symbol                   | Parameter              | Conditions                                                                   | Min      | Max                     | Unit |

|--------------------------|------------------------|------------------------------------------------------------------------------|----------|-------------------------|------|

| f <sub>MCKL</sub>        | SAI Main clock output  | -                                                                            | 256 * 8K | 256 * Fs <sup>(2)</sup> | MHz  |

| E                        | SAL clock froguency    | Master data: 32 bits                                                         | -        | 128 * Fs                | MHz  |

| F <sub>SCK</sub>         | SAI clock frequency    | Slave data: 32 bits                                                          | -        | 128 * Fs                |      |

| t <sub>v(FS)</sub>       | FS valid time          | Master mode<br>2.7 V <= V <sub>DD</sub> <= 3.6 V                             | -        | 19                      |      |

|                          |                        | Master mode<br>1.71 V <= V <sub>DD</sub> <= 3.6 V                            | -        | 28                      |      |

| t                        | FS hold time           | Master mode                                                                  | 13       | -                       |      |

| t <sub>h(FS)</sub>       |                        | Slave mode                                                                   | 0        | -                       |      |

| t <sub>su(FS)</sub>      | FS setup time          | Slave mode                                                                   | 3        | -                       |      |

| t <sub>su(SD_A_MR)</sub> | Data input setup time  | Master receiver                                                              | 0.5      | -                       |      |

| t <sub>su(SD_B_SR)</sub> | Data input setup time  | Slave receiver                                                               | 1.5      | -                       |      |

| t <sub>h(SD_A_MR)</sub>  | Data input hold time   | Master receiver                                                              | 5        | -                       |      |

| t <sub>h(SD_B_SR)</sub>  | Data input hold time   | Slave receiver                                                               | 2.5      | -                       | ns   |

| +                        | Data output valid time | Slave transmitter (after enable edge)<br>2.7 V <= V <sub>DD</sub> <= 3.6 V   |          | 15                      |      |

| t <sub>v(SD_B_ST)</sub>  |                        | Slave transmitter (after enable edge)<br>1.71 V <= V <sub>DD</sub> <= 3.6 V  | -        | 28                      |      |

| t <sub>h(SD_B_ST)</sub>  | Data output hold time  | Slave transmitter (after enable edge)                                        | 10       | -                       |      |

| +                        | Data output valid time | Master transmitter (after enable edge)<br>2.7 V <= V <sub>DD</sub> <= 3.6 V  |          | 15                      |      |

| t <sub>v(SD_A_MT)</sub>  | Data output valid time | Master transmitter (after enable edge)<br>1.71 V <= V <sub>DD</sub> <= 3.6 V | -        | 29                      |      |

| t <sub>h(SD_A_MT)</sub>  | Data output hold time  | Master transmitter (after enable edge)                                       | 13       | -                       |      |

## Table 69. SAI characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. 256 \* Fs maximum corresponds to 45 MHz (APB2 maximum frequency)

| Symbol                            | Parameter                                                                       | Conditions                                         | Min | Тур | Max  | Unit |

|-----------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|------|

|                                   |                                                                                 | 12-bit resolution<br>Single ADC                    | -   | -   | 2    | Msps |

| f <sub>S</sub> <sup>(2)</sup>     | $f_S^{(2)}$ Sampling rate<br>( $f_{ADC}$ = 30 MHz, and<br>$t_S$ = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode   | -   | -   | 3.75 | Msps |

|                                   |                                                                                 | 12-bit resolution<br>Interleave Triple ADC<br>mode | -   | -   | 6    | Msps |

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode            | -                                                  | -   | 300 | 500  | μA   |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode            | -                                                  | -   | 1.6 | 1.8  | mA   |

### Table 75. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is possible with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

2. Guaranteed by characterization results.

3.  $V_{\mathsf{REF}^+}$  is internally connected to  $V_{\mathsf{DDA}}$  and  $V_{\mathsf{REF}^-}$  is internally connected to  $V_{\mathsf{SSA}}.$

4.  $R_{ADC}$  maximum value is given for  $V_{DD}$ =1.7 V, and minimum value for  $V_{DD}$ =3.3 V.

5. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 75.

## Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} = \frac{(k-0.5)}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

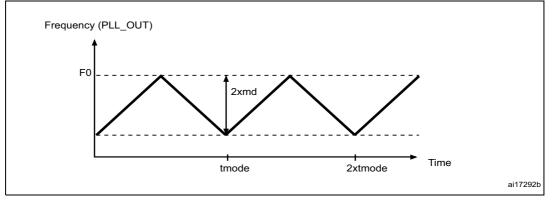

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       | ( (0.10)                                                    | ±3  | ±4                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±2  | ±3                 |      |

| EG     | Gain error                   | $V_{\text{REF}}$ = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V                  | ±1  | ±2                 |      |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |

Table 76. ADC accuracy at f<sub>ADC</sub> = 18 MHz<sup>(1)</sup>

1. Better performance could be achieved in restricted  $V_{DD}$ , frequency and temperature ranges.

2. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.16 does not affect the ADC accuracy.

Figure 48. ADC accuracy characteristics

- 1. See also Table 77.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4. End point correlation line.

- 5. E<sub>T</sub> = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

## **Electrical characteristics**

| Symbol                             | Parameter                                                                                                                                                                | Table 86. DAC cha<br>Conditions | Min | Тур | Max  | Unit | Comments                                                                                                          |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------|

| DNL <sup>(4)</sup>                 | Differential non<br>linearity Difference<br>between two                                                                                                                  | -                               | -   | -   | ±0.5 | LSB  | Given for the DAC in 10-bit configuration.                                                                        |

| DINE                               | consecutive code-<br>1LSB)                                                                                                                                               | _                               | -   | _   | ±2   | LSB  | Given for the DAC in 12-bit configuration.                                                                        |

|                                    | Integral non<br>linearity (difference                                                                                                                                    | -                               | -   | -   | ±1   | LSB  | Given for the DAC in 10-bit configuration.                                                                        |

| INL <sup>(4)</sup>                 | between measured<br>value at Code i and<br>the value at Code i<br>on a line drawn<br>between Code 0<br>and last Code<br>1023)                                            | -                               | -   | -   | ±4   | LSB  | Given for the DAC in 12-bit configuration.                                                                        |

|                                    | Offset error<br>(difference between                                                                                                                                      | -                               | -   | -   | ±10  | mV   | Given for the DAC in 12-bit configuration                                                                         |

| Offset <sup>(4)</sup>              | measured value at<br>Code (0x800) and<br>the ideal value =<br>$V_{REF+}/2$ )                                                                                             | -                               | -   | -   | ±3   | LSB  | Given for the DAC in 10-bit at<br>V <sub>REF+</sub> = 3.6 V                                                       |

|                                    |                                                                                                                                                                          | -                               | -   | -   | ±12  | LSB  | Given for the DAC in 12-bit at<br>V <sub>REF+</sub> = 3.6 V                                                       |

| Gain<br>error <sup>(4)</sup>       | Gain error                                                                                                                                                               | -                               | -   | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                                         |

|                                    | Settling time (full<br>scale: for a 10-bit<br>input code transition<br>between the lowest<br>and the highest<br>input codes when<br>DAC_OUT reaches<br>final value ±4LSB | -                               | -   | 3   | 6    | μs   | C <sub>LOAD</sub> ≤50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                             |

| THD <sup>(4)</sup>                 | Total Harmonic<br>Distortion<br>Buffer ON                                                                                                                                | -                               | -   | -   | -    | dB   | $C_{LOAD}$ ≤ 50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                                   |

| Update<br>rate <sup>(2)</sup>      | Max frequency for a<br>correct DAC_OUT<br>change when small<br>variation in the input<br>code (from code i to<br>i+1LSB)                                                 | -                               | -   | -   | 1    | MS/s | C <sub>LOAD</sub> ≤50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                             |

| t <sub>WAKEUP</sub> <sup>(4)</sup> | Wakeup time from<br>off state (Setting the<br>ENx bit in the DAC<br>Control register)                                                                                    | -                               | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |

| PSRR+ <sup>(2)</sup>               | Power supply<br>rejection ratio (to<br>V <sub>DDA</sub> ) (static DC<br>measurement)                                                                                     | -                               | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                  |

| Table 86. | DAC | characteristics | (continued) |

|-----------|-----|-----------------|-------------|

|-----------|-----|-----------------|-------------|

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

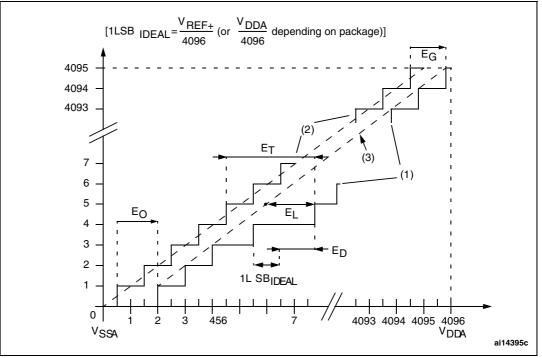

# 7.1 WLCSP81 package information

Figure 63. WLCSP81 - 81-ball, 4.039 x 3.951 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

# Table 111. UFBGA144 - 144-ball, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball gridarray package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| F      | 0.550       | 0.600 | 0.650 | 0.0177                | 0.0197 | 0.0217 |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0039 |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |

| fff    | -           | -     | 0.080 | -                     | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

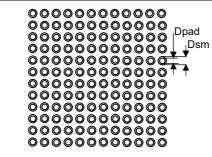

# Figure 82. UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball grid array recommended footprint

A02Y\_FP\_V1

## Table 112. UFBGA144 recommended PCB design rules (0.80 mm pitch BGA)

| Dimension | Recommended values                                               |  |  |

|-----------|------------------------------------------------------------------|--|--|

| Pitch     | 0.80 mm                                                          |  |  |

| Dpad      | 0.400 mm                                                         |  |  |

| Dsm       | 0.550 mm typ. (depends on the soldermask registration tolerance) |  |  |

Note:

4 to 6 mils solder paste screen printing process. Stencil opening is 0.400 mm. Stencil thickness is between 0.100 mm and 0.125 mm. Pad trace width is 0.120 mm.

Non solder mask defined (NSMD) pads are recommended.