Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

E·XFI

| Product Status                 | Active                                                                      |

|--------------------------------|-----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 300000                                                                      |

| Total RAM Bits                 | 21094400                                                                    |

| Number of I/O                  | 300                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 0.97V ~ 1.08V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 536-LFBGA, CSPBGA                                                           |

| Supplier Device Package        | 536-CSPBGA (16x16)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/mpf300tl-fcsg536i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 7.9.4    | Design Dependence of T PUFT and T WRFT               | 67 |

|----------|------------------------------------------------------|----|

| 7.9.5    | Cold Reset to Fabric and I/Os (Low Speed) Functional | 67 |

| 7.9.6    | Warm Reset to Fabric and I/Os (Low Speed) Functional | 67 |

| 7.9.7    | Miscellaneous Initialization Parameters              | 67 |

| 7.9.8    | I/O Calibration                                      | 68 |

| 7.10 Ded | licated Pins                                         | 69 |

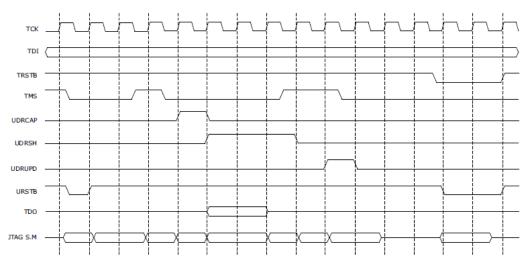

| 7.10.1   | JTAG Switching Characteristics                       | 69 |

| 7.10.2   | SPI Switching Characteristics                        |    |

| 7.10.3   | SmartDebug Probe Switching Characteristics           | 70 |

| 7.10.4   | DEVRST_N Switching Characteristics                   | 70 |

| 7.10.5   | FF_EXIT Switching Characteristics                    | 70 |

| 7.11 Use | r Crypto                                             | 71 |

| 7.11.1   | TeraFire 5200B Switching Characteristics             |    |

| 7.11.2   | TeraFire 5200B Throughput Characteristics            | 71 |

# **1** Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 1.3

Revision 1.3 was published in June 2018. The following is a summary of changes.

- The System Services section was updated. For more information, see System Services (see page 59).

- The Non-Volatile Characteristics section was updated. For more information, see Non-Volatile Characteristics (see page 51).

- The Fabric Macros section was updated. For more information, see Fabric Macros (see page 60).

- The Transceiver Switching Characteristics section was updated. For more information, see Transceiver Switching Characteristics (see page 42).

# 1.2 Revision 1.2

Revision 1.2 was published in June 2018. The following is a summary of changes.

• The datasheet has moved to preliminary status. Every table has been updated.

# 1.3 Revision 1.1

Revision 1.1 was published in August 2017. The following is a summary of changes.

- LVDS specifications changed to 1.25G. For more information, see HSIO Maximum Input Buffer Speed and HSIO Maximum Output Buffer Speed.

- LVDS18, LVDS25/LVDS33, and LVDS25 specifications changed to 800 Mbps. For more information, see I/O Standards Specifications.

- A note was added indicting a zeroization cycle counts as a programming cycle. For more information, see Non-Volatile Characteristics.

- A note was added defining power down conditions for programming recovery conditions. For more information, see Power-Supply Ramp Times.

# 1.4 Revision 1.0

Revision 1.0 was the first publication of this document.

# 5 Silicon Status

There are three silicon status levels:

- Advanced—initial estimated information based on simulations

- Preliminary—information based on simulation and/or initial characterization

- Production—final production silicon data

The following table shows the status of the PolarFire FPGA device.

### Table 2 • PolarFire FPGA Silicon Status

| Device               | Silicon Status |

|----------------------|----------------|

| MPF100T, TL, TS, TLS | Preliminary    |

| MPF200T, TL, TS, TLS | Preliminary    |

| MPF300T, TL, TS, TLS | Preliminary    |

| MPF500T, TL, TS, TLS | Preliminary    |

| K | X  | MICROCHIP | company |

|---|----|-----------|---------|

| 2 | `` | WICHOCHIE | company |

| Parameter                                                                                                        | Symbol       | Min    | Тур     | Max          | Unit |

|------------------------------------------------------------------------------------------------------------------|--------------|--------|---------|--------------|------|

| Transceiver TX and RX lanes supply at 1.05 V mode (when any lane rate is greater than 10.3125 Gbps) <sup>1</sup> | Vdda         | 1.02   | 1.05    | 1.08         | V    |

| Programming and HSIO receiver supply                                                                             | VDD18        | 1.71   | 1.80    | 1.89         | V    |

| FPGA core and FPGA PLL high-voltage supply                                                                       | VDD25        | 2.425  | 2.50    | 2.575        | V    |

| Transceiver PLL high-voltage supply                                                                              | VDDA25       | 2.425  | 2.50    | 2.575        | V    |

| Transceiver reference clock supply –3.3 V nominal                                                                | Vdd_xcvr_clk | 3.135  | 3.3     | 3.465        | V    |

| Transceiver reference clock supply –2.5 V nominal                                                                | Vdd_xcvr_clk | 2.375  | 2.5     | 2.625        | V    |

| Global VREF for transceiver reference clocks <sup>3</sup>                                                        | XCVRvref     | Ground |         | VDD_XCVR_CLK | V    |

| HSIO DC I/O supply. Allowed nominal options: 1.2 V, 1.35 V, 1.5 V, and 1.8 V <sup>4</sup>                        | VDDIx        | 1.14   | Various | 1.89         | V    |

| GPIO DC I/O supply. Allowed nominal options: 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 $V^{2,4}$                       | VDDIx        | 1.14   | Various | 3.465        | V    |

| Dedicated I/O DC supply for JTAG and SPI (GPIO Bank<br>3). Allowed nominal options: 1.8 V, 2.5 V, and 3.3 V      | Vddi3        | 1.71   | Various | 3.465        | V    |

| GPIO auxiliary supply for I/O bank x with $V_{\text{DDIx}}$ = 3.3 V nominal^{2,4}                                | Vddauxx      | 3.135  | 3.3     | 3.465        | V    |

| GPIO auxiliary supply for I/O bank x with $V_{DDIx}$ = 2.5 V nominal or lower <sup>2,4</sup>                     | Vddauxx      | 2.375  | 2.5     | 2.625        | V    |

| Extended commercial temperature range                                                                            | TJ           | 0      |         | 100          | °C   |

| Industrial temperature range                                                                                     | Tı           | -40    |         | 100          | °C   |

| Extended commercial programming temperature range                                                                | Tprg         | 0      |         | 100          | °C   |

| Industrial programming temperature range                                                                         | Tprg         | -40    |         | 100          | °C   |

1. V<sub>DD</sub> and V<sub>DDA</sub> can independently operate at 1.0 V or 1.05 V nominal. These supplies are not dynamically adjustable.

For GPIO buffers where I/O bank is designated as bank number, if VDDIX is 2.5 V nominal or 3.3 V nominal, VDDAUXX must be connected to the VDDIX supply for that bank. If VDDIX for a given GPIO bank is <2.5 V nominal, VDDAUXX per I/O bank must be powered at 2.5 V nominal.</li>

3. XCVR<sub>VREF</sub> globally sets the reference voltage of the transceiver's single-ended reference clock input buffers. It is typically near V<sub>DD\_XCVR\_CLK</sub>/2 V but is allowed in the specified range.

4. The power supplies for a given I/O bank x are shown as VDDIx and VDDAUXx.

PolarFire

| I/O<br>Standard | Vool<br>Min (V) | Vooi<br>Typ (V) | Vool<br>Max (V) | V⊾<br>Min (V) | V⊩<br>Max (V) | V⊮<br>Min (V) | Vін <sup>1</sup><br>Max (V) |

|-----------------|-----------------|-----------------|-----------------|---------------|---------------|---------------|-----------------------------|

| SSTL135I        | 1.283           | 1.35            | 1.418           | -0.3          | VREF          | VREF          | 1.418                       |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.09          | 0.09          |                             |

| SSTL135II       | 1.283           | 1.35            | 1.418           | -0.3          | VREF          | VREF          | 1.418                       |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.09          | 0.09          |                             |

| HSTL15I         | 1.425           | 1.5             | 1.575           | -0.3          | VREF          | VREF          | 1.575                       |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.1           | 0.1           |                             |

| HSTL15II        | 1.425           | 1.5             | 1.575           | -0.3          | VREF          | VREF          | 1.575                       |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.1           | 0.1           |                             |

| HSTL135I        | 1.283           | 1.35            | 1.418           | -0.3          | VREF          | VREF          | 1.418                       |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.09          | 0.09          |                             |

| HSTL135II       | 1.283           | 1.35            | 1.418           | -0.3          | VREF          | VREF          | 1.418                       |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.09          | 0.09          |                             |

| HSTL12I         | 1.14            | 1.2             | 1.26            | -0.3          | VREF          | VREF          | 1.26                        |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.1           | 0.1           |                             |

| HSTL12II        | 1.14            | 1.2             | 1.26            | -0.3          | VREF          | VREF          | 1.26                        |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.1           | 0.1           |                             |

| HSUL18I         | 1.71            | 1.8             | 1.89            | -0.3          | 0.3           | 0.7           | 1.89                        |

|                 |                 |                 |                 |               | ×             | ×             |                             |

|                 |                 |                 |                 |               | Vddi          | Vddi          |                             |

| HSUL18II        | 1.71            | 1.8             | 1.89            | -0.3          | 0.3           | 0.7           | 1.89                        |

|                 |                 |                 |                 |               | ×             | ×             |                             |

|                 |                 |                 |                 |               | Vddi          | Vddi          |                             |

| HSUL12I         | 1.14            | 1.2             | 1.26            | -0.3          | VREF          | VREF          | 1.26                        |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.1           | 0.1           |                             |

| POD12I          | 1.14            | 1.2             | 1.26            | -0.3          | VREF          | VREF          | 1.26                        |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.08          | 0.08          |                             |

| POD12II         | 1.14            | 1.2             | 1.26            | -0.3          | VREF          | VREF          | 1.26                        |

|                 |                 |                 |                 |               | -             | +             |                             |

|                 |                 |                 |                 |               | 0.08          | 0.08          |                             |

1. GPIO V<sup>IH</sup> max is 3.45 V with PCI clamp diode turned off regardless of mode, that is, over-voltage tolerant.

2. For external stub-series resistance. This resistance is on-die for GPIO.

Note: 3.3 V and 2.5 V are only supported in GPIO banks.

| Parameter                                      | Description                       | Min (%) | Тур | Max (%) | Unit | Condition                                  |

|------------------------------------------------|-----------------------------------|---------|-----|---------|------|--------------------------------------------|

| Single-ended                                   | Internal                          | -20     | 120 | 20      | Ω    | V <sub>DDI</sub> = 2.5 V/1.8 V/1.5 V/1.2 V |

| termination to V <sub>55</sub> <sup>4, 5</sup> | parallel<br>termination<br>to Vss | -20     | 240 | 20      | Ω    | V <sub>DDI</sub> = 2.5 V/1.8 V/1.5 V/1.2 V |

1. Measured across P to N with 400 mV bias.

- 2. The venin impedance is calculated based on independent P and N as measured at 50% of  $V_{\text{DDI}}.$

- 3. For 50  $\Omega/75 \Omega/150 \Omega$  cases, nearest supported values of 40  $\Omega/60 \Omega/120 \Omega$  are used.

4. Measured at 50% of  $V_{DDI}$ .

5. Supported terminations vary with the IO type regardless of V\_DDI nominal voltage. Refer to Libero for available combinations.

# 7 AC Switching Characteristics

This section contains the AC switching characteristics of the PolarFire FPGA device.

# 7.1 I/O Standards Specifications

This section describes I/O delay measurement methodology, buffer speed, switching characteristics, digital latency, gearing training calibration, and maximum physical interface (PHY) rate for memory interface IP.

# 7.1.1 Input Delay Measurement Methodology Maximum PHY Rate for Memory Interface IP

The following table provides information about the methodology for input delay measurement.

| Standard  | Description  | VL1    | VH1                | VID <sup>2</sup> | VICM <sup>2</sup> | Vmeas <sup>3, 4</sup> | Vref <sup>1, 5</sup> | Uni |

|-----------|--------------|--------|--------------------|------------------|-------------------|-----------------------|----------------------|-----|

| PCI       | PCIE 3.3 V   | 0      | VDDI               |                  |                   | VDDI/2                |                      | V   |

| LVTTL33   | LVTTL 3.3 V  | 0      | VDDI               |                  |                   | VDDI/2                |                      | V   |

| LVCMOS33  | LVCMOS 3.3 V | 0      | VDDI               |                  |                   | VDDI/2                |                      | V   |

| LVCMOS25  | LVCMOS 2.5 V | 0      | VDDI               |                  |                   | VDDI/2                |                      | V   |

| LVCMOS18  | LVCMOS 1.8 V | 0      | VDDI               |                  |                   | VDDI/2                |                      | V   |

| LVCMOS15  | LVCMOS 1.5 V | 0      | VDDI               |                  |                   | VDDI/2                |                      | V   |

| LVCMOS12  | LVCMOS 1.2 V | 0      | VDDI               |                  |                   | VDDI/2                |                      | V   |

| SSTL25I   | SSTL 2.5 V   | Vref - | VREF +             |                  |                   | Vref                  | 1.25                 | V   |

|           | Class I      | 0.5    | 0.5                |                  |                   |                       |                      |     |

| SSTL25II  | SSTL 2.5 V   | Vref - | VREF +             |                  |                   | VREF                  | 1.25                 | V   |

|           | Class II     | 0.5    | 0.5                |                  |                   |                       |                      |     |

| SSTL18I   | SSTL 1.8 V   | VREF - | VREF +             |                  |                   | VREF                  | 0.90                 | V   |

|           | Class I      | 0.5    | 0.5                |                  |                   |                       |                      |     |

| SSTL18II  | SSTL 1.8 V   | Vref - | VREF +             |                  |                   | VREF                  | 0.90                 | V   |

|           | Class II     | 0.5    | 0.5                |                  |                   |                       |                      |     |

| SSTL15I   | SSTL 1.5 V   | Vref - | VREF +             |                  |                   | VREF                  | 0.75                 | V   |

|           | Class I      | .175   | .175               |                  |                   |                       |                      |     |

| SSTL15II  | SSTL 1.5 V   | Vref - | VREF +             |                  |                   | VREF                  | 0.75                 | V   |

|           | Class II     | .175   | .175               |                  |                   |                       |                      |     |

| SSTL135I  | SSTL 1.35 V  | Vref - | VREF +             |                  |                   | VREF                  | 0.675                | V   |

|           | Class I      | .16    | .16                |                  |                   |                       |                      |     |

| SSTL135II | SSTL 1.35 V  | Vref - | VREF +             |                  |                   | VREF                  | 0.675                | V   |

|           | Class II     | .16    | .16                |                  |                   |                       |                      |     |

| HSTL15I   | HSTL 1.5 V   | VREF - | V <sub>REF</sub> + |                  |                   | VREF                  | 0.75                 | V   |

|           | Class I      | .5     | .5                 |                  |                   |                       |                      |     |

| HSTL15II  | HSTL 1.5 V   | Vref - | V <sub>REF</sub> + |                  |                   | VREF                  | 0.75                 | V   |

|           | Class II     | .5     | .5                 |                  |                   |                       |                      |     |

| HSTL135I  | HSTL 1.35 V  | Vref - | VREF + .           |                  |                   | VREF                  | 0.675                | V   |

|           | Class I      | 0.45   | 45                 |                  |                   |                       |                      |     |

| HSTL135II | HSTL 1.35 V  | Vref - | V <sub>REF</sub> + |                  |                   | VREF                  | 0.675                | V   |

|           | Class II     | .45    | .45                |                  |                   |                       |                      |     |

| HSTL12    | HSTL 1.2 V   | Vref - | V <sub>REF</sub> + |                  |                   | VREF                  | 0.60                 | V   |

|           |              | .4     | .4                 |                  |                   |                       |                      |     |

### Table 22 • Input Delay Measurement Methodology

| Standard        | STD | -1  | Unit |

|-----------------|-----|-----|------|

| LVCMOS12 (8 mA) | 250 | 300 | Mbps |

# Table 27 • GPIO Maximum Output Buffer Speed

| Standard                | STD  | -1   | Unit |

|-------------------------|------|------|------|

| LVDS25/LCMDS25          | 1250 | 1250 | Mbps |

| LVDS33/LCMDS33          | 1250 | 1600 | Mbps |

| RSDS25                  | 800  | 800  | Mbps |

| MINILVDS25              | 800  | 800  | Mbps |

| SUBLVDS25               | 800  | 800  | Mbps |

| PPDS25                  | 800  | 800  | Mbps |

| SLVSE15                 | 500  | 500  | Mbps |

| BUSLVDSE25              | 500  | 500  | Mbps |

| MLVDSE25                | 500  | 500  | Mbps |

| LVPECLE33               | 500  | 500  | Mbps |

| SSTL25I                 | 800  | 800  | Mbps |

| SSTL25II                | 800  | 800  | Mbps |

| SSTL25I (differential)  | 800  | 800  | Mbps |

| SSTL25II (differential) | 800  | 800  | Mbps |

| SSTL18I                 | 800  | 800  | Mbps |

| SSTL18II                | 800  | 800  | Mbps |

| SSTL18I (differential)  | 800  | 800  | Mbps |

| SSTL18II (differential) | 800  | 800  | Mbps |

| SSTL15I                 | 800  | 1066 | Mbps |

| SSTL15II                | 800  | 1066 | Mbps |

| SSTL15I (differential)  | 800  | 1066 | Mbps |

| SSTL15II (differential) | 800  | 1066 | Mbps |

| HSTL15I                 | 900  | 900  | Mbps |

| HSTL15II                | 900  | 900  | Mbps |

| HSTL15I (differential)  | 900  | 900  | Mbps |

| HSTL15II (differential) | 900  | 900  | Mbps |

| HSUL18I                 | 400  | 400  | Mbps |

| HSUL18II                | 400  | 400  | Mbps |

| HSUL18I (differential)  | 400  | 400  | Mbps |

| HSUL18II (differential) | 400  | 400  | Mbps |

| PCI                     | 500  | 500  | Mbps |

| LVTTL33 (20 mA)         | 500  | 500  | Mbps |

| LVCMOS33 (20 mA)        | 500  | 500  | Mbps |

| LVCMOS25 (16 mA)        | 500  | 500  | Mbps |

| LVCMOS18 (12 mA)        | 500  | 500  | Mbps |

| LVCMOS15 (10 mA)        | 500  | 500  | Mbps |

| LVCMOS12 (8 mA)         | 250  | 300  | Mbps |

| MIPIE25                 | 500  | 500  | Mbps |

## 7.1.6 User I/O Switching Characteristics

The following section describes characteristics for user I/O switching.

For more information about user I/O timing, see the *PolarFire I/O Timing Spreadsheet* (to be released).

### 7.1.6.1 I/O Digital

The following tables provide information about I/O digital.

#### Table 30 • I/O Digital Receive Single-Data Rate Switching Characteristics

| Parameter | Interface<br>Name | Topology | STD<br>Min | STD<br>Typ | STD<br>Max | –1<br>Min | —1<br>Тур | -1<br>Max | Unit | Clock-to-Data<br>Condition                 |

|-----------|-------------------|----------|------------|------------|------------|-----------|-----------|-----------|------|--------------------------------------------|

| Fмах      | RX_SDR_G_A        | Rx SDR   |            |            |            |           |           |           | MHz  | From a global<br>clock source,<br>aligned  |

| Fмах      | RX_SDR_L_A        | Rx SDR   |            |            |            |           |           |           | MHz  | From a lane<br>clock source,<br>aligned    |

| Fmax      | RX_SDR_G_C        | Rx SDR   |            |            |            |           |           |           | MHz  | From a global<br>clock source,<br>centered |

| Fmax      | RX_SDR_L_C        | Rx SDR   |            |            |            |           |           |           | MHz  | From a lane<br>clock source,<br>centered   |

#### Table 31 • I/O Digital Receive Double-Data Rate Switching Characteristics

| Parameter | Interface Name | Topology                  | STD<br>Min | STD<br>Typ | STD<br>Max | -1<br>Min | —1<br>Тур | -1<br>Max | Unit | Clock-to-<br>Data<br>Condition                     |

|-----------|----------------|---------------------------|------------|------------|------------|-----------|-----------|-----------|------|----------------------------------------------------|

| Fмах      | RX_DDR_G_A     | Rx DDR                    |            | 335        |            |           | 335       | MHz       | MHz  | From a<br>global<br>clock<br>source,<br>aligned    |

| Fмах      | RX_DDR_L_A     | Rx DDR                    |            | 250        |            |           | 250       |           | MHz  | From a<br>lane clock<br>source,<br>aligned         |

| Fмах      | RX_DDR_G_C     | Rx DDR                    |            | 335        |            |           | 335       |           | MHz  | From a<br>global<br>clock<br>source,<br>centered   |

| Fмах      | RX_DDR_L_C     | Rx DDR                    |            | 250        |            |           | 250       |           | MHz  | From a<br>lane clock<br>source,<br>centered        |

| Fмах 2:1  | RX_DDRX_B_A    | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>aligned |

| Parameter       | Interface Name | Topology                  | STD<br>Min | STD<br>Typ | STD<br>Max | –1<br>Min | —1<br>Тур | -1<br>Max | Unit | Clock-to-<br>Data<br>Condition                      |

|-----------------|----------------|---------------------------|------------|------------|------------|-----------|-----------|-----------|------|-----------------------------------------------------|

| Fмах <b>4:1</b> | RX_DDRX_B_A    | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>aligned  |

| Fmax 8:1        | RX_DDRX_B_A    | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>aligned  |

| Fмах 2:1        | RX_DDRX_B_C    | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>centered |

| Fмах <b>4:1</b> | RX_DDRX_B_C    | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>centered |

| Fмах 8:1        | RX_DDRX_B_C    | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>centered |

| Fмах 2:1        | RX_DDRX_BL_A   | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>aligned  |

| Fмах 4:1        | RX_DDRX_BL_A   | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>aligned  |

| Fмах 8:1        | RX_DDRX_BL_A   | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>aligned  |

| Fмах 2:1        | RX_DDRX_BL_C   | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLI<br>clock<br>source,<br>centered |

| Fmax 4:1        | RX_DDRX_BL_C   | Rx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLH<br>clock<br>source,<br>centered |

| Parameter                                          | Interface<br>Name | Topology                  | STD<br>Min | STD<br>Typ | STD<br>Max | –1<br>Min | —1<br>Тур | -1<br>Max | Unit | Forwarded<br>Clock-to-<br>Data Skew                          |

|----------------------------------------------------|-------------------|---------------------------|------------|------------|------------|-----------|-----------|-----------|------|--------------------------------------------------------------|

| Output<br>F <sub>MAX</sub> 2:1                     | TX_DDRX_B_C       | Tx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLK<br>clock source,<br>centered<br>with PLL |

| Output<br>FMAX 4:1                                 | TX_DDRX_B_C       | Tx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLK<br>clock source,<br>centered<br>with PLL |

| Output<br>FMAX 8:1                                 | TX_DDRX_B_C       | Tx DDR<br>digital<br>mode |            |            |            |           |           |           | MHz  | From a<br>HS_IO_CLK<br>clock source,<br>centered<br>with PLL |

| In delay,<br>out delay,<br>DLL delay<br>step sizes |                   |                           | 12.7       | 30         | 35         | 12.7      | 25        | 29.5      | ps   |                                                              |

### Table 34 • I/O CDR Switching Characteristics

| Parameter                                         | Min | Max  | Unit |

|---------------------------------------------------|-----|------|------|

| Data rate                                         | 266 | 1250 | Mbps |

| Receiver Sinusoidal jitter tolerance <sup>1</sup> | 0.2 |      | UI   |

1. Jitter values based on bit error ratio (BER) of 10–12, 80 MHz sinusoidal jitter injected to Rx data. **Note:** See the LVDS output buffer specifications for transmit characteristics.

# 7.2 Clocking Specifications

This section describes the PLL and DLL clocking and oscillator specifications.

# 7.2.1 Clocking

The following table provides clocking specifications.

### Table 35 • Global and Regional Clock Characteristics (-40 °C to 100 °C)

| Parameter                                | Symbol | V dd =<br>1.0 V STD | V <sub>DD</sub> =<br>1.0 V –1 | V dd =<br>1.05 V STD | V dd =<br>1.05 V -1 | Unit | Condition                         |

|------------------------------------------|--------|---------------------|-------------------------------|----------------------|---------------------|------|-----------------------------------|

| Global clock<br>FMAX                     | Fmaxg  | 500                 | 500                           | 500                  | 500                 | MHz  |                                   |

| Regional<br>clock<br>Fmax                | Fmaxr  | 375                 | 375                           | 375                  | 375                 | MHz  | Transceiver<br>interfaces<br>only |

|                                          | Fmaxr  | 250                 | 250                           | 250                  | 250                 | MHz  | All other interfaces              |

| Global clock<br>duty cycle<br>distortion | Tdcdg  | 190                 | 190                           | 190                  | 190                 | ps   | At<br>500 MHz                     |

# 7.3.2 SRAM Blocks

The following tables describe the LSRAM blocks' performance.

| Parameter           | V <sub>DD</sub> =<br>1.0 V – STD | V <sub>DD</sub> =<br>1.0 V - 1 | V <sub>DD</sub> =<br>1.05 V – STD | V <sub>DD</sub> =<br>1.05 V – 1 | Unit | Condition                                                                                   |

|---------------------|----------------------------------|--------------------------------|-----------------------------------|---------------------------------|------|---------------------------------------------------------------------------------------------|

| Operating frequency | 343                              | 428                            | 343                               | 428                             | MHz  | Two-port, all supported widths,<br>pipelined, simple-write, and write-<br>feed-through      |

|                     | 309                              | 428                            | 309                               | 428                             | MHz  | Two-port, all supported widths,<br>non-pipelined, simple-write, and<br>write-feed-through   |

|                     | 343                              | 428                            | 343                               | 428                             | MHz  | Dual-port, all supported widths,<br>pipelined, simple-write, and write-<br>feed-through     |

|                     | 309                              | 428                            | 309                               | 428                             | MHz  | Dual-port, all supported widths,<br>non-pipelined, simple-write, and<br>write-feed-through  |

|                     | 343                              | 428                            | 343                               | 428                             | MHz  | Two-port pipelined ECC mode,<br>pipelined, simple-write, and write-<br>feed-through         |

|                     | 279                              | 295                            | 279                               | 295                             | MHz  | Two-port non-pipelined ECC<br>mode, pipelined, simple-write,<br>and write-feed-through      |

|                     | 343                              | 428                            | 343                               | 428                             | MHz  | Two-port pipelined ECC mode,<br>non-pipelined, simple-write, and<br>write-feed-through      |

|                     | 196                              | 285                            | 196                               | 285                             | MHz  | Two-port non-pipelined ECC<br>mode, non-pipelined, simple-<br>write, and write-feed-through |

|                     | 274                              | 285                            | 274                               | 285                             | MHz  | Two-port, all supported widths, pipelined, and read-before-write                            |

|                     | 274                              | 285                            | 274                               | 285                             | MHz  | Two-port, all supported widths,<br>non-pipelined, and read-before-<br>write                 |

|                     | 274                              | 285                            | 274                               | 285                             | MHz  | Dual-port, all supported widths, pipelined, and read-before-write                           |

|                     | 274                              | 285                            | 274                               | 285                             | MHz  | Dual-port, all supported widths,<br>non-pipelined, and read-before-<br>write                |

|                     | 274                              | 285                            | 274                               | 285                             | MHz  | Two-port pipelined ECC mode, pipelined, and read-before-write                               |

|                     | 274                              | 285                            | 274                               | 285                             | MHz  | Two-port non-pipelined ECC<br>mode, pipelined, and read-before-<br>write                    |

|                     | 274                              | 285                            | 274                               | 285                             | MHz  | Two-port pipelined ECC mode,<br>non-pipelined, and read-before-<br>write                    |

|                     | 193                              | 285                            | 193                               | 285                             | MHz  | Two-port non-pipelined ECC<br>mode, non-pipelined, and read-<br>before-write                |

а 🕵 Міскоснір company

|                                   |                 |         |     |          |         |     |          | · · · p · · j |

|-----------------------------------|-----------------|---------|-----|----------|---------|-----|----------|---------------|

| Parameter                         | Symbol          | STD     | STD | STD      | -1      | -1  | -1       | Unit          |

|                                   |                 | Min     | Тур | Max      | Min     | Тур | Max      |               |

| Reference clock input             | Fxcvrrefclkmax  | 20      |     | 156      | 20      |     | 156      | MHz           |

| rate <sup>1, 2, 3</sup>           | CASCADE         |         |     |          |         |     |          |               |

| Reference clock rate at           | Ftxrefclkpfd    | 20      |     | 156      | 20      |     | 156      | MHz           |

| the PFD⁴                          |                 |         |     |          |         |     |          |               |

| Reference clock rate              | FTXREFCLKPFD10G | 75      |     | 156      | 75      |     | 156      | MHz           |

| recommended at the                |                 |         |     |          |         |     |          |               |

| PFD for Tx rates 10 Gbps          |                 |         |     |          |         |     |          |               |

| and above <sup>4</sup>            |                 |         |     |          |         |     |          |               |

| Tx reference clock                | Ftxrefpn        |         |     | -110     |         |     | -110     | dBc           |

| phase noise                       |                 |         |     |          |         |     |          | /Hz           |

| requirements to meet              |                 |         |     |          |         |     |          |               |

| jitter specifications (156        |                 |         |     |          |         |     |          |               |

| MHz clock at reference            |                 |         |     |          |         |     |          |               |

| clock input)⁵                     |                 |         |     |          |         |     |          |               |

| Phase noise at 10 KHz             | FTXREFPN        |         |     | -110     |         |     | -110     | dBc           |

|                                   |                 |         |     |          |         |     |          | /Hz           |

| Phase noise at 100 KHz            | FTXREFPN        |         |     | -115     |         |     | -115     | dBc           |

|                                   |                 |         |     |          |         |     |          | /Hz           |

| Phase noise at 1 MHz              | FTXREFPN        |         |     | -135     |         |     | -135     | dBc           |

|                                   |                 |         |     |          |         |     |          | /Hz           |

| Reference clock input             | TREFRISE        |         | 200 | 500      |         | 200 | 500      | ps            |

| rise time (10%–90%)               |                 |         |     |          |         |     |          |               |

| Reference clock input             | TREFFALL        |         | 200 | 500      |         | 200 | 500      | ps            |

| fall time (90%–10%)               |                 |         |     |          |         |     |          |               |

| Reference clock duty              | TREFDUTY        | 40      |     | 60       | 40      |     | 60       | %             |

| cycle                             |                 |         |     |          |         |     |          |               |

| Spread spectrum                   | Mod_Spread      | 0.1     |     | 3.1      | 0.1     |     | 3.1      | %             |

| modulation spread <sup>6</sup>    |                 |         |     |          |         |     |          |               |

| Spread spectrum                   | Mod_Freq        | TxREF   | 32  | TxREF    | TxREF   | 32  | TxREF    | KHz           |

| modulation frequency <sup>7</sup> |                 | CLKPFD/ |     | CLKPFD/  | CLKPFD/ |     | CLKPFD/  |               |

|                                   |                 | (128)   |     | (128*63) | (128)   |     | (128*63) |               |

1. See the maximum reference clock rate allowed per input buffer standard.

2. The minimum value applies to this clock when used as an XCVR reference clock. It does not apply when used as a non-XCVR input buffer (DC input allowed).

- 3. Cascaded reference clock.

- 4. After reference clock input divider.

- Required maximum phase noise is scaled based on actual F<sub>TxRefClkPFD</sub> value by 20 × log10 (TxRefClkPFD /156 MHz). It is assumed that the reference clock divider of 4 is used for these calculations to always meet the maximum PFD frequency specification.

- 6. Programmable capability for depth of down-spread or center-spread modulation.

- 7. Programmable modulation rate based on the modulation divider setting (1 to 63).

### 7.4.3 Transceiver Reference Clock I/O Standards

The following table describes the differential I/O standards supported as transceiver reference clocks.

#### Table 60 • 10GbE (RXAUI)

|                           | Data Rate | Min | Max | Unit |

|---------------------------|-----------|-----|-----|------|

| Total transmit jitter     | 6.25 Gbps |     |     | UI   |

| Receiver jitter tolerance | 6.25 Gbps |     |     | UI   |

## 7.5.4 1GbE (1000BASE-T)

The following table describes 1GbE (1000BASE-T).

# Table 61 • 1GbE (1000BASE-T)

|                           | Data Rate | Min | Max | Unit |

|---------------------------|-----------|-----|-----|------|

| Total transmit jitter     | 1.25 Gbps |     |     | UI   |

| Receiver jitter tolerance | 1.25 Gbps |     |     | UI   |

The following table describes 1GbE (1000BASE-X).

#### Table 62 • 1GbE (1000BASE-X)

|                           | Data Rate | Min | Max | Unit |

|---------------------------|-----------|-----|-----|------|

| Total transmit jitter     | 1.25 Gbps |     |     | UI   |

| Receiver jitter tolerance | 1.25 Gbps |     |     | UI   |

# 7.5.5 SGMII and QSGMII

The following table describes SGMII.

#### Table 63 • SGMII

| Parameter                 | Data Rate | Min   | Max  | Unit |

|---------------------------|-----------|-------|------|------|

| Total transmit jitter     | 1.25 Gbps |       | 0.24 | UI   |

| Receiver jitter tolerance | 1.25 Gbps | 0.749 |      | UI   |

The following table describes QSGMII.

#### Table 64 • QSGMII

| Parameter                 | Data Rate | Min  | Max | Unit |

|---------------------------|-----------|------|-----|------|

| Total transmit jitter     | 5.0 Gbps  |      | 0.3 | UI   |

| Receiver jitter tolerance | 5.0 Gbps  | 0.65 |     | UI   |

## 7.5.6 SDI

The following table describes SDI.

#### Table 65 • SDI

| Parameter                 | Data Rate | Min | Max | Unit |

|---------------------------|-----------|-----|-----|------|

| Total transmit jitter     |           |     |     | UI   |

| Receiver jitter tolerance |           |     |     | UI   |

|                                                                               |     |     |      | -                          |

|-------------------------------------------------------------------------------|-----|-----|------|----------------------------|

| Parameter                                                                     | Тур | Max | Unit | Conditions                 |

| Time to destroy data in non-volatile memory (recoverable) <sup>1, 3</sup>     |     |     | ms   | One iteration of scrubbing |

| Time to destroy data in non-volatile memory (non-recoverable) <sup>1, 4</sup> |     |     | ms   | One iteration of scrubbing |

| Time to scrub the fabric data <sup>1</sup>                                    |     |     | S    | Full scrubbing             |

| Time to scrub the pNVM data (like new) <sup>1, 2</sup>                        |     |     | S    | Full scrubbing             |

| Time to scrub the pNVM data (recoverable) <sup>1,3</sup>                      |     |     | S    | Full scrubbing             |

| Time to scrub the fabric data PNVM data (non-recoverable) <sup>1, 4</sup>     |     |     | S    | Full scrubbing             |

| Time to verify <sup>5</sup>                                                   |     |     | S    |                            |

|                                                                               |     |     |      |                            |

1. Total completion time after interning zeroization.

- 2. Like new mode—zeroizes user design security setting and sNVM content.

- 3. Recoverable mode—zeroizes user design security setting, sNVM and factory keys.

- 4. Non-recoverable mode—zeroizes user design security setting, sNVM and factory keys, and factory data required for programming.

- 5. Time to verify after scrubbing completes.

#### Table 79 • Zeroization Times for MPF300T, TL, TS, and TLS Devices

| Parameter                                                                      | Тур | Max | Unit | Conditions                 |

|--------------------------------------------------------------------------------|-----|-----|------|----------------------------|

| Time to enter zeroization                                                      |     |     | ms   | Zip flag set               |

| Time to destroy the fabric data <sup>1</sup>                                   |     |     | ms   | Data erased                |

| Time to destroy data in non-volatile memory (like new) <sup>1, 2</sup>         |     |     | ms   | One iteration of scrubbing |

| Time to destroy data in non-volatile memory (recoverable) <sup>1, 3</sup>      |     |     | ms   | One iteration of scrubbing |

| Time to destroy data in non-volatile memory (non- recoverable) <sup>1, 4</sup> |     |     | ms   | One iteration of scrubbing |

| Time to scrub the fabric data <sup>1</sup>                                     |     |     | S    | Full scrubbing             |

| Time to scrub the pNVM data (like new) <sup>1,2</sup>                          |     |     | S    | Full scrubbing             |

| Time to scrub the pNVM data (recoverable) <sup>1,3</sup>                       |     |     | S    | Full scrubbing             |

| Time to scrub the fabric data pNVM data (non-recoverable) $^{1,4}$             |     |     | S    | Full scrubbing             |

| Time to verify <sup>5</sup>                                                    |     |     | S    |                            |

- 1. Total completion time after interning zeroization.

- 2. Like new mode—zeroizes user design security setting and sNVM content.

- 3. Recoverable mode—zeroizes user design security setting, sNVM and factory keys.

- 4. Non-recoverable mode—zeroizes user design security setting, sNVM and factory keys, and factory data required for programming.

- 5. Time to verify after scrubbing completes.

\_

#### Table 80 • Zeroization Times for MPF500T, TL, TS, and TLS Devices

| Parameter                                                              | Тур | Max | Unit | Conditions                 |

|------------------------------------------------------------------------|-----|-----|------|----------------------------|

| Time to enter zeroization                                              |     |     | ms   | Zip flag set               |

| Time to destroy the fabric data <sup>1</sup>                           |     |     | ms   | Data erased                |

| Time to destroy data in non-volatile memory (like new) <sup>1, 2</sup> |     |     | ms   | One iteration of scrubbing |

| Time to destroy data in non-volatile memory (recoverable) $^{\rm 1,3}$ |     |     | ms   | One iteration of scrubbing |

# 7.8.2 UJTAG\_SEC Switching Characteristics

The following table describes characteristics of UJTAG\_SEC switching.

#### Table 89 • UJTAG Security Performance Characteristics

| Parameter     | Symbol | Min | Тур | Max | Unit | Condition |

|---------------|--------|-----|-----|-----|------|-----------|

| TCK frequency | Fтск   |     |     |     | MHz  |           |

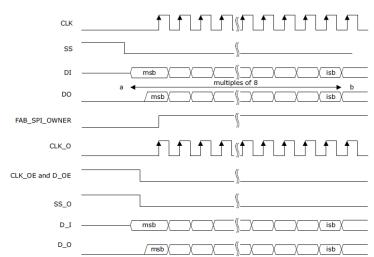

### 7.8.3 USPI Switching Characteristics

The following section describes characteristics of USPI switching.

#### Table 90 • SPI Macro Interface Timing Characteristics

| Parameter                   | Symbol      | V <sub>DDI</sub> = 3.3 V<br>Max | V <sub>DDI</sub> = 2.5 V<br>Max | V <sub>DDI</sub> = 1.8 V<br>Max | V <sub>DDI</sub> = 1.5 V<br>Max | V <sub>DDI</sub> = 1.2 V<br>Max | Unit |

|-----------------------------|-------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|------|

| Propagation                 | TPD_MOSI    | 0.8                             | 1                               | 1.2                             | 1.4                             | 1.6                             | ns   |

| delay from<br>the fabric to | TPD_MISO    | 3.5                             | 3.75                            | 4                               | 4.25                            | 4.5                             | ns   |

| pins <sup>1</sup>           | TPD_SS      | 3.5                             | 3.75                            | 4                               | 4.25                            | 4.5                             | ns   |

|                             | TPD_SCK     | 3.5                             | 3.75                            | 4                               | 4.25                            | 4.5                             | ns   |

|                             | TPD_MOSI_OE | 3.5                             | 3.75                            | 4                               | 4.25                            | 4.5                             | ns   |

|                             | TPD_SS_OE   | 3.5                             | 3.75                            | 4                               | 4.25                            | 4.5                             | ns   |

|                             | TPD_SCK_OE  | 3.5                             | 3.75                            | 4                               | 4.25                            | 4.5                             | ns   |

1. Assumes CL of the relevant I/O standard as described in the input and output delay measurement tables.

#### Figure 4 • USPI Switching Characteristics

### 7.8.4 Tamper Detectors

The following section describes tamper detectors.

#### Table 91 • ADC Conversion Rate

| Parameter           | Description                                                                                                                                                  | Min      | Тур¹         | Max     |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|---------|

| TCONV1              | Time from enable changing from zero to non-zero value to first conversion completes. Minimum value applies when POWEROFF = 0.                                | 420 μs   |              | 470 μs  |

| Τζοννν              | Time between subsequent channel conversions.                                                                                                                 |          | 480 µs       |         |

| TSETUP              | Data channel and output to valid asserted. Data is held until next conversion completes, that is >480 $\mu s.$                                               | 0 ns     |              |         |

| Tvalid <sup>2</sup> | Width of the valid pulse.                                                                                                                                    | 1.625 μs |              | 2 µs    |

| Trate               | Time from start of first set of conversions to the start of the next set. Can be considered as the conversion rate. Is set by the conversion rate parameter. | 480 µs   | Rate × 32 μs | 8128 μs |

1. Min, typ, and max refer to variation due to functional configuration and the raw TVS value. The actual internal correction time will vary based on the raw TVS value.

2. The pulse width varies depending on the time taken to complete the internal calibration multiplication, this can be up to 375 ns.

**Note:** Once the TVS block is active, the enable signal is sampled 25 ns before the falling edge of valid. The next enabled channel in the sequence 0-1-2-3 is started; that is, if channel 0 has just completed and only channels 0 and 3 are enabled, the next channel will be 3. When all the enabled channels in the sequence 0-1-2-3 are completed, the TVS waits for the conversion rate timer to expire. The enable signal may be changed at any time if it changes to 4'b0000 while valid is asserted (and 25 ns before valid is deasserted), then no further conversions will be started.

#### Table 92 • Temperature and Voltage Sensor Electrical Characteristics

| Parameter                    | Min | Тур | Max | Unit | Condition |

|------------------------------|-----|-----|-----|------|-----------|

| Temperature sensing range    | -40 |     | 125 | °C   |           |

| Temperature sensing accuracy | -10 |     | 10  | °C   |           |

| Parameter                                                           | Symbol          | Тур  | Max | Unit |

|---------------------------------------------------------------------|-----------------|------|-----|------|

| Time from negation of RESPONSE to all I/Os re-enabled               | Tclr_io_disable | 28   | 38  | μs   |

| Time from triggering the response to security locked                | TLOCKDOWN       |      |     | ns   |

| Time from negation of RESPONSE to earlier security unlock condition | Tclr_lockdown   |      |     | ns   |

| Time from triggering the response to device enters RESET            | Ttr_RESET       | 11.7 | 14  | μs   |

| Time from triggering the response to start of zeroization           | Ttr_ZEROLISE    | 7.4  | 8.2 | ms   |

## 7.8.5 System Controller Suspend Switching Characteristics

The following table describes the characteristics of system controller suspend switching.

#### Table 95 • System Controller Suspend Entry and Exit Characteristics

| Parameter                                                         | Symbol                      | Definition                                | Тур | Max | Unit |

|-------------------------------------------------------------------|-----------------------------|-------------------------------------------|-----|-----|------|

| Time from TRSTb falling<br>edge to SUSPEND_EN signal<br>assertion | Tsuspend_Tr <sup>1, 2</sup> | Suspend entry time from TRST_N assertion  | 42  | 44  | ns   |

| Time from TRSTb rising edge to ACTIVE signal assertion            | $T_{suspend}$ exit          | Suspend exit time from<br>TRST_N negation | 361 | 372 | ns   |

1. ACTIVE indicates that the system controller is inactive or active regardless of the state of SUSPEND\_EN.

2. ACTIVE signal must never be asserted with SUSPEND\_EN is asserted.

### 7.8.6 Dynamic Reconfiguration Interface

The following table provides interface timing information for the DRI, which is an embedded APB slave interface within the FPGA fabric that does not use FPGA resources.

#### **Table 96 • Dynamic Reconfiguration Interface Timing Characteristics**

| Parameter      | Symbol   | Max | Unit |

|----------------|----------|-----|------|

| PCLK frequency | FPD_PCLK | 200 | MHz  |

# 7.9 Power-Up to Functional Timing

Microsemi non-volatile FPGA technology offers the fastest boot-time of any mid-range FPGA in the market. The following tables describes both cold-boot (from power-on) and warm-boot (assertion of DEVRST\_N pin or assertion of reset from the tamper macro) timing. The power-up diagrams assume all power supplies to the device are stable.

### 7.9.1 Power-On (Cold) Reset Initialization Sequence

The following cold reset timing diagram shows the initialization sequencing of the device.

### Table 101 • Cold and Warm Boot

| Parameter                                                                                                            | Symbol        | Min | Тур                    | Max                             | Unit | Condition |

|----------------------------------------------------------------------------------------------------------------------|---------------|-----|------------------------|---------------------------------|------|-----------|

| The time from T <sub>FAB_READY</sub> to<br>ready to program through<br>JTAG/SPI-Slave                                |               | 0   | 0                      | 0                               | ms   |           |

| The time from T <sub>FAB_READY</sub> to auto-update start                                                            |               |     | TPUF_OVHD <sup>1</sup> | $T_{PUF_OVHD^1}$                | ms   |           |

| The time from T <sub>FAB_READY</sub> to programming recovery start                                                   |               |     | TPUF_OVHD <sup>1</sup> | $T_{\text{PUF}\_\text{OVHD}^1}$ | ms   |           |

| The time from T <sub>FAB_READY</sub> to<br>the tamper flags being<br>available                                       | TTAMPER_READY | 0   | 0                      | 0                               | ms   |           |

| The time from<br>T <sub>FAB_READY</sub> to the Athena<br>Crypto co-processor being<br>available (for S devices only) | Tcrypto_ready | 0   | 0                      | 0                               | ms   |           |

1. Programming depends on the PUF to power up. Refer to TPUF\_OVHD at section Secure NVM Performance (see page 58).

# 7.9.8 I/O Calibration

The following tables specify the initial I/O calibration time for the fastest and slowest supported VDDI ramp times of 0.2 ms to 50 ms, respectively. This only applies to I/O banks specified by the user to be auto-calibrated.

#### Table 102 • I/O Initial Calibration Time (TCALIB)

| Ramp Time | Min (ms) | Max (ms) | Condition                      |

|-----------|----------|----------|--------------------------------|

| 0.2 ms    | 0.98     | 2.63     | Applies to HSIO and GPIO banks |

| 50 ms     | 41.62    | 62.19    | Applies to HSIO and GPIO banks |

#### Notes:

- The user may specify any VDDI ramp time in the range specified above. The nominal initial calibration time is given by the specified VDDI ramp time plus 2 ms.

- In order for IO calibration to start, VDDI and VDDAUX of the I/O bank must be higher than the trip point levels specified in I/O-Related Supplies (see page 66).

#### Table 103 • I/O Fast Recalibration Time (TRECALIB)

| I/O Type  | Min (ms) | Typ (ms) | Max (ms) | Condition                           |

|-----------|----------|----------|----------|-------------------------------------|

| GPIO bank | 0.16     | 0.20     | 0.24     | GPIO configured for 3.3 V operation |

| HSIO bank | 0.20     | 0.25     | 0.30     | HSIO configured for 1.8 V operation |

**Note:** In order to obtain fast re-calibration, the user must assert the relevant clock request signal from the FPGA fabric to the I/O bank controller.

The following table describes the time to enter Flash\*Freeze Mode and to exit Flash\*Freeze mode.

#### Table 107 • SPI Master Mode (PolarFire Master) During Device Initialization

| Parameter     | Symbol | Min | Тур | Max | Unit | Condition |

|---------------|--------|-----|-----|-----|------|-----------|

| SCK frequency | Fмsck  |     |     | 40  | MHz  |           |

#### Table 108 • SPI Slave Mode (PolarFire Slave)

| Parameter     | Symbol | Min | Тур | Max | Unit | Condition |

|---------------|--------|-----|-----|-----|------|-----------|

| SCK frequency | Fssck  |     |     | 80  | MHz  |           |

### 7.10.3 SmartDebug Probe Switching Characteristics

The following table describes characteristics of SmartDebug probe switching.

#### Table 109 • SmartDebug Probe Performance Characteristics

| Parameter                         | Symbol           | VDD =<br>1.0 V STD | V <sub>DD</sub> =<br>1.0 V – 1 | VDD =<br>1.05 V STD | V <sub>DD</sub> =<br>1.05 V - 1 | Unit |

|-----------------------------------|------------------|--------------------|--------------------------------|---------------------|---------------------------------|------|

| Maximum frequency of probe signal | Fmax             | 100                | 100                            | 100                 | 100                             | MHz  |

| Minimum delay of probe signal     | $T_{Min\_delay}$ | 13                 | 12                             | 13                  | 12                              | ns   |

| Maximum delay of probe signal     | $T_{Max\_delay}$ | 13                 | 12                             | 13                  | 12                              | ns   |

# 7.10.4 DEVRST\_N Switching Characteristics

\_

The following table describes characteristics of DEVRST\_N switching.

### Table 110 • DEVRST\_N Electrical Characteristics

| Parameter                  | Symbol     | Min  | Тур | Max | Unit | Condition                                                                  |

|----------------------------|------------|------|-----|-----|------|----------------------------------------------------------------------------|

| DEVRST_N ramp rate         | DRRAMP     |      | 10  |     | μs   | It must be a normal clean digital signal, with typical rise and fall times |

| DEVRST_N<br>assert time    | DRassert   | 1    |     |     | μs   | The minimum time for DEVRST_N assertion to be recognized                   |

| DEVRST_N<br>de-assert time | DRdeassert | 2.75 |     |     | ms   | The minimum time DEVRST_N needs to be de-asserted before assertion         |

### 7.10.5 FF\_EXIT Switching Characteristics

The following table describes characteristics of FF\_EXIT switching.

#### Table 111 • FF\_EXIT Electrical Characteristics

| Parameter                            | Symbol                | Min | Тур | Max | Unit | Condition                                                              |

|--------------------------------------|-----------------------|-----|-----|-----|------|------------------------------------------------------------------------|

| FF_EXIT_N ramp rate                  | FFRAMP                |     | 10  |     | μs   |                                                                        |

| Minimum FF_EXIT_N assert time        | FFassert              | 1   |     |     | μs   | The minimum time for FF_EXIT_N to be recognized                        |

| Minimum FF_EXIT_N de-<br>assert time | <b>FF</b><br>DEASSERT | 170 |     |     | μs   | The minimum time FF_EXIT_N needs to be<br>de-asserted before assertion |