Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Betano                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                              |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | LCD, POR, PWM, Voltage Detect, WDT                                               |

| Number of I/O              | 72                                                                               |

| Program Memory Size        | 48KB (48K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 2K x 8                                                                           |

| RAM Size                   | 3.5K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

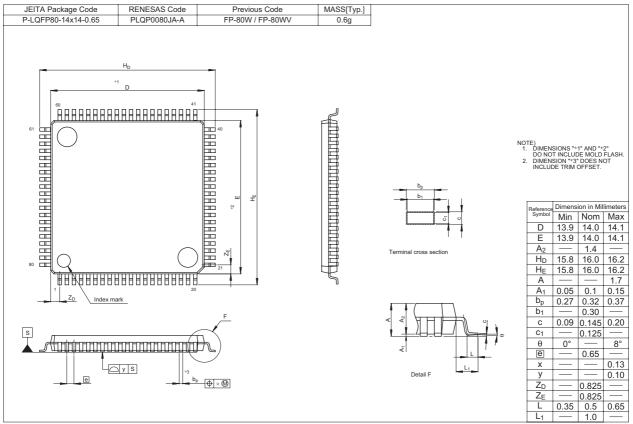

| Package / Case             | 80-LQFP                                                                          |

| Supplier Device Package    | 80-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f2la87anfa-v0 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | -                                    |              |              |              |              |              |                                      |              | -            | -            |              |              | -            |              |              | • •          |

|--------------|--------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Programmable | R8C/LA3A Group<br>Total: 26 I/O pins |              |              |              |              |              | R8C/LA5A Group<br>Total: 44 I/O pins |              |              |              |              |              |              |              |              |              |

| I/O Port     | Bit 7                                | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1                                | Bit 0        | Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

| P0           | —                                    | —            |              |              |              |              |                                      | —            | $\checkmark$ |

| P2           | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P3           | —                                    | _            |              |              | _            |              |                                      | _            | $\checkmark$ |

| P5           | —                                    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                         | $\checkmark$ |              | $\checkmark$ |

| P7           | —                                    | —            |              | —            |              | —            | $\checkmark$                         | —            | —            | —            | —            | —            | —            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P8           | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P9           | —                                    | —            |              |              | _            | _            | $\checkmark$                         | $\checkmark$ |              | _            |              |              |              | _            | $\checkmark$ | $\checkmark$ |

### Table 1.2 Programmable I/O Ports Provided for Each Group (R8C/LA3A Group, R8C/LA5A Group)

Notes:

1. The symbol " $\checkmark$ " indicates a programmable I/O port.

2. The symbol "-" indicates the settings should be made as follows:

- Set 0 to the corresponding bits in the PDi (i = 0, 3, 5, 7, 9) register. When read, the content is 0.

- Set 0 to the corresponding bits in the Pi (i = 0, 3, 5, 7, 9) register. When read, the content is 0.

| Programmable<br>I/O Port |              | R8C/LA6A Group<br>Total: 56 I/O pins |              |              |              |              |              | R8C/LA8A Group<br>Total: 72 I/O pins |              |              |              |              |              |              |              |              |

|--------------------------|--------------|--------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| NO FOIL                  | Bit 7        | Bit 6                                | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0                                | Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

| P0                       | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P1                       | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | _                                    | $\checkmark$ |

| P2                       | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P3                       | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P4                       | $\checkmark$ | $\checkmark$                         | —            | —            |              | _            |              | _                                    | $\checkmark$ |

| P5                       | —            | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                         |              | $\checkmark$ |

| P6                       | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | _                                    | $\checkmark$ |

| P7                       | —            | —                                    | —            | —            | —            | —            | —            | _                                    |              | $\checkmark$ |

| P8                       | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| P9                       | —            | —                                    | —            | —            | —            | —            | $\checkmark$ | $\checkmark$                         |              | —            | _            | _            | _            | —            | $\checkmark$ | $\checkmark$ |

Table 1.3

Programmable I/O Ports Provided for Each Group (R8C/LA6A Group, R8C/LA8A Group)

Notes:

1. The symbol " $\checkmark$ " indicates a programmable I/O port.

2. The symbol "-" indicates the settings should be made as follows:

- Set 0 to the corresponding bits in the PDi (i = 1, 4 to 7, 9) register. When read, the content is 0.

- Set 0 to the corresponding bits in the Pi (i = 1, 4 to 7, 9) register. When read, the content is 0.

- Set 0 to the corresponding bits in the P7DRR register. When read, the content is 0.

| Item                 |               | iction            | Specification                                                                                   |                                                                             |                                                                                         |  |  |  |  |  |  |

|----------------------|---------------|-------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Timer                | Timer RB0,    | , Timer RB1       | 8 bits x 2 (with 8-bit prescaler)                                                               |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               |                   |                                                                                                 |                                                                             | programmable waveform generation mode                                                   |  |  |  |  |  |  |

|                      |               |                   | (PWM output), programmable one-shot generation mode, programmable wait                          |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               |                   | one-shot generation mode                                                                        |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      | Timer RC      |                   | 16 bits × 1 (with 4 capture/compare registers)                                                  |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               |                   |                                                                                                 | Timer mode (input capture function, output compare function),               |                                                                                         |  |  |  |  |  |  |

|                      |               |                   |                                                                                                 | PWM mode (output: 3 pins), PWM2 mode (PWM output: 1 pin)                    |                                                                                         |  |  |  |  |  |  |

|                      | Timer RH      |                   |                                                                                                 | Real-time clock mode (counting of seconds, minutes, hours, day of the week, |                                                                                         |  |  |  |  |  |  |

|                      |               |                   |                                                                                                 | ate, month, year), output compare mode                                      |                                                                                         |  |  |  |  |  |  |

|                      |               | R8C/LA3A          | Timer RJ0,                                                                                      | 16 bits × 2                                                                 | Timer mode (period timer), pulse output mode                                            |  |  |  |  |  |  |

|                      | Timer RJ1     |                   | Timer RJ1                                                                                       |                                                                             | (output level inverted every period), event counter mode, pulse width measurement mode, |  |  |  |  |  |  |

|                      | Timer RJ2     |                   |                                                                                                 |                                                                             | pulse period measurement mode                                                           |  |  |  |  |  |  |

|                      |               | Group             | -                                                                                               |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               | R8C/LA6A          |                                                                                                 |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               | Group             | Time or D 10                                                                                    | 10 hite v 0                                                                 | -                                                                                       |  |  |  |  |  |  |

|                      |               | R8C/LA8A          | Timer RJ0,                                                                                      | 16 bits × 3                                                                 |                                                                                         |  |  |  |  |  |  |

|                      |               | Group             | Timer RJ1,<br>Timer RJ2                                                                         |                                                                             |                                                                                         |  |  |  |  |  |  |

| Serial               | UART0         |                   | 1 channel                                                                                       |                                                                             |                                                                                         |  |  |  |  |  |  |

| Interface            | UARTU         |                   | Clock synchronous serial I/O/UART                                                               |                                                                             |                                                                                         |  |  |  |  |  |  |

| Internace            | UART2         |                   | 1 channel                                                                                       |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      | 0/11/2        |                   | Clock synchronous serial I/O/UART, I <sup>2</sup> C mode (I <sup>2</sup> C-bus), multiprocessor |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               |                   | communication function                                                                          |                                                                             |                                                                                         |  |  |  |  |  |  |

| Synchron             | ous Serial    |                   | 1 (shared with I <sup>2</sup> C-bus)                                                            |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      | cation Unit ( | SSU)              |                                                                                                 | 1 0-503)                                                                    |                                                                                         |  |  |  |  |  |  |

| I <sup>2</sup> C bus |               | ,                 | 1 (shared with                                                                                  | SSU)                                                                        |                                                                                         |  |  |  |  |  |  |

| A/D Conv             | erter         | R8C/LA3A          | 10-bit resolutio                                                                                | n × 5 channels,                                                             | including sample and hold function, with sweep                                          |  |  |  |  |  |  |

|                      |               | Group             |                                                                                                 |                                                                             | luded (measurement temperature range:                                                   |  |  |  |  |  |  |

|                      |               |                   | –20 to 85 °C (N                                                                                 | V version)/ -40 t                                                           | to 85 °C (D version))                                                                   |  |  |  |  |  |  |

|                      |               | R8C/LA5A          | 10-bit resolutio                                                                                | n × 7 channels,                                                             | including sample and hold function, with sweep                                          |  |  |  |  |  |  |

|                      |               | Group             |                                                                                                 |                                                                             | luded (measurement temperature range:                                                   |  |  |  |  |  |  |

|                      |               |                   |                                                                                                 |                                                                             | to 85 °C (D version))                                                                   |  |  |  |  |  |  |

|                      |               | R8C/LA6A          |                                                                                                 |                                                                             | including sample and hold function, with sweep                                          |  |  |  |  |  |  |

|                      |               | Group             |                                                                                                 |                                                                             | luded (measurement temperature range:                                                   |  |  |  |  |  |  |

|                      |               |                   |                                                                                                 |                                                                             | to 85 °C (D version))                                                                   |  |  |  |  |  |  |

|                      |               | R8C/LA8A          |                                                                                                 |                                                                             | s, including sample and hold function, with sweep                                       |  |  |  |  |  |  |

|                      |               | Group             |                                                                                                 |                                                                             | luded (measurement temperature range:                                                   |  |  |  |  |  |  |

| 0                    |               |                   |                                                                                                 |                                                                             | to 85 °C (D version))                                                                   |  |  |  |  |  |  |

| Comparat             | or B          | R8C/LA3A          | 1 circuit (comp                                                                                 | arator B1)                                                                  |                                                                                         |  |  |  |  |  |  |

|                      |               | Group             | O ainavita (c.e.e.                                                                              | neveter D4                                                                  |                                                                                         |  |  |  |  |  |  |

|                      |               | R8C/LA5A          | ∠ circuits (com                                                                                 | parator B1, com                                                             | iparator B3)                                                                            |  |  |  |  |  |  |

|                      |               | Group<br>R8C/LA6A | 4                                                                                               |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               |                   |                                                                                                 |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               | Group             | 4                                                                                               |                                                                             |                                                                                         |  |  |  |  |  |  |

|                      |               | R8C/LA8A<br>Group |                                                                                                 |                                                                             |                                                                                         |  |  |  |  |  |  |

| L                    |               | Group             |                                                                                                 |                                                                             |                                                                                         |  |  |  |  |  |  |

Table 1.7Specifications (2)

| Item                    | Pin Name                                                                                                                                                           | I/O Type | Description                                                                                                                                                                                                                                                                                           |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> C bus    | SCL                                                                                                                                                                | I/O      | Clock I/O pin.                                                                                                                                                                                                                                                                                        |

|                         | SDA                                                                                                                                                                | I/O      | Data I/O pin.                                                                                                                                                                                                                                                                                         |

| SSU                     | SSI                                                                                                                                                                | I/O      | Data I/O pin.                                                                                                                                                                                                                                                                                         |

|                         | SCS                                                                                                                                                                | I/O      | Chip-select signal I/O pin.                                                                                                                                                                                                                                                                           |

|                         | SSCK                                                                                                                                                               | I/O      | Clock I/O pin.                                                                                                                                                                                                                                                                                        |

|                         | SSO                                                                                                                                                                | I/O      | Data I/O pin.                                                                                                                                                                                                                                                                                         |

| Reference voltage input | VREF                                                                                                                                                               | I        | Reference voltage input pin for the A/D converter.                                                                                                                                                                                                                                                    |

| A/D converter           | AN0 to AN11                                                                                                                                                        | I        | A/D converter analog input pins.                                                                                                                                                                                                                                                                      |

|                         | ADTRG                                                                                                                                                              | I        | AD external trigger input pin.                                                                                                                                                                                                                                                                        |

| Comparator B            | IVCMP1, IVCMP3                                                                                                                                                     | I        | Comparator B analog voltage input pins.                                                                                                                                                                                                                                                               |

|                         | IVREF1, IVREF3                                                                                                                                                     | I        | Comparator B reference voltage input pins.                                                                                                                                                                                                                                                            |

| I/O ports               | P0_0 to P0_7,<br>P1_0 to P1_7,<br>P2_0 to P2_7,<br>P3_0 to P3_7,<br>P4_0 to P4_7,<br>P5_0 to P5_6,<br>P6_0 to P6_7<br>P7_0 to P7_6,<br>P8_0 to P8_7,<br>P9_0, P9_1 | I/O      | CMOS I/O ports. Each port has an I/O select direction register,<br>allowing each pin in the port to be directed for input or output<br>individually.<br>Any port set to input can be set to use a pull-up resistor or not<br>by a program.<br>Ports P7_0, P7_1 and P8 can be used as LED drive ports. |

| Segment output          | SEG0 to SEG39                                                                                                                                                      | 0        | LCD segment output pins.                                                                                                                                                                                                                                                                              |

| Common output           | COM0 to COM3,<br>COMEXP                                                                                                                                            | 0        | LCD common output pins.                                                                                                                                                                                                                                                                               |

| LCD power supply        | VL1                                                                                                                                                                | I        | Apply the following voltage: 1 V $\leq$ VL1 $\leq$ VCC and VL1 $\leq$ VL2.                                                                                                                                                                                                                            |

|                         | VL2                                                                                                                                                                | I        | Apply the following voltage: VL2 $\leq$ 5.5 V and VL1 $\leq$ VL2 $\leq$ VL3.                                                                                                                                                                                                                          |

|                         | VL3                                                                                                                                                                | I        | Apply the following voltage: VL3 $\leq$ 5.5 V and VL2 $\leq$ VL3.                                                                                                                                                                                                                                     |

| Table 1.21 | Pin Functions for R8C/LA8A Group (2) |

|------------|--------------------------------------|

|------------|--------------------------------------|

I: Input O: Output I/O: Input and output

Note:

1. Contact the oscillator manufacturer for oscillation characteristics.

### 3. Memory

### 3. Memory

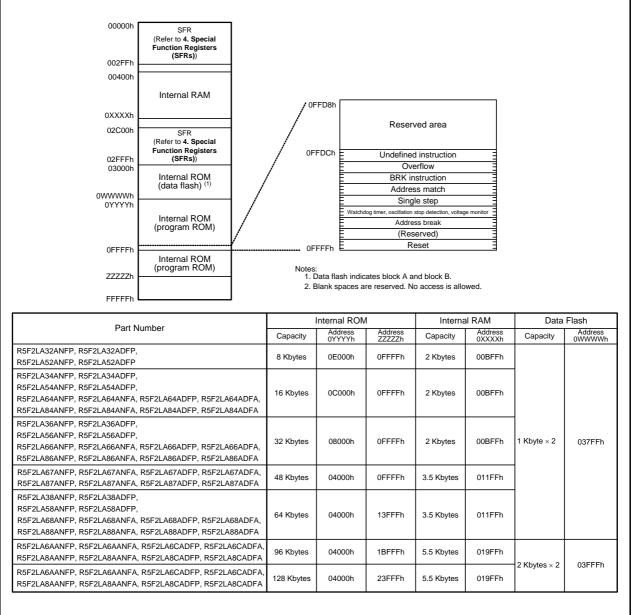

Figure 3.1 shows a Memory Map of each group. Each group has a 1-Mbyte address space from addresses 00000h to FFFFh. For example, a 48-Kbyte internal ROM area is allocated addresses 04000h to 0FFFFh.

The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. The starting address of each interrupt routine is stored here.

The internal ROM (data flash) is allocated higher addresses, beginning with address 03000h.

For example, two 1-Kbyte internal ROM (data flash) areas are allocated addresses 03000h to 037FFh. Two 2-Kbyte internal RAM (data flash) areas are allocated addresses 03000h to 03FFFh.

The internal RAM is allocated higher addresses, beginning with address 00400h. For example, a 3.5-Kbyte internal RAM area is allocated addresses 00400h to 011FFh. The internal RAM is used not only for data storage but also as a stack area when a subroutine is called or when an interrupt request is acknowledged.

Special function registers (SFRs) are allocated addresses 00000h to 002FFh and 02C00h to 02FFh. Peripheral function control registers are allocated here. All unallocated spaces within the SFRs are reserved and cannot be accessed by users.

Figure 3.1 Memory Map

| ddress<br>0080h | Register Timer RJ0 Control Register           | Symbol<br>TRJ0CR | After Reset |

|-----------------|-----------------------------------------------|------------------|-------------|

|                 |                                               |                  |             |

| 0081h           | Timer RJ0 I/O Control Register                | TRJOIOC          | 00h         |

| 0082h           | Timer RJ0 Mode Register                       | TRJOMR           | 00h         |

| 0083h           | Timer RJ0 Event Pin Select Register           | TRJ0ISR          | 00h         |

| 0084h           | Timer RJ0 Register                            | TRJ0             | FFh         |

| 0085h           |                                               |                  | FFh         |

| 0086h           |                                               |                  |             |

| 0087h           |                                               |                  |             |

| 0088h           | Timer RJ1 Control Register                    | TRJ1CR           | 00h         |

| 0089h           | Timer RJ1 I/O Control Register                | TRJ1IOC          | 00h         |

|                 | 5                                             |                  |             |

| 008Ah           | Timer RJ1 Mode Register                       | TRJ1MR           | 00h         |

| 008Bh           | Timer RJ1 Event Pin Select Register           | TRJ1ISR          | 00h         |

| 008Ch           | Timer RJ1 Register                            | TRJ1             | FFh         |

| 008Dh           |                                               |                  | FFh         |

| 008Eh           |                                               |                  |             |

| 008Fh           |                                               |                  |             |

| 0090h           | Timer RJ2 Control Register                    | TRJ2CR           | 00h         |

|                 | 0                                             |                  |             |

| 0091h           | Timer RJ2 I/O Control Register                | TRJ2IOC          | 00h         |

| 0092h           | Timer RJ2 Mode Register                       | TRJ2MR           | 00h         |

| 0093h           | Timer RJ2 Event Pin Select Register           | TRJ2ISR          | 00h         |

| 0094h           | Timer RJ2 Register                            | TRJ2             | FFh         |

| 0095h           | 1                                             |                  | FFh         |

| 0096h           |                                               |                  |             |

| 0097h           |                                               |                  |             |

| 009711<br>0098h | Timer RB1 Control Register                    | TRB1CR           | 00h         |

|                 | 5                                             |                  |             |

| 0099h           | Timer RB1 One-Shot Control Register           | TRB10CR          | 00h         |

| 009Ah           | Timer RB1 I/O Control Register                | TRB1IOC          | 00h         |

| 009Bh           | Timer RB1 Mode Register                       | TRB1MR           | 00h         |

| 009Ch           | Timer RB1 Prescaler Register                  | TRB1PRE          | FFh         |

| 009Dh           | Timer RB1 Secondary Register                  | TRB1SC           | FFh         |

| 009Eh           | Timer RB1 Primary Register                    | TRB1PR           | FFh         |

|                 | Timer (CDTT Timary (Cegister                  | INDII K          | 1111        |

| 009Fh           |                                               |                  |             |

| 00A0h           | UART0 Transmit/Receive Mode Register          | U0MR             | 00h         |

| 00A1h           | UART0 Bit Rate Register                       | U0BRG            | XXh         |

| 00A2h           | UART0 Transmit Buffer Register                | U0TB             | XXh         |

| 00A3h           |                                               |                  | XXh         |

| 00A4h           | UART0 Transmit/Receive Control Register 0     | U0C0             | 00001000b   |

| 00A5h           | UART0 Transmit/Receive Control Register 1     | U0C1             | 00000010b   |

| 00/(6h          | UARTO Receive Buffer Register                 | UORB             | XXh         |

|                 | UARTO Receive Buller Register                 | UURB             |             |

| 00A7h           |                                               |                  | XXh         |

| 00A8h           | UART2 Transmit/Receive Mode Register          | U2MR             | 00h         |

| 00A9h           | UART2 Bit Rate Register                       | U2BRG            | XXh         |

| 00AAh           | UART2 Transmit Buffer Register                | U2TB             | XXh         |

| 00ABh           | 1 ~                                           |                  | XXh         |

| 00ACh           | UART2 Transmit/Receive Control Register 0     | U2C0             | 00001000b   |

| 00ACh           | UART2 Transmit/Receive Control Register 0     | U2C1             | 00001000b   |

|                 | 5                                             | U2RB             |             |

| 00AEh           | UART2 Receive Buffer Register                 | UZKB             | XXh         |

| 00AFh           |                                               |                  | XXh         |

| 00B0h           | UART2 Digital Filter Function Select Register | URXDF            | 00h         |

| 00B1h           |                                               |                  |             |

| 00B2h           |                                               |                  |             |

| 00B3h           |                                               |                  |             |

| 00B4h           |                                               |                  |             |

|                 |                                               |                  |             |

| 00B5h           |                                               |                  |             |

| 00B6h           |                                               |                  |             |

| 00B7h           |                                               |                  |             |

| 00B8h           |                                               |                  |             |

| 00B9h           |                                               |                  |             |

| 00BAh           |                                               |                  |             |

| 00BBh           | UART2 Special Mode Register 5                 | U2SMR5           | 00h         |

|                 |                                               |                  |             |

| 00BCh           | UART2 Special Mode Register 4                 | U2SMR4           | 00h         |

| 00BDh           | UART2 Special Mode Register 3                 | U2SMR3           | 000X0X0Xb   |

|                 | UART2 Special Mode Register 2                 | U2SMR2           | X000000b    |

| 00BEh           | UART2 Special Mode Register                   | 020101112        | X000000D    |

| Table 4.12         SFR Information for R8C/LA8A Group (3) | (1) |

|-----------------------------------------------------------|-----|

|-----------------------------------------------------------|-----|

Note:

1. Blank spaces are reserved. No access is allowed.

|                | SFR Information for RoC/LAGA Group (6) (*) | Cuma ha - I | Attor Doc -4 |

|----------------|--------------------------------------------|-------------|--------------|

| Address        | Register                                   | Symbol      | After Reset  |

| 0140h          |                                            |             |              |

| 0141h          |                                            |             |              |

| 0142h          |                                            |             |              |

| 0143h          |                                            |             |              |

| 0144h          |                                            |             |              |

| 0145h          |                                            |             |              |

| 0146h          |                                            |             |              |

| 0147h          |                                            |             |              |

| 0148h          |                                            |             |              |

| 0149h          |                                            |             |              |

| 014Ah          |                                            |             |              |

| 014Bh          |                                            |             |              |

| 014Ch          |                                            |             |              |

| 014Dh          |                                            |             |              |

| 014Eh          |                                            |             |              |

| 014Fh          |                                            |             |              |

| 0150h          |                                            |             |              |

| 0151h          |                                            |             |              |

| 0152h          |                                            |             |              |

| 0153h          |                                            |             |              |

| 0154h          |                                            |             |              |

| 0155h          |                                            |             |              |

| 0156h          |                                            |             |              |

| 0157h          |                                            |             |              |

| 0158h          |                                            |             |              |

| 0159h          |                                            |             |              |

| 015Ah          |                                            |             |              |

| 015Bh          |                                            |             |              |

| 015Ch          |                                            |             |              |

| 015Dh          |                                            |             |              |

| 015Eh          |                                            |             |              |

| 015Fh          |                                            |             |              |

| 0160h          |                                            |             |              |

| 0161h          |                                            |             |              |

| 0162h          |                                            |             |              |

| 0163h          |                                            |             |              |

| 0164h          |                                            |             |              |

| 0165h          |                                            |             |              |

| 0166h          |                                            |             |              |

| 0167h          |                                            |             |              |

| 0168h          |                                            |             |              |

| 0169h          |                                            |             |              |

| 016Ah          |                                            |             |              |

| 016Bh          |                                            |             |              |

| 016Ch          |                                            |             |              |

| 016Ch<br>016Dh |                                            |             |              |

| 016Dh<br>016Eh |                                            |             |              |

| 016Eh<br>016Fh |                                            |             |              |

| 016Fh<br>0170h |                                            |             |              |

|                |                                            |             |              |

| 0171h          |                                            | l           |              |

| 0172h          |                                            |             |              |

| 0173h          |                                            |             |              |

| 0174h          |                                            |             |              |

| 0175h          |                                            |             |              |

| 0176h          |                                            |             |              |

| 0177h          |                                            |             |              |

| 0178h          |                                            |             |              |

| 0179h          |                                            |             |              |

| 017Ah          |                                            |             |              |

| 017Bh          |                                            |             |              |

| 017Ch          |                                            |             |              |

| 017Dh          |                                            |             |              |

| 017Eh          |                                            |             | 1            |

| 017Fh          |                                            |             | 1            |

| X: Undefined   |                                            | I           | 1            |

Table 4.15

SFR Information for R8C/LA8A Group (6) <sup>(1)</sup>

X: Undefined Note:

1. Blank spaces are reserved. No access is allowed.

| Address | Register                          | Symbol  | After Reset |

|---------|-----------------------------------|---------|-------------|

| 0200h   | LCD Control Register              | LCR0    | 00h         |

| 0201h   |                                   |         |             |

| 0202h   | LCD Option Clock Control Register | LCR2    | 00h         |

| 0203h   | LCD Clock Control Register        | LCR3    | 00h         |

| 0204h   | LCD Display Control Register      | LCR4    | 00h         |

| 0205h   |                                   |         |             |

| 0206h   | LCD Port Select Register 0        | LSE0    | 00h         |

| 0207h   | LCD Port Select Register 1        | LSE1    | 00h         |

| 0208h   | LCD Port Select Register 2        | LSE2    | 00h         |

| 0209h   | LCD Port Select Register 3        | LSE3    | 00h         |

| 020Ah   | LCD Port Select Register 4        | LSE4    | 00h         |

| 020Bh   | LCD Port Select Register 5        | LSE5    | 00h         |

| 020Ch   |                                   |         |             |

| 020Dh   |                                   |         |             |

| 020Eh   |                                   |         |             |

| 020Fh   |                                   |         |             |

| 0210h   | LCD Display Data Register         | LRAOL   | XXh         |

| 0211h   |                                   | LRA1L   | XXh         |

| 0212h   | ]                                 | LRA2L   | XXh         |

| 0213h   |                                   | LRA3L   | XXh         |

| 0214h   | ]                                 | LRA4L   | XXh         |

| 0215h   |                                   | LRA5L   | XXh         |

| 0216h   |                                   | LRA6L   | XXh         |

| 0217h   |                                   | LRA7L   | XXh         |

| 0218h   |                                   | LRA8L   | XXh         |

| 0219h   |                                   | LRA9L   | XXh         |

| 021Ah   |                                   | LRA10L  | XXh         |

| 021Bh   |                                   | LRA11L  | XXh         |

| 021Ch   |                                   | LRA12L  | XXh         |

| 021Dh   |                                   | LRA13L  | XXh         |

| 021Eh   |                                   | LRA14L  | XXh         |

| 021Fh   |                                   | LRA15L  | XXh         |

| 0220h   |                                   | LRA16L  | XXh         |

| 0221h   |                                   | LRA17L  | XXh         |

| 0222h   |                                   | LRA18L  | XXh         |

| 0223h   |                                   | LRA19L  | XXh         |

| 0224h   |                                   | LRA20L  | XXh         |

| 0225h   |                                   | LRA21L  | XXh         |

| 0226h   |                                   | LRA22L  | XXh         |

| 0227h   |                                   | LRA23L  | XXh         |

| 0228h   |                                   | LRA24L  | XXh         |

| 0229h   |                                   | LRA25L  | XXh         |

| 022Ah   | 1                                 | LRA26L  | XXh         |

| 022Bh   | 1                                 | LRA27L  | XXh         |

| 022Ch   | 1                                 | LRA28L  | XXh         |

| 022Dh   | 1                                 | LRA29L  | XXh         |

| 022Eh   | 1                                 | LRA30L  | XXh         |

| 022Fh   | 1                                 | LRA31L  | XXh         |

| 0230h   | 1                                 | LRA32L  | XXh         |

| 0231h   | 1                                 | LRA33L  | XXh         |

| 0232h   | 1                                 | LRA34L  | XXh         |

| 0233h   | 1                                 | LRA35L  | XXh         |

| 0234h   | 1                                 | LRA36L  | XXh         |

| 0235h   | 1                                 | LRA37L  | XXh         |

| 0236h   | 1                                 | LRA38L  | XXh         |

| 0237h   | 4                                 | LRA39L  | XXh         |

| :       |                                   | 2.0.002 |             |

| 2FFFh   |                                   |         |             |

|         |                                   |         |             |

### Table 4.18 SFR Information for R8C/LA8A Group (9) <sup>(1)</sup>

X: Undefined Note:

1. Blank spaces are reserved. No access is allowed.

| Symbol           | Parameter                                                              | Conditions                  |            | Unit |                                |       |

|------------------|------------------------------------------------------------------------|-----------------------------|------------|------|--------------------------------|-------|

|                  |                                                                        |                             | Min.       | Тур. | Max.                           | Unit  |

| -                | Program/erase endurance (1)                                            |                             | 10,000 (2) | -    | -                              | times |

| _                | Byte program time                                                      |                             | -          | 80   | -                              | μS    |

| -                | Block erase time                                                       |                             | -          | 0.12 | -                              | S     |

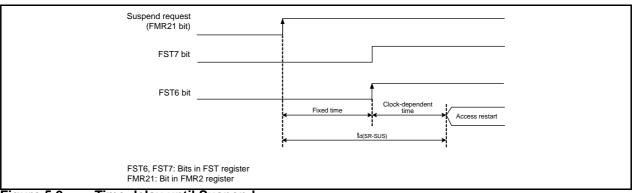

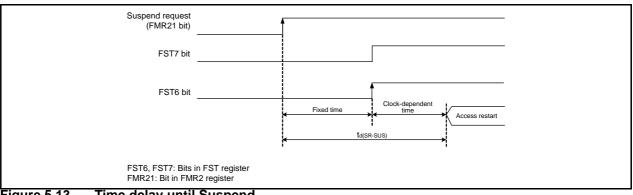

| td(SR-SUS)       | Time delay from suspend request<br>until suspend                       |                             | -          | _    | 0.25 + CPU clock<br>× 3 cycles | ms    |

| -                | Time from suspend until erase restart                                  |                             | -          | -    | 30 + CPU clock<br>× 1 cycle    | μS    |

| td(CMDRST-READY) | Time from when command is forcibly terminated until reading is enabled |                             | -          | -    | 30 + CPU clock<br>× 1 cycle    | μS    |

| -                | Program, erase voltage                                                 |                             | 1.8        | -    | 5.5                            | V     |

| -                | Read voltage                                                           |                             | 1.8        | -    | 5.5                            | V     |

| -                | Program, erase temperature                                             |                             | 0          | -    | 60                             | °C    |

| _                | Data hold time <sup>(6)</sup>                                          | Ambient temperature = 85 °C | 10         | -    | -                              | year  |

### Table 5.7Flash Memory (Program ROM) Characteristics<br/>(Vcc = 1.8 to 5.5 V and Topr = 0 to 60 °C, unless otherwise specified.)

Notes:

1. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis.

If the programming and erasure endurance is n (n = 1,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to different addresses in block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one.

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

2. Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

- 3. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. It is also advisable to retain data on the erasure endurance of each block and limit the number of erase operations to a certain number.

- 4. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

5. Customers desiring program/erase failure rate information should contact their Renesas technical support representative.

6. The data hold time includes time that the power supply is off or the clock is not supplied.

# Table 5.8Flash Memory (Data flash Block A and Block B) Characteristics<br/>(Vcc = 1.8 to 5.5 V and Topr = -20 to 85 °C (N version)/ -40 to 85 °C (D version), unless<br/>otherwise specified.)

| Symbol           | Parameter                                                              | Conditiono                  |               | Unit |                                |           |  |

|------------------|------------------------------------------------------------------------|-----------------------------|---------------|------|--------------------------------|-----------|--|

| Symbol           | Parameter                                                              | Conditions                  | Min.          | Тур. | Max.                           | Unit      |  |

| -                | Program/erase endurance (1)                                            |                             | 10,000<br>(2) | -    | -                              | time<br>s |  |

| -                | Byte program time<br>(program/erase endurance ≤ 10,000 times)          |                             | -             | 150  | -                              | μS        |  |

| -                | Block erase time<br>(program/erase endurance ≤ 10,000 times)           |                             | -             | 0.05 | 1                              | S         |  |

| td(SR-SUS)       | Time delay from suspend request until suspend                          |                             | -             | -    | 0.25 + CPU clock<br>× 3 cycles | ms        |  |

| -                | Time from suspend until erase restart                                  |                             | -             | -    | 30 + CPU clock<br>× 1 cycle    | μS        |  |

| td(CMDRST-READY) | Time from when command is forcibly terminated until reading is enabled |                             | -             | -    | 30 + CPU clock<br>× 1 cycle    | μS        |  |

| -                | Program, erase voltage                                                 |                             | 1.8           | -    | 5.5                            | V         |  |

| -                | Read voltage                                                           |                             | 1.8           | -    | 5.5                            | V         |  |

| -                | Program, erase temperature                                             |                             | -20 (6)       | -    | 85                             | °C        |  |

| -                | Data hold time <sup>(7)</sup>                                          | Ambient temperature = 85 °C | 10            | -    | _                              | year      |  |

Notes:

1. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis.

If the programming and erasure endurance is n (n = 10,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to different addresses in block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one.

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

2. Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

3. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. In addition, averaging the erasure endurance between blocks A and B can further reduce the actual erasure endurance. It is also advisable to retain data on the erasure endurance of each block and limit the number of erase operations to a certain number.

4. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

5. Customers desiring program/erase failure rate information should contact their Renesas technical support representative.

6. -40 °C for D version.

7. The data hold time includes time that the power supply is off or the clock is not supplied.

| <b>r</b> |                                  | 1                        |         |                |                | Condition               |             |                                                                          | 0                                                                                                                                                              | tondo | - d         |     |      |

|----------|----------------------------------|--------------------------|---------|----------------|----------------|-------------------------|-------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|-----|------|

|          |                                  |                          | Osail   | lation         | 0-             | Chin                    | Condition   | 1                                                                        | Τ                                                                                                                                                              | 5     | tanda       | ra  |      |

| Symbol   | Parameter                        |                          | Cir     | lation<br>cuit | Osc            | Chip<br>illator<br>Low- | CPU Clock   | Low-Power-<br>Consumption                                                | Other                                                                                                                                                          | Min.  | Typ.<br>(3) | Max | Unit |

|          |                                  |                          | XIN (2) | XCIN           | High-<br>Speed | Speed                   |             | Setting                                                                  |                                                                                                                                                                |       | (3)         | •   |      |

| lcc      | Power                            | High-                    | 8 MHz   | Off            | Off            | 125 kHz                 | No division | -                                                                        |                                                                                                                                                                | -     | 2.1         | -   | mΑ   |

|          | supply<br>current <sup>(1)</sup> | speed<br>clock<br>mode   | 8 MHz   | Off            | Off            | 125 kHz                 | Divide-by-8 | -                                                                        |                                                                                                                                                                | -     | 0.9         | -   | mA   |

|          |                                  | High-                    | Off     | Off            | 5 MHz          |                         | No division | -                                                                        |                                                                                                                                                                | -     | 1.8         | 5   | mΑ   |

|          |                                  | speed<br>on-chip         | Off     | Off            | 5 MHz          | 125 kHz                 |             | -                                                                        |                                                                                                                                                                | I     | 1.1         | -   | mΑ   |

|          |                                  | oscillator<br>mode       | Off     | Off            | 4 MHz          | 125 kHz                 | -           | MSTCR0 = BEh<br>MSTCR1 = 3Fh                                             |                                                                                                                                                                | -     | 0.9         | -   | mA   |

|          |                                  | Low-<br>speed<br>on-chip | Off     | Off            | Off            | 125 kHz                 |             | FMR27 = 1<br>VCA20 = 0                                                   |                                                                                                                                                                | -     | 106         | 300 | μA   |

|          |                                  | oscillator<br>mode       | Off     | Off            | Off            | 125 kHz                 | Divide-by-8 | FMR27 = 1<br>VCA20 = 0                                                   |                                                                                                                                                                | -     | 54          | 200 | μA   |

|          |                                  | Low-<br>speed<br>clock   | Off     | 32 kHz         | Off            | Off                     | No division | FMR27 = 1<br>VCA20 = 0                                                   |                                                                                                                                                                | -     | 54          | 200 | μA   |

|          |                                  | mode                     | Off     | 32 kHz         | Off            | Off                     | No division | FMSTP = 1<br>VCA20 = 0                                                   | Flash memory off<br>Program operation on RAM                                                                                                                   | -     | 36          | -   | μA   |

|          |                                  | Wait<br>mode             | Off     | Off            | Off            | 125 kHz                 | -           | VCA27 = 0<br>VCA26 = 0<br>VCA25 = 0<br>VCA20 = 1                         | While a WAIT instruction is<br>executed<br>Peripheral clock operation                                                                                          | -     | 9.0         | 50  | μA   |

|          |                                  |                          | Off     | Off            | Off            | 125 kHz                 | -           | VCA27 = 0<br>VCA26 = 0<br>VCA25 = 0<br>VCA20 = 1<br>CM02 = 1<br>CM01 = 1 | While a WAIT instruction is<br>executed<br>Peripheral clock off                                                                                                | -     | 2.5         | 31  | μA   |

|          |                                  |                          | Off     | 32 kHz         | Off            | Off                     | -           | VCA27 = 0<br>VCA26 = 0<br>VCA25 = 0<br>VCA20 = 1<br>CM02 = 1<br>CM01 = 0 | While a WAIT LCD drive<br>instruction is<br>executed (4)<br>Peripheral When external<br>clock off division<br>Timer RH<br>operation in<br>real-time clock mode | -     | 2.4         | 1   | μA   |

|          |                                  |                          | Off     | 32 kHz         | Off            | Off                     | _           | VCA27 = 0<br>VCA26 = 0<br>VCA25 = 0<br>VCA20 = 1<br>CM02 = 1<br>CM01 = 1 | While a WAIT instruction is<br>executed<br>Peripheral clock off<br>Timer RH operation in real-<br>time clock mode                                              | -     | 1.7         | 1   | μA   |

|          |                                  | Stop<br>mode             | Off     | Off            | Off            | Off                     | -           | VCA27 = 0<br>VCA26 = 0<br>VCA25 = 0<br>CM10 = 1                          | Topr = 25 °C<br>Peripheral clock off                                                                                                                           | -     | 0.5         | 2.2 | μA   |

|          |                                  |                          | Off     | Off            | Off            | Off                     | -           | VCA27 = 0<br>VCA26 = 0<br>VCA25 = 0<br>CM10 = 1                          | Topr = 85 °C<br>Peripheral clock off                                                                                                                           | -     | 1.2         | -   | μA   |

|          |                                  | Power-<br>off mode       | Off     | Off            | Off            | Off                     | -           | -                                                                        | Power-off 0<br>Topr = 25 °C                                                                                                                                    | -     | 0.01        | 0.1 | μA   |

|          |                                  |                          | Off     | Off            | Off            | Off                     | -           | -                                                                        | Power-off 0<br>Topr = 85 °C                                                                                                                                    | -     | 0.02        | -   | μA   |

|          |                                  |                          | Off     | 32 kHz         | Off            | Off                     | -           | VCA27 = 0<br>VCA26 = 0<br>VCA25 = 0<br>CM10 = 1                          | Power-off 2<br>Topr = 25 °C                                                                                                                                    | -     | 1.2         | 4   | μA   |

|          |                                  |                          | Off     | 32 kHz         | Off            | Off                     | _           | VCA27 = 0<br>VCA26 = 0<br>VCA25 = 0<br>CM10 = 1                          | Power-off 2<br>Topr = 85 °C                                                                                                                                    | -     | 2           | -   | μA   |

#### **Table 5.23** DC Characteristics (6) [1.8 V $\leq$ Vcc < 2.7 V] (Topr = -20 to 85 °C (N version)/ -40 to 85 °C (D version), unless otherwise specified.)

Notes: 1. 2. 3. 4.

Vcc = 1.8 V to 2.7 V, single chip mode, output pins are open, and other pins are Vss. XIN is set to square wave input. Vcc = 2.2 V VLCD = Vcc, external division resistors are used for VL3 to VL1, 1/3 bias, 1/4 duty, f(FR) = 64 Hz, SEG0 to SEG26 are selected, and segment and common output pins are open. The standard value does not include the current that flows through external division resistors.

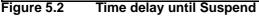

### 5.1.5 AC Characteristics

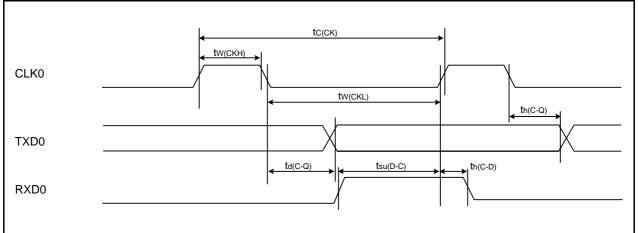

# Table 5.24Timing Requirements of Synchronous Serial Communication Unit (SSU)<br/>(Vcc = 1.8 to 5.5 V, Vss = 0 V, and Topr = -20 to 85 °C (N version)/<br/>-40 to 85 °C (D version), unless otherwise specified.)

| Symbol        | Paramete               | w          | Conditions                                      |            | Stand | lard          | Unit     |

|---------------|------------------------|------------|-------------------------------------------------|------------|-------|---------------|----------|

| Symbol        | Paramete               | ſ          | Conditions                                      | Min.       | Тур.  | Max.          | Unit     |

| tsucyc        | SSCK clock cycle time  | e          |                                                 | 4          | -     | -             | tcyc (1) |