Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | 8051                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | UART/USART                                                             |

| Peripherals                | POR                                                                    |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LCC (J-Lead)                                                        |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p80c32sbaa-512 |

80C51 8-bit microcontroller family 128/256 byte RAM ROMless low voltage (2.7V-5.5V), low power, high speed (33 MHz)

80C31/80C32

#### DESCRIPTION

The Philips 80C31/32 is a high-performance static 80C51 design fabricated with Philips high-density CMOS technology with operation from 2.7 V to 5.5 V.

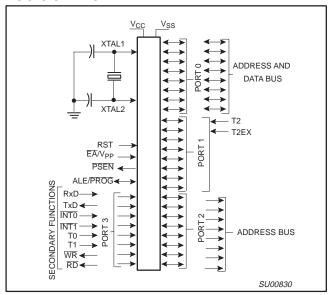

The 80C31/32 ROMless devices contain a 128  $\times$  8 RAM/256  $\times$  8 RAM, 32 I/O lines, three 16-bit counter/timers, a six-source, four-priority level nested interrupt structure, a serial I/O port for either multi-processor communications, I/O expansion or full duplex UART, and on-chip oscillator and clock circuits.

In addition, the device is a low power static design which offers a wide range of operating frequencies down to zero. Two software selectable modes of power reduction—idle mode and power-down mode are available. The idle mode freezes the CPU while allowing the RAM, timers, serial port, and interrupt system to continue functioning. The power-down mode saves the RAM contents but freezes the oscillator, causing all other chip functions to be inoperative. Since the design is static, the clock can be stopped without loss of user data and then the execution resumed from the point the clock was stopped.

#### **SELECTION TABLE**

For applications requiring more ROM and RAM, see the 8XC54/58 and 8XC51RA+/RB+/RC+/80C51RA+ data sheet.

| ROM/EPROM<br>Memory Size<br>(X by 8) | RAM Size<br>(X by 8) | Programmable<br>Timer Counter<br>(PCA) | Hardware<br>Watch Dog<br>Timer |  |  |  |

|--------------------------------------|----------------------|----------------------------------------|--------------------------------|--|--|--|

| 80C31/8XC51                          |                      |                                        |                                |  |  |  |

| 0K/4K                                | 128                  | No                                     | No                             |  |  |  |

| 80C32/8XC52/54                       | /58                  |                                        |                                |  |  |  |

| 0K/8K/16K/32K                        | 256                  | No                                     | No                             |  |  |  |

| 80C51RA+/8XC5                        | 1RA+/RB+/RC          | +                                      |                                |  |  |  |

| 0K/8K/16K/32K                        | 512                  | Yes                                    | Yes                            |  |  |  |

| 8XC51RD+                             |                      |                                        |                                |  |  |  |

| 64K                                  | 1024                 | Yes                                    | Yes                            |  |  |  |

#### **FEATURES**

- 8051 Central Processing Unit

- 128 × 8 RAM (80C31)

- 256 × 8 RAM (80C32)

- Three 16-bit counter/timers

- Boolean processor

- Full static operation

- Low voltage (2.7 V to 5.5 V@ 16 MHz) operation

- Memory addressing capability

- 64k ROM and 64k RAM

- Power control modes:

- Clock can be stopped and resumed

- Idle mode

- Power-down mode

- CMOS and TTL compatible

- TWO speed ranges at V<sub>CC</sub> = 5 V

- 0 to 16 MHz

- 0 to 33 MHz

- Three package styles

- Extended temperature ranges

- Dual Data Pointers

- 4 level priority interrupt

- 6 interrupt sources

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

- Programmable clock out

- Asynchronous port reset

- Low EMI (inhibit ALE)

- Wake-up from Power Down by an external interrupt

80C51 8-bit microcontroller family 128/256 byte RAM ROMless low voltage (2.7V–5.5V), low power, high speed (33 MHz)

80C31/80C32

# 80C51/87C51 AND 80C31 ORDERING INFORMATION

| ROMIess     | TEMPERATURE RANGE °C<br>AND PACKAGE      | VOLTAGE<br>RANGE | FREQ.<br>(MHz) | DRAWING<br>NUMBER |

|-------------|------------------------------------------|------------------|----------------|-------------------|

| P80C31SBPN  | 0 to +70, Plastic Dual In-line Package   | 2.7 V to 5.5 V   | 0 to 16        | SOT129-1          |

| P80C31SBAA  | 0 to +70, Plastic Leaded Chip Carrier    | 2.7 V to 5.5 V   | 0 to 16        | SOT187-2          |

| P80C31SBBB  | 0 to +70, Plastic Quad Flat Pack         | 2.7 V to 5.5 V   | 0 to 16        | SOT307-2          |

| P80C31SFPN  | -40 to +85, Plastic Dual In-line Package | 2.7 V to 5.5 V   | 0 to 16        | SOT129-1          |

| P80C31SFA A | -40 to +85, Plastic Leaded Chip Carrier  | 2.7 V to 5.5 V   | 0 to 16        | SOT187-2          |

| P80C31SFBB  | -40 to +85, Plastic Quad Flat Pack       | 2.7 V to 5.5 V   | 0 to 16        | SOT307-2          |

# PART NUMBER DERIVATION

| DEVICE NUMBER | OPERATING FREQUENCY, MAX (S) | TEMPERATURE RANGE (B)                | PACKAGE (AA) |

|---------------|------------------------------|--------------------------------------|--------------|

| P80C31        | S = 16 MHz                   | B = 0° to +70°C                      | AA = PLCC    |

| P80C32        | U = 33 MHz                   | $F = -40^{\circ}C$ to $+85^{\circ}C$ | BB = PQFP    |

|               |                              |                                      | PN = PDIP    |

# **80C32 ORDERING INFORMATION**

| ROMIess     | TEMPERATURE RANGE °C<br>AND PACKAGE      | FREQ<br>MHz | DRAWING<br>NUMBER |

|-------------|------------------------------------------|-------------|-------------------|

| P80C32SBP N | 0 to +70, Plastic Dual In-line Package   | 16          | SOT129-1          |

| P80C32SBA A | 0 to +70, Plastic Leaded Chip Carrier    | 16          | SOT187-2          |

| P80C32SBB B | 0 to +70, Plastic Quad Flat Pack         | 16          | SOT307-2          |

| P80C32SFP N | -40 to +85, Plastic Dual In-line Package | 16          | SOT129-1          |

| P80C32SFA A | -40 to +85, Plastic Leaded Chip Carrier  | 16          | SOT187-2          |

| P80C32SFB B | -40 to +85, Plastic Quad Flat Pack       | 16          | SOT307-2          |

| P80C32UBA A | 0 to +70, Plastic Leaded Chip Carrier    | 33          | SOT187-2          |

| P80C32UBP N | 0 to +70, Plastic Dual In-line Package   | 33          | SOT129-1          |

| P80C32UBB B | 0 to +70, Plastic Quad Flat Pack         | 33          | SOT307-2          |

| P80C32UFA A | -40 to +85, Plastic Leaded Chip Carrier  | 33          | SOT187-2          |

| P80C32UFP N | -40 to +85, Plastic Dual In-line Package | 33          | SOT129-1          |

| P80C32UFB B | -40 to +85, Plastic Quad Flat Pack       | 33          | SOT307-2          |

80C31/80C32

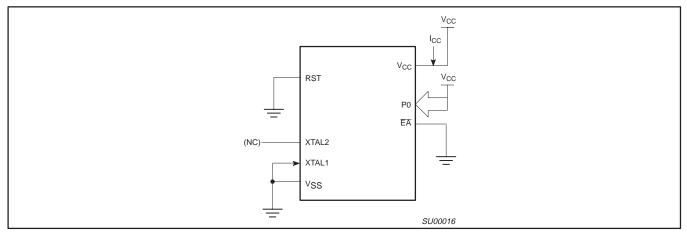

#### LOGIC SYMBOL

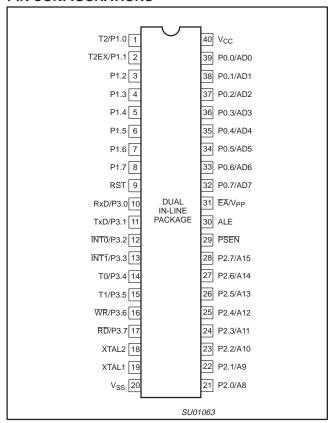

# **PIN CONFIGURATIONS**

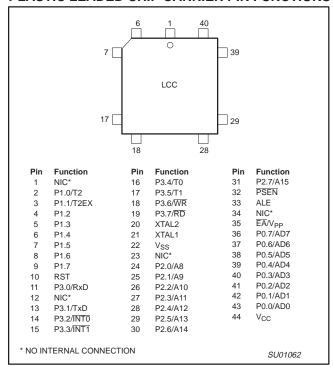

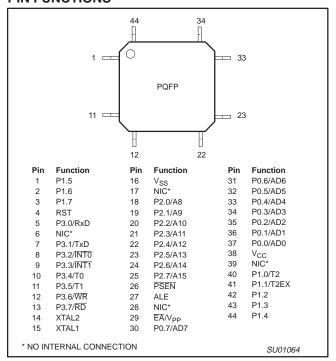

#### PLASTIC LEADED CHIP CARRIER PIN FUNCTIONS

# PLASTIC QUAD FLAT PACK PIN FUNCTIONS

80C31/80C32

Table 1. 8XC51/80C31 Special Function Registers

| SYMBOL   | DESCRIPTION             | DIRECT<br>ADDRESS | BIT<br>MSB | ADDRES   | S, SYMB  | OL, OR A | LTERNATI          | VE POR   | T FUNCT | ION<br>LSB | RESET<br>VALUE |

|----------|-------------------------|-------------------|------------|----------|----------|----------|-------------------|----------|---------|------------|----------------|

| ACC*     | Accumulator             | E0H               | E7         | E6       | E5       | E4       | E3                | E2       | E1      | E0         | 00H            |

| AUXR#    | Auxiliary               | 8EH               | -          | -        | T -      | - T      | T -               | _        | -       | AO         | xxxxxxx0B      |

| AUXR1#   | Auxiliary 1             | A2H               | _          | -        | -        | _        | WUPD <sup>2</sup> | 0        | -       | DPS        | xxx000x0B      |

| B*       | B register              | F0H               | F7         | F6       | F5       | F4       | F3                | F2       | F1      | F0         | 00H            |

| DPTR:    | Data Pointer (2 bytes)  |                   |            |          |          |          |                   |          |         |            |                |

| DPH      | Data Pointer High       | 83H               |            |          |          |          |                   |          |         |            | 00H            |

| DPL      | Data Pointer Low        | 82H               |            |          |          |          |                   |          |         |            | 00H            |

|          |                         |                   | AF         | AE       | AD       | AC       | AB                | AA       | A9      | A8         |                |

| IE*      | Interrupt Enable        | A8H               | EA         | -        | ET2      | ES       | ET1               | EX1      | ET0     | EX0        | 0x000000B      |

|          |                         |                   | BF         | BE       | BD       | ВС       | BB                | ВА       | B9      | B8         | 1              |

| IP*      | Interrupt Priority      | B8H               | _          | _        | PT2      | PS       | PT1               | PX1      | PT0     | PX0        | xx000000B      |

|          |                         |                   | B7         | B6       | B5       | B4       | В3                | B2       | B1      | B0         | 1              |

| IPH#     | Interrupt Priority High | B7H               | _          | _        | PT2H     | PSH      | PT1H              | PX1H     | PT0H    | PX0H       | xx000000B      |

|          | ' ' '                   |                   | 87         | 86       | 85       | 84       | 83                | 82       | 81      | 80         | 1              |

| P0*      | Port 0                  | 80H               | AD7        | AD6      | AD5      | AD4      | AD3               | AD2      | AD1     | AD0        | FFH            |

|          |                         |                   | 97         | 96       | 95       | 94       | 93                | 92       | 91      | 90         | 1              |

| P1*      | Port 1                  | 90H               |            | <u> </u> | <u> </u> | <u> </u> | 1 -               | <u> </u> | T2EX    | T2         | FFH            |

|          |                         |                   | A7         | A6       | A5       | A4       | A3                | A2       | A1      | A0         | 1              |

| P2*      | Port 2                  | A0H               | AD15       | AD14     | AD13     | AD12     | AD11              | AD10     | AD9     | AD8        | FFH            |

|          | 1 0112                  | 7.011             | B7         | B6       | B5       | B4       | B3                | B2       | B1      | B0         | 1              |

| P3*      | Port 3                  | ВОН               | RD         | WR       | T1       | T0       | INT1              | INTO     | TxD     | RxD        | FFH            |

| 10       | 1 011 0                 | 5011              | 100        | ***      |          | 10       | 11411             | 11410    | TAB     | TOOL       | ┨              |

| PCON#1   | Power Control           | 87H               | SMOD1      | SMOD0    | <u> </u> | POF      | GF1               | GF0      | PD      | IDL        | 00xx0000B      |

|          |                         |                   | D7         | D6       | D5       | D4       | D3                | D2       | D1      | D0         | 1              |

| PSW*     | Program Status Word     | D0H               | CY         | AC       | F0       | RS1      | RS0               | OV       | T -     | Р          | 000000x0B      |

| RACAP2H# | Timer 2 Capture High    | СВН               |            | - 110    |          |          |                   | -        |         |            | 00H            |

| RACAP2L# | Timer 2 Capture Low     | CAH               |            |          |          |          |                   |          |         |            | 00H            |

| SADDR#   | Slave Address           | A9H               |            |          |          |          |                   |          |         |            | 00H            |

| SADEN#   | Slave Address Mask      | В9Н               |            |          |          |          |                   |          |         |            | 00H            |

| SBUF     | Serial Data Buffer      | 99H               |            |          |          |          |                   |          |         |            | xxxxxxxxB      |

|          |                         |                   | 9F         | 9E       | 9D       | 9C       | 9B                | 9A       | 99      | 98         |                |

| SCON*    | Serial Control          | 98H               | SM0/FE     | SM1      | SM2      | REN      | TB8               | RB8      | TI      | RI         | 00Н            |

| SP       | Stack Pointer           | 81H               |            | <u> </u> | <u> </u> |          | <u>I</u>          |          | 1       |            | 07H            |

|          |                         |                   | 8F         | 8E       | 8D       | 8C       | 8B                | 8A       | 89      | 88         |                |

| TCON*    | Timer Control           | 88H               | TF1        | TR1      | TF0      | TR0      | IE1               | IT1      | IE0     | IT0        | 00H            |

|          |                         |                   | CF         | CE       | CD       | CC       | СВ                | CA       | C9      | C8         | 1              |

| T2CON*   | Timer 2 Control         | C8H               | TF2        | EXF2     | RCLK     | TCLK     | EXEN2             | TR2      | C/T2    | CP/RL2     | 00H            |

| T2MOD#   | Timer 2 Mode Control    | C9H               |            | _        | -        | -        | -                 | -        | T2OE    | DCEN       | xxxxxx00B      |

| TH0      | Timer High 0            | 8CH               |            |          |          |          |                   |          |         | DOLIV      | 00H            |

| TH1      | Timer High 1            | 8DH               |            |          |          |          |                   |          |         |            | 00H            |

| TH2#     | Timer High 2            | CDH               |            |          |          |          |                   |          |         |            | 00H            |

| TL0      | Timer Low 0             | 8AH               | 1          |          |          |          |                   |          |         |            | 00H            |

| TL1      | Timer Low 1             | 8BH               |            |          |          |          |                   |          |         |            | 00H            |

| TL2#     | Timer Low 2             | CCH               | <u> </u>   |          |          |          |                   |          |         |            | 00H            |

| TMOD     | Timer Mode              | 89H               | GATE       | C/T      | M1       | M0       | GATE              | C/T      | M1      | M0         | 00H            |

# NOTE:

Unused register bits that are not defined should not be set by the user's program. If violated, the device could function incorrectly.

\* SFRs are bit addressable.

- # SFRs are modified from or added to the 80C51 SFRs.

- Reserved bits.

- 1. Reset value depends on reset source.

- 2. Not available on 80C31.

7 2000 Aug 07

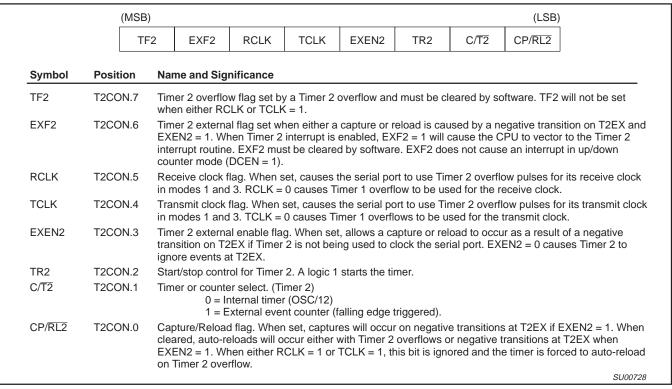

Figure 1. Timer/Counter 2 (T2CON) Control Register

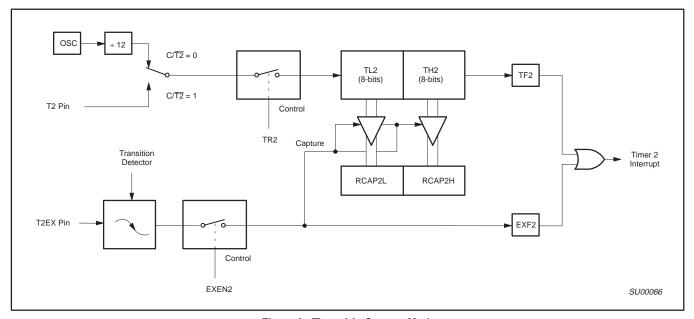

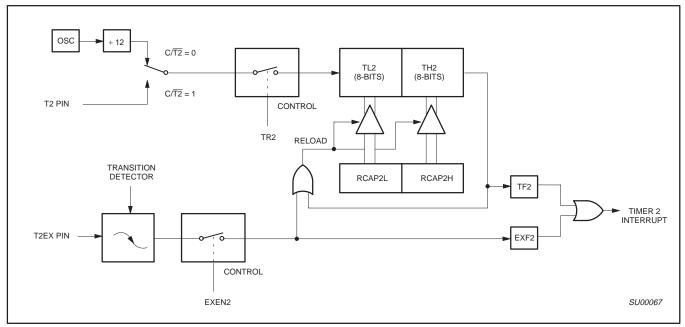

Figure 2. Timer 2 in Capture Mode

80C31/80C32

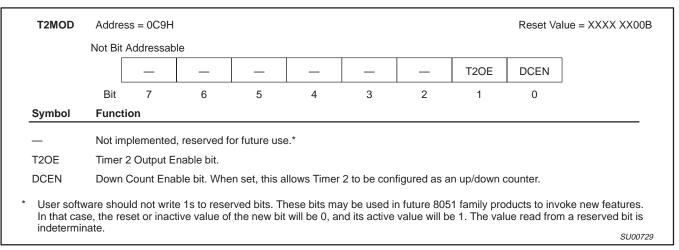

Figure 3. Timer 2 Mode (T2MOD) Control Register

Figure 4. Timer 2 in Auto-Reload Mode (DCEN = 0)

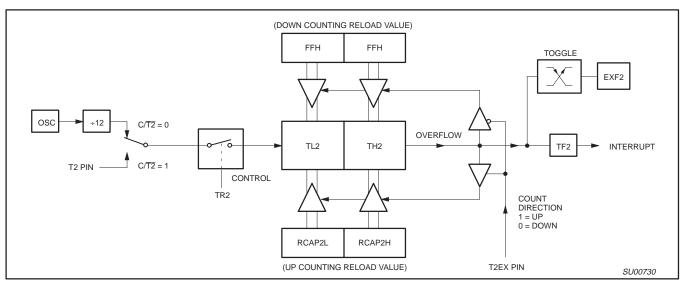

Figure 5. Timer 2 Auto Reload Mode (DCEN = 1)

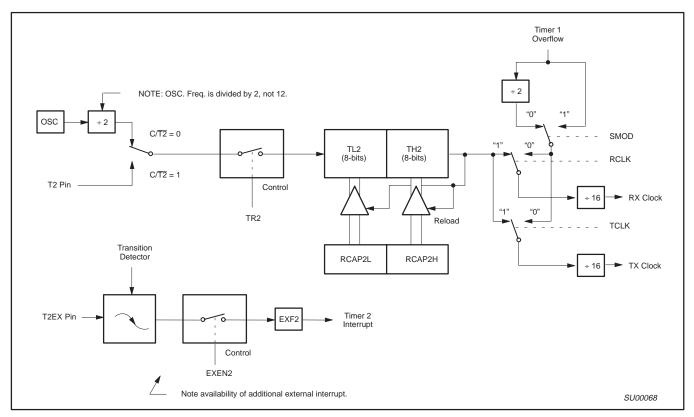

Figure 6. Timer 2 in Baud Rate Generator Mode

80C31/80C32

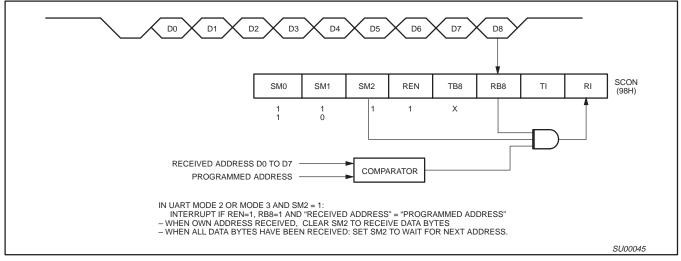

and 1 and exclude Slave 2 use address 1110 0100, since it is necessary to make bit 2 = 1 to exclude slave 2.

The Broadcast Address for each slave is created by taking the logical OR of SADDR and SADEN. Zeros in this result are trended as don't-cares. In most cases, interpreting the don't-cares as ones, the broadcast address will be FF hexadecimal.

Upon reset SADDR (SFR address 0A9H) and SADEN (SFR address 0B9H) are leaded with 0s. This produces a given address of all "don't cares" as well as a Broadcast address of all "don't cares". This effectively disables the Automatic Addressing mode and allows the microcontroller to use standard 80C51 type UART drivers which do not make use of this feature.

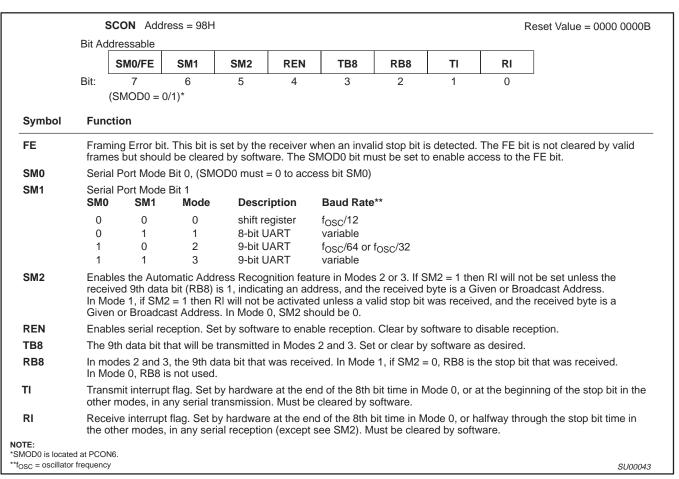

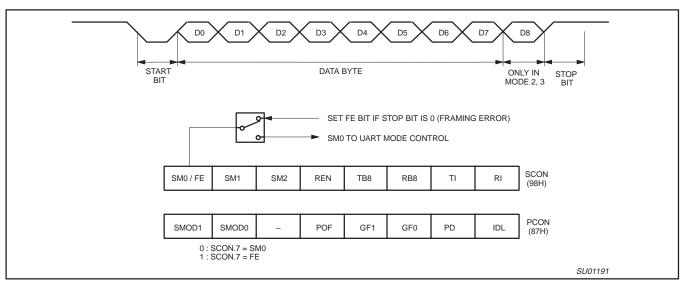

Figure 7. SCON: Serial Port Control Register

Figure 8. UART Framing Error Detection

Figure 9. UART Multiprocessor Communication, Automatic Address Recognition

80C31/80C32

# **Interrupt Priority Structure**

The 80C31 and 80C32 have a 6-source four-level interrupt structure. They are the IE, IP and IPH. (See Figures 10, 11, and 12.) The IPH (Interrupt Priority High) register that makes the four-level interrupt structure possible. The IPH is located at SFR address B7H. The structure of the IPH register and a description of its bits is shown in Figure 12.

The function of the IPH SFR is simple and when combined with the IP SFR determines the priority of each interrupt. The priority of each interrupt is determined as shown in the following table:

| PRIORI | TY BITS | INTERRUPT PRIORITY LEVEL   |

|--------|---------|----------------------------|

| IPH.x  | IP.x    | INTERROPT PRIORITI LEVEL   |

| 0      | 0       | Level 0 (lowest priority)  |

| 0      | 1       | Level 1                    |

| 1      | 0       | Level 2                    |

| 1      | 1       | Level 3 (highest priority) |

An interrupt will be serviced as long as an interrupt of equal or higher priority is not already being serviced. If an interrupt of equal or higher level priority is being serviced, the new interrupt will wait until it is finished before being serviced. If a lower priority level interrupt is being serviced, it will be stopped and the new interrupt serviced. When the new interrupt is finished, the lower priority level interrupt that was stopped will be completed.

Table 7. Interrupt Table

|        |                  | _            |                                       |                |

|--------|------------------|--------------|---------------------------------------|----------------|

| SOURCE | POLLING PRIORITY | REQUEST BITS | HARDWARE CLEAR?                       | VECTOR ADDRESS |

| X0     | 1                | IE0          | N (L) <sup>1</sup> Y (T) <sup>2</sup> | 03H            |

| T0     | 2                | TP0          | Υ                                     | 0BH            |

| X1     | 3                | IE1          | N (L) Y (T)                           | 13H            |

| T1     | 4                | TF1          | Υ                                     | 1BH            |

| SP     | 5                | RI, TI       | N                                     | 23H            |

| T2     | 6                | TF2, EXF2    | N                                     | 2BH            |

#### NOTES:

- 1. L = Level activated

- 2. T = Transition activated

|      |           | 7      | 6                         | 5                        | 4           | 3                     | 2   | 1   | 0         |

|------|-----------|--------|---------------------------|--------------------------|-------------|-----------------------|-----|-----|-----------|

|      | IE (0A8H) | EA     | _                         | ET2                      | ES          | ET1                   | EX1 | ET0 | EX0       |

|      |           |        | Bit = 1 en<br>Bit = 0 dis | ables the i<br>ables it. | nterrupt.   |                       |     |     |           |

| BIT  | SYMBOL    | FUNC   | TION                      |                          |             |                       |     |     |           |

| IE.7 | EA        |        |                           |                          |             | rrupts are earing its |     |     | each inte |

| IE.6 | _         | Not im | plemente                  | d. Reserv                | ed for futu | ıre use.              |     |     |           |

| IE.5 | ET2       | Timer  | 2 interrup                | t enable b               | it.         |                       |     |     |           |

| IE.4 | ES        | Serial | Port inter                | upt enabl                | e bit.      |                       |     |     |           |

| IE.3 | ET1       | Timer  | 1 interrup                | t enable b               | it.         |                       |     |     |           |

| IE.2 | EX1       | Extern | al interru                | ot 1 enable              | e bit.      |                       |     |     |           |

| IE.1 | ET0       | Timer  | 0 interrup                | t enable b               | it.         |                       |     |     |           |

| IE.0 | EX0       | Extern | al interru                | ot 0 enable              | e bit.      |                       |     |     |           |

Figure 10. IE Registers

80C51 8-bit microcontroller family 128/256 byte RAM ROMless low voltage (2.7V–5.5V), low power, high speed (33 MHz)

80C31/80C32

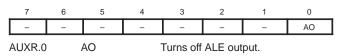

#### **Reduced EMI Mode**

The AO bit (AUXR.0) in the AUXR register when set disables the ALE output.

# **Reduced EMI Mode**

# AUXR (8EH)

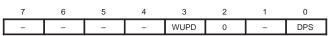

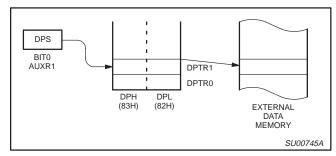

# **Dual DPTR**

The dual DPTR structure (see Figure 13) enables a way to specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1/bit0 that allows the program code to switch between them.

New Register Name: AUXR1#

SFR Address: A2H

Reset Value: xxx000x0B

# AUXR1 (A2H)

Where:

$\label{eq:decomposition} \text{DPS} = \text{AUXR1/bit0} = \text{Switches between DPTR0} \text{ and DPTR1}.$

| Select Reg | DPS |

|------------|-----|

| DPTR0      | 0   |

| DPTR1      | 1   |

The DPS bit status should be saved by software when switching between DPTR0 and DPTR1.

Note that bit 2 is not writable and is always read as a zero. This allows the DPS bit to be quickly toggled simply by executing an INC DPTR instruction without affecting the WOPD or LPEP bits.

Figure 13.

#### **DPTR Instructions**

The instructions that refer to DPTR refer to the data pointer that is currently selected using the AUXR1/bit 0 register. The six instructions that use the DPTR are as follows:

| INC DPTR          | Increments the data pointer by 1          |

|-------------------|-------------------------------------------|

| MOV DPTR, #data16 | Loads the DPTR with a 16-bit constant     |

| MOV A, @ A+DPTR   | Move code byte relative to DPTR to ACC    |

| MOVX A, @ DPTR    | Move external RAM (16-bit address) to ACC |

| MOVX @ DPTR , A   | Move ACC to external RAM (16-bit address) |

| JMP @ A + DPTR    | Jump indirect relative to DPTR            |

The data pointer can be accessed on a byte-by-byte basis by specifying the low or high byte in an instruction which accesses the SFRs. See application note AN458 for more details.

80C31/80C32

#### DC ELECTRICAL CHARACTERISTICS

$T_{amb} = 0^{\circ}C$  to +70°C or -40°C to +85°C,  $V_{CC} = 2.7$  V to 5.5 V,  $V_{SS} = 0$  V (16 MHz devices)

|                               |                                                                                                                                               | TEST                                                                                                                    |                          | LIMITS           |                          |                      |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|--------------------------|----------------------|

| SYMBOL                        | PARAMETER                                                                                                                                     | CONDITIONS                                                                                                              | MIN                      | TYP <sup>1</sup> | MAX                      | UNIT                 |

| M                             | lanut laurus liana                                                                                                                            | 4.0 V < V <sub>CC</sub> < 5.5 V                                                                                         | -0.5                     |                  | 0.2 V <sub>CC</sub> -0.1 | V                    |

| $V_{IL}$                      | Input low voltage                                                                                                                             | 2.7 V <v<sub>CC&lt; 4.0 V</v<sub>                                                                                       | -0.5                     |                  | 0.7                      | V                    |

| V <sub>IH</sub>               | Input high voltage (ports 0, 1, 2, 3, EA)                                                                                                     |                                                                                                                         | 0.2 V <sub>CC</sub> +0.9 |                  | V <sub>CC</sub> +0.5     | V                    |

| V <sub>IH1</sub>              | Input high voltage, XTAL1, RST                                                                                                                |                                                                                                                         | 0.7 V <sub>CC</sub>      |                  | V <sub>CC</sub> +0.5     | V                    |

| V <sub>OL</sub>               | Output low voltage, ports 1, 2, 8                                                                                                             | $V_{CC} = 2.7 \text{ V}$ $I_{OL} = 1.6 \text{ mA}^2$                                                                    |                          |                  | 0.4                      | V                    |

| V <sub>OL1</sub>              | Output low voltage, port 0, ALE, PSEN <sup>8, 7</sup>                                                                                         | $V_{CC} = 2.7 \text{ V}$ $I_{OL} = 3.2 \text{ mA}^2$                                                                    |                          |                  | 0.4                      | ٧                    |

|                               | Output high purposes 4 0 0 3                                                                                                                  | V <sub>CC</sub> = 2.7 V<br>I <sub>OH</sub> = -20 μA                                                                     | V <sub>CC</sub> - 0.7    |                  |                          | V                    |

| V <sub>OH</sub> Output high v | Output high voltage, ports 1, 2, 3 <sup>3</sup>                                                                                               | V <sub>CC</sub> = 4.5 V<br>I <sub>OH</sub> = -30 μA                                                                     | V <sub>CC</sub> - 0.7    |                  |                          | V                    |

| V <sub>OH1</sub>              | Output high voltage (port 0 in external bus mode), ALE <sup>9</sup> , PSEN <sup>3</sup>                                                       | $V_{CC} = 2.7 \text{ V}$ $I_{OH} = -3.2 \text{ mA}$                                                                     | V <sub>CC</sub> - 0.7    |                  |                          | V                    |

| I <sub>IL</sub>               | Logical 0 input current, ports 1, 2, 3                                                                                                        | V <sub>IN</sub> = 0.4 V                                                                                                 | -1                       |                  | -50                      | μΑ                   |

| I <sub>TL</sub>               | Logical 1-to-0 transition current, ports 1, 2, 3 <sup>6</sup>                                                                                 | V <sub>IN</sub> = 2.0 V<br>See note 4                                                                                   |                          |                  | -650                     | μА                   |

| ILI                           | Input leakage current, port 0                                                                                                                 | $0.45 < V_{IN} < V_{CC} - 0.3$                                                                                          |                          |                  | ±10                      | μΑ                   |

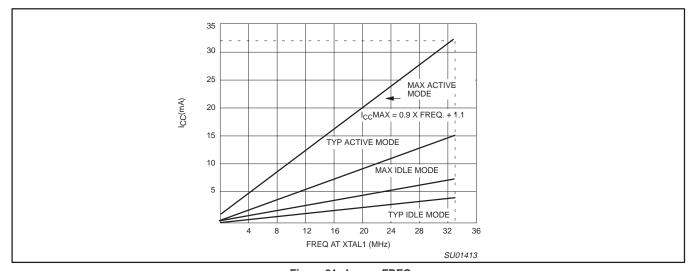

| Icc                           | Power supply current (see Figure 21): Active mode @ 16 MHz Idle mode @ 16 MHz Power-down mode or clock stopped (see Figure 25 for conditions) | See note 5 $T_{amb} = 0^{\circ}\text{C to } 70^{\circ}\text{C}$ $T_{amb} = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                          | 3                | 50<br>75                 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| R <sub>RST</sub>              | Internal reset pull-down resistor                                                                                                             |                                                                                                                         | 40                       |                  | 225                      | kΩ                   |

| C <sub>IO</sub>               | Pin capacitance <sup>10</sup> (except EA)                                                                                                     |                                                                                                                         |                          |                  | 15                       | pF                   |

# NOTES:

- 1. Typical ratings are not guaranteed. The values listed are at room temperature, 5 V.

- Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the Vols of ALE and ports 1 and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE pin may exceed 0.8 V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. IoL can exceed these conditions provided that no single output sinks more than 5 mA and no more than two outputs exceed the test conditions

- 3. Capacitive loading on ports 0 and 2 may cause the  $V_{OH}$  on ALE and  $\overline{PSEN}$  to momentarily fall below the  $V_{CC}$ -0.7 specification when the address bits are stabilizing.

- Pins of ports 1, 2 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2 V.

- See Figures 22 through 25 for I<sub>CC</sub> test conditions.

$I_{CC} = 0.9 \times FREQ. + 1.1 \text{ mA}$

- Idle mode:  $I_{CC} = 0.18 \times FREQ. +1.01$  mA; See Figure 21. 6. This value applies to  $T_{amb} = 0^{\circ}C$  to  $+70^{\circ}C$ . For  $T_{amb} = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $I_{TL} = -750$   $\mu$ A.

- Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

- 8. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 15 mA (\*NOTE: This is 85°C specification.)

Maximum I<sub>OL</sub> per 8-bit port: 26 mA

Maximum total I<sub>OL</sub> for all outputs: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 9. ALE is tested to V<sub>OH1</sub>, except when ALE is off then V<sub>OH</sub> is the voltage specification.

- 10. Pin capacitance is characterized but not tested. Pin capacitance is less than 25 pF.

2000 Aug 07

80C31/80C32

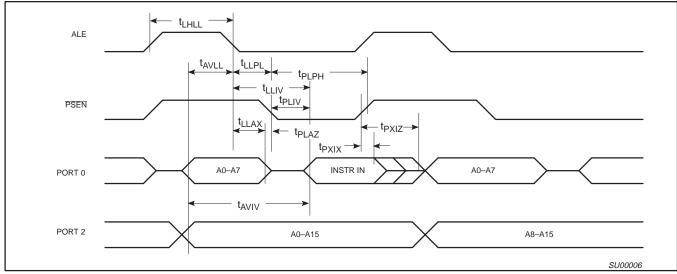

# **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0$ °C to +70°C or -40°C to +85°C,  $V_{CC} = +2.7$  V to +5.5 V,  $V_{SS} = 0$  V<sup>1, 2, 3</sup>

|                                |                            |                                                     | 16 MHz | CLOCK | VARIABL                  | 1                                    |      |

|--------------------------------|----------------------------|-----------------------------------------------------|--------|-------|--------------------------|--------------------------------------|------|

| SYMBOL                         | FIGURE                     | PARAMETER                                           | MIN    | MAX   | MIN                      | MAX                                  | UNIT |

| 1/t <sub>CLCL</sub>            | 14                         | Oscillator frequency <sup>5</sup> Speed versions :S |        |       | 3.5                      | 16                                   | MHz  |

| LHLL                           | 14                         | ALE pulse width                                     | 85     |       | 2t <sub>CLCL</sub> -40   |                                      | ns   |

| t <sub>AVLL</sub>              | 14                         | Address valid to ALE low                            | 22     |       | t <sub>CLCL</sub> -40    |                                      | ns   |

| t <sub>LLAX</sub>              | 14                         | Address hold after ALE low                          | 32     |       | t <sub>CLCL</sub> -30    |                                      | ns   |

| t <sub>LLIV</sub>              | 14                         | ALE low to valid instruction in                     |        | 150   |                          | 4t <sub>CLCL</sub> -100              | ns   |

| t <sub>LLPL</sub>              | 14                         | ALE low to PSEN low                                 | 32     |       | t <sub>CLCL</sub> -30    |                                      | ns   |

| t <sub>PLPH</sub>              | 14                         | PSEN pulse width                                    | 142    |       | 3t <sub>CLCL</sub> -45   |                                      | ns   |

| t <sub>PLIV</sub>              | 14                         | PSEN low to valid instruction in                    |        | 82    |                          | 3t <sub>CLCL</sub> -105              | ns   |

| t <sub>PXIX</sub>              | 14                         | Input instruction hold after PSEN                   | 0      |       | 0                        |                                      | ns   |

| t <sub>PXIZ</sub>              | 14                         | Input instruction float after PSEN                  |        | 37    |                          | t <sub>CLCL</sub> -25                | ns   |

| t <sub>AVIV</sub> <sup>4</sup> | 14                         | Address to valid instruction in                     |        | 207   |                          | 5t <sub>CLCL</sub> -105              | ns   |

| t <sub>PLAZ</sub>              | 14                         | PSEN low to address float                           |        | 10    |                          | 10                                   | ns   |

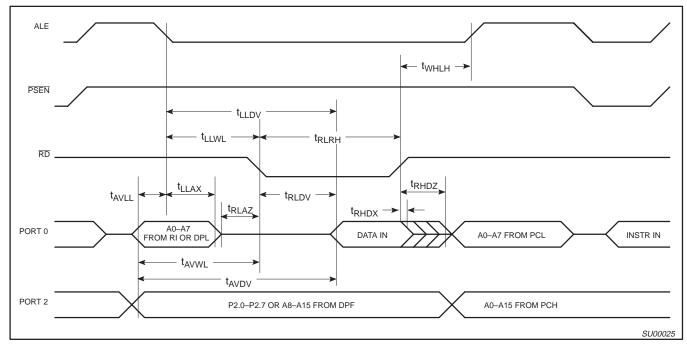

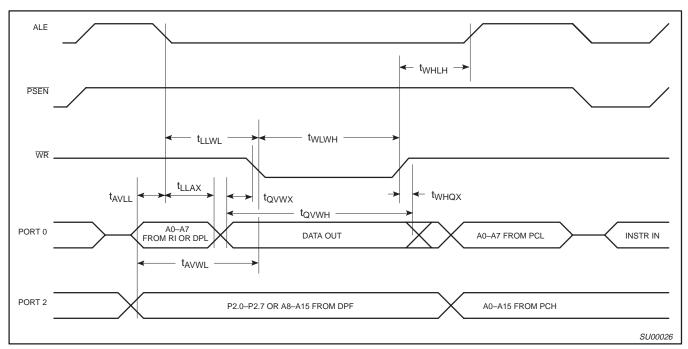

| Data Memo                      | ory                        |                                                     |        |       | •                        | •                                    |      |

| t <sub>RLRH</sub>              | 15, 16                     | RD pulse width                                      | 275    |       | 6t <sub>CLCL</sub> -100  |                                      | ns   |

| twlwh                          | 15, 16                     | WR pulse width                                      | 275    |       | 6t <sub>CLCL</sub> -100  |                                      | ns   |

| RLDV                           | 15, 16                     | RD low to valid data in                             |        | 147   |                          | 5t <sub>CLCL</sub> -165              | ns   |

| RHDX                           | 15, 16 Data hold after RD  |                                                     | 0      |       | 0                        |                                      | ns   |

| t <sub>RHDZ</sub>              | 15, 16 Data float after RD |                                                     |        | 65    |                          | 2t <sub>CLCL</sub> -60               | ns   |

| tLLDV                          | 15, 16                     | ALE low to valid data in                            |        | 350   |                          | 8t <sub>CLCL</sub> -150              | ns   |

| t <sub>AVDV</sub>              | 15, 16                     | Address to valid data in                            |        | 397   |                          | 9t <sub>CLCL</sub> -165              | ns   |

| t <sub>LLWL</sub>              | 15, 16                     | ALE low to RD or WR low                             | 137    | 239   | 3t <sub>CLCL</sub> -50   | 3t <sub>CLCL</sub> +50               | ns   |

| t <sub>AVWL</sub>              | 15, 16                     | Address valid to WR low or RD low                   | 122    |       | 4t <sub>CLCL</sub> -130  |                                      | ns   |

| t <sub>QVWX</sub>              | 15, 16                     | Data valid to WR transition                         | 13     |       | t <sub>CLCL</sub> -50    |                                      | ns   |

| t <sub>WHQX</sub>              | 15, 16                     | Data hold after WR                                  | 13     |       | t <sub>CLCL</sub> -50    |                                      | ns   |

| t <sub>QVWH</sub>              | 16                         | Data valid to WR high                               | 287    |       | 7t <sub>CLCL</sub> -150  |                                      | ns   |

| t <sub>RLAZ</sub>              | 15, 16                     | RD low to address float                             |        | 0     |                          | 0                                    | ns   |

| twhlh                          | 15, 16                     | RD or WR high to ALE high                           | 23     | 103   | t <sub>CLCL</sub> -40    | t <sub>CLCL</sub> +40                | ns   |

| External C                     | lock                       |                                                     | _      |       |                          |                                      | •    |

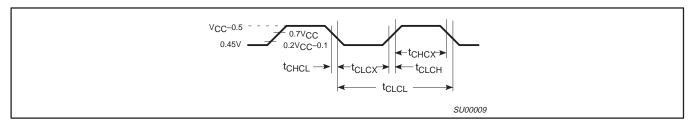

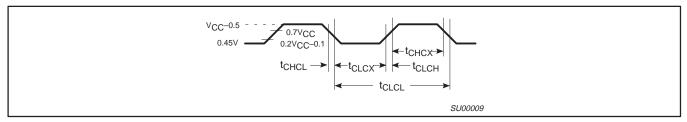

| t <sub>CHCX</sub>              | 18                         | High time                                           | 20     | 1     | 20                       | t <sub>CLCL</sub> -t <sub>CLCX</sub> | ns   |

| t <sub>CLCX</sub>              | 18                         | Low time                                            | 20     |       | 20                       | t <sub>CLCL</sub> -t <sub>CHCX</sub> | ns   |

| t <sub>CLCH</sub>              | 18                         | Rise time                                           |        | 20    |                          | 20                                   | ns   |

| tchcl                          | 18                         | Fall time                                           |        | 20    |                          | 20                                   | ns   |

| Shift Regis                    | ter                        | •                                                   |        |       | •                        | •                                    |      |

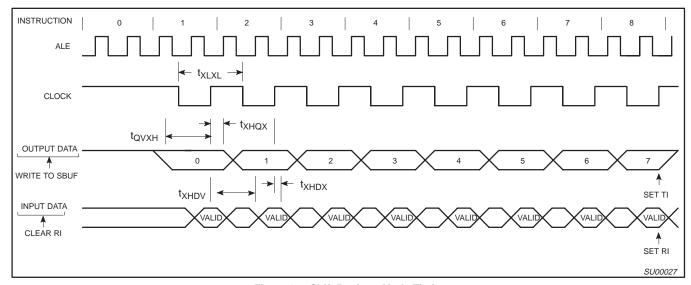

| t <sub>XLXL</sub>              | 17                         | Serial port clock cycle time                        | 750    |       | 12t <sub>CLCL</sub>      |                                      | ns   |

| t <sub>QVXH</sub>              | 17                         | Output data setup to clock rising edge              | 492    | 1     | 10t <sub>CLCL</sub> -133 |                                      | ns   |

| t <sub>XHQX</sub>              | 17                         | Output data hold after clock rising edge            | 8      |       | 2t <sub>CLCL</sub> -117  |                                      | ns   |

| t <sub>XHDX</sub>              |                            |                                                     | 0      |       | 0                        |                                      | ns   |

| t <sub>XHDV</sub>              | 17                         | Clock rising edge to input data valid               | +      | 492   | 1                        | 10t <sub>CLCL</sub> -133             | ns   |

- Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

- 3. Interfacing the 80C31 and 80C32 to devices with float times up to 45ns is permitted. This limited bus contention will not cause damage to Port 0 drivers.

- 4. See application note AN457 for external memory interface.

- 5. Parts are guaranteed to operate down to 0 Hz. When an external clock source is used, the RST pin should be held high for a minimum of 20 µs for power-on or wakeup from power down.

2000 Aug 07 23

80C31/80C32

# **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0^{\circ}C$  to +70°C or -40°C to +85°C,  $V_{CC} = 5 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}^{1, 2, 3}$

|                   |        |                                          |                                                    | E CLOCK <sup>4</sup>                 |              |     |      |

|-------------------|--------|------------------------------------------|----------------------------------------------------|--------------------------------------|--------------|-----|------|

|                   |        |                                          | 16 MHz                                             | 33 MHz                               | ╛            |     |      |

| SYMBOL            | FIGURE | PARAMETER                                | MIN                                                | MAX                                  | MIN          | MAX | UNIT |

| t <sub>LHLL</sub> | 14     | ALE pulse width                          | 2t <sub>CLCL</sub> -40                             |                                      | 21           |     | ns   |

| t <sub>AVLL</sub> | 14     | Address valid to ALE low                 | t <sub>CLCL</sub> -25                              |                                      | 5            |     | ns   |

| t <sub>LLAX</sub> | 14     | Address hold after ALE low               | t <sub>CLCL</sub> -25                              |                                      |              |     | ns   |

| t <sub>LLIV</sub> | 14     | ALE low to valid instruction in          |                                                    | 4t <sub>CLCL</sub> -65               |              | 55  | ns   |

| t <sub>LLPL</sub> | 14     | ALE low to PSEN low                      | t <sub>CLCL</sub> -25                              |                                      | 5            |     | ns   |

| t <sub>PLPH</sub> | 14     | PSEN pulse width                         | 3t <sub>CLCL</sub> -45                             |                                      | 45           |     | ns   |

| t <sub>PLIV</sub> | 14     | PSEN low to valid instruction in         |                                                    | 3t <sub>CLCL</sub> -60               |              | 30  | ns   |

| t <sub>PXIX</sub> | 14     | Input instruction hold after PSEN        | 0                                                  |                                      | 0            |     | ns   |

| t <sub>PXIZ</sub> | 14     | Input instruction float after PSEN       |                                                    | t <sub>CLCL</sub> -25                |              | 5   | ns   |

| t <sub>AVIV</sub> | 14     | Address to valid instruction in          |                                                    | 5t <sub>CLCL</sub> -80               |              | 70  | ns   |

| t <sub>PLAZ</sub> | 14     | PSEN low to address float                |                                                    | 10                                   |              | 10  | ns   |

| Data Memo         | ry     | •                                        | •                                                  |                                      | •            |     |      |

| t <sub>RLRH</sub> | 15, 16 | RD pulse width                           | 6t <sub>CLCL</sub> -100                            |                                      | 82           |     | ns   |

| t <sub>WLWH</sub> | 15, 16 | WR pulse width                           | 6t <sub>CLCL</sub> -100                            |                                      | 82           |     | ns   |

| t <sub>RLDV</sub> | 15, 16 | RD low to valid data in                  |                                                    | 5t <sub>CLCL</sub> -90               |              | 60  | ns   |

| t <sub>RHDX</sub> | 15, 16 | Data hold after RD                       | 0                                                  |                                      | 0            |     | ns   |

| t <sub>RHDZ</sub> | 15, 16 | Data float after RD                      |                                                    | 2t <sub>CLCL</sub> -28               |              | 32  | ns   |

| t <sub>LLDV</sub> | 15, 16 | ALE low to valid data in                 |                                                    | 8t <sub>CLCL</sub> -150              |              | 90  | ns   |

| t <sub>AVDV</sub> | 15, 16 | Address to valid data in                 |                                                    | 9t <sub>CLCL</sub> -165              |              | 105 | ns   |

| t <sub>LLWL</sub> | 15, 16 | ALE low to RD or WR low                  | 3t <sub>CLCL</sub> -50                             | 3t <sub>CLCL</sub> +50               | 40           | 140 | ns   |

| t <sub>AVWL</sub> | 15, 16 | Address valid to WR low or RD low        | 4t <sub>CLCL</sub> -75                             |                                      | 45           |     | ns   |

| t <sub>QVWX</sub> | 15, 16 | Data valid to WR transition              | t <sub>CLCL</sub> -30                              |                                      | 0            |     | ns   |

| t <sub>WHQX</sub> | 15, 16 | Data hold after WR                       | t <sub>CLCL</sub> -25                              |                                      | 5            |     | ns   |

| t <sub>QVWH</sub> | 16     | Data valid to WR high                    | 7t <sub>CLCL</sub> -130                            |                                      | 80           |     | ns   |

| t <sub>RLAZ</sub> | 15, 16 | RD low to address float                  | 0202                                               | 0                                    |              | 0   | ns   |

| twhlh             | 15, 16 | RD or WR high to ALE high                | t <sub>CLCL</sub> -25                              | t <sub>CLCL</sub> +25                | 5            | 55  | ns   |

| External Clo      | ock    |                                          | 0202                                               | 0101                                 |              |     |      |

| t <sub>CHCX</sub> | 18     | High time                                | 0.38t <sub>CLCL</sub>                              | t <sub>CLCL</sub> -t <sub>CLCX</sub> |              |     | ns   |

| tclcx             | 18     | Low time                                 | 0.38t <sub>CLCL</sub>                              | t <sub>CLCL</sub> -t <sub>CHCX</sub> |              |     | ns   |

| tclch             | 18     | Rise time                                | - 0202                                             | 5                                    |              |     | ns   |

| tCHCL             | 18     | Fall time                                |                                                    | 5                                    |              |     | ns   |

| Shift Regist      |        | 1                                        | -                                                  | -                                    |              |     |      |

| t <sub>XLXL</sub> | 17     | Serial port clock cycle time             | 12t <sub>CLCL</sub>                                |                                      | 360          |     | ns   |

| t <sub>QVXH</sub> | 17     | Output data setup to clock rising edge   | 10t <sub>CLCL</sub> -133                           |                                      | 167          |     | ns   |

| t <sub>XHQX</sub> | 17     | Output data hold after clock rising edge | 2t <sub>CLCL</sub> -80                             |                                      | 1            |     | ns   |

| t <sub>XHDX</sub> | 17     | Input data hold after clock rising edge  | 0                                                  |                                      | 0            |     | ns   |

| -VUDV             | 17     | Clock rising edge to input data valid    | <del>                                       </del> | 10t <sub>CLCL</sub> -133             | <del>L</del> | 167 | ns   |

# NOTES:

- 1. Parameters are valid over operating temperature range unless otherwise specified.

- 2. Load capacitance for port 0, ALE, and  $\overline{PSEN} = 100 \, pF$ , load capacitance for all other outputs = 80 pF.

- 3. Interfacing the 80C31 and 80C32 to devices with float times up to 45ns is permitted. This limited bus contention will not cause damage to Port 0 drivers.

- 4. Variable clock is specified for oscillator frequencies greater than 16 MHz to 33 MHz. For frequencies equal or less than 16 MHz, see 16 MHz "AC Electrical Characteristics", page 23.

- 5. Parts are guaranteed to operate down to 0 Hz. When an external clock source is used, the RST pin should be held high for a minimum of 20 μs for power-on or wakeup from power down.

80C31/80C32

## **EXPLANATION OF THE AC SYMBOLS**

Each timing symbol has five characters. The first character is always 't' (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designations are:

A - Address

C - Clock

D - Input data

H - Logic level high

I – Instruction (program memory contents)

L - Logic level low, or ALE

P - PSEN

Q - Output data

$R - \overline{RD}$  signal

t - Time

V - Valid

W- WR signal

X - No longer a valid logic level

Z - Float

**Examples:** t<sub>AVLL</sub> = Time for address valid to ALE low.

$t_{LLPL}$  =Time for ALE low to  $\overline{PSEN}$  low.

Figure 14. External Program Memory Read Cycle

Figure 15. External Data Memory Read Cycle

Figure 16. External Data Memory Write Cycle

Figure 17. Shift Register Mode Timing

Figure 18. External Clock Drive

80C51 8-bit microcontroller family 128/256 byte RAM ROMless low voltage (2.7V–5.5V), low power, high speed (33 MHz)

80C31/80C32

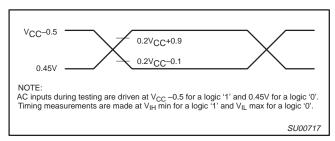

Figure 19. AC Testing Input/Output

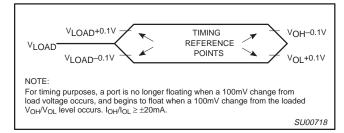

Figure 20. Float Waveform

$\label{eq:continuous} \mbox{Figure 21. I}_{\mbox{CC}} \mbox{ vs. FREQ} \\ \mbox{Valid only within frequency specifications of the device under test}$

80C51 8-bit microcontroller family 128/256 byte RAM ROMless low voltage (2.7V–5.5V), low power, high speed (33 MHz)

80C31/80C32

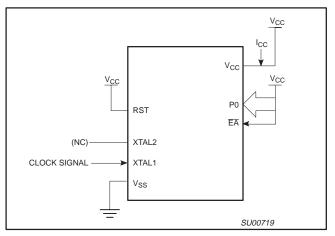

Figure 22. I<sub>CC</sub> Test Condition, Active Mode All other pins are disconnected

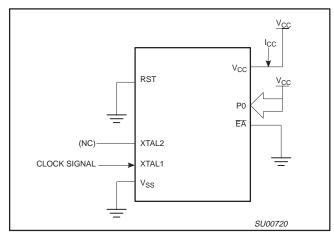

Figure 23. I<sub>CC</sub> Test Condition, Idle Mode All other pins are disconnected

Figure 24. Clock Signal Waveform for  $I_{CC}$  Tests in Active and Idle Modes  $t_{CLCH} = t_{CHCL} = 5 ns$

Figure 25.  $I_{CC}$  Test Condition, Power Down Mode All other pins are disconnected.  $V_{CC}$  = 2 V to 5.5 V

80C31/80C32

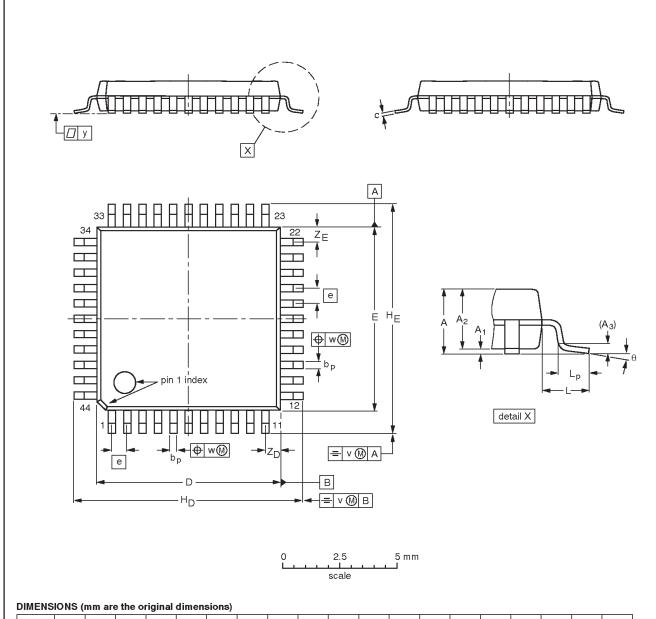

# QFP44: plastic quad flat package; 44 leads (lead length 1.3 mm); body 10 x 10 x 1.75 mm

SOT307-2

| UNIT | A<br>max. | Α1           | A <sub>2</sub> | A <sub>3</sub> | Ьp           | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е   | H <sub>D</sub> | HE           | L   | Lp           | v    | w    | у   | Z <sub>D</sub> <sup>(1)</sup> | Z <sub>E</sub> <sup>(1)</sup> | θ         |

|------|-----------|--------------|----------------|----------------|--------------|--------------|------------------|------------------|-----|----------------|--------------|-----|--------------|------|------|-----|-------------------------------|-------------------------------|-----------|

| mm   | 2.10      | 0.25<br>0.05 | 1.85<br>1.65   | 0.25           | 0.40<br>0.20 | 0.25<br>0.14 | 10.1<br>9.9      | 10.1<br>9.9      | 0.8 | 12.9<br>12.3   | 12.9<br>12.3 | 1.3 | 0.95<br>0.55 | 0.15 | 0.15 | 0.1 | 1.2<br>0.8                    | 1.2<br>0.8                    | 10°<br>0° |

# Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  | REFERENCES |       | EUROPEAN | ISSUE DATE |                                  |

|----------|------------|-------|----------|------------|----------------------------------|

| VERSION  | IEC        | JEDEC | EIAJ     | PROJECTION | ISSUE DATE                       |

| SOT307-2 |            |       |          |            | <del>-95-02-04</del><br>97-08-01 |

80C51 8-bit microcontroller family 128/256 byte RAM ROMless low voltage (2.7V–5.5V), low power, high speed (33 MHz)

80C31/80C32

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                             |

|---------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                          |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 2000 All rights reserved. Printed in U.S.A.

Date of release: 08-00

Document order number: 9397 750 07403

Let's make things better.

Philips Semiconductors