#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                               |

| Core Processor             | CIP-51 8051                                                            |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 72MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 20                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.25K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                            |

| Data Converters            | A/D 12x14b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 24-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 24-QFN (3x3)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8lb10f16e-a-qfn24 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.4 Clocking

The CPU core and peripheral subsystem may be clocked by both internal and external oscillator resources. By default, the system clock comes up running from the 24.5 MHz oscillator divided by 8.

The clock control system offers the following features:

- · Provides clock to core and peripherals.

- 24.5 MHz internal oscillator (HFOSC0), accurate to ±2% over supply and temperature corners.

- 72 MHz internal oscillator (HFOSC1), accurate to ±2% over supply and temperature corners.

- 80 kHz low-frequency oscillator (LFOSC0).

- · External Crystal / RC / C Oscillator.

- · External CMOS clock input (EXTCLK).

- · Clock divider with eight settings for flexible clock scaling:

- Divide the selected clock source by 1, 2, 4, 8, 16, 32, 64, or 128.

- HFOSC0 and HFOSC1 include 1.5x pre-scalers for further flexibility.

#### 3.5 Counters/Timers and PWM

#### Programmable Counter Array (PCA0)

The programmable counter array (PCA) provides multiple channels of enhanced timer and PWM functionality while requiring less CPU intervention than standard counter/timers. The PCA consists of a dedicated 16-bit counter/timer and one 16-bit capture/compare module for each channel. The counter/timer is driven by a programmable timebase that has flexible external and internal clocking options. Each capture/compare module may be configured to operate independently in one of five modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, or Pulse-Width Modulated (PWM) Output. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the crossbar to port I/O when enabled.

- · 16-bit time base

- · Programmable clock divisor and clock source selection

- · Up to six independently-configurable channels

- 8, 9, 10, 11 and 16-bit PWM modes (center or edge-aligned operation)

- Output polarity control

- Frequency output mode

- Capture on rising, falling or any edge

- Compare function for arbitrary waveform generation

- · Software timer (internal compare) mode

- · Can accept hardware "kill" signal from comparator 0 or comparator 1

## Timers (Timer 0, Timer 1, Timer 2, Timer 3, Timer 4, and Timer 5)

Several counter/timers are included in the device: two are 16-bit counter/timers compatible with those found in the standard 8051, and the rest are 16-bit auto-reload timers for timing peripherals or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. The other timers offer both 16-bit and split 8-bit timer functionality with auto-reload and capture capabilities.

Timer 0 and Timer 1 include the following features:

- Standard 8051 timers, supporting backwards-compatibility with firmware and hardware.

- Clock sources include SYSCLK, SYSCLK divided by 12, 4, or 48, the External Clock divided by 8, or an external pin.

- · 8-bit auto-reload counter/timer mode

- 13-bit counter/timer mode

- 16-bit counter/timer mode

- Dual 8-bit counter/timer mode (Timer 0)

Timer 2, Timer 3, Timer 4, and Timer 5 are 16-bit timers including the following features:

- · Clock sources for all timers include SYSCLK, SYSCLK divided by 12, or the External Clock divided by 8

- · LFOSC0 divided by 8 may be used to clock Timer 3 and Timer 4 in active or suspend/snooze power modes

- Timer 4 is a low-power wake source, and can be chained together with Timer 3

- 16-bit auto-reload timer mode

- Dual 8-bit auto-reload timer mode

- · External pin capture

- · LFOSC0 capture

- Comparator 0 capture

- Configurable Logic output capture

### Watchdog Timer (WDT0)

The device includes a programmable watchdog timer (WDT) running off the low-frequency oscillator. A WDT overflow forces the MCU into the reset state. To prevent the reset, the WDT must be restarted by application software before overflow. If the system experiences a software or hardware malfunction preventing the software from restarting the WDT, the WDT overflows and causes a reset. Following a reset, the WDT is automatically enabled and running with the default maximum time interval. If needed, the WDT can be disabled by system software or locked on to prevent accidental disabling. Once locked, the WDT cannot be disabled until the next system reset. The state of the RST pin is unaffected by this reset.

The Watchdog Timer has the following features:

- · Programmable timeout interval

- · Runs from the low-frequency oscillator

- · Lock-out feature to prevent any modification until a system reset

#### 3.6 Communications and Other Digital Peripherals

#### Universal Asynchronous Receiver/Transmitter (UART0)

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates. Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

The UART module provides the following features:

- · Asynchronous transmissions and receptions

- Baud rates up to SYSCLK/2 (transmit) or SYSCLK/8 (receive)

- 8- or 9-bit data

- · Automatic start and stop generation

- · Single-byte buffer on transmit and receive

### 4. Electrical Specifications

### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the conditions listed in Table 4.1 Recommended Operating Conditions on page 13, unless stated otherwise.

Table 4.1. Recommended Operating Conditions

### 4.1.1 Recommended Operating Conditions

| Parameter                                          | Symbol              | Test Condition | Min | Тур | Max             | Unit |

|----------------------------------------------------|---------------------|----------------|-----|-----|-----------------|------|

| Operating Supply Voltage on VDD                    | V <sub>DD</sub>     |                | 2.2 | _   | 3.6             | V    |

| Operating Supply Voltage on VIO <sup>2,</sup><br>3 | V <sub>IO</sub>     |                | TBD |     | V <sub>DD</sub> | V    |

| System Clock Frequency                             | f <sub>SYSCLK</sub> |                | 0   | —   | 73.5            | MHz  |

| Operating Ambient Temperature                      | T <sub>A</sub>      |                | -40 | —   | 105             | °C   |

| Noto:                                              |                     |                |     |     |                 | •    |

#### Note:

1. All voltages with respect to GND

2. In certain package configurations, the VIO and VDD supplies are bonded to the same pin.

3. GPIO levels are undefined whenever VIO is less than 1 V.

### 4.1.4 Flash Memory

| Parameter                                               | Symbol             | Test Condition                 | Min | Тур  | Max | Units  |

|---------------------------------------------------------|--------------------|--------------------------------|-----|------|-----|--------|

| Write Time <sup>1 ,2</sup>                              | t <sub>WRITE</sub> | One Byte,                      | 19  | 20   | 21  | μs     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| Erase Time <sup>1,2</sup>                               | t <sub>ERASE</sub> | One Page,                      | 5.2 | 5.35 | 5.5 | ms     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| V <sub>DD</sub> Voltage During Programming <sup>3</sup> | V <sub>PROG</sub>  |                                | 2.2 | _    | 3.6 | V      |

| Endurance (Write/Erase Cycles)                          | N <sub>WE</sub>    |                                | 20k | 100k |     | Cycles |

### Table 4.4. Flash Memory

Note:

1. Does not include sequencing time before and after the write/erase operation, which may be multiple SYSCLK cycles.

2. The internal High-Frequency Oscillator 0 has a programmable output frequency, which is factory programmed to 24.5 MHz. If user firmware adjusts the oscillator speed, it must be between 22 and 25 MHz during any flash write or erase operation. It is recommended to write the HFO0CAL register back to its reset value when writing or erasing flash.

3. Flash can be safely programmed at any voltage above the supply monitor threshold (V<sub>VDDM</sub>).

4. Data Retention Information is published in the Quarterly Quality and Reliability Report.

### 4.1.5 Power Management Timing

### Table 4.5. Power Management Timing

| Parameter                 | Symbol               | Test Condition  | Min | Тур | Max | Units   |

|---------------------------|----------------------|-----------------|-----|-----|-----|---------|

| Idle Mode Wake-up Time    | t <sub>IDLEWK</sub>  |                 | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time | t <sub>SUS-</sub>    | SYSCLK = HFOSC0 | _   | 170 | _   | ns      |

|                           | PENDWK               | CLKDIV = 0x00   |     |     |     |         |

| Snooze Mode Wake-up Time  | t <sub>SLEEPWK</sub> | SYSCLK = HFOSC0 | —   | 12  | —   | μs      |

|                           |                      | CLKDIV = 0x00   |     |     |     |         |

### 4.1.6 Internal Oscillators

| Parameter                       | Symbol                    | Test Condition                    | Min  | Тур  | Max  | Unit   |

|---------------------------------|---------------------------|-----------------------------------|------|------|------|--------|

| High Frequency Oscillator 0 (2- | 4.5 MHz)                  |                                   |      |      | 1    |        |

| Oscillator Frequency            | f <sub>HFOSC0</sub>       | Full Temperature and Supply Range | 24   | 24.5 | 25   | MHz    |

| Power Supply Sensitivity        | PSS <sub>HFOS</sub><br>C0 | T <sub>A</sub> = 25 °C            | -    | 0.5  | _    | %/V    |

| Temperature Sensitivity         | TS <sub>HFOSC0</sub>      | V <sub>DD</sub> = 3.0 V           | _    | 40   | _    | ppm/°C |

| High Frequency Oscillator 1 (7) | 2 MHz)                    |                                   |      | 1    | 1    | -      |

| Oscillator Frequency            | f <sub>HFOSC1</sub>       | Full Temperature and Supply Range | 70.5 | 72   | 73.5 | MHz    |

| Power Supply Sensitivity        | PSS <sub>HFOS</sub><br>C1 | T <sub>A</sub> = 25 °C            | -    | TBD  | _    | %/V    |

| Temperature Sensitivity         | TS <sub>HFOSC1</sub>      | V <sub>DD</sub> = 3.0 V           | _    | TBD  | _    | ppm/°C |

| Low Frequency Oscillator (80 k  | (Hz)                      | 1                                 | 1    | 1    | 1    | 1      |

| Oscillator Frequency            | f <sub>LFOSC</sub>        | Full Temperature and Supply Range | 75   | 80   | 85   | kHz    |

| Power Supply Sensitivity        | PSS <sub>LFOSC</sub>      | T <sub>A</sub> = 25 °C            | _    | 0.05 | _    | %/V    |

| Temperature Sensitivity         | TS <sub>LFOSC</sub>       | V <sub>DD</sub> = 3.0 V           | _    | 65   | _    | ppm/°C |

### Table 4.6. Internal Oscillators

### 4.1.7 External Clock Input

### Table 4.7. External Clock Input

| Parameter                             | Symbol             | Test Condition | Min | Тур | Max | Unit |

|---------------------------------------|--------------------|----------------|-----|-----|-----|------|

| External Input CMOS Clock             | f <sub>CMOS</sub>  |                | 0   | —   | 50  | MHz  |

| Frequency (at EXTCLK pin)             |                    |                |     |     |     |      |

| External Input CMOS Clock High Time   | t <sub>CMOSH</sub> |                | 9   | _   |     | ns   |

| External Input CMOS Clock Low<br>Time | t <sub>CMOSL</sub> |                | 9   | _   | _   | ns   |

### 4.1.11 Temperature Sensor

| Parameter                                                | Symbol           | Test Condition        | Min | Тур  | Max | Unit  |

|----------------------------------------------------------|------------------|-----------------------|-----|------|-----|-------|

| Uncalibrated Offset                                      | V <sub>OFF</sub> | T <sub>A</sub> = 0 °C | —   | TBD  | _   | mV    |

| Uncalibrated Offset Error <sup>1</sup>                   | E <sub>OFF</sub> | T <sub>A</sub> = 0 °C | _   | TBD  | —   | mV    |

| Slope                                                    | М                |                       | _   | 2.83 |     | mV/°C |

| Slope Error <sup>1</sup>                                 | E <sub>M</sub>   |                       | _   | TBD  | _   | μV/°C |

| Linearity                                                |                  |                       | —   | TBD  | —   | °C    |

| Turn-on Time                                             |                  |                       | _   | TBD  | _   | μs    |

| Temp Sensor Error Using Typical                          |                  | T = 0 °C to 70 °C     | TBD | _    | TBD | °C    |

| Slope and Factory-Calibrated Off-<br>set <sup>2, 3</sup> |                  | T = -20 °C to 85 °C   | -3  | _    | 3   | °C    |

|                                                          |                  | T = -40 °C to 105 °C  | TBD | —    | TBD | °C    |

### Table 4.11. Temperature Sensor

### Note:

1. Represents one standard deviation from the mean.

2. The factory-calibrated offset value is stored in the read-only area of flash in locations 0xFFD4 (low byte) and 0xFFD5 (high byte). The 14-bit result represents the output of the ADC when sampling the temp sensor using the 1.65 V internal voltage reference.

3. Temp sensor error is based upon characterization and is not tested across temperature in production. The values represent three standard deviations above and below the mean.

### 4.1.15 Port I/O

### Table 4.15. Port I/O

| Parameter                                  | Symbol          | Test Condition                                            | Min                   | Тур | Мах                   | Unit |

|--------------------------------------------|-----------------|-----------------------------------------------------------|-----------------------|-----|-----------------------|------|

| Output High Voltage (High Drive)           | V <sub>OH</sub> | I <sub>OH</sub> = -7 mA, V <sub>IO</sub> ≥ 3.0 V          | V <sub>IO</sub> - 0.7 | _   | —                     | V    |

|                                            |                 | $I_{OH}$ = -3.3 mA, 2.2 V ≤ V <sub>IO</sub> < 3.0 V       | V <sub>IO</sub> x 0.8 | _   | _                     | V    |

|                                            |                 | $I_{OH}$ = -1.8 mA, 1.71 V $\leq$ V <sub>IO</sub> < 2.2 V |                       |     |                       |      |

| Output Low Voltage (High Drive)            | V <sub>OL</sub> | I <sub>OL</sub> = 13.5 mA, V <sub>IO</sub> ≥ 3.0 V        | _                     | _   | 0.6                   | V    |

|                                            |                 | $I_{OL}$ = 7 mA, 2.2 V $\leq$ V <sub>IO</sub> < 3.0 V     | _                     | _   | V <sub>IO</sub> x 0.2 | V    |

|                                            |                 | $I_{OL}$ = 3.6 mA, 1.71 V $\leq$ V <sub>IO</sub> < 2.2 V  |                       |     |                       |      |

| Output High Voltage (Low Drive)            | V <sub>OH</sub> | I <sub>OH</sub> = -4.75 mA, V <sub>IO</sub> ≥ 3.0 V       | V <sub>IO</sub> - 0.7 | _   | _                     | V    |

|                                            |                 | $I_{OH}$ = -2.25 mA, 2.2 V ≤ V <sub>IO</sub> < 3.0 V      | V <sub>IO</sub> x 0.8 | —   | —                     | V    |

|                                            |                 | $I_{OH}$ = -1.2 mA, 1.71 V $\leq$ V <sub>IO</sub> < 2.2 V |                       |     |                       |      |

| Output Low Voltage (Low Drive)             | V <sub>OL</sub> | I <sub>OL</sub> = 6.5 mA, V <sub>IO</sub> ≥ 3.0 V         | —                     | —   | 0.6                   | V    |

|                                            |                 | $I_{OL}$ = 3.5 mA, 2.2 V ≤ V <sub>IO</sub> < 3.0 V        | _                     | —   | V <sub>IO</sub> x 0.2 | V    |

|                                            |                 | $I_{OL}$ = 1.8 mA, 1.71 V $\leq$ V <sub>IO</sub> < 2.2 V  |                       |     |                       |      |

| Input High Voltage                         | V <sub>IH</sub> |                                                           | 0.7 x                 | —   | —                     | V    |

|                                            |                 |                                                           | V <sub>IO</sub>       |     |                       |      |

| Input Low Voltage                          | V <sub>IL</sub> |                                                           | —                     | _   | 0.3 x                 | V    |

|                                            |                 |                                                           |                       |     | V <sub>IO</sub>       |      |

| Pin Capacitance                            | C <sub>IO</sub> |                                                           | —                     | 7   | —                     | pF   |

| Weak Pull-Up Current                       | I <sub>PU</sub> | V <sub>DD</sub> = 3.6                                     | -30                   | -20 | -10                   | μA   |

| (V <sub>IN</sub> = 0 V)                    |                 |                                                           |                       |     |                       |      |

| Input Leakage (Pullups off or Ana-<br>log) | I <sub>LK</sub> | GND < V <sub>IN</sub> < V <sub>IO</sub>                   | TBD                   | _   | TBD                   | μA   |

| Input Leakage Current with VIN             | I <sub>LK</sub> | $V_{IO} < V_{IN} < V_{IO} + 2.5 V$                        | 0                     | 5   | 150                   | μA   |

| above V <sub>IO</sub>                      |                 | Any pin except P3.0, P3.1, P3.2, or P3.3                  |                       |     |                       |      |

## 6. Pin Definitions

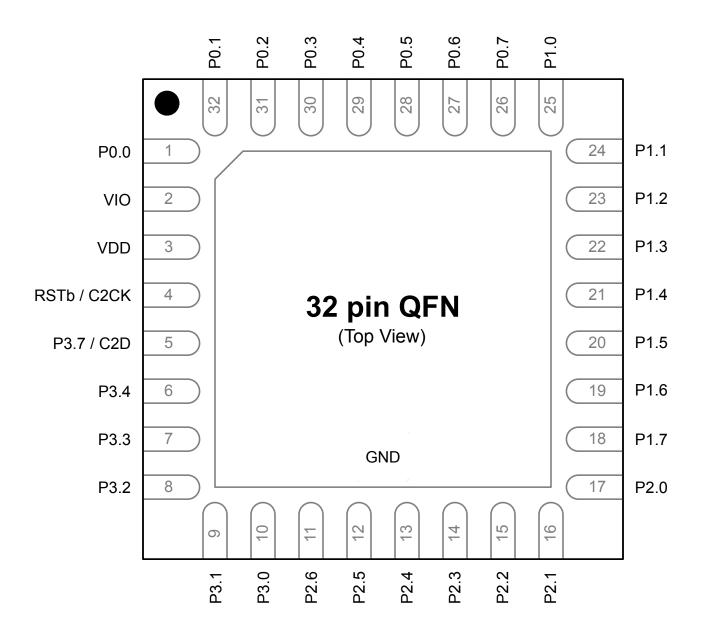

### 6.1 EFM8LB1x-QFN32 Pin Definitions

Figure 6.1. EFM8LB1x-QFN32 Pinout

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 22            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                         | ADC0.9           |

|               |          |                   |                     | CLU0B.13                        |                  |

|               |          |                   |                     | CLU1B.11                        |                  |

|               |          |                   |                     | CLU2B.11                        |                  |

|               |          |                   |                     | CLU3A.13                        |                  |

| 23            | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                         | ADC0.8           |

|               |          |                   |                     | CLU0A.13                        | CMP0P.8          |

|               |          |                   |                     | CLU1A.11                        | CMP0N.8          |

|               |          |                   |                     | CLU2B.10                        |                  |

|               |          |                   |                     | CLU3A.12                        |                  |

|               |          |                   |                     | CLU3B.13                        |                  |

| 24            | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                         | ADC0.7           |

|               |          |                   |                     | CLU0B.12                        | CMP0P.7          |

|               |          |                   |                     | CLU1B.10                        | CMP0N.7          |

|               |          |                   |                     | CLU2A.11                        |                  |

|               |          |                   |                     | CLU3B.12                        |                  |

| 25            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                         | ADC0.6           |

|               |          |                   |                     | CLU1OUT                         | CMP0P.6          |

|               |          |                   |                     | CLU0A.12                        | CMP0N.6          |

|               |          |                   |                     | CLU1A.10                        | CMP1P.1          |

|               |          |                   |                     | CLU2A.10                        | CMP1N.1          |

| 26            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                         | ADC0.5           |

|               |          |                   |                     | INT0.7                          | CMP0P.5          |

|               |          |                   |                     | INT1.7                          | CMP0N.5          |

|               |          |                   |                     | CLU0B.11                        | CMP1P.0          |

|               |          |                   |                     | CLU1B.9                         | CMP1N.0          |

|               |          |                   |                     | CLU3A.11                        |                  |

| 27            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                         | ADC0.4           |

|               |          |                   |                     | CNVSTR                          | CMP0P.4          |

|               |          |                   |                     | INT0.6                          | CMP0N.4          |

|               |          |                   |                     | INT1.6                          |                  |

|               |          |                   |                     | CLU0A.11                        |                  |

|               |          |                   |                     | CLU1B.8                         |                  |

|               |          |                   |                     | CLU3A.10                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 28            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                         | ADC0.3           |

|               |          |                   |                     | INT0.5                          | CMP0P.3          |

|               |          |                   |                     | INT1.5                          | CMP0N.3          |

|               |          |                   |                     | UART0_RX                        |                  |

|               |          |                   |                     | CLU0B.10                        |                  |

|               |          |                   |                     | CLU1A.9                         |                  |

| 29            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.2           |

|               |          |                   |                     | INT0.4                          | CMP0P.2          |

|               |          |                   |                     | INT1.4                          | CMP0N.2          |

|               |          |                   |                     | UART0_TX                        |                  |

|               |          |                   |                     | CLU0A.10                        |                  |

|               |          |                   |                     | CLU1A.8                         |                  |

| 30            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | XTAL2            |

|               |          |                   |                     | EXTCLK                          |                  |

|               |          |                   |                     | INT0.3                          |                  |

|               |          |                   |                     | INT1.3                          |                  |

|               |          |                   |                     | CLU0B.9                         |                  |

|               |          |                   |                     | CLU2B.10                        |                  |

|               |          |                   |                     | CLU3A.9                         |                  |

| 31            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | XTAL1            |

|               |          |                   |                     | INT0.2                          | ADC0.1           |

|               |          |                   |                     | INT1.2                          | CMP0P.1          |

|               |          |                   |                     | CLU0OUT                         | CMP0N.1          |

|               |          |                   |                     | CLU0A.9                         |                  |

|               |          |                   |                     | CLU2B.8                         |                  |

|               |          |                   |                     | CLU3A.8                         |                  |

| 32            | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                         | ADC0.0           |

|               |          |                   |                     | INT0.1                          | CMP0P.0          |

|               |          |                   |                     | INT1.1                          | CMP0N.0          |

|               |          |                   |                     | CLU0B.8                         | AGND             |

|               |          |                   |                     | CLU2A.9                         |                  |

|               |          |                   |                     | CLU3B.9                         |                  |

| Center        | GND      | Ground            |                     |                                 |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 25            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                         | ADC0.6           |

|               |          |                   |                     | CLU1OUT                         | CMP0P.6          |

|               |          |                   |                     | CLU0A.12                        | CMP0N.6          |

|               |          |                   |                     | CLU1A.10                        | CMP1P.1          |

|               |          |                   |                     | CLU2A.10                        | CMP1N.1          |

| 26            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                         | ADC0.5           |

|               |          |                   |                     | INT0.7                          | CMP0P.5          |

|               |          |                   |                     | INT1.7                          | CMP0N.5          |

|               |          |                   |                     | CLU0B.11                        | CMP1P.0          |

|               |          |                   |                     | CLU1B.9                         | CMP1N.0          |

|               |          |                   |                     | CLU3A.11                        |                  |

| 27            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                         | ADC0.4           |

|               |          |                   |                     | CNVSTR                          | CMP0P.4          |

|               |          |                   |                     | INT0.6                          | CMP0N.4          |

|               |          |                   |                     | INT1.6                          |                  |

|               |          |                   |                     | CLU0A.11                        |                  |

|               |          |                   |                     | CLU1B.8                         |                  |

|               |          |                   |                     | CLU3A.10                        |                  |

| 28            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                         | ADC0.3           |

|               |          |                   |                     | INT0.5                          | CMP0P.3          |

|               |          |                   |                     | INT1.5                          | CMP0N.3          |

|               |          |                   |                     | UART0_RX                        |                  |

|               |          |                   |                     | CLU0B.10                        |                  |

|               |          |                   |                     | CLU1A.9                         |                  |

| 29            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.2           |

|               |          |                   |                     | INT0.4                          | CMP0P.2          |

|               |          |                   |                     | INT1.4                          | CMP0N.2          |

|               |          |                   |                     | UART0_TX                        |                  |

|               |          |                   |                     | CLU0A.10                        |                  |

|               |          |                   |                     | CLU1A.8                         |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 30            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | XTAL2            |

|               |          |                   |                     | EXTCLK                          |                  |

|               |          |                   |                     | INT0.3                          |                  |

|               |          |                   |                     | INT1.3                          |                  |

|               |          |                   |                     | CLU0B.9                         |                  |

|               |          |                   |                     | CLU2B.10                        |                  |

|               |          |                   |                     | CLU3A.9                         |                  |

| 31            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | XTAL1            |

|               |          |                   |                     | INT0.2                          | ADC0.1           |

|               |          |                   |                     | INT1.2                          | CMP0P.1          |

|               |          |                   |                     | CLU0OUT                         | CMP0N.1          |

|               |          |                   |                     | CLU0A.9                         |                  |

|               |          |                   |                     | CLU2B.8                         |                  |

|               |          |                   |                     | CLU3A.8                         |                  |

| 32            | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                         | ADC0.0           |

|               |          |                   |                     | INT0.1                          | CMP0P.0          |

|               |          |                   |                     | INT1.1                          | CMP0N.0          |

|               |          |                   |                     | CLU0B.8                         | AGND             |

|               |          |                   |                     | CLU2A.9                         |                  |

|               |          |                   |                     | CLU3B.9                         |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 19            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                         | ADC0.5           |

|               |          |                   |                     | INT0.7                          | CMP0P.5          |

|               |          |                   |                     | INT1.7                          | CMP0N.5          |

|               |          |                   |                     | CLU1OUT                         | CMP1P.1          |

|               |          |                   |                     | CLU0B.11                        | CMP1N.1          |

|               |          |                   |                     | CLU1B.9                         |                  |

|               |          |                   |                     | CLU3A.11                        |                  |

| 20            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                         | ADC0.4           |

|               |          |                   |                     | CNVSTR                          | CMP0P.4          |

|               |          |                   |                     | INT0.6                          | CMP0N.4          |

|               |          |                   |                     | INT1.6                          | CMP1P.0          |

|               |          |                   |                     | CLU0A.11                        | CMP1N.0          |

|               |          |                   |                     | CLU1B.8                         |                  |

|               |          |                   |                     | CLU3A.10                        |                  |

| 21            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                         | ADC0.3           |

|               |          |                   |                     | INT0.5                          | CMP0P.3          |

|               |          |                   |                     | INT1.5                          | CMP0N.3          |

|               |          |                   |                     | UART0_RX                        |                  |

|               |          |                   |                     | CLU0B.10                        |                  |

|               |          |                   |                     | CLU1A.9                         |                  |

| 22            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.2           |

|               |          |                   |                     | INT0.4                          | CMP0P.2          |

|               |          |                   |                     | INT1.4                          | CMP0N.2          |

|               |          |                   |                     | UART0_TX                        |                  |

|               |          |                   |                     | CLU0A.10                        |                  |

|               |          |                   |                     | CLU1A.8                         |                  |

| 23            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | XTAL2            |

|               |          |                   |                     | EXTCLK                          |                  |

|               |          |                   |                     | INT0.3                          |                  |

|               |          |                   |                     | INT1.3                          |                  |

|               |          |                   |                     | CLU0B.9                         |                  |

|               |          |                   |                     | CLU2B.10                        |                  |

|               |          |                   |                     | CLU3A.9                         |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 24            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | XTAL1            |

|               |          |                   |                     | INT0.2                          | ADC0.1           |

|               |          |                   |                     | INT1.2                          | CMP0P.1          |

|               |          |                   |                     | CLU0OUT                         | CMP0N.1          |

|               |          |                   |                     | CLU0A.9                         |                  |

|               |          |                   |                     | CLU2B.8                         |                  |

|               |          |                   |                     | CLU3A.8                         |                  |

| Center        | GND      | Ground            |                     |                                 |                  |

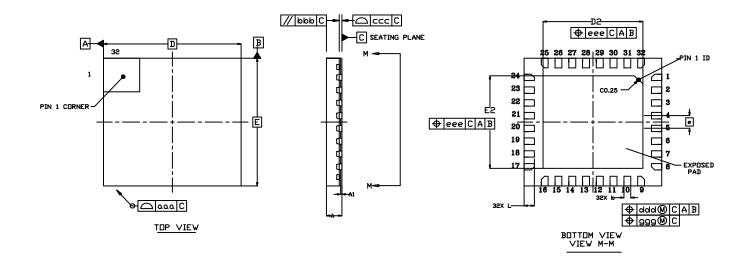

## 7. QFN32 Package Specifications

### 7.1 QFN32 Package Dimensions

Figure 7.1. QFN32 Package Drawing

| Dimension | Min       | Тур       | Мах  |  |  |  |  |

|-----------|-----------|-----------|------|--|--|--|--|

| A         | 0.45      | 0.50      | 0.55 |  |  |  |  |

| A1        | 0.00      | 0.035     | 0.05 |  |  |  |  |

| b         | 0.15      | 0.20      | 0.25 |  |  |  |  |

| D         |           | 4.00 BSC. |      |  |  |  |  |

| D2        | 2.80      | 2.90      | 3.00 |  |  |  |  |

| е         | 0.40 BSC. |           |      |  |  |  |  |

| E         | 4.00 BSC. |           |      |  |  |  |  |

| E2        | 2.80      | 2.90      | 3.00 |  |  |  |  |

| L         | 0.20      | 0.30      | 0.40 |  |  |  |  |

| ааа       | —         | _         | 0.10 |  |  |  |  |

| bbb       | —         | —         | 0.10 |  |  |  |  |

| ссс       | —         |           |      |  |  |  |  |

| ddd       | —         | —         | 0.10 |  |  |  |  |

| eee       | —         | —         | 0.10 |  |  |  |  |

| 999       | _         | _         | 0.05 |  |  |  |  |

### Table 7.1. QFN32 Package Dimensions

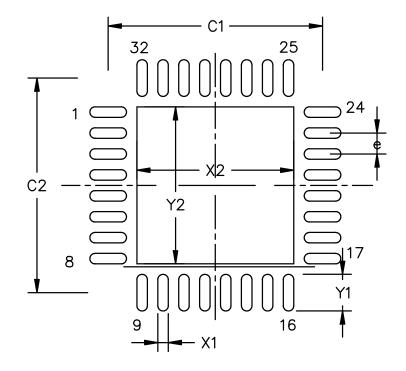

### 7.2 QFN32 PCB Land Pattern

Figure 7.2. QFN32 PCB Land Pattern Drawing

| Table 7.2. Q | FN32 PCB Land Pattern Dimensions |

|--------------|----------------------------------|

|--------------|----------------------------------|

| Dimension | Min | Мах  |

|-----------|-----|------|

| C1        | —   | 4.00 |

| C2        | —   | 4.00 |

| X1        | —   | 0.2  |

| X2        | _   | 2.8  |

| Y1        | —   | 0.75 |

| Y2        | —   | 2.8  |

| е         | _   | 0.4  |

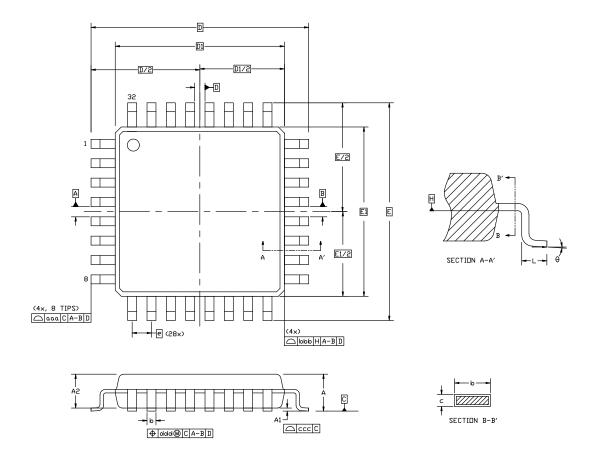

## 8. QFP32 Package Specifications

### 8.1 QFP32 Package Dimensions

Figure 8.1. QFP32 Package Drawing

### Table 8.1. QFP32 Package Dimensions

| Dimension | Min      | Тур      | Мах  |  |  |  |  |

|-----------|----------|----------|------|--|--|--|--|

| A         | _        | —        | 1.20 |  |  |  |  |

| A1        | 0.05     | —        | 0.15 |  |  |  |  |

| A2        | 0.95     | 1.00     | 1.05 |  |  |  |  |

| b         | 0.30     | 0.37     | 0.45 |  |  |  |  |

| С         | 0.09     | —        | 0.20 |  |  |  |  |

| D         |          | 9.00 BSC |      |  |  |  |  |

| D1        | 7.00 BSC |          |      |  |  |  |  |

| е         |          | 0.80 BSC |      |  |  |  |  |

| E         | 9.00 BSC |          |      |  |  |  |  |

| E1        |          | 7.00 BSC |      |  |  |  |  |

| L         | 0.50     | 0.60     | 0.70 |  |  |  |  |

| Dimension | Min | Тур     | Мах |  |  |  |  |  |

|-----------|-----|---------|-----|--|--|--|--|--|

| ааа       |     | 0.20    |     |  |  |  |  |  |

| bbb       |     | 0.20    |     |  |  |  |  |  |

| ССС       |     | 0.10    |     |  |  |  |  |  |

| ddd       |     | 0.20    |     |  |  |  |  |  |

| theta     | 0°  | 0° 3.5° |     |  |  |  |  |  |

| Note:     |     |         |     |  |  |  |  |  |

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MS-026.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

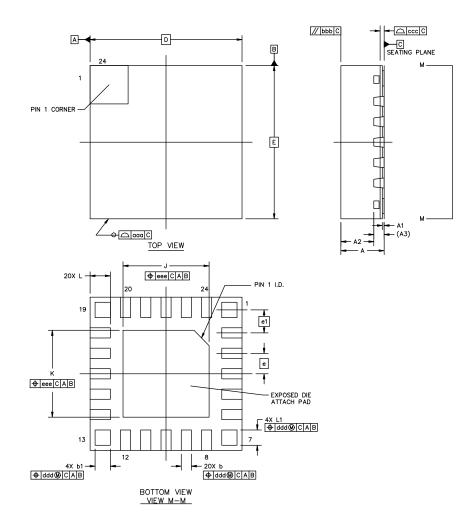

# 9. QFN24 Package Specifications

### 9.1 QFN24 Package Dimensions

Figure 9.1. QFN24 Package Drawing

| Table 9.1. | QFN24 Package Dimensions |

|------------|--------------------------|

|------------|--------------------------|

| Dimension | Min      | Тур       | Мах  |  |  |  |  |

|-----------|----------|-----------|------|--|--|--|--|

| A         | 0.8      | 0.85      | 0.9  |  |  |  |  |

| A1        | 0.00     | _         | 0.05 |  |  |  |  |

| A2        | —        | —         |      |  |  |  |  |

| A3        |          | 0.203 REF |      |  |  |  |  |

| b         | 0.15     | 0.15 0.2  |      |  |  |  |  |

| b1        | 0.25     | 0.35      |      |  |  |  |  |

| D         | 3.00 BSC |           |      |  |  |  |  |

| E         | 3.00 BSC |           |      |  |  |  |  |

|    | 6.3 EFM8LB1x-QFN24 Pin Definitions .  |  |  |  |  |   |  |  |   |   | .40 |

|----|---------------------------------------|--|--|--|--|---|--|--|---|---|-----|

|    | 6.4 EFM8LB1x-QSOP24 Pin Definitions . |  |  |  |  |   |  |  | • |   | .45 |

| 7. | . QFN32 Package Specifications.       |  |  |  |  |   |  |  |   |   | 50  |

|    | 7.1 QFN32 Package Dimensions          |  |  |  |  |   |  |  |   |   | .50 |

|    | 7.2 QFN32 PCB Land Pattern            |  |  |  |  |   |  |  |   |   | .52 |

|    | 7.3 QFN32 Package Marking             |  |  |  |  |   |  |  |   | • | .53 |

| 8. | . QFP32 Package Specifications.       |  |  |  |  |   |  |  |   |   | 54  |

|    | 8.1 QFP32 Package Dimensions          |  |  |  |  |   |  |  |   |   | .54 |

|    | 8.2 QFP32 PCB Land Pattern            |  |  |  |  |   |  |  | • |   | .56 |

|    | 8.3 QFP32 Package Marking             |  |  |  |  |   |  |  | • | • | .57 |

| 9. | . QFN24 Package Specifications.       |  |  |  |  |   |  |  |   |   | 58  |

|    | 9.1 QFN24 Package Dimensions          |  |  |  |  |   |  |  |   |   | .58 |

|    | 9.2 QFN24 PCB Land Pattern            |  |  |  |  |   |  |  |   |   | .60 |

|    | 9.3 QFN24 Package Marking             |  |  |  |  |   |  |  | • |   | .61 |

| 10 | 0. QSOP24 Package Specifications      |  |  |  |  |   |  |  |   |   | 62  |

|    | 10.1 QSOP24 Package Dimensions        |  |  |  |  |   |  |  |   |   | .62 |

|    | 10.2 QSOP24 PCB Land Pattern          |  |  |  |  |   |  |  |   |   | .64 |

|    | 10.3 QSOP24 Package Marking           |  |  |  |  |   |  |  |   |   | .65 |

| 11 | 1. Revision History                   |  |  |  |  |   |  |  |   |   | 66  |

|    | 11.1 Revision 0.1                     |  |  |  |  |   |  |  |   |   | .66 |

|    | 11.2 Revision 0.2                     |  |  |  |  |   |  |  |   |   | .66 |

| Та | able of Contents                      |  |  |  |  | • |  |  |   |   | 67  |