#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | 80C51                                                                     |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.400", 10.16mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5115-tisum |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SFR Mapping

Tables 3 through Table 11 show the Special Function Registers (SFRs) of the T89C5115.

## Table 2. C51 Core SFRs

| Mnemonic | Add | Name                                     | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator                              |    |    |    |     |     |    |    |   |

| В        | F0h | B Register                               |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word                      | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer                            |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low<br>byte<br>LSB of DPTR  |    |    |    |     |     |    |    |   |

| DPH      |     | Data Pointer High<br>byte<br>MSB of DPTR |    |    |    |     |     |    |    |   |

## Table 3. I/O Port SFRs

| Mnemonic | Add | Name        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|-------------|---|---|---|---|---|---|---|---|

| P1       | 90h | Port 1      |   |   |   |   |   |   |   |   |

| P2       | A0h | Port 2 (x2) |   |   |   |   |   |   |   |   |

| P3       | B0h | Port 3      |   |   |   |   |   |   |   |   |

| P4       | C0h | Port 4 (x2) |   |   |   |   |   |   |   |   |

## Table 4. Timers SFRs

| Mnemonic | Add | Name                          | 7     | 6     | 5   | 4   | 3     | 2     | 1   | 0   |

|----------|-----|-------------------------------|-------|-------|-----|-----|-------|-------|-----|-----|

| TH0      | 8Ch | Timer/Counter 0 High byte     |       |       |     |     |       |       |     |     |

| TL0      | 8Ah | Timer/Counter 0 Low byte      |       |       |     |     |       |       |     |     |

| TH1      | 8Dh | Timer/Counter 1 High byte     |       |       |     |     |       |       |     |     |

| TL1      | 8Bh | Timer/Counter 1 Low byte      |       |       |     |     |       |       |     |     |

| TH2      | CDh | Timer/Counter 2 High byte     |       |       |     |     |       |       |     |     |

| TL2      | CCh | Timer/Counter 2 Low byte      |       |       |     |     |       |       |     |     |

| TCON     | 88h | Timer/Counter 0 and 1 control | TF1   | TR1   | TF0 | TR0 | IE1   | IT1   | IE0 | IT0 |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes   | GATE1 | C/T1# | M11 | M01 | GATE0 | C/T0# | M10 | M00 |

# **Table 18.** AUXR1 RegisterAUXR1 (S:A2h)Auxiliary Control Register 1

| 7             | 6                     | 5                                       | 4                                                                                                                            | 3               | 2              | 1              | 0           |  |  |  |

|---------------|-----------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|----------------|-------------|--|--|--|

| -             | -                     | ENBOOT                                  | ENBOOT - GF3 0 - DPS                                                                                                         |                 |                |                |             |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic       | Description                             | Description                                                                                                                  |                 |                |                |             |  |  |  |

| 7 - 6         | -                     | <b>Reserved</b><br>The value rea        | Reserved<br>The value read from these bits is indeterminate. Do not set these bits.                                          |                 |                |                |             |  |  |  |

| 5             | ENBOOT <sup>(1)</sup> | Set this bit to                         | Enable Boot Flash<br>Set this bit to map the boot Flash between F800h -FFFFh<br>Clear this bit to disable boot Flash.        |                 |                |                |             |  |  |  |

| 4             | -                     | <b>Reserved</b><br>The value rea        | ad from this b                                                                                                               | it is indetermi | nate. Do not s | et this bit.   |             |  |  |  |

| 3             | GF3                   | General Pur                             | pose Flag 3                                                                                                                  |                 |                |                |             |  |  |  |

| 2             | 0                     | Always Zero<br>This bit is stu<br>flag. |                                                                                                                              | to allow INC A  | UXR1 instruct  | ion without af | fecting GF3 |  |  |  |

| 1             | -                     | Reserved fo                             | r Data Pointe                                                                                                                | er Extension    |                |                |             |  |  |  |

| 0             | DPS                   | Set to select                           | Data Pointer Select bit<br>Set to select second dual data pointer: DPTR1.<br>Clear to select first dual data pointer: DPTR0. |                 |                |                |             |  |  |  |

Reset Value = XXXX 00X0b

Note: 1. ENBOOT is initialized with the invert BLJB at reset. See In-System Programming section.

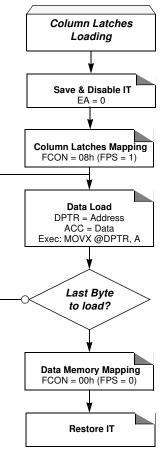

| EEPROM Data<br>Memory               | The 2K bytes on-chip EEPROM memory block is located at addresses 0000h to 07FFh of the XRAM/XRAM memory space and is selected by setting control bits in the EECON register. A read in the EEPROM memory is done with a MOVX instruction.                                                                                                                                                                                                                                                       |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | A physical write in the EEPROM memory is done in two steps: write data in the column latches and transfer of all data latches into an EEPROM memory row (programming).                                                                                                                                                                                                                                                                                                                          |

|                                     | The number of data written on the page may vary from 1 up to 128 Bytes (the page size). When programming, only the data written in the column latch is programmed and a ninth bit is used to obtain this feature. This provides the capability to program the whole memory by Bytes, by page or by a number of Bytes in a page. Indeed, each ninth bit is set when the writing the corresponding byte in a row and all these ninth bits are reset after the writing of the complete EEPROM row. |

| Write Data in the Column<br>Latches | Data is written by byte to the column latches as for an external RAM memory. Out of the 11 address bits of the data pointer, the 4 MSBs are used for page selection (row) and 7 are used for byte selection. Between two EEPROM programming sessions, all the addresses in the column latches must stay on the same page, meaning that the 4 MSB must no be changed.                                                                                                                            |

|                                     | The following procedure is used to write to the column latches:                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                     | Save and disable interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     | Set bit EEE of EECON register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | Load DPTR with the address to write                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                     | Store A register with the data to be written                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                     | Execute a MOVX @DPTR, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | If needed loop the three last instructions until the end of a 128 Bytes page                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                     | Restore interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                     | Note: The last page address used when loading the column latch is the one used to select the page programming address.                                                                                                                                                                                                                                                                                                                                                                          |

| Programming                         | The EEPROM programming consists of the following actions:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                     | • Write one or more Bytes of one page in the column latches. Normally, all Bytes must belong to the same page; if not, the last page address will be latched and the others discarded.                                                                                                                                                                                                                                                                                                          |

|                                     | <ul> <li>Launch programming by writing the control sequence (50h followed by A0h) to the<br/>EECON register.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | • EEBUSY flag in EECON is then set by hardware to indicate that programming is in progress and that the EEPROM segment is not available for reading.                                                                                                                                                                                                                                                                                                                                            |

|                                     | • The end of programming is indicated by a hardware clear of the EEBUSY flag.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | Note: The sequence 5xh and Axh must be executed without instructions between then other-<br>wise the programming is aborted.                                                                                                                                                                                                                                                                                                                                                                    |

| Read Data                           | The following procedure is used to read the data stored in the EEPROM memory:                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | Save and disable interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     | Set bit EEE of EECON register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | Load DPTR with the address to read                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                     | Execute a MOVX A, @DPTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | Restore interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 14. Column Latches Loading Procedure<sup>(1)</sup>

Note: 1. The last page address used when loading the column latch is the one used to select the page programming address.

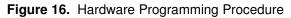

## **Programming the Flash Spaces**

User

The following procedure is used to program the User space and is summarized in Figure 15:

- Load up to one page of data in the column latches from address 0000h to 3FFFh.

- Save then disable the interrupts.

- Launch the programming by writing the data sequence 50h followed by A0h in FCON register. This step must be executed from FM1. The end of the programming indicated by the FBUSY flag cleared.

- Restore the interrupts.

٠

Extra Row

- The following procedure is used to program the Extra Row space and is summarized in Figure 15:

- Load data in the column latches from address FF80h to FFFFh.

- Save then disable the interrupts.

- Launch the programming by writing the data sequence 52h followed by A2h in FCON register. This step of the procedure must be executed from FM1. The end of the programming indicated by the FBUSY flag cleared.

- Restore the interrupts.

<sup>36</sup> **AT89C5115**

## Reading the Flash Spaces

| User                   | <ul> <li>The following procedure is used to read the User space:</li> <li>Read one byte in Accumulator by executing MOVC A,@A+DPTR with A+DPTR is the address of the code byte to read.</li> </ul> |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Note: FCON must be cleared (00h) when not used.                                                                                                                                                    |

| Extra Row              | The following procedure is used to read the Extra Row space and is summarized in Figure 17:                                                                                                        |

|                        | <ul> <li>Map the Extra Row space by writing 02h in FCON register.</li> </ul>                                                                                                                       |

|                        | <ul> <li>Read one byte in Accumulator by executing MOVC A,@A+DPTR with A= 0 &amp;<br/>DPTR= FF80h to FFFFh.</li> </ul>                                                                             |

|                        | Clear FCON to unmap the Extra Row.                                                                                                                                                                 |

| Hardware Security Byte | The following procedure is used to read the Hardware Security Byte and is sum-<br>marized in Figure 17:                                                                                            |

|                        | <ul> <li>Map the Hardware Security space by writing 04h in FCON register.</li> </ul>                                                                                                               |

|                        | <ul> <li>Read the byte in Accumulator by executing MOVC A,@A+DPTR with A= 0 &amp;<br/>DPTR= 0000h.</li> </ul>                                                                                      |

|                        | Clear FCON to unmap the Hardware Security Byte.                                                                                                                                                    |

AT89C5115

**Table 40.** TL0 RegisterTL0 (S:8Ah)Timer 0 Low Byte Register

| 7             | 6               | 5           | 4           | 3 | 2 | 1 | 0 |  |  |

|---------------|-----------------|-------------|-------------|---|---|---|---|--|--|

|               |                 |             |             |   |   |   |   |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description | Description |   |   |   |   |  |  |

| 7:0           |                 | Low Byte of | Timer 0     |   |   |   |   |  |  |

Reset Value = 0000 0000b

**Table 41.** TH1 Register TH1 (S:8Dh) Timer 1 High Byte Register

| 7             | 6               | 5                    | 4           | 3 | 2 | 1 | 0 |  |  |

|---------------|-----------------|----------------------|-------------|---|---|---|---|--|--|

|               |                 |                      |             |   |   |   |   |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description          | Description |   |   |   |   |  |  |

| 7:0           |                 | High Byte of Timer 1 |             |   |   |   |   |  |  |

Reset Value = 0000 0000b

**Table 42.** TL1 RegisterTL1 (S:8Bh)Timer 1 Low Byte Register

| 7             | 6               | 5           | 4       | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|---------|---|---|---|---|

|               |                 |             |         |   |   |   |   |

| Bit<br>Number | Bit<br>Mnemonic | Description |         |   |   |   |   |

| 7:0           |                 | Low Byte of | Timer 1 |   |   |   |   |

Reset Value = 0000 0000b

Table 46.TL2 RegisterTL2 (S:CCh)Timer 2 Low Byte Register

| 7             | 6               | 5           | 4       | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|---------|---|---|---|---|

| -             | -               | -           | -       | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |         |   |   |   |   |

| 7 - 0         |                 | Low Byte of | Timer 2 |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

## Table 47. RCAP2H Register

RCAP2H (S:CBh) Timer 2 Reload/Capture High Byte Register

| 7             | 6               | 5            | 4                                    | 3 | 2 | 1 | 0 |  |  |

|---------------|-----------------|--------------|--------------------------------------|---|---|---|---|--|--|

| -             | -               | -            | -                                    | - | - | - | - |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description  | Description                          |   |   |   |   |  |  |

| 7 - 0         |                 | High Byte of | High Byte of Timer 2 Reload/Capture. |   |   |   |   |  |  |

Reset Value = 0000 0000b Not bit addressable

## Table 48. RCAP2L Register

RCAP2L (S:CAh) Timer 2 Reload/Capture Low Byte Register

| 7             | 6               | 5           | 4                                   | 3 | 2 | 1 | 0 |  |

|---------------|-----------------|-------------|-------------------------------------|---|---|---|---|--|

| -             | -               | -           | -                                   | - | - | - | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Description | Description                         |   |   |   |   |  |

| 7 - 0         |                 | Low Byte of | Low Byte of Timer 2 Reload/Capture. |   |   |   |   |  |

Reset Value = 0000 0000b Not bit addressable

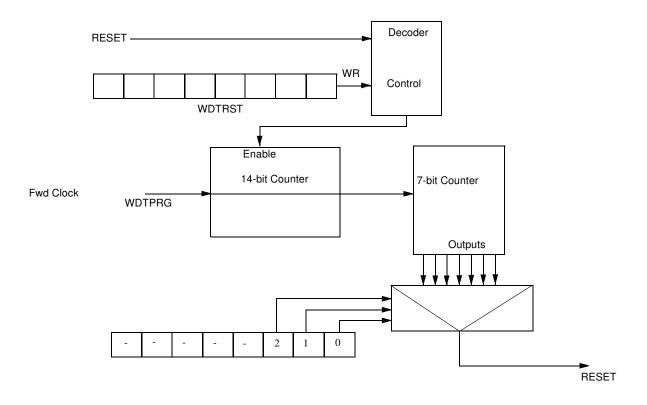

## Watchdog Timer

T89C5115 contains a powerful programmable hardware Watchdog Timer (WDT) that automatically resets the chip if it software fails to reset the WDT before the selected time interval has elapsed. It permits large Timeout ranging from 16ms to 2s  $@f_{OSC} = 12$  MHz in X1 mode.

This WDT consists of a 14-bit counter plus a 7-bit programmable counter, a Watchdog Timer reset register (WDTRST) and a Watchdog Timer programming (WDTPRG) register. When exiting reset, the WDT is -by default- disable.

To enable the WDT, the user has to write the sequence 1EH and E1H into WDTRST register with no instruction between the two writes. When the Watchdog Timer is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will generate an output RESET pulse at the RST pin. The RESET pulse duration is  $96xT_{OSC}$ , where  $T_{OSC}=1/f_{OSC}$ . To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset

Note: When the watchdog is enable it is impossible to change its period.

#### Figure 31. Watchdog Timer

## **PCA Interrupt**

Figure 33. PCA Interrupt System

CCON CF CCF1 CCF0 CR 0xD8 PCA Timer/Counter Module 0 Module 1 To Interrupt ECF ECCFn EC ΕA CMOD.0 IEN0.7 IEN0.6 CCAPMn.0

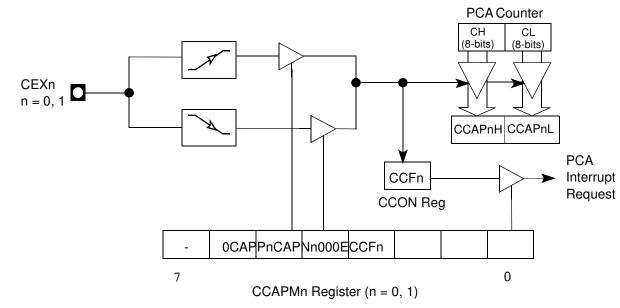

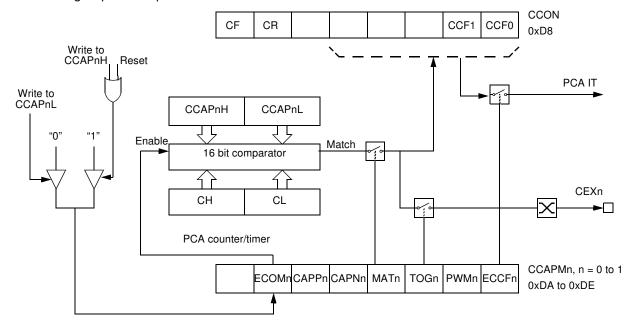

**PCA Capture Mode** To use one of the PCA modules in capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated.

Figure 34. PCA Capture Mode

AT89C5115 🕳

74

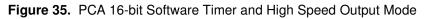

## 16-bit Software Timer Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

## High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set.

Figure 36. PCA High Speed Output Mode

## Pulse Width Modulator Mode

All the PCA modules can be used as PWM outputs. The output frequency depends on the source for the PCA timer. All the modules will have the same output frequency because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than it, the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows the PWM to be updated without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

## Table 57. CCAPMn Registers

CCAPM0 (S:DAh) CCAPM1 (S:DBh) PCA Compare/Capture Module n Mode registers (n=0..1)

| 7        | 6       | 5        | 4                                                                                                                                                                                                                                                                        | 3               | 2                | 1              | 0            |  |

|----------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|----------------|--------------|--|

| -        | ECOMn   | CAPPn    | CAPNn                                                                                                                                                                                                                                                                    | MATn            | TOGn             | PWMn           | ECCFn        |  |

| Bit Numb | ber Bit | Mnemonic | Description                                                                                                                                                                                                                                                              |                 |                  |                |              |  |

| 7        |         | -        | Reserved<br>The Value rea                                                                                                                                                                                                                                                | ad from this bi | it is indetermir | nate. Do not s | et this bit. |  |

| 6        |         | ECOMn    | Enable Compare Mode Module x bit<br>Clear to disable the Compare function.<br>Set to enable the Compare function.<br>The Compare function is used to implement the software Times<br>high-speed output, the Pulse Width Modulator (PWM) and the<br>Watchdog Timer (WDT). |                 |                  |                |              |  |

| 5        |         | CAPPn    | Capture Mode (Positive) Module x bit<br>Clear to disable the Capture function triggered by a positive ed<br>on CEXx pin.<br>Set to enable the Capture function triggered by a positive edge<br>CEXx pin                                                                  |                 |                  |                |              |  |

| 4        |         | CAPNn    | Capture Mode (Negative) Module x bit<br>Clear to disable the Capture function triggered by a negative edge<br>on CEXx pin.<br>Set to enable the Capture function triggered by a negative edge<br>CEXx pin.                                                               |                 |                  |                |              |  |

| 3        |         | MATn     | Match Module x bit<br>Set when a match of the PCA Counter with the Compare/Cap<br>register sets CCFx bit in CCON register, flagging an interrupt.                                                                                                                        |                 |                  |                |              |  |

| 2        |         | TOGn     | Toggle Module x bit           The toggle mode is configured by setting ECOMx, MATx an bits.           Set when a match of the PCA Counter with the Compare/C register toggles the CEXx pin.                                                                              |                 |                  |                |              |  |

| 1        |         | PWMn     | Pulse Width Modulation Module x Mode bit<br>Set to configure the module x as an 8-bit Pulse Width Modula<br>with output waveform on CEXx pin.                                                                                                                            |                 |                  |                | Modulator    |  |

| 0        |         | ECCFn    | Enable CCFx Interrupt bit<br>Clear to disable CCFx bit in CCON register to generate an interrup<br>request.<br>Set to enable CCFx bit in CCON register to generate an interrup<br>request.                                                                               |                 |                  |                |              |  |

Reset Value = X000 0000b

The bits SCH0 to SCH2 in ADCON register are used for the analog input channel selection.

| SCH2 | SCH1 | SCH0 | Selected Analog Input |  |  |  |  |

|------|------|------|-----------------------|--|--|--|--|

| 0    | 0    | 0    | AN0                   |  |  |  |  |

| 0    | 0    | 1    | AN1                   |  |  |  |  |

| 0    | 1    | 0    | AN2                   |  |  |  |  |

| 0    | 1    | 1    | AN3                   |  |  |  |  |

| 1    | 0    | 0    | AN4                   |  |  |  |  |

| 1    | 0    | 1    | AN5                   |  |  |  |  |

| 1    | 1    | 0    | AN6                   |  |  |  |  |

| 1    | 1    | 1    | AN7                   |  |  |  |  |

Table 60.

Selected Analog input

**Voltage Conversion** When the ADCIN is equals to VAREF the ADC converts the signal to 3FFh (full scale). If the input voltage equals VAGND, the ADC converts it to 000h. Input voltage between VAREF and VAGND are a straight-line linear conversion. All other voltages will result in 3FFh if greater than VAREF and 000h if less than VAGND.

Note that ADCIN should not exceed VAREF absolute maximum range (See section "AC-DC").

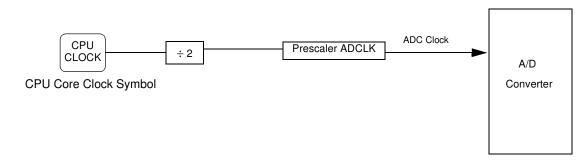

**Clock Selection** The ADC clock is the same as CPU.

The maximum clock frequency is defined in the DC parmeter for A/D converter. A prescaler is featured (ADCCLK) to generate the ADC clock from the oscillator frequency.

if PRS = 0 then  $F_{ADC} = F_{periph} / 64$

if PRS > 0 then  $F_{ADC} = F_{periph} / 2 \times PRS$

Figure 40. A/D Converter Clock

**ADC Standby Mode** When the ADC is not used, it is possible to set it in standby mode by clearing bit ADEN in ADCON register. In this mode the power dissipation is reduced.

## IT ADC management

An interrupt end-of-conversion will occurs when the bit ADEOC is activated and the bit EADC is set. For re-arming the interrupt the bit ADEOC must be cleared by software.

Table 63.ADCLK RegisterADCLK (S:F2h)ADC Clock Prescaler

| 7             | 6               | 5                                                                                            | 4                                                                                    | 3     | 2     | 1     | 0     |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|

| -             | -               | -                                                                                            | PRS 4                                                                                | PRS 3 | PRS 2 | PRS 1 | PRS 0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                  |                                                                                      |       |       |       |       |  |  |

| 7 - 5         | -               | <b>Reserved</b><br>The value rea                                                             | Reserved<br>The value read from these bits are indeterminate. Do not set these bits. |       |       |       |       |  |  |

| 4-0           | PRS4:0          | Clock Prescaler<br>Fadc = Fcpuclock/(4*PRS)) in X1 mode<br>Fadc=Fcpuclock/(2*PRS) in X2 mode |                                                                                      |       |       |       |       |  |  |

Reset Value = XXX0 0000b

**Table 64.** ADDH RegisterADDH (S:F5h Read Only)ADC Data High Byte Register

| 7             | 6               | 5           | 4      | 3      | 2      | 1      | 0      |

|---------------|-----------------|-------------|--------|--------|--------|--------|--------|

| ADAT 9        | ADAT 8          | ADAT 7      | ADAT 6 | ADAT 5 | ADAT 4 | ADAT 3 | ADAT 2 |

| Bit<br>Number | Bit<br>Mnemonic | Description |        |        |        |        |        |

|               |                 |             |        |        |        |        |        |

Reset Value = 00h

**Table 65.** ADDL RegisterADDL (S:F4h Read Only)ADC Data Low Byte Register

| 7             | 6               | 5                         | 4                                                                                    | 3 | 2 | 1      | 0      |  |

|---------------|-----------------|---------------------------|--------------------------------------------------------------------------------------|---|---|--------|--------|--|

| -             | -               | -                         | -                                                                                    | - | - | ADAT 1 | ADAT 0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description               |                                                                                      |   |   |        |        |  |

| 7 - 2         | -               | Reserved<br>The value rea | Reserved<br>The value read from these bits are indeterminate. Do not set these bits. |   |   |        |        |  |

| 1-0           | ADAT1:0         | ADC result<br>bits 1-0    |                                                                                      |   |   |        |        |  |

Reset Value = 00h

**Figure 44.** IEN1 Register IEN1 (S:E8h) Interrupt Enable Register

| 7             | 6               | 5                                | 4                                                                                                   | 3               | 2              | 1            | 0 |  |  |

|---------------|-----------------|----------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|---|--|--|

| -             | -               | -                                | -                                                                                                   | -               | -              | EADC         | - |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                                                                                                     |                 |                |              |   |  |  |

| 7             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                     |                 |                |              |   |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                      | it is indetermi | nate. Do not s | et this bit. |   |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                      | it is indetermi | nate. Do not s | et this bit. |   |  |  |

| 4             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                      | it is indetermi | nate. Do not s | et this bit. |   |  |  |

| 3             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                      | it is indetermi | nate. Do not s | et this bit. |   |  |  |

| 2             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                      | it is indetermi | nate. Do not s | et this bit. |   |  |  |

| 1             | EADC            | Clear to disa                    | ADC Interrupt Enable bit<br>Clear to disable the ADC interrupt.<br>Set to enable the ADC interrupt. |                 |                |              |   |  |  |

| 0             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                      | it is indetermi | nate. Do not s | et this bit. |   |  |  |

Reset Value = xxxx x000b bit addressable

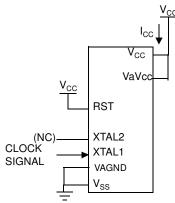

- Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Ports 1, 2 and 3: 15 mA Maximum total I<sub>OL</sub> for all output pins: 71 mA If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 4. Power-down I<sub>CC</sub> is measured with all output pins disconnected; XTAL2 NC.; RST = V<sub>SS</sub> (See Figure 47.).

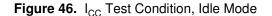

- 5. Idle I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns,  $V_{IL} = V_{SS} + 0.5V$ ,  $V_{IH} = V_{CC} 0.5V$ ; XTAL2 N.C; RST =  $V_{SS}$  (See Figure 46.).

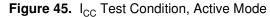

- 6. Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (See Figure 48.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5V, V<sub>IH</sub> = V<sub>CC</sub> 0.5V; XTAL2 N.C.; RST = V<sub>CC</sub>. I<sub>CC</sub> would be slightly higher if a crystal oscillator used (See Figure 45.).

- 7. ICC\_FLASH\_WRITE operating current while a Flash block write is on going.

All other pins are disconnected.

All other pins are disconnected

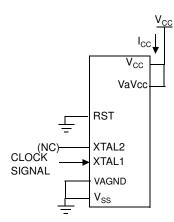

## **Shift Register Timing Waveforms**

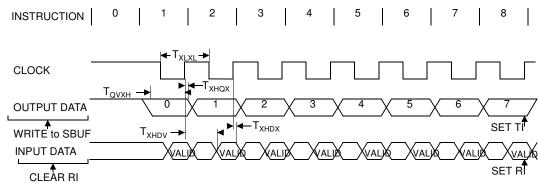

## External Clock Drive Characteristics (XTAL1)

## Table 77. AC Parameters

| Symbol                               | Parameter               | Min | Мах | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 Mode | 40  | 60  | %     |

## External Clock Drive Waveforms

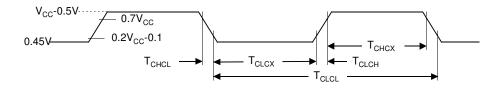

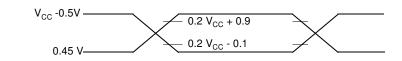

## AC Testing Input/Output Waveforms

INPUT/OUTPUT

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

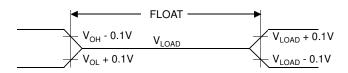

## **Float Waveforms**

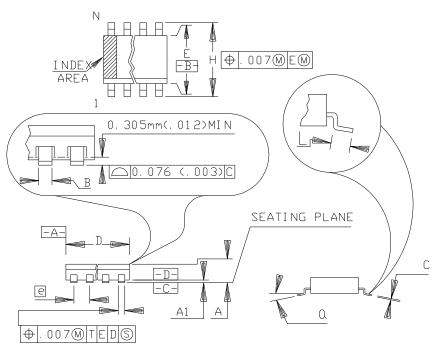

SOIC28

|    | М     | M     | I NCH |       |  |

|----|-------|-------|-------|-------|--|

| A  | 2, 29 | 2.54  | . 090 | . 100 |  |

| A1 | 0.102 | 0.254 | . 004 | . 010 |  |

| В  | 0.38  | 0.51  | .015  | . 020 |  |

| С  | 0.15  | 0.27  | . 006 | .0105 |  |

| D  | 20.83 | 21.08 | . 820 | . 830 |  |

| E  | 10.03 | 10.29 | . 395 | . 405 |  |

| e  | 1.27  | BSC   | . 050 | BSC   |  |

| Н  | 13.49 | 13.84 | . 531 | . 545 |  |

| L  | 0.53  | 1.04  | . 021 | . 041 |  |

| N  | 3     | 2     | 3     | 2     |  |

| ۵  | 0°    | 8°    | 0°    | 8°    |  |

| Features                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                                                                                                                                                                                                                                                                                                                                                     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin Configurations                                                                                                                                                                                                                                                                                                                                                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin Description                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I/O Configurations                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Port Structure                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Read-Modify-Write Instructions                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Quasi Bi-directional Port Operation                                                                                                                                                                                                                                                                                                                                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SFR Mapping                                                                                                                                                                                                                                                                                                                                                                     | . 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Clock                                                                                                                                                                                                                                                                                                                                                                           | . 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |