#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore Processor80C51Core Size8-BitSpeed40MFzConnectivityVART/USARTPropheralsPOR, PWM, WDTNumber of I/O20Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEPROM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersAD 8.10BOperating Type40° ~ 85°C (TA)Monting Type32-GEPPProkage / Case32-GEPP |                            |                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size8-BitSpeed40MHzConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O20Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersAID 8x10bOperating Temperature-40°C ~ 85°C (TA)                                                        | Product Status             | Obsolete                                                                 |

| Speed40MHzConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O20Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                            | Core Processor             | 80C51                                                                    |

| ConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O20Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                      | Core Size                  | 8-Bit                                                                    |

| PeripheralsPOR, PWM, WDTNumber of I/O20Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                            | Speed                      | 40MHz                                                                    |

| Number of I/O20Program Memory Size16KB (16K × 8)Program Memory TypeFLASHEEPROM Size2K × 8RAM Size512 × 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                             | Connectivity               | UART/USART                                                               |

| Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                                            | Peripherals                | POR, PWM, WDT                                                            |

| Program Memory TypeFLASHEEPROM Size2K x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                                                                             | Number of I/O              | 20                                                                       |

| EEPROM Size2K x 8RAM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                                                                                                     | Program Memory Size        | 16KB (16K x 8)                                                           |

| RAM Size512 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                                                                                                                      | Program Memory Type        | FLASH                                                                    |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                                                                                                                                     | EEPROM Size                | 2K x 8                                                                   |

| Data ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                                                                                                                                                                        | RAM Size                   | 512 x 8                                                                  |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface Mount                                                                                                                                                                                                                                                | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount                                                                                                                                                                                                                                                      | Data Converters            | A/D 8x10b                                                                |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                                                            | Oscillator Type            | Internal                                                                 |

|                                                                                                                                                                                                                                                                                                                                        | Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Package / Case 32-LQFP                                                                                                                                                                                                                                                                                                                 | Mounting Type              | Surface Mount                                                            |

|                                                                                                                                                                                                                                                                                                                                        | Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package 32-VQFP (7x7)                                                                                                                                                                                                                                                                                                  | Supplier Device Package    | 32-VQFP (7x7)                                                            |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/t89c5115-ratim                                                                                                                                                                                                                                                  | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c5115-ratim |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Pin Configurations

| VAREF [1<br>VAGND [2<br>VAVCC [3<br>P4.1 [4<br>P4.0 [5<br>P2.1 [6<br>P3.7 [7<br>P3.6 [8<br>P3.5/T1 [9<br>P3.4/T0 [10<br>P3.3/INT1 [11<br>P3.2/INT0 [12<br>P3.1/TxD [13<br>P3.0/RxD [14 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 P1.0/AN0/T2<br>27 P1.1/AN1/T2EX<br>26 P1.2/AN2/ECI<br>25 P1.3/AN3/CEX0<br>24 P1.4/AN4/CEX1<br>23 P1.5/AN5<br>22 P1.6/AN6<br>21 P1.7/AN7<br>20 P2.0<br>19 RESET<br>18 VSS<br>17 VCC<br>16 XTAL1<br>15 XTAL2 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAREF [ 1<br>VAGND ] 2<br>VAVCC ] 3<br>P4.1[ 4<br>P4.0[ 5<br>P3.5/T1 ] 6<br>P3.3/INT1 ] 8<br>P3.2/INT0 ] 9<br>P3.1/TxD ] 10<br>P3.0/RxD ] 11<br>XTAL2 ] 12                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24 P1.0/AN0/T2<br>23 P1.1/AN1/T2EX<br>22 P1.2/AN2/ECI<br>21 P1.3/AN3/CEX0<br>20 P1.4/AN4/CEX1<br>19 P1.5/AN5<br>18 P1.6/AN6<br>17 P1.7/AN7<br>16 RESET<br>15 VSS<br>14 VCC<br>13 XTAL1                        |

| P4.0 5<br>P2.1 6<br>P3.7 7<br>P3.6 8<br>P3.5/T1 9<br>P3.4/T0 10<br>P3.3/INT1 11                                                                                                        | P3.1/TxD [13 P3.1/TxD [13 P3.0/RxD [14 P3.0/RxD [14 P3.0/RxD [14 P3.0/RxD [14 P3.0/RxD [14 P1.0/RND P1 | №         25       P1.3/AN3/CEX0         24       P1.4/AN4/CEX1         23       P1.5/AN5         22       P1.6/AN6         21       P1.7/AN7         20       P2.0         19       RESET                    |

| Clock       | The T89C5115 core needs only 6 clock periods per machine cycle. This feature, called "X2", provides the following advantages:                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | <ul> <li>Divides frequency crystals by 2 (cheaper crystals) while keeping the same CPU<br/>power.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | <ul> <li>Saves power consumption while keeping the same CPU power (oscillator power<br/>saving).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | <ul> <li>Saves power consumption by dividing dynamic operating frequency by 2 in operating and idle modes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | <ul> <li>Increases CPU power by 2 while keeping the same crystal frequency.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | In order to keep the original C51 compatibility, a divider-by-2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by the software.                                                                                                                                                                                                                                                                                                                   |

|             | An extra feature is available to start after Reset in the X2 Mode. This feature can be<br>enabled by a bit X2B in the Hardware Security Byte. This bit is described in the section<br>'In-System Programming'.                                                                                                                                                                                                                                                                                                               |

| Description | The X2 bit in the CKCON register (See Table 11) allows switching from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode).                                                                                                                                                                                                                                                                                                                                |

|             | Setting this bit activates the X2 feature (X2 Mode) for the CPU Clock only (See Figure 3).                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | The Timers 0, 1 and 2, Uart, PCA, or watchdog switch in X2 Mode only if the corre-<br>sponding bit is cleared in the CKCON register.                                                                                                                                                                                                                                                                                                                                                                                         |

|             | The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on the XTAL1 input. In X2 Mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 3. shows the clock generation block diagram. The X2 bit is validated on the XTAL1 $\div$ 2 rising edge to avoid glitches when switching from the X2 to the STD mode. Figure 4 shows the mode switching waveforms. |

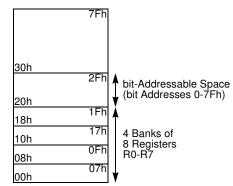

Figure 10. Lower 128 Bytes Internal RAM Organization

- Upper 128 Bytes RAM The upper 128 Bytes of RAM are accessible from address 80h to FFh using only indirect addressing mode.

- **Expanded RAM** The on-chip 256 Bytes of expanded RAM (XRAM) are accessible from address 0000h to 00FFh using indirect addressing mode through MOVX instructions. In this address range.

- Note: Lower 128 Bytes RAM, Upper 128 Bytes RAM, and expanded RAM are made of volatile memory cells. This means that the RAM content is indeterminate after power-up and must then be initialized properly.

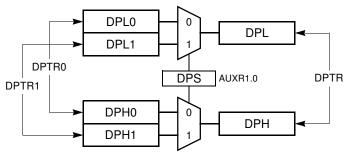

### **Dual Data Pointer**

### Description

The T89C5115 implements a second data pointer for speeding up code execution and reducing code size in case of intensive usage of external memory accesses. DPTR0 and DPTR1 are Seen by the CPU as DPTR and are accessed using the SFR addresses 83h and 84h that are the DPH and DPL addresses. The DPS bit in AUXR1 register (See Figure 18) is used to select whether DPTR is the data pointer 0 or the data pointer 1 (See Figure 11).

Figure 11. Dual Data Pointer Implementation

### Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare...) are well served by using one data pointer as a "source" pointer and the other one as a "destination" pointer. Hereafter is an example of block move implementation using the two pointers and coded in assembler. The latest C compiler takes also advantage of this feature by providing enhanced algorithm libraries.

The INC instruction is a short (2 Bytes) and fast (6 machine cycle) way to manipulate the DPS bit in the AUXR1 register. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is 0 or 1 on entry.

```

; ASCII block move using dual data pointers

; Modifies DPTR0, DPTR1, A and PSW

; Ends when encountering NULL character

; Note: DPS exits opposite to the entry state unless an extra INC AUXR1 is

added

AUXR1EQU0A2h

move:movDPTR, #SOURCE ; address of SOURCE

incAUXR1 ; switch data pointers

movDPTR, #DEST ; address of DEST

mv_loop:incAUXR1; switch data pointers

movxA,@DPTR; get a byte from SOURCE

incDPTR; increment SOURCE address

incAUXR1; switch data pointers

movx@DPTR,A; write the byte to DEST

incDPTR; increment DEST address

jnzmv_loop; check for NULL terminator

```

```

end_move:

```

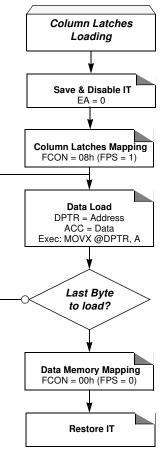

Figure 14. Column Latches Loading Procedure<sup>(1)</sup>

Note: 1. The last page address used when loading the column latch is the one used to select the page programming address.

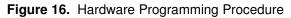

### **Programming the Flash Spaces**

User

The following procedure is used to program the User space and is summarized in Figure 15:

- Load up to one page of data in the column latches from address 0000h to 3FFFh.

- Save then disable the interrupts.

- Launch the programming by writing the data sequence 50h followed by A0h in FCON register. This step must be executed from FM1. The end of the programming indicated by the FBUSY flag cleared.

- Restore the interrupts.

٠

Extra Row

- The following procedure is used to program the Extra Row space and is summarized in Figure 15:

- Load data in the column latches from address FF80h to FFFFh.

- Save then disable the interrupts.

- Launch the programming by writing the data sequence 52h followed by A2h in FCON register. This step of the procedure must be executed from FM1. The end of the programming indicated by the FBUSY flag cleared.

- Restore the interrupts.

<sup>36</sup> **AT89C5115**

### Reading the Flash Spaces

| User                   | <ul> <li>The following procedure is used to read the User space:</li> <li>Read one byte in Accumulator by executing MOVC A,@A+DPTR with A+DPTR is the address of the code byte to read.</li> </ul> |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Note: FCON must be cleared (00h) when not used.                                                                                                                                                    |

| Extra Row              | The following procedure is used to read the Extra Row space and is summarized in Figure 17:                                                                                                        |

|                        | <ul> <li>Map the Extra Row space by writing 02h in FCON register.</li> </ul>                                                                                                                       |

|                        | <ul> <li>Read one byte in Accumulator by executing MOVC A,@A+DPTR with A= 0 &amp;<br/>DPTR= FF80h to FFFFh.</li> </ul>                                                                             |

|                        | Clear FCON to unmap the Extra Row.                                                                                                                                                                 |

| Hardware Security Byte | The following procedure is used to read the Hardware Security Byte and is sum-<br>marized in Figure 17:                                                                                            |

|                        | <ul> <li>Map the Hardware Security space by writing 04h in FCON register.</li> </ul>                                                                                                               |

|                        | <ul> <li>Read the byte in Accumulator by executing MOVC A,@A+DPTR with A= 0 &amp;<br/>DPTR= 0000h.</li> </ul>                                                                                      |

|                        | Clear FCON to unmap the Hardware Security Byte.                                                                                                                                                    |

## **Sharing Instructions**

| Action | RAM | ERAM | EEPROM<br>DATA | Boot<br>FLASH | FM0   | Hardware<br>Byte | XROW  |

|--------|-----|------|----------------|---------------|-------|------------------|-------|

| Read   | MOV | MOVX | MOVX           | MOVC          | MOVC  | MOVC             | MOVC  |

| Write  | MOV | MOVX | MOVX           | -             | by cl | by cl            | by cl |

Note: by cl : using Column Latch

### Table 27. Read MOVX A, @DPTR

| EEE bit in<br>EECON<br>Register | FPS in<br>FCON Register | ENBOOT | ERAM | EEPROM<br>DATA | Flash<br>Column<br>Latch |

|---------------------------------|-------------------------|--------|------|----------------|--------------------------|

| 0                               | 0                       | Х      | ОК   |                |                          |

| 0                               | 1                       | Х      | ОК   |                |                          |

| 1                               | 0                       | Х      |      | ОК             |                          |

| 1                               | 1                       | Х      | ОК   |                |                          |

### Table 28. Write MOVX @DPTR,A

| EEE bit in<br>EECON<br>Register | FPS bit in<br>FCON Register | ENBOOT | ERAM | EEPROM<br>Data | Flash<br>Column<br>Latch |

|---------------------------------|-----------------------------|--------|------|----------------|--------------------------|

| 0                               | 0                           | х      | ОК   |                |                          |

| 0                               | 1                           | х      |      |                | ОК                       |

| 1                               | 0                           | х      |      | ОК             |                          |

| 1                               | 1                           | х      |      |                | ОК                       |

### Hardware Security Byte

Table 31.

Hardware Security byte

| 7             | 6               | 5                                                             | 4                                                                                                                                                            | 3 | 2   | 1   | 0         |

|---------------|-----------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----------|

| X2B           | BLJB            | -                                                             | -                                                                                                                                                            | - | LB2 | LB1 | LB0       |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                   | Description                                                                                                                                                  |   |     |     |           |

| 7             | X2B             |                                                               | X2 bit<br>Set this bit to start in standard mode<br>Clear this bit to start in X2 Mode.                                                                      |   |     |     |           |

| 6             | BLJB            | - 1: To start t                                               | Boot Loader Jump bit<br>- 1: To start the user's application on next RESET (@0000h) located in FM0,<br>- 0: To start the boot loader(@F800h) located in FM1. |   |     |     | d in FM0, |

| 5 - 3         | -               | Reserved<br>The value read from these bits are indeterminate. |                                                                                                                                                              |   |     |     |           |

| 2 - 0         | LB2:0           | Lock bits (se                                                 | ee Table 22)                                                                                                                                                 |   |     |     |           |

After erasing the chip in parallel mode, the default value is : FFh

The erasing in ISP mode (from bootloader) does not modify this byte.

Notes: 1. Only the 4 MSB bits can be accessed by software.

2. The 4 LSB bits can only be accessed by parallel mode.

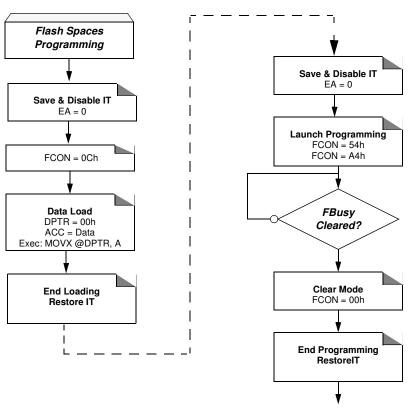

## Serial I/O Port

The T89C5115 I/O serial port is compatible with the I/O serial port in the 80C52. It provides both synchronous and asynchronous communication modes. It operates as a Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- Automatic address recognition

### Figure 20. Serial I/O Port Block Diagram

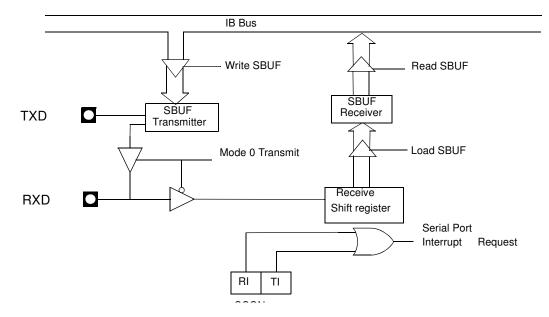

# **Framing Error Detection** Framing bit error detection is provided for the three asynchronous modes. To enable the framing bit error detection feature, set SMOD0 bit in PCON register.

Figure 21. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register bit is set.

The software may examine the FE bit after each reception to check for data errors. Once set, only software or a reset clears the FE bit. Subsequently received frames with valid stop bits cannot clear the FE bit. When the FE feature is enabled, RI rises on the stop bit instead of the last data bit (See Figure 22 and Figure 23).

## Registers

### Table 32. SCON Register

SCON (S:98h) Serial Control Register

| 7             | 6               | 5                                                                                                                                                                                               | 4                                                                                                                                                                           | 3                                              | 2    | 1              | 0  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|----------------|----|

| FE/SM0        | SM1             | SM2                                                                                                                                                                                             | REN                                                                                                                                                                         | TB8                                            | RB8  | TI             | RI |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                     |                                                                                                                                                                             |                                                |      |                |    |

| 7             | FE              | Clear to rese                                                                                                                                                                                   |                                                                                                                                                                             | 00 = 1)<br>ite, not cleared<br>invalid stop bi |      | op bit.        |    |

|               | SM0             |                                                                                                                                                                                                 | <b>Iode bit 0 (S</b><br>I for serial por                                                                                                                                    | MOD0 = 0)<br>rt mode select                    | ion. |                |    |

| 6             | SM1             | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                          |                                                                                                                                                                             |                                                |      |                |    |

| 5             | SM2             | Serial port Mode 2 bit/Multiprocessor Communication Enable bit<br>Clear to disable multiprocessor communication feature.<br>Set to enable multiprocessor communication feature in mode 2 and 3. |                                                                                                                                                                             |                                                |      |                |    |

| 4             | REN             | Reception Enable bit<br>Clear to disable serial reception.<br>Set to enable serial reception.                                                                                                   |                                                                                                                                                                             |                                                |      |                |    |

| 3             | TB8             | Transmitter bit 8/Ninth bit to Transmit in Modes 2 and 3<br>Clear to transmit a logic 0 in the 9th bit.<br>Set to transmit a logic 1 in the 9th bit.                                            |                                                                                                                                                                             |                                                |      |                |    |

| 2             | RB8             | <b>Receiver bit 8/Ninth bit Received in Modes 2 and 3</b><br>Cleared by hardware if 9th bit received is a logic 0.<br>Set by hardware if 9th bit received is a logic 1.                         |                                                                                                                                                                             |                                                |      |                |    |

| 1             | ті              | <b>Transmit Interrupt Flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning o<br>stop bit in the other modes.             |                                                                                                                                                                             |                                                |      | ginning of the |    |

| 0             | RI              | Clear to ackr<br>Set by hardw                                                                                                                                                                   | Receive Interrupt Flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0, See Figure 22. and<br>Figure 23. in the other modes. |                                                |      |                |    |

Reset Value = 0000 0000b bit addressable

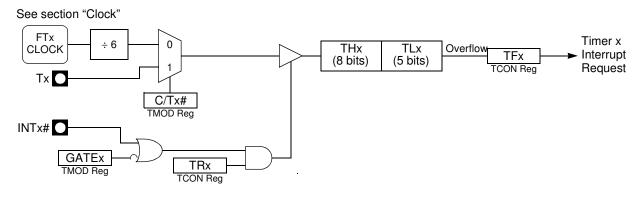

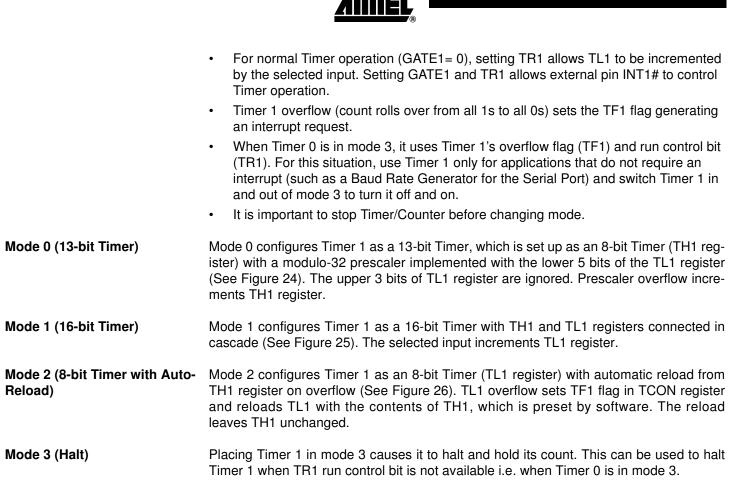

### Mode 0 (13-bit Timer)

Mode 0 configures Timer 0 as an 13-bit Timer which is set up as an 8-bit Timer (TH0 register) with a modulo 32 prescaler implemented with the lower five bits of TL0 register (See Figure 24). The upper three bits of TL0 register are indeterminate and should be ignored. Prescaler overflow increments TH0 register.

Figure 24. Timer/Counter x (x= 0 or 1) in Mode 0

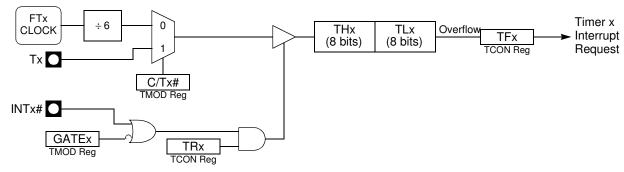

### Mode 1 (16-bit Timer)

Mode 1 configures Timer 0 as a 16-bit Timer with TH0 and TL0 registers connected in cascade (See Figure 25). The selected input increments TL0 register.

Figure 25. Timer/Counter x (x= 0 or 1) in Mode 1 See section "Clock"

**Mode 2 (8-bit Timer with Auto-Reload)** Mode 2 configures Timer 0 as an 8-bit Timer (TL0 register) that automatically reloads from TH0 register (See Figure 26). TL0 overflow sets TF0 flag in TCON register and reloads TL0 with the contents of TH0, which is preset by software. When the interrupt request is serviced, hardware clears TF0. The reload leaves TH0 unchanged. The next reload value may be changed at any time by writing it to TH0 register.

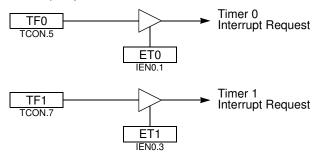

Interrupt Each Timer handles one interrupt source that is the timer overflow flag TF0 or TF1. This flag is set every time an overflow occurs. Flags are cleared when vectoring to the Timer interrupt routine. Interrupts are enabled by setting ETx bit in IEN0 register. This assumes interrupts are globally enabled by setting EA bit in IEN0 register.

Figure 28. Timer Interrupt System

# **Table 38.** TMOD RegisterTMOD (S:89h)

Timer/Counter Mode Control Register

| 7     | 6     | 5   | 4   | 3     | 2     | 1   | 0   |

|-------|-------|-----|-----|-------|-------|-----|-----|

| GATE1 | C/T1# | M11 | M01 | GATE0 | C/T0# | M10 | M00 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | GATE1           | <b>Timer 1 Gating Control bit</b><br>Clear to enable Timer 1 whenever TR1 bit is set.<br>Set to enable Timer 1 only while INT1# pin is high and TR1 bit is set.                                                                                                                                                            |

| 6             | C/T1#           | <b>Timer 1 Counter/Timer Select bit</b><br>Clear for Timer operation: Timer 1 counts the divided-down system clock.<br>Set for Counter operation: Timer 1 counts negative transitions on external pin T1.                                                                                                                  |

| 5             | M11             | Timer 1 Mode Select bits                                                                                                                                                                                                                                                                                                   |

| 4             | M01             | M11       M01       Operating mode         0       Mode 0: 8-bit Timer/Counter (TH1) with 5bit prescaler (TL1).         0       1       Mode 1: 16-bit Timer/Counter.         1       1       Mode 3: Timer 1 halted. Retains count.         1       0       Mode 2: 8-bit auto-reload Timer/Counter (TL1). <sup>(1)</sup> |

| 3             | GATE0           | <b>Timer 0 Gating Control bit</b><br>Clear to enable Timer 0 whenever TR0 bit is set.<br>Set to enable Timer/Counter 0 only while INT0# pin is high and TR0 bit is set.                                                                                                                                                    |

| 2             | C/T0#           | <b>Timer 0 Counter/Timer Select bit</b><br>Clear for Timer operation: Timer 0 counts the divided-down system clock.<br>Set for Counter operation: Timer 0 counts negative transitions on external pin T0.                                                                                                                  |

| 1             | M10             | Timer 0 Mode Select bit         M10 M00 Operating mode         0       0         Mode 0: 8-bit Timer/Counter (TH0) with 5bit prescaler (TL0).         0       1         Mode 0: 4-0 bit Timer/Counter                                                                                                                      |

| 0             | M00             | <ul> <li>Mode 1: 16-bit Timer/Counter.</li> <li>Mode 2: 8-bit auto-reload Timer/Counter (TL0).<sup>(2)</sup></li> <li>Mode 3: TL0 is an 8-bit Timer/Counter.</li> <li>TH0 is an 8-bit Timer using Timer 1's TR0 and TF0 bits.</li> </ul>                                                                                   |

Reset Value = 0000 0000b

Notes: 1. Reloaded from TH1 at overflow.

2. Reloaded from TH0 at overflow.

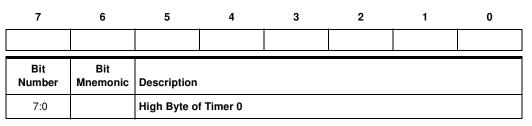

**Table 39.** TH0 RegisterTH0 (S:8Ch)Timer 0 High Byte Register

Reset Value = 0000 0000b

| Timer 2          | The T89C5115 Timer 2 is compatible with Timer 2 in the 80C52.                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | It is a 16-bit timer/counter: the count is maintained by two eightbit timer registers, TH2 and TL2 that are cascade-connected. It is controlled by T2CON register (See Table 44) and T2MOD register (See Table 45). Timer 2 operation is similar to Timer 0 and Timer 1. $C/T2$ selects $F_{T2 clock}/6$ (timer operation) or external pin T2 (counter operation) as timer clock. Setting TR2 allows TL2 to be incremented by the selected input. |

|                  | Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  | Auto-reload mode (up or down counter)                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                         |

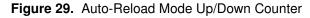

| Auto-Reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. This feature is controlled by the DCEN bit in T2MOD register (See Table<br>44). Setting the DCEN bit enables Timer 2 to count up or down as shown in Figure 29. In<br>this mode the T2EX pin controls the counting direction.                                                                                                              |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                      |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                   |

The EXF2 bit toggles when Timer 2 overflow or underflow, depending on the direction of the count. EXF2 does not generate an interrupt. This bit can be used to provide 17-bit resolution.

62

## Registers

**Table 43.** T2CON RegisterT2CON (S:C8h)Timer 2 Control Register

| 7             | 6               | 5                                                                                                                                                                                                                                           | 4                                                                                                                                                                                                                                                  | 3                                                                | 2             | 1                        | 0       |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|--------------------------|---------|

| TF2           | EXF2            | RCLK                                                                                                                                                                                                                                        | TCLK                                                                                                                                                                                                                                               | EXEN2                                                            | TR2           | C/T2#                    | CP/RL2# |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                    |                                                                  |               |                          |         |

| 7             | TF2             | Must be clea                                                                                                                                                                                                                                | rflow Flag<br>ti if RCLK=1 c<br>red by softwa<br>vare on Timer                                                                                                                                                                                     | re.                                                              |               |                          |         |

| 6             | EXF2            | Set when a c<br>EXEN2=1.<br>Set to cause<br>interrupt is en                                                                                                                                                                                 | Timer 2 External Flag<br>Set when a capture or a reload is caused by a negative transition on T2E<br>EXEN2=1.<br>Set to cause the CPU to vector to Timer 2 interrupt routine when Timer 2<br>interrupt is enabled.<br>Must be cleared by software. |                                                                  |               |                          |         |

| 5             | RCLK            | Clear to use                                                                                                                                                                                                                                | Receive Clock bit<br>Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                |                                                                  |               |                          |         |

| 4             | TCLK            | <b>Transmit Clock bit</b><br>Clear to use timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                               |                                                                                                                                                                                                                                                    |                                                                  |               |                          |         |

| 3             | EXEN2           | <b>Timer 2 External Enable bit</b><br>Clear to ignore events on T2EX pin for Timer 2 operation.<br>Set to cause a capture or reload when a negative transition on T2EX pin is<br>detected, if Timer 2 is not used to clock the serial port. |                                                                                                                                                                                                                                                    |                                                                  |               | X pin is                 |         |

| 2             | TR2             | Timer 2 Run<br>Clear to turn<br>Set to turn or                                                                                                                                                                                              | off Timer 2.                                                                                                                                                                                                                                       |                                                                  |               |                          |         |

| 1             | C/T2#           | Clear for time                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                    | <b>it</b><br>nput from inte<br>input from T2                     |               | tem: f <sub>OSC</sub> ). |         |

| 0             | CP/RL2#         | If RCLK=1 or<br>Timer 2 over<br>Clear to auto<br>EXEN2=1.                                                                                                                                                                                   | flow.<br>-reload on Tir                                                                                                                                                                                                                            | <b>bit</b><br>/RL2# is ignor<br>ner 2 overflow<br>transitions or | s or negative | transitions on           |         |

Reset Value = 0000 0000b bit addressable

**Table 52.**WDTRST RegisterWDTRST (S:A6h Write Only) – Watchdog Timer Enable register

| 7             | 6               | 5           | 4            | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|--------------|---|---|---|---|

| -             | -               | -           | -            | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |              |   |   |   |   |

| 7             | -               | Watchdog Co | ontrol Value |   |   |   |   |

Reset Value = 1111 1111b

Note: The WDRST register is used to reset/enable the WDT by writing 1EH then E1H in sequence without instruction between these two sequences.

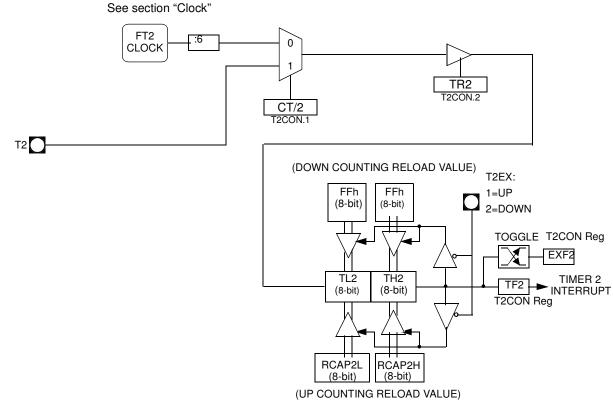

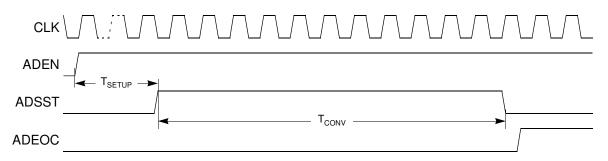

### Figure 38. ADC Description

Figure 39 shows the timing diagram of a complete conversion. For simplicity, the figure depicts the waveforms in idealized form and do not provide precise timing information. For ADC characteristics and timing parameters refer to the section "AC Characteristics" of this datasheet.

### Figure 39. Timing Diagram

Note: Tsetup min, see the AC Parameter for A/D conversion.

Tconv = 11 clock ADC = 1 sample and hold + 10-bit conversion

The user must ensure that Tsetup time between setting ADEN and the start of the first conversion.

### ADC Converter Operation

A start of single A/D conversion is triggered by setting bit ADSST (ADCON.3).

After completion of the A/D conversion, the ADSST bit is cleared by hardware.

The end-of-conversion flag ADEOC (ADCON.4) is set when the value of conversion is available in ADDH and ADDL, it must be cleared by software. If the bit EADC (IEN1.1) is set, an interrupt occur when flag ADEOC is set (See Figure 41). Clear this flag for rearming the interrupt.

Note: Always leave Tsetup time before starting a conversion unless ADEN is permanently high. In this case one should wait Tsetup only before the first conversion

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs. I<sub>OL</sub>/I<sub>OH</sub>  $\geq \pm$  20mA.

**Clock Waveforms** Valid in normal clock mode. In X2 Mode XTAL2 must be changed to XTAL2/2.

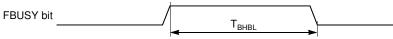

### Flash/EEPROM Memory

Table 78. Memory AC Timing

$V_{cc}$  = 3.0V to 5.5V,  $T_A$  = -40°C to +85°C

| Symbol            | Parameter                                        | Min     | Тур | Max | Unit   |

|-------------------|--------------------------------------------------|---------|-----|-----|--------|

| T <sub>BHBL</sub> | Flash/EEPROM Internal Busy<br>(Programming) Time |         | 13  | 17  | ms     |

| N <sub>FCY</sub>  | Number of Flash/EEPROM Erase/Write Cycles        | 100 000 |     |     | cycles |

| T <sub>FDR</sub>  | Flash/EEPROM Data Retention Time                 | 10      |     |     | years  |

Figure 49. Flash Memory - Internal Busy Waveforms

### A/D Converter

Table 79. AC Parameters for A/D Conversion

| Symbol              | Parameter | Min | Тур | Max | Unit |

|---------------------|-----------|-----|-----|-----|------|

| T <sub>SETUP</sub>  |           | 4   |     |     | μs   |

| ADC Clock Frequency |           |     | 700 |     | KHz  |

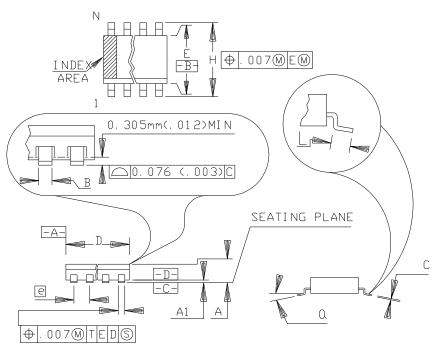

SOIC28

|    | М     | M     | ΙN    | СН    |

|----|-------|-------|-------|-------|

| A  | 2, 29 | 2.54  | . 090 | . 100 |

| A1 | 0.102 | 0.254 | . 004 | . 010 |

| В  | 0.38  | 0.51  | .015  | . 020 |

| С  | 0.15  | 0.27  | . 006 | .0105 |

| D  | 20.83 | 21.08 | . 820 | . 830 |

| E  | 10.03 | 10.29 | . 395 | . 405 |

| e  | 1.27  | BSC   | . 050 | BSC   |

| Н  | 13.49 | 13.84 | . 531 | . 545 |

| L  | 0.53  | 1.04  | . 021 | . 041 |

| N  | 32    |       | 3     | 2     |

| ۵  | 0°    | 8°    | 0°    | 8°    |

## Datasheet Revision History for T89C5115

| Changes from 4128A-<br>01/03 to 4128B-06/03    | 1.<br>2.       | Changed the endurance of Flash to 100, 000 Write/Erase cycles.<br>Added note on Flash retention formula for V <sub>IH1</sub> , in Section "Electrical Character-<br>istics", page 97.                                                  |

|------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changes from 4128B-<br>06/03 to 4128C-12/03    | 1.<br>2.<br>3. | Changed value of IPDMAX to 400, Section "Electrical Characteristics", page 97.<br>PCA, CPS0, register correction, Section "PCA Registers", page 78.<br>Cross Memory section added Section "Operation Cross Memory Access",<br>page 42. |

| Changes from 4128C -<br>12/03 to 4128D - 01/05 | 1.             | Various minor corrections throughout the document.                                                                                                                                                                                     |

| Changes from 4128D -<br>01/05 to 4128E - 10/05 | 1.             | Added green product ordering information.                                                                                                                                                                                              |

| Changes from 4128E -<br>10/05 to 4182F - 06/05 | 1.             | Minor corrections throughout the document.                                                                                                                                                                                             |

| Changes from 4182F -<br>06/05 to 4182G - 01/08 | 1.             | Removed non-green part numbers from ordering information.                                                                                                                                                                              |