Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 2K x 8                                                                   |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SO                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c5115-tisim |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Pin Configurations

| VAREF [1<br>VAGND [2<br>VAVCC [3<br>P4.1 [4<br>P4.0 [5<br>P2.1 [6<br>P3.7 [7<br>P3.6 [8<br>P3.5/T1 [9<br>P3.4/T0 [10<br>P3.3/INT1 [11<br>P3.2/INT0 [12<br>P3.1/TxD [13<br>P3.0/RxD [14 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 P1.0/AN0/T2<br>27 P1.1/AN1/T2EX<br>26 P1.2/AN2/ECI<br>25 P1.3/AN3/CEX0<br>24 P1.4/AN4/CEX1<br>23 P1.5/AN5<br>22 P1.6/AN6<br>21 P1.7/AN7<br>20 P2.0<br>19 RESET<br>18 VSS<br>17 VCC<br>16 XTAL1<br>15 XTAL2 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAREF [ 1<br>VAGND ] 2<br>VAVCC ] 3<br>P4.1[ 4<br>P4.0[ 5<br>P3.5/T1 ] 6<br>P3.3/INT1 ] 8<br>P3.2/INT0 ] 9<br>P3.1/TxD ] 10<br>P3.0/RxD ] 11<br>XTAL2 ] 12                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24 P1.0/AN0/T2<br>23 P1.1/AN1/T2EX<br>22 P1.2/AN2/ECI<br>21 P1.3/AN3/CEX0<br>20 P1.4/AN4/CEX1<br>19 P1.5/AN5<br>18 P1.6/AN6<br>17 P1.7/AN7<br>16 RESET<br>15 VSS<br>14 VCC<br>13 XTAL1                        |

| P4.0 5<br>P2.1 6<br>P3.7 7<br>P3.6 8<br>P3.5/T1 9<br>P3.4/T0 10<br>P3.3/INT1 11                                                                                                        | P3.1/TxD [13 P3.1/TxD [13 P3.0/RxD [14 P3.0/RxD [14 P3.0/RxD [14 P3.0/RxD [14 P3.0/RxD [14 P1.0/RND P1 | №         25       P1.3/AN3/CEX0         24       P1.4/AN4/CEX1         23       P1.5/AN5         22       P1.6/AN6         21       P1.7/AN7         20       P2.0         19       RESET                    |

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0:7   | I/O  | Port 3:         Is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1's written to them are pulled high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 3 pins that are being pulled low externally will be a source of current (I <sub>IL</sub> , See section 'Electrical Characteristic') because of the internal pull-ups.         The output latch corresponding to a secondary function must be programmed to one for that function to operate (except for TxD and WR). The secondary functions are assigned to the pins of port 3 as follows: P3.0/RxD: Receiver data input (asynchronous) or data input/output (synchronous) of the serial interface P3.1/TxD: Transmitter data output (asynchronous) or clock output (synchronous) of the serial interface P3.2/INT0: External interrupt 0 input/timer 0 gate control input P3.3/INT1: External interrupt 1 input/timer 1 gate control input P3.4/T0: Timer 1 counter input P3.5/T1: Timer 1 counter input P3.6: Regular I/O port pin P3.7: Regular I/O port pin |

| P4.0:1   | I/O  | Port 4:<br>Is an 2-bit bi-directional I/O port with internal pull-ups. Port 4 pins that have 1's written to them are pulled<br>high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 4 pins that are being<br>pulled low externally will be a source of current (IIL, on the datasheet) because of the internal pull-up<br>transistor.<br>P4.0:<br>P4.1:<br>It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET    | I/O  | <b>Reset:</b><br>A high level on this pin during two machine cycles while the oscillator is running resets the device. An internal pull-down resistor to VSS permits power-on reset using only an external capacitor to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTAL1    | I    | <b>XTAL1:</b><br>Input of the inverting oscillator amplifier and input of the internal clock generator circuits. To drive the device from an external clock source, XTAL1 should be driven, while XTAL2 is left unconnected. To operate above a frequency of 16 MHz, a duty cycle of 50% should be maintained.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| XTAL2    | 0    | <b>XTAL2:</b><br>Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

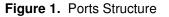

#### I/O Configurations

Each Port SFR operates via type-D latches, as illustrated in Figure 1 for Ports 3 and 4. A CPU 'write to latch' signal initiates transfer of internal bus data into the type-D latch. A CPU 'read latch' signal transfers the latched Q output onto the internal bus. Similarly, a 'read pin' signal transfers the logical level of the Port pin. Some Port data instructions activate the 'read latch' signal while others activate the 'read pin' signal. Latch instructions are referred to as Read-Modify-Write instructions. Each I/O line may be independently programmed as input or output.

**Port Structure** Figure 1 shows the structure of Ports, which have internal pull-ups. An external source can pull the pin low. Each Port pin can be configured either for general-purpose I/O or for its alternate input output function.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 1 to 4). To use a pin for general-purpose input, set the bit in the Px register. This turns off the output FET drive.

To configure a pin for its alternate function, set the bit in the Px register. When the latch is set, the 'alternate output function' signal controls the output level (See Figure 1). The operation of Ports is discussed further in 'Quasi-Bi-directional Port Operation' paragraph.

Note: 1. The internal pull-up can be disabled on P1 when analog function is selected.

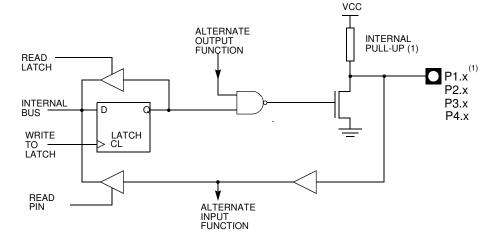

associated nFET is switched off. This is traditional CMOS switch convention. Current strengths are 1/10 that of pFET #3.

Note: During Reset, pFET#1 is not avtivated. During Reset, only the weak pFET#3 pull up the pin.

# **Table 18.** AUXR1 RegisterAUXR1 (S:A2h)Auxiliary Control Register 1

| 7             | 6                     | 5                                | 4                                                                                                                     | 3                                  | 2              | 1            | 0   |  |

|---------------|-----------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|--------------|-----|--|

| -             | -                     | ENBOOT                           | -                                                                                                                     | GF3                                | 0              | -            | DPS |  |

| Bit<br>Number | Bit<br>Mnemonic       | Description                      |                                                                                                                       |                                    |                |              |     |  |

| 7 - 6         | -                     | <b>Reserved</b><br>The value rea | <b>deserved</b><br>he value read from these bits is indeterminate. Do not set these bits.                             |                                    |                |              |     |  |

| 5             | ENBOOT <sup>(1)</sup> | Set this bit to                  | Enable Boot Flash<br>Set this bit to map the boot Flash between F800h -FFFFh<br>Clear this bit to disable boot Flash. |                                    |                |              |     |  |

| 4             | -                     | <b>Reserved</b><br>The value rea | ad from this b                                                                                                        | it is indetermi                    | nate. Do not s | et this bit. |     |  |

| 3             | GF3                   | General Pur                      | pose Flag 3                                                                                                           |                                    |                |              |     |  |

| 2             | 0                     |                                  | Always Zero<br>This bit is stuck to logic 0 to allow INC AUXR1 instruction without affecting GF3<br>flag.             |                                    |                |              |     |  |

| 1             | -                     | Reserved fo                      | Reserved for Data Pointer Extension                                                                                   |                                    |                |              |     |  |

| 0             | DPS                   |                                  | second dual                                                                                                           | data pointer: D<br>ata pointer: DF |                |              |     |  |

Reset Value = XXXX 00X0b

Note: 1. ENBOOT is initialized with the invert BLJB at reset. See In-System Programming section.

| EEPROM Data<br>Memory               | The 2K bytes on-chip EEPROM memory block is located at addresses 0000h to 07FFh of the XRAM/XRAM memory space and is selected by setting control bits in the EECON register. A read in the EEPROM memory is done with a MOVX instruction.                                                                                                                                                                                                                                                       |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | A physical write in the EEPROM memory is done in two steps: write data in the column latches and transfer of all data latches into an EEPROM memory row (programming).                                                                                                                                                                                                                                                                                                                          |

|                                     | The number of data written on the page may vary from 1 up to 128 Bytes (the page size). When programming, only the data written in the column latch is programmed and a ninth bit is used to obtain this feature. This provides the capability to program the whole memory by Bytes, by page or by a number of Bytes in a page. Indeed, each ninth bit is set when the writing the corresponding byte in a row and all these ninth bits are reset after the writing of the complete EEPROM row. |

| Write Data in the Column<br>Latches | Data is written by byte to the column latches as for an external RAM memory. Out of the 11 address bits of the data pointer, the 4 MSBs are used for page selection (row) and 7 are used for byte selection. Between two EEPROM programming sessions, all the addresses in the column latches must stay on the same page, meaning that the 4 MSB must no be changed.                                                                                                                            |

|                                     | The following procedure is used to write to the column latches:                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                     | Save and disable interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     | Set bit EEE of EECON register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | Load DPTR with the address to write                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                     | Store A register with the data to be written                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                     | Execute a MOVX @DPTR, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | If needed loop the three last instructions until the end of a 128 Bytes page                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                     | Restore interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                     | Note: The last page address used when loading the column latch is the one used to select the page programming address.                                                                                                                                                                                                                                                                                                                                                                          |

| Programming                         | The EEPROM programming consists of the following actions:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                     | • Write one or more Bytes of one page in the column latches. Normally, all Bytes must belong to the same page; if not, the last page address will be latched and the others discarded.                                                                                                                                                                                                                                                                                                          |

|                                     | <ul> <li>Launch programming by writing the control sequence (50h followed by A0h) to the<br/>EECON register.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | • EEBUSY flag in EECON is then set by hardware to indicate that programming is in progress and that the EEPROM segment is not available for reading.                                                                                                                                                                                                                                                                                                                                            |

|                                     | • The end of programming is indicated by a hardware clear of the EEBUSY flag.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | Note: The sequence 5xh and Axh must be executed without instructions between then other-<br>wise the programming is aborted.                                                                                                                                                                                                                                                                                                                                                                    |

| Read Data                           | The following procedure is used to read the data stored in the EEPROM memory:                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | Save and disable interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     | Set bit EEE of EECON register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | Load DPTR with the address to read                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                     | Execute a MOVX A, @DPTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | Restore interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Registers

Table 19.EECON RegisterEECON (S:0D2h)EEPROM Control Register

| 7          | 6               | 5                              | 4                                                                                                                                                            | 3                                                           | 2           | 1          | 0      |  |

|------------|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------|------------|--------|--|

| EEPL3      | EEPL2           | EEPL1                          | EEPL0                                                                                                                                                        | -                                                           | -           | EEE        | EEBUSY |  |

| Bit Number | Bit<br>Mnemonic | Descriptio                     | n                                                                                                                                                            |                                                             |             |            |        |  |

| 7 - 4      | EEPL3-0         | U U                            | •                                                                                                                                                            | Command bit<br>Kh to EEPL to                                |             | ogramming. |        |  |

| 3          | -               | <b>Reserved</b><br>The value r | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                              |                                                             |             |            |        |  |

| 2          | -               | <b>Reserved</b><br>The value r | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                              |                                                             |             |            |        |  |

| 1          | EEE             | Set to map<br>latches)         | Enable EEPROM Space bit<br>Set to map the EEPROM space during MOVX instructions (Write in the column<br>latches)<br>Clear to map the XRAM space during MOVX. |                                                             |             |            |        |  |

| 0          | EEBUSY          | Set by hard<br>Cleared by      | hardware wh                                                                                                                                                  | <b>g</b><br>rogramming is<br>en programmi<br>d by software. | ng is done. |            |        |  |

Reset Value = XXXX XX00b Not bit addressable

#### **XROW Bytes** The EXTRA ROW (XROW) includes 128 bytes. Some of these bytes are used for specific purpose in conjonction with the bootloader.

| Table 30. | XROW | Mapping |

|-----------|------|---------|

|-----------|------|---------|

| Description                                     | Default Value | Address |

|-------------------------------------------------|---------------|---------|

| Copy of the Manufacturer Code                   | 58h           | 30h     |

| Copy of the Device ID#1: Family code            | D7h           | 31h     |

| Copy of the Device ID#2: Memories size and type | BBh           | 60h     |

| Copy of the Device ID#3: Name and Revision      | FFh           | 61h     |

# **Hardware Conditions** It is possible to force the controller to execute the bootloader after a Reset with hardware conditions.

During the first programming, the user can define a configuration on Port1 that will be recognized by the chip as the hardware conditions during a Reset. If this condition is met, the chip will start executing the bootloader at the end of the Reset.

See a detailed description in the applicable Document.

- Datasheet Bootloader UART T89C5115.

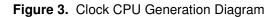

| Timers/Counters             | The T89C5115 implements two general-purpose, 16-bit Timers/Counters. Such are identified as Timer 0 and Timer 1, and can be independently configured to operate in a variety of modes as a Timer or an event Counter. When operating as a Timer, the Timer/Counter runs for a programmed length of time, then issues an interrupt request. When operating as a Counter, the Timer/Counter counts negative transitions on an external pin. After a preset number of counts, the Counter issues an interrupt request. The various operating modes of each Timer/Counter are described in the following sections.                                                                          |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer/Counter<br>Operations | A basic operation is Timer registers THx and TLx ( $x = 0, 1$ ) connected in cascade to form a 16-bit Timer. Setting the run control bit (TRx) in TCON register (See Figure 37) turns the Timer on by allowing the selected input to increment TLx. When TLx overflows it increments THx; when THx overflows it sets the Timer overflow flag (TFx) in TCON register. Setting the TRx does not clear the THx and TLx Timer registers. Timer registers can be accessed to obtain the current count or to enter preset values. They can be read at any time but TRx bit must be cleared to preset their values, otherwise the behavior of the Timer/Counter is unpredictable.              |

|                             | The C/Tx# control bit selects Timer operation or Counter operation by selecting the divided-down peripheral clock or external pin Tx as the source for the counted signal. TRx bit must be cleared when changing the mode of operation, otherwise the behavior of the Timer/Counter is unpredictable. For Timer operation (C/Tx# = 0), the Timer register counts the divided-down peripheral clock. The Timer register is incremented once every peripheral cycle (6 peripheral clock periods). The Timer clock rate is $f_{PER}/6$ , i.e. $f_{OSC}/12$ in standard mode or $f_{OSC}/6$ in X2 Mode.                                                                                     |

|                             | For Counter operation (C/Tx# = 1), the Timer register counts the negative transitions on the Tx external input pin. The external input is sampled every peripheral cycles. When the sample is high in one cycle and low in the next one, the Counter is incremented. Since it takes 2 cycles (12 peripheral clock periods) to recognize a negative transition, the maximum count rate is $f_{PER}/12$ , i.e. $f_{OSC}/24$ in standard mode or $f_{OSC}/12$ in X2 Mode. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full peripheral cycle. |

| Timer 0                     | Timer 0 functions as either a Timer or event Counter in four modes of operation.<br>Figure 24 through Figure 27 show the logical configuration of each mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                             | Timer 0 is controlled by the four lower bits of TMOD register (See Figure 38) and bits 0, 1, 4 and 5 of TCON register (See Figure 37). TMOD register selects the method of Timer gating (GATE0), Timer or Counter operation (T/C0#) and mode of operation (M10 and M00). TCON register provides Timer 0 control functions: overflow flag (TF0), run control bit (TR0), interrupt flag (IE0) and interrupt type control bit (IT0). For normal Timer operation (GATE0 = 0), setting TR0 allows TL0 to be incremented by the selected input. Setting GATE0 and TR0 allows external pin INT0# to control Timer operation.                                                                   |

|                             | Timer 0 overflow (count rolls over from all 1s to all 0s) sets TF0 flag generating an inter-<br>rupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                             | It is important to stop Timer/Counter before changing mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

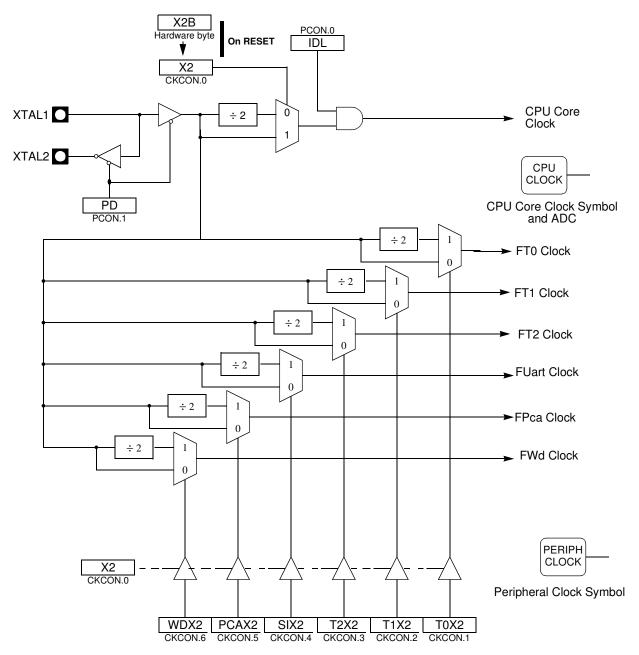

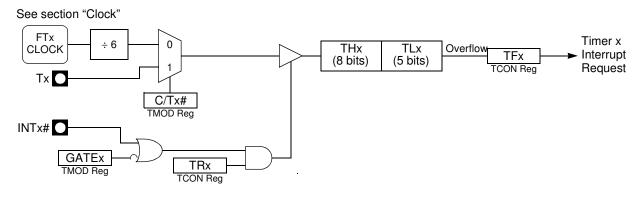

#### Mode 0 (13-bit Timer)

Mode 0 configures Timer 0 as an 13-bit Timer which is set up as an 8-bit Timer (TH0 register) with a modulo 32 prescaler implemented with the lower five bits of TL0 register (See Figure 24). The upper three bits of TL0 register are indeterminate and should be ignored. Prescaler overflow increments TH0 register.

Figure 24. Timer/Counter x (x= 0 or 1) in Mode 0

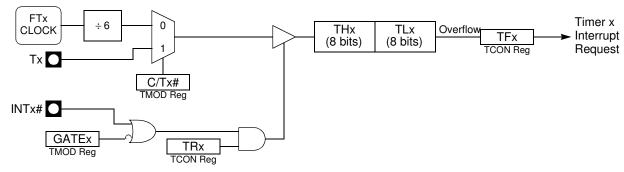

#### Mode 1 (16-bit Timer)

Mode 1 configures Timer 0 as a 16-bit Timer with TH0 and TL0 registers connected in cascade (See Figure 25). The selected input increments TL0 register.

Figure 25. Timer/Counter x (x= 0 or 1) in Mode 1 See section "Clock"

**Mode 2 (8-bit Timer with Auto-Reload)** Mode 2 configures Timer 0 as an 8-bit Timer (TL0 register) that automatically reloads from TH0 register (See Figure 26). TL0 overflow sets TF0 flag in TCON register and reloads TL0 with the contents of TH0, which is preset by software. When the interrupt request is serviced, hardware clears TF0. The reload leaves TH0 unchanged. The next reload value may be changed at any time by writing it to TH0 register.

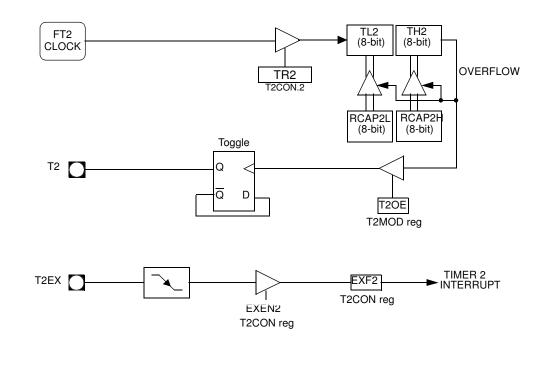

#### Programmable Clock-Output

In clock-out mode, Timer 2 operates as a 50%-duty-cycle, programmable clock generator (Figure 30). The input clock increments TL2 at frequency  $f_{OSC}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency depending on the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$Clock - OutFrequency = \frac{FT2clock}{4 \times (65536 - RCAP2H/RCAP2L)}$

For a 16 MHz system clock in x1 mode, Timer 2 has a programmable frequency range of 61 Hz ( $f_{OSC}/2^{16}$ ) to 4 MHz ( $f_{OSC}/4$ ). The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or different depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

#### Figure 30. Clock-Out Mode

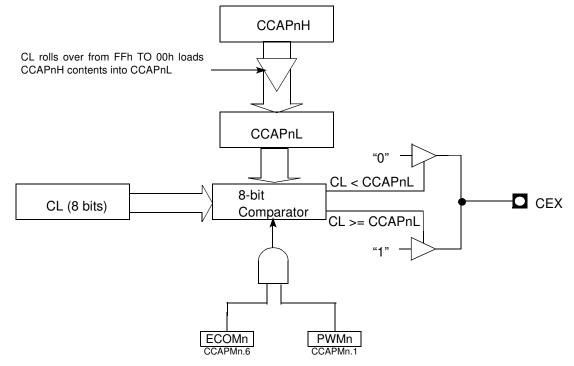

#### Figure 37. PCA PWM Mode

#### Registers

Figure 43. IEN0 Register IEN0 (S:A8h) Interrupt Enable Register

| 7             | 6               | 5                                               | 4                                                                                                                                                                                                               | 3           | 2   | 1   | 0   |  |  |

|---------------|-----------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|-----|-----|--|--|

| EA            | EC              | ET2                                             | ES                                                                                                                                                                                                              | ET1         | EX1 | ET0 | EX0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                     |                                                                                                                                                                                                                 |             |     |     |     |  |  |

| 7             | EA              | Clear to disa<br>Set to enable<br>If EA=1, eacl | nable All Interrupt bit<br>lear to disable all interrupts.<br>et to enable all interrupts.<br>EA=1, each interrupt source is individually enabled or disabled by setting or<br>earing its interrupt enable bit. |             |     |     |     |  |  |

| 6             | EC              |                                                 | pt Enable<br>ble the PCA in<br>the PCA inte                                                                                                                                                                     |             |     |     |     |  |  |

| 5             | ET2             | Clear to disa                                   | <b>Fimer 2 Overflow Interrupt Enable bit</b><br>Clear to disable Timer 2 overflow interrupt.<br>Set to enable Timer 2 overflow interrupt.                                                                       |             |     |     |     |  |  |

| 4             | ES              |                                                 | <b>Enable bit</b><br>ble serial port<br>e serial port in                                                                                                                                                        |             |     |     |     |  |  |

| 3             | ET1             | Clear to disa                                   | Timer 1 Overflow Interrupt Enable bit<br>Clear to disable timer 1 overflow interrupt.<br>Set to enable timer 1 overflow interrupt.                                                                              |             |     |     |     |  |  |

| 2             | EX1             | Clear to disa                                   | External Interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                                |             |     |     |     |  |  |

| 1             | ET0             | Clear to disa                                   | Fimer 0 Overflow Interrupt Enable bit<br>Clear to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt.                                                                              |             |     |     |     |  |  |

| 0             | EX0             | Clear to disa                                   | errupt 0 Enat<br>ble external ir<br>e external inte                                                                                                                                                             | nterrupt 0. |     |     |     |  |  |

Reset Value = 0000 0000b bit addressable

**Table 69.** IPL1 RegisterIPL1 (S:F8h)Interrupt Priority Low Register 1

| 7             | 6               | 5                                | 4                                                                                                 | 3               | 2              | 1            | 0 |  |  |

|---------------|-----------------|----------------------------------|---------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|---|--|--|

| -             | -               | -                                | -                                                                                                 | -               | POVRL          | PADCL        | - |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                                                                                                   |                 |                |              |   |  |  |

| 7             | -               | <b>Reserved</b><br>The value rea | eserved<br>ne value read from this bit is indeterminate. Do not set this bit.                     |                 |                |              |   |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                    | it is indetermi | nate. Do not s | et this bit. |   |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                   |                 |                |              |   |  |  |

| 4             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                    | it is indetermi | nate. Do not s | et this bit. |   |  |  |

| 3             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                   |                 |                |              |   |  |  |

| 2             | POVRL           |                                  | Timer Overrun Interrupt Priority Level Less Significant bit<br>Refer to PI2CH for priority level. |                 |                |              |   |  |  |

| 1             | PADCL           |                                  | ADC Interrupt Priority Level Less Significant bit<br>Refer to PSPIH for priority level.           |                 |                |              |   |  |  |

| 0             | -               | Reserved<br>The value rea        | ad from this b                                                                                    | it is indetermi | nate. Do not s | et this bit. |   |  |  |

Reset Value = XXXX X000b bit addressable

**Table 71.** IPH1 RegisterIPH1 (S:F7h)Interrupt high priority Register 1

| 7             | 6               | 5                               | 4                        | 3               | 2              | 1            | 0 |  |

|---------------|-----------------|---------------------------------|--------------------------|-----------------|----------------|--------------|---|--|

| -             | -               | -                               | -                        | -               | POVRH          | PADCH        | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                          |                 |                |              |   |  |

| 7             | -               | <b>Reserved</b><br>The value re | ad from this b           | it is indetermi | nate. Do not s | et this bit. |   |  |

| 6             | -               | <b>Reserved</b><br>The value re | ad from this b           | it is indetermi | nate. Do not s | et this bit. |   |  |

| 5             | -               | <b>Reserved</b><br>The value re | ad from this b           | it is indetermi | nate. Do not s | et this bit. |   |  |

| 4             | -               | <b>Reserved</b><br>The value re | ad from this b           | it is indetermi | nate. Do not s | et this bit. |   |  |

| 3             | -               | <b>Reserved</b><br>The value re | ad from this b           | it is indetermi | nate. Do not s | et this bit. |   |  |

| 2             | POVRH           |                                 | 0 0 Lowest<br>0 1<br>1 0 |                 |                |              |   |  |

| 1             | PADCH           | PADCH PA<br>0<br>0<br>1         | 0 0 Lowest<br>0 1<br>1 0 |                 |                |              |   |  |

| 0             | -               | <b>Reserved</b><br>The value re | ad from this b           | it is indetermi | nate. Do not s | et this bit. |   |  |

Reset Value = XXXX X000b

### **Electrical Characteristics**

#### Absolute Maximum Ratings\*

| I = industrial40°C to 85°C                               |

|----------------------------------------------------------|

| Storage Temperature                                      |

| Voltage on $V_{CC}$ from $V_{SS}$ 0.5V to + 6V           |

| Voltage on Any Pin from $V_{SS}$ 0.5V to $V_{CC}$ + 0.2V |

| Power Dissipation 1 W                                    |

|                                                          |

\*NOTICE: Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability. Power Dissipation value is based on the maximum allowable die temperature and the thermal resistance of the package.

#### DC Parameters for Standard Voltage

| $T_A = -40^{\circ}C$ to $+85^{\circ}C$ ; $V_{SS} = 0$ V; $V_{CC} = 3$ volts to 5.5 volts; $F = 0$ to 40 MHz |  |

|-------------------------------------------------------------------------------------------------------------|--|

| Table 72. DC Parameters in Standard Voltage                                                                 |  |

| ymbol                           | Parameter                                              | Min                                                                                                                                                                  | <b>Typ</b> <sup>(1)</sup> | Max                   | Unit        | Test Conditions                                                                                                                 |

|---------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                 | Input Low Voltage                                      | -0.5                                                                                                                                                                 |                           | 0.2Vcc - 0.1          | V           |                                                                                                                                 |

| V <sub>IH</sub>                 | Input High Voltage except XTAL1, RST                   | 0.2 V <sub>CC</sub> + 0.9                                                                                                                                            |                           | V <sub>CC</sub> + 0.5 | V           |                                                                                                                                 |

| V <sub>IH1</sub> <sup>(2)</sup> | Input High Voltage, XTAL1, RST                         | 0.7 V <sub>CC</sub>                                                                                                                                                  |                           | V <sub>CC</sub> + 0.5 | V           |                                                                                                                                 |

| V <sub>OL</sub>                 | Output Low Voltage, ports 1, 2, 3 and $4^{(3)}$        |                                                                                                                                                                      |                           | 0.3<br>0.45<br>1.0    | V<br>V<br>V | $I_{OL} = 100 \ \mu A$<br>$I_{OL} = 1.6 \ m A$<br>$I_{OL} = 3.5 \ m A$                                                          |

| V <sub>OH</sub>                 | Output High Voltage, ports 1, 2, 3, 4 and 5            | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5                                                                                              |                           |                       | V<br>V<br>V | $\begin{split} I_{OH} &= -10 \; \mu A \\ I_{OH} &= -30 \; \mu A \\ I_{OH} &= -60 \; \mu A \\ V_{CC} &= 5V \pm 10\% \end{split}$ |

| R <sub>RST</sub>                | RST Pulldown Resistor                                  | 50                                                                                                                                                                   | 90                        | 200                   | kΩ          |                                                                                                                                 |

| I <sub>IL</sub>                 | Logical 0 Input Current ports 1, 2, 3 and 4            |                                                                                                                                                                      |                           | -50                   | μA          | Vin = 0.45V                                                                                                                     |

| I <sub>LI</sub>                 | Input Leakage Current                                  |                                                                                                                                                                      |                           | ±10                   | μA          | 0.45V < Vin < V <sub>CC</sub>                                                                                                   |

| I <sub>TL</sub>                 | Logical 1 to 0 Transition Current, ports 1, 2, 3 and 4 |                                                                                                                                                                      |                           | -650                  | μA          | Vin = 2.0V                                                                                                                      |

| C <sub>IO</sub>                 | Capacitance of I/O Buffer                              |                                                                                                                                                                      |                           | 10                    | pF          | Fc = 1 MHz<br>TA = 25°C                                                                                                         |

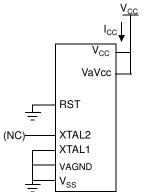

| I <sub>PD</sub>                 | Power-down Current                                     |                                                                                                                                                                      | 160                       | 400                   | μA          | $3V < V_{CC} < 5.5V^{(4)}$                                                                                                      |

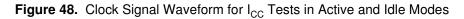

| I <sub>CC</sub>                 | Power Supply Current                                   | $I_{CCOP} = 0.7 \text{ Freq (MHz)} + 3 \text{ mA}$<br>ICC_FLASH_WRITE <sup>(7)</sup> =0.4 Freq (MHz) + 20 mA<br>$I_{CCIDLE} = 0.6 \text{ Freq (MHz)} + 2 \text{ mA}$ |                           |                       |             | 3V < V <sub>CC</sub> < 5.5V <sup>(1)(2)</sup>                                                                                   |

Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature.

Flash retention is guaranteed with the same formula for V<sub>CC</sub> min down to 0V.

AIMEL

All other pins are disconnected.

#### DC Parameters for A/D Converter

#### Table 73. DC Parameters for AD Converter in Precision Conversion

| Symbol              | Parameter                       | Min      | Typ <sup>(1)</sup> | Max               | Unit | Test Conditions |

|---------------------|---------------------------------|----------|--------------------|-------------------|------|-----------------|

| AVin                | Analog input voltage            | Vss- 0.2 |                    | Max Vref<br>+ 0.6 | v    |                 |

| VaVcc               | Analog supply voltage           | Vref     | Vcc                | Vcc +<br>10%      | v    |                 |

| Rref <sup>(2)</sup> | Resistance between Vref and Vss | 12       | 16                 | 24                | KΩ   |                 |

| Vref                | Reference voltage               | 2.40     |                    | 3.00              | V    |                 |

| Rai                 | Analog input Resistor           |          |                    | 400               | Ω    | During sampling |

| Cai                 | Analog input Capacitance        |          | 60                 |                   | pF   | During sampling |

| INL                 | Integral non linearity          |          | 1                  | 2                 | lsb  |                 |

| DNL                 | Differential non linearity      |          | 0.5                | 1                 | lsb  |                 |

| OE                  | Offset error                    | -2       |                    | 2                 | lsb  |                 |

Notes: 1. Typicals are based on a limited number of samples and are not guaranteed.

2. With ADC enabled.

## **Ordering Information**

Table 80. Possible Order Entries

| Part-Number     | Memory Size | Supply<br>Voltage | Temperature<br>Range | Max<br>Frequency | Package | Packing |  |

|-----------------|-------------|-------------------|----------------------|------------------|---------|---------|--|

| T89C5115-SISIM  |             |                   |                      |                  |         |         |  |

| T89C5115-TISIM  | OBSOLETE    |                   |                      |                  |         |         |  |

| T89C5115-RATIM  |             |                   |                      |                  |         |         |  |

| AT89C5115-SISUM | 16K         | 5V                | Industrial & Green   | 40 MHz           | PLCC28  | Stick   |  |

| AT89C5115-TISUM | 16K         | 5V                | Industrial & Green   | 40 MHz           | SOIC28  | Stick   |  |

| AT89C5115-RATUM | 16K         | 5V                | Industrial & Green   | 40 MHz           | VQFP32  | Tray    |  |

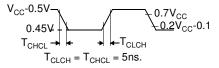

SOIC28

|    | М     | M     | I NCH |       |  |

|----|-------|-------|-------|-------|--|

| A  | 2, 29 | 2.54  | . 090 | . 100 |  |

| A1 | 0.102 | 0.254 | . 004 | . 010 |  |

| В  | 0.38  | 0.51  | .015  | . 020 |  |

| С  | 0.15  | 0.27  | . 006 | .0105 |  |

| D  | 20.83 | 21.08 | . 820 | . 830 |  |

| E  | 10.03 | 10.29 | . 395 | . 405 |  |

| e  | 1.27  | BSC   | . 050 | BSC   |  |

| Н  | 13.49 | 13.84 | . 531 | . 545 |  |

| L  | 0.53  | 1.04  | . 021 | . 041 |  |

| N  | 3     | 2     | 3     | 2     |  |

| ۵  | 0°    | 8°    | 0°    | 8°    |  |