Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                   |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                            |

| Core Processor             | ARM® Cortex®-M4                                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                                |

| Speed                      | 180MHz                                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 63                                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                             |

| EEPROM Size                | -                                                                                                 |

| RAM Size                   | 128K x 8                                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                       |

| Data Converters            | A/D 14x12b; D/A 2x12b                                                                             |

| Oscillator Type            | Internal                                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                     |

| Package / Case             | 81-UFBGA, WLCSP                                                                                   |

| Supplier Device Package    | 81-WLCSP (3.80x3.69)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f446mey6tr                           |

|                            |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

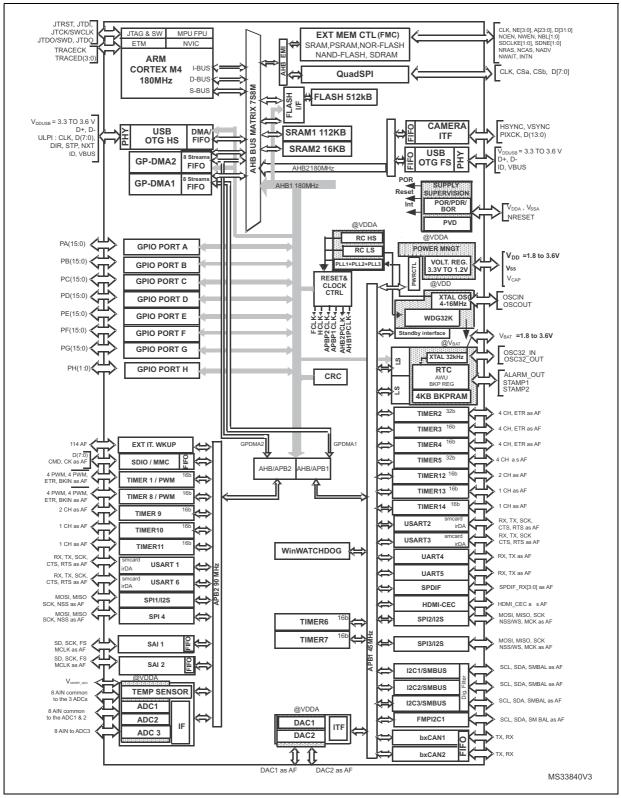

Figure 3. STM32F446xC/E block diagram

## 3.21.4 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

## 3.21.5 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.21.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

# 3.22 Inter-integrated circuit interface (I<sup>2</sup>C)

Four I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. Three I<sup>2</sup>C can support the standard (up to 100 KHz) and fast (up to 400 KHz) modes.

One I<sup>2</sup>C can support the standard (up to 100 KHz), fast (up to 400 KHz) and fast mode plus (up to 1MHz) modes.

They (all I<sup>2</sup>C) support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave).

A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see Table 7).

| -                                   | Analog filter | Digital filter                                            |

|-------------------------------------|---------------|-----------------------------------------------------------|

| Pulse width of<br>suppressed spikes |               | Programmable length from 1 to 15<br>I2C peripheral clocks |

#### Table 7. Comparison of I2C analog and digital filters

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

# 3.25 HDMI (high-definition multimedia interface) consumer electronics control (CEC)

The devices embeds a HDMI-CEC controller that provides hardware support of consumer electronics control (CEC) (Appendix supplement 1 to the HDMI standard). This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead.

# 3.26 Inter-integrated sound (I<sup>2</sup>S)

Three standard  $I^2S$  interfaces (multiplexed with SPI1, SPI2 and SPI3) are available. They can be operated in master or slave mode, in simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the  $I^2S$  interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

## 3.27 SPDIF-RX Receiver Interface (SPDIFRX)

The SPDIF-RX peripheral, is designed to receive an S/PDIF flow compliant with IEC-60958 and IEC-61937. These standards support simple stereo streams up to high sample rate, and compressed multi-channel surround sound, such as those defined by Dolby or DTS (up to 5.1).

The main features of the SPDIF-RX are the following:

- Up to 4 inputs available

- Automatic symbol rate detection

- Maximum symbol rate: 12.288 MHz

- Stereo stream from 32 to 192 kHz supported

- Supports Audio IEC-60958 and IEC-61937, consumer applications

- Parity bit management

- Communication using DMA for audio samples

- Communication using DMA for control and user channel information

- Interrupt capabilities

The SPDIF-RX receiver provides all the necessary features to detect the symbol rate, and decode the incoming data stream.

The user can select the wanted SPDIF input, and when a valid signal will be available, the SPDIF-RX will re-sample the incoming signal, decode the Manchester stream, recognize frames, sub-frames and blocks elements. It delivers to the CPU decoded data, and associated status flags.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4, TIM5, or TIM8 timer.

## 3.38 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as V<sub>BAT</sub>, ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and V<sub>BAT</sub> conversion are enabled at the same time, only V<sub>BAT</sub> conversion is performed.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

## 3.39 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 10-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

## 3.40 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 3.41 Embedded Trace Macrocell<sup>™</sup>

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F446xx through a small number of ETM pins to an external hardware trace port analyser (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

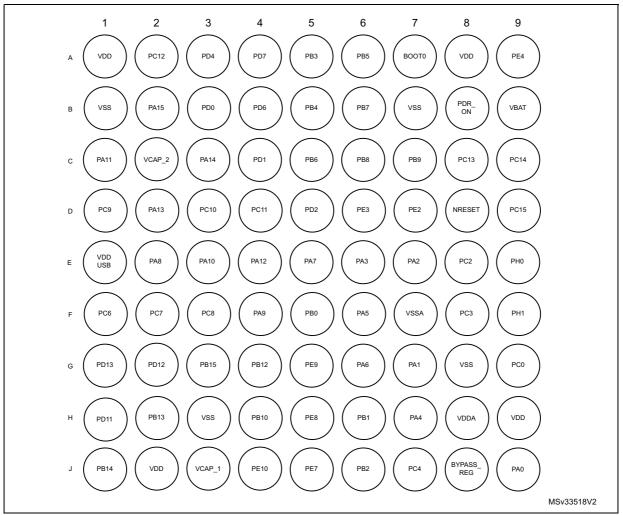

Figure 13. STM32F446xC/xE WLCSP81 ballout

1. The above figure shows the package top view.

62/202

DocID027107 Rev 6

|      |      | AF0         | AF1      | AF2                      | AF3                | AF4              | AF5                       | AF6                                             | AF7                                    | AF8                                   | AF9                                      | AF10       | AF11                     | AF12          | AF13         | AF14 | AF15        |

|------|------|-------------|----------|--------------------------|--------------------|------------------|---------------------------|-------------------------------------------------|----------------------------------------|---------------------------------------|------------------------------------------|------------|--------------------------|---------------|--------------|------|-------------|

| Port | SYS  | TIM1/2      | TIM3/4/5 | TIM8/9/<br>10/11/<br>CEC | I2C1/2/3<br>/4/CEC | SPI1/2/3/<br>4   | SPI2/3/4/<br>SAI1         | SPI2/3/<br>USART1/<br>2/3/UART<br>5/SPDIFR<br>X | SAI/<br>USART6/<br>UART4/5/<br>SPDIFRX | CAN1/2<br>TIM12/13/<br>14/<br>QUADSPI | SAI2/<br>QUADSPI/<br>OTG2_HS/<br>OTG1_FS | OTG1_FS    | FMC/<br>SDIO/<br>OTG2_FS | DCMI          | -            | SYS  |             |

|      | PD0  | -           | -        | -                        | -                  | -                | SPI4_MISO                 | SPI3_<br>MOSI/<br>I2S3_SD                       | -                                      | -                                     | CAN1_RX                                  | -          | -                        | FMC_D2        | -            | -    | EVEN<br>OUT |

|      | PD1  | -           | -        | -                        | -                  | -                | -                         | -                                               | SPI2_NSS/<br>I2S2_WS                   | -                                     | CAN1_TX                                  | -          | -                        | FMC_D3        | -            | -    | EVEN<br>OUT |

|      | PD2  | -           | -        | TIM3_ETR                 | -                  | -                | -                         | -                                               | -                                      | UART5_RX                              | -                                        | -          | -                        | SDIO_CMD      | DCMI_<br>D11 | -    | EVEN<br>OUT |

|      | PD3  | TRACE<br>D1 | -        | -                        | -                  | -                | SPI2_SCK/<br>I2S2_CK      | -                                               | USART2_<br>CTS                         | -                                     | QUADSPI_<br>CLK                          | -          | -                        | FMC_CLK       | DCMI_<br>D5  | -    | EVEN<br>OUT |

|      | PD4  | -           | -        | -                        | -                  | -                | -                         | -                                               | USART2_<br>RTS                         | -                                     | -                                        | -          | -                        | FMC_NOE       | -            | -    | EVEN<br>OUT |

|      | PD5  | -           | -        | -                        | -                  | -                | -                         | -                                               | USART2_<br>TX                          | -                                     | -                                        | -          | -                        | FMC_NWE       | -            | -    | EVEN<br>OUT |

|      | PD6  | -           | -        | -                        | -                  | -                | SPI3_<br>MOSI/<br>I2S3_SD | SAI1_<br>SD_A                                   | USART2_<br>RX                          | -                                     | -                                        | -          | -                        | FMC_<br>NWAIT | DCMI_<br>D10 | -    | EVEN<br>OUT |

| rt D | PD7  | -           | -        | -                        | -                  | -                | -                         | -                                               | USART2_<br>CK                          | SPDIF_<br>RX0                         | -                                        | -          | -                        | FMC_NE1       | -            | -    | EVEN<br>OUT |

|      | PD8  | -           | -        | -                        | -                  | -                | -                         | -                                               | USART3_<br>TX                          | SPDIF_<br>RX1                         | -                                        | -          | -                        | FMC_D13       | -            | -    | EVEN<br>OUT |

|      | PD9  | -           | -        | -                        | -                  | -                | -                         | -                                               | USART3_<br>RX                          | -                                     | -                                        | -          | -                        | FMC_D14       | -            | -    | EVEN<br>OUT |

|      | PD10 | -           | -        | -                        | -                  | -                | -                         | -                                               | USART3_<br>CK                          | -                                     | -                                        | -          | -                        | FMC_D15       | -            | -    | EVEN<br>OUT |

|      | PD11 | -           | -        | -                        | -                  | FMPI2C1<br>_SMBA | -                         | -                                               | USART3_<br>CTS                         | -                                     | QUADSPI_<br>BK1_IO0                      | SAI2_SD_A  | -                        | FMC_A16       | -            | -    | EVEN<br>OUT |

| ţ    | PD12 | -           | -        | TIM4_CH1                 | -                  | FMPI2C1<br>_SCL  | -                         | -                                               | USART3_<br>RTS                         | -                                     | QUADSPI_<br>BK1_IO1                      | SAI2_FS_A  | -                        | FMC_A17       | -            | -    | EVEN<br>OUT |

| t    | PD13 | -           | -        | TIM4_CH2                 | -                  | FMPI2C1<br>_SDA  | -                         | -                                               | -                                      | -                                     | QUADSPI_<br>BK1_IO3                      | SAI2_SCK_A | -                        | FMC_A18       | -            | -    | EVEN<br>OUT |

| t    | PD14 | -           | -        | TIM4_CH3                 | -                  | FMPI2C1<br>_SCL  | -                         | -                                               | -                                      | SAI2_<br>SCK_A                        | -                                        | -          | -                        | FMC_D0        | -            | -    | EVEN<br>OUT |

|      | PD15 | -           | -        | TIM4_CH4                 | -                  | FMPI2C1<br>_SDA  | -                         | -                                               | -                                      | -                                     | -                                        | -          | -                        | FMC_D1        | -            | -    | EVEN<br>OUT |

Pinout and pin description

STM32F446xC/E

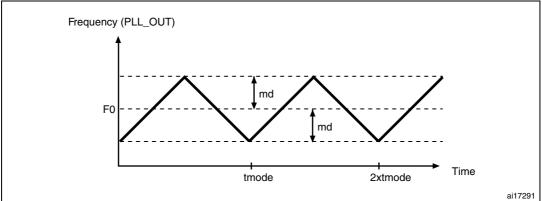

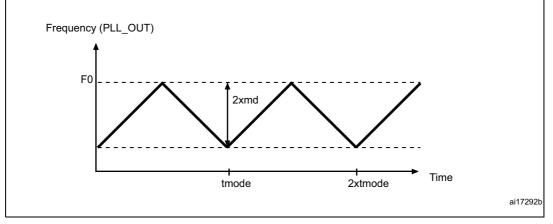

*Figure 29* and *Figure 30* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

$T_{mode}$  is the modulation period.

md is the modulation depth.

## 6.3.13 Memory characteristics

## **Flash memory**

The characteristics are given at TA = - 40 to 105  $^{\circ}$ C unless otherwise specified. The devices are shipped to customers with the Flash memory erased.

Table 47. Flash memory characteristics

|                 |                | -                                           |     |     |     |      |

|-----------------|----------------|---------------------------------------------|-----|-----|-----|------|

| Symbol          | Parameter      | Conditions                                  | Min | Тур | Max | Unit |

|                 | Supply current | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 5   | -   |      |

| I <sub>DD</sub> |                | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                 |                | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

#### **Electrical characteristics**

| OSPEEDR<br>y[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                      | Min | Тур | Мах                | Unit |  |  |  |                                                 |   |   |                    |  |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------|-----|-----|--------------------|------|--|--|--|-------------------------------------------------|---|---|--------------------|--|

| value                                         |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 25                 |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  | (3)                                                                             | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 12.5               |      |  |  |  |                                                 |   |   |                    |  |

|                                               | _                                                |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 10                 | <br> |  |  |  |                                                 |   |   |                    |  |

|                                               | f <sub>max(IO)</sub> out                         | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 50                 | MHz  |  |  |  |                                                 |   |   |                    |  |

| 04                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 20                 |      |  |  |  |                                                 |   |   |                    |  |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 12.5               | -    |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 10                 |      |  |  |  |                                                 |   |   |                    |  |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall                                                   | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 6                  |      |  |  |  |                                                 |   |   |                    |  |

|                                               | t <sub>r(IO)out</sub>                            | time and output low to high level rise time                                     | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 20                 | ns   |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 10                 |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 50 <sup>(4)</sup>  |      |  |  |  |                                                 |   |   |                    |  |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 100 <sup>(4)</sup> | MHz  |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 25                 |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 50                 |      |  |  |  |                                                 |   |   |                    |  |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 42.5               |      |  |  |  |                                                 |   |   |                    |  |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥2.7 V  | -   | -   | 6                  | ns   |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 4                  |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 10                 |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 6                  |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 |                                                 |     |     |                    |      |  |  |  | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | - | - | 100 <sup>(4)</sup> |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 50                 | MHz  |  |  |  |                                                 |   |   |                    |  |

|                                               | £                                                | Maximum fraguescu (3)                                                           | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 42.5               |      |  |  |  |                                                 |   |   |                    |  |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 180 <sup>(4)</sup> |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 100                |      |  |  |  |                                                 |   |   |                    |  |

| 44                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 72.5               |      |  |  |  |                                                 |   |   |                    |  |

| 11                                            |                                                  |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 4                  |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 6                  |      |  |  |  |                                                 |   |   |                    |  |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall                                                   | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 7                  |      |  |  |  |                                                 |   |   |                    |  |

|                                               | t <sub>r(IO)out</sub>                            | time and output low to high level rise time                                     | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 2.5                | ns   |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 3.5                |      |  |  |  |                                                 |   |   |                    |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 4                  | 1    |  |  |  |                                                 |   |   |                    |  |

| -                                             | t <sub>EXTIpw</sub>                              | Pulse width of external signals detected by the EXTI controller                 | -                                               | 10  | -   | -                  | ns   |  |  |  |                                                 |   |   |                    |  |

Table 58. I/O AC characteristics<sup>(1)(2)</sup> (continued)

The I<sup>2</sup>C characteristics are described in *Table 61*. Refer also to *Section 6.3.17: I/O port characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                                                                                              |     | rd mode<br>1)(2)    | Fast mod | e I <sup>2</sup> C <sup>(1)(2)</sup> | Unit |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|---------------------|----------|--------------------------------------|------|

|                                            |                                                                                                        | Min | Max                 | Min      | Max                                  |      |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                                                     | 4.7 | -                   | 1.3      | -                                    | μs   |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                                                    | 4.0 | -                   | 0.6      | -                                    | μο   |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                                                         | 250 | -                   | 100      | -                                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                                                     | -   | 3450 <sup>(3)</sup> | -        | 900 <sup>(4)</sup>                   |      |

| t <sub>v(SDA, ACK)</sub>                   | Data, ACK valid time                                                                                   | -   | 3.45                | -        | 0.9                                  |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                                                  | -   | 1000                | -        | 300                                  | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                                                  | -   | 300                 | -        | 300                                  |      |

| t <sub>h(STA)</sub>                        | Start condition hold time                                                                              | 4.0 | -                   | 0.6      | -                                    |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                                                    | 4.7 | -                   | 0.6      | -                                    | μs   |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                                                              | 4.0 | -                   | 0.6      | -                                    | μs   |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                                                                | 4.7 | -                   | 1.3      | -                                    | μs   |

| t <sub>SP</sub>                            | Pulse width of the spikes<br>that are suppressed by the<br>analog filter for standard and<br>fast mode | -   | -                   | 0.05     | 0.09 <sup>(5)</sup>                  | μs   |

| Cb                                         | Capacitive load for each bus line                                                                      | -   | 400                 | -        | 400                                  | pF   |

| Table | 61. | l <sup>2</sup> C | characteristics |

|-------|-----|------------------|-----------------|

|-------|-----|------------------|-----------------|

1. Guaranteed based on test during characterization.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies, and a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

4. The maximum data hold time has only to be met if the interface does not stretch the low period of SCL signal.

5. The minimum width of the spikes filtered by the analog filter is above  $t_{SP}(max)$ .

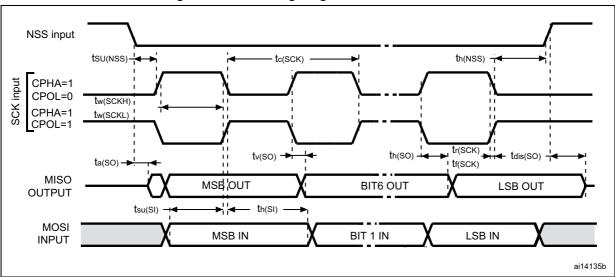

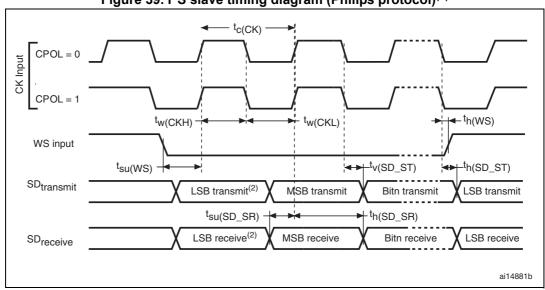

Figure 37. SPI timing diagram - slave mode and CPHA = 1

#### **QSPI** interface characteristics

Unless otherwise specified, the parameters given in *Table 64* for QSPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 16*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C=20pF

- Measurement points are done at CMOS levels: 0.5VDD

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol                                    | Parameter               | Conditions                                                   | Min                         | Тур | Мах                        | Unit |

|-------------------------------------------|-------------------------|--------------------------------------------------------------|-----------------------------|-----|----------------------------|------|

|                                           |                         | Write mode<br>1.71 V≤V <sub>DD</sub> ≤3.6 V<br>Cload = 15 pF | -                           | -   | 90                         |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | QSPI clock frequency    | Read mode<br>2.7V <vdd< 3.6v<br="">Cload = 15 pF</vdd<>      | -                           | -   | 90                         | MHz  |

|                                           |                         | 1.71 V≤V <sub>DD</sub> ≤3.6 V                                | -                           | -   | 48                         |      |

| t <sub>w(CKH)</sub>                       | QSPI clock high and low | _                                                            | (T <sub>(CK)</sub> / 2) - 2 | -   | Т <sub>(СК)</sub> / 2      |      |

| t <sub>w(CKL)</sub>                       |                         | -                                                            | T <sub>(CK)</sub> / 2       | -   | (T <sub>(CK)</sub> / 2) +2 |      |

| t <sub>s(IN)</sub>                        | Data input setup time   | -                                                            | 2                           | -   | -                          | ns   |

| t <sub>h(IN)</sub>                        | Data input hold time    | -                                                            | 4.5                         | -   | -                          | 115  |

| t <sub>v(OUT)</sub>                       | Data output valid time  | -                                                            | -                           | 1.5 | 3                          |      |

| t <sub>h(OUT)</sub>                       | Data output hold time   | -                                                            | 0                           | -   | -                          |      |

#### Table 64. QSPI dynamic characteristics in SDR Mode<sup>(1)</sup>

1. Guaranteed based on test during characterization.

| Symbol                                    | Parameter            | Conditions                                                   | Min | Тур | Мах | Unit |

|-------------------------------------------|----------------------|--------------------------------------------------------------|-----|-----|-----|------|

|                                           |                      | Write mode<br>1.71 V≤V <sub>DD</sub> ≤3.6 V<br>Cload = 15 pF | -   | -   | 60  |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | QSPI clock frequency | Read mode<br>2.7V <vdd< 3.6v<br="">Cload = 15 pF</vdd<>      | -   | -   | 60  | MHz  |

|                                           |                      | 1.71 V≤V <sub>DD</sub> ≤3.6 V                                | -   | -   | 48  |      |

## Table 65. QSPI dynamic characteristics in DDR Mode<sup>(1)</sup>

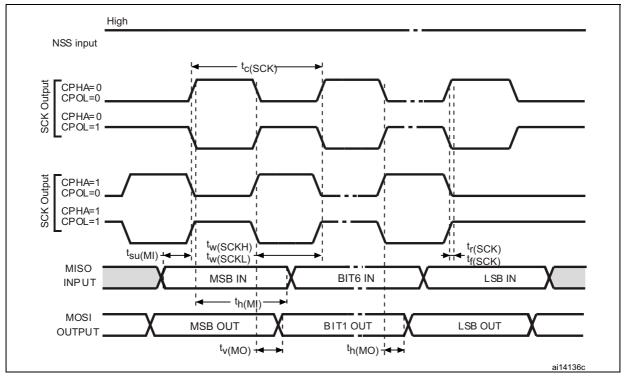

Figure 39. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

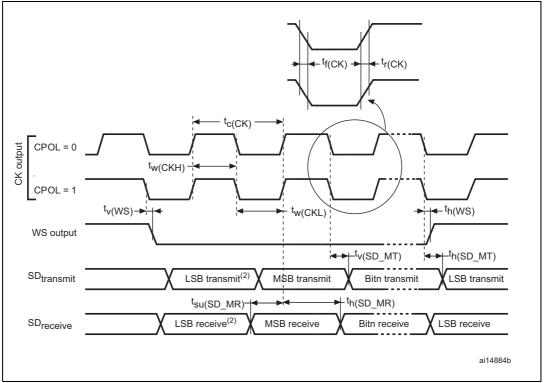

# Figure 40. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

|                           | ittikar anningo                           |                          |                        | -    |

|---------------------------|-------------------------------------------|--------------------------|------------------------|------|

| Symbol                    | Parameter                                 | Min                      | Max                    | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> - 0.5 | 8T <sub>HCLK</sub> + 1 |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> - 0.5 | 6T <sub>HCLK</sub> + 1 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> - 0.5 | -                      | 115  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> + 2   | -                      |      |

Table 89. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings  $^{(1)(2)}$

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

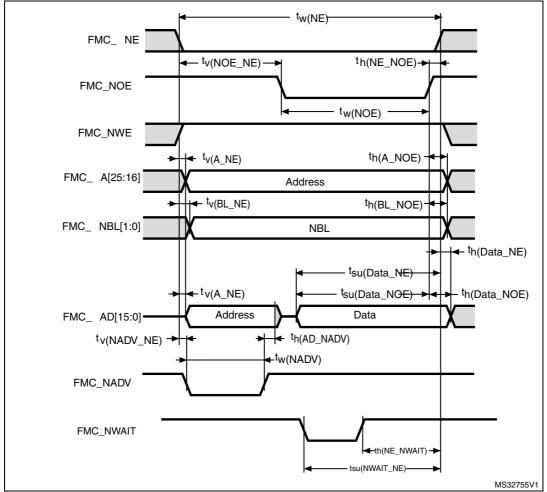

| Symbol                    | Parameter                                              | Min                     | Max                      | Unit |

|---------------------------|--------------------------------------------------------|-------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                        | 4T <sub>HCLK</sub> - 2  | 4T <sub>HCLK</sub> +0.5  |      |

| t <sub>v(NWE_NE)</sub>    | FMC_NEx low to FMC_NWE low                             | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5  |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                                       | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NWE)</sub>    | FMC_NWE high to FMC_NE high hold time                  | T <sub>HCLK</sub>       | -                        |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                             | -                       | 0                        |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                            | 0.5                     | 1                        |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                      | T <sub>HCLK</sub> -0.5  | T <sub>HCLK</sub> + 0.5  | ns   |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(adress) valid hold time after<br>FMC_NADV high) | T <sub>HCLK</sub> -2    | -                        |      |

| t <sub>h(A_NWE)</sub>     | Address hold time after FMC_NWE high                   | T <sub>HCLK</sub>       | -                        |      |

| t <sub>h(BL_NWE)</sub>    | FMC_BL hold time after FMC_NWE high                    | T <sub>HCLK</sub> –2    | -                        |      |

| $t_{v(BL_NE)}$            | FMC_NEx low to FMC_BL valid                            | -                       | 2                        |      |

| t <sub>v(Data_NADV)</sub> | FMC_NADV high to Data valid                            | -                       | T <sub>HCLK</sub> + 1.5  |      |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FMC_NWE high                      | T <sub>HCLK</sub> + 0.5 | -                        |      |

Table 92. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

| Symbol                    | Parameter Min                                              |                          | Max                      | Unit |

|---------------------------|------------------------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                            | 9T <sub>HCLK</sub>       | 9T <sub>HCLK</sub> + 0.5 |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                                           | 7T <sub>HCLK</sub>       | 7T <sub>HCLK</sub> + 2   | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high                        | 6T <sub>HCLK</sub> + 1.5 | -                        |      |

| t <sub>h(NE_NWAIT)</sub>  | WAIT) FMC_NEx hold time after FMC_NWAIT 4T <sub>HCLK</sub> |                          | -                        |      |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

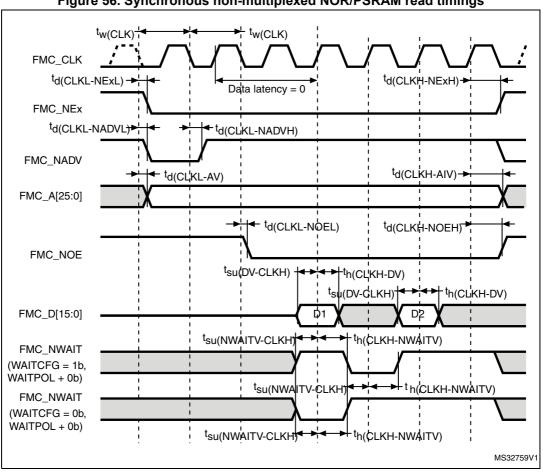

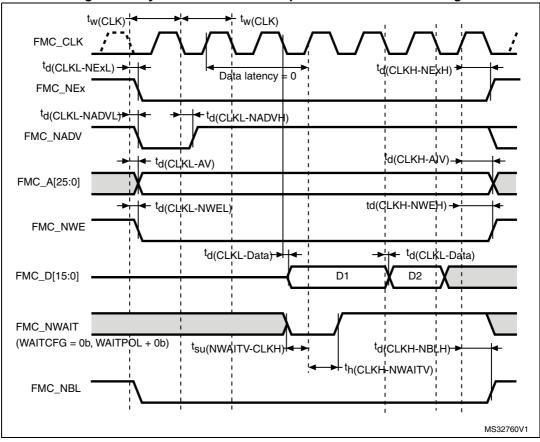

## Synchronous waveforms and timings

*Figure 54* through *Figure 57* represent synchronous waveforms and *Table 94* through *Table 97* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F446 reference manual: RM0390)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

Figure 56. Synchronous non-multiplexed NOR/PSRAM read timings

| Table 96. Synchronous non-multiplexed NOR/PSRAM read timings <sup>(1)</sup> |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

| Symbol                      | Parameter                                      | Min                     | Max | Unit |

|-----------------------------|------------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                                 | 2T <sub>HCLK</sub>      | -   |      |

| t <sub>(CLKL-NExL)</sub>    | FMC_CLK low to FMC_NEx low (x=02)              | -                       | 2.5 |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)           | T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                    | -                       | 0   |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high                   | 0                       | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)           | -                       | 2.5 |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)        | T <sub>HCLK</sub>       | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>   | FMC_CLK low to FMC_NOE low                     | -                       | 2   |      |

| t <sub>d(CLKH-NOEH)</sub>   | FMC_CLK high to FMC_NOE high                   | T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>su(DV-CLKH)</sub>    | FMC_D[15:0] valid data before FMC_CLK high     | 1                       | -   |      |

| t <sub>h(CLKH-DV)</sub>     | FMC_D[15:0] valid data after FMC_CLK high      | 3.5                     | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | IT-CLKH) FMC_NWAIT valid before FMC_CLK high 1 |                         | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high             | 3.5                     | -   | ]    |

- 1. C<sub>L</sub> = 30 pF.

- 2. Guaranteed based on test during characterization.

| Symbol                      | Parameter                                                               | Min                     |     | Unit |

|-----------------------------|-------------------------------------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                                                          | 2T <sub>HCLK</sub> – 1  | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)                                       | -                       | 2.5 |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)                                    | T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                                             | -                       | 2   |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high                                            | 0                       | -   |      |

| t <sub>d(CLKL-AV)</sub>     | V)     FMC_CLK high to FMC_Ax invalid (x=1625)     0                    |                         | 2   |      |

| t <sub>d(CLKH-AIV)</sub>    |                                                                         |                         | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   |                                                                         |                         | 3   | 115  |

| t <sub>d(CLKH-NWEH)</sub>   | WEH)         FMC_CLK high to FMC_NWE high         T <sub>HCLK</sub> + 1 |                         | -   |      |

| t <sub>d(CLKL-Data)</sub>   | ata) FMC_D[15:0] valid data after FMC_CLK low -                         |                         | 2.5 |      |

| $t_{d(CLKL-NBLL)}$          | LKL-NBLL) FMC_CLK low to FMC_NBL low                                    |                         | -   |      |

| t <sub>d(CLKH-NBLH)</sub>   | KH-NBLH) FMC_CLK high to FMC_NBL high T <sub>HCLK</sub> +               |                         | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high                                     | 1.5                     | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | KH-NWAIT)         FMC_NWAIT valid after FMC_CLK high         0          |                         | -   |      |

Table 97. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

## NAND controller waveforms and timings

*Figure 58* through *Figure 61* represent synchronous waveforms, and *Table 98* and *Table 99* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FSMC\_SetupTime = 0x01;

- COM.FMC\_WaitSetupTime = 0x03;

- COM.FMC\_HoldSetupTime = 0x02;

- COM.FMC\_HiZSetupTime = 0x01;

- ATT.FMC\_SetupTime = 0x01;

- ATT.FMC\_WaitSetupTime = 0x03;

- ATT.FMC\_HoldSetupTime = 0x02;

- ATT.FMC\_HiZSetupTime = 0x01;

- Bank = FMC\_Bank\_NAND;

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b;

- ECC = FMC\_ECC\_Enable;

- ECCPageSize = FMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

| Symbol                        | Parameter              | Min                     | Мах                     | Unit |

|-------------------------------|------------------------|-------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> -0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time  | 1                       | -                       |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 4                       | -                       |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -                       | 3                       |      |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                       | 1.5                     | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0                       | -                       | 113  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                       | 1.5                     |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                       | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                       | 0.5                     |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                       | -                       |      |

# Table 100. SDRAM read timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed based on test during characterization.

# Table 101. LPSDR SDRAM read timings<sup>(1)(2)</sup>

| Symbol                        | Parameter              | Min                      | Мах                      | Unit |

|-------------------------------|------------------------|--------------------------|--------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> - 0.5 | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time  | 1                        | -                        |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 5                        | -                        |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -                        | 3                        |      |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                        | 3                        | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0                        | -                        | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 2                        |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                        |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 2                        |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                        | -                        |      |

1. CL = 10 pF.

2. Guaranteed based on test during characterization.

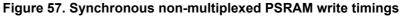

|                     | Table 105. Dynamic character            | ristics: SD / MI | MC charact | teristics <sup>(1)(2</sup> | 2)  |       |

|---------------------|-----------------------------------------|------------------|------------|----------------------------|-----|-------|

| Symbol              | Parameter                               | Conditions       | Min        | Тур                        | Max | Unit  |

| f <sub>PP</sub>     | Clock frequency in data transfer mode   | -                | 0          | -                          | 50  | MHz   |

| -                   | SDIO_CK/fPCLK2 frequency ratio          | -                | -          | -                          | 8/3 | -     |

| t <sub>W(CKL)</sub> | Clock low time                          | fpp =50MHz       | 9.5        | 10.5                       | -   | ne    |

| t <sub>W(CKH)</sub> | Clock high time                         | fpp =50MHz       | 8.5        | 9.5                        | -   | ns ns |

| CMD, D inp          | outs (referenced to CK) in MMC and SE   | ) HS mode        |            |                            |     |       |

| t <sub>ISU</sub>    | Input setup time HS                     | fpp =50MHz       | 1          | -                          | -   |       |

| t <sub>IH</sub>     | Input hold time HS                      | fpp =50MHz       | 4.5        | -                          | -   | – ns  |

| CMD, D ou           | tputs (referenced to CK) in MMC and S   | D HS mode        |            |                            |     | -     |

| t <sub>OV</sub>     | Output valid time HS                    | fpp =50MHz       | -          | 12.5                       | 13  |       |

| t <sub>OH</sub>     | Output hold time HS                     | fpp =50MHz       | 11         | -                          | -   | ns    |

| CMD, D inp          | outs (referenced to CK) in SD default m | node             |            |                            |     |       |

| t <sub>ISUD</sub>   | Input setup time SD                     | fpp =25MHz       | 2.5        | -                          | -   |       |

| t <sub>IHD</sub>    | Input hold time SD                      | fpp =25MHz       | 5.5        | -                          | -   | ns    |

| CMD, D ou           | tputs (referenced to CK) in SD default  | mode             |            |                            |     |       |

| t <sub>OVD</sub>    | Output valid default time SD            | fpp =24MHz       | -          | 3.5                        | 4   |       |

| t <sub>OHD</sub>    | Output hold default time SD             | fpp =24MHz       | 2          | -                          | -   | ns    |

(4)(0)

1. Guaranteed based on test during characterization.

2.  $V_{DD}$  = 2.7 to 3.6 V.