Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                                |

| Speed                      | 180MHz                                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 50                                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                             |

| EEPROM Size                | -                                                                                                 |

| RAM Size                   | 128K x 8                                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                       |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                             |

| Oscillator Type            | Internal                                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                     |

| Package / Case             | 64-LQFP                                                                                           |

| Supplier Device Package    | 64-LQFP (10x10)                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f446ret6                             |

|                            |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 92.  | Asynchronous multiplexed PSRAM/NOR write timings                               |

|------------|--------------------------------------------------------------------------------|

| Table 93.  | Asynchronous multiplexed PSRAM/NOR write-NWAIT timings                         |

| Table 94.  | Synchronous multiplexed NOR/PSRAM read timings                                 |

| Table 95.  | Synchronous multiplexed PSRAM write timings                                    |

| Table 96.  | Synchronous non-multiplexed NOR/PSRAM read timings                             |

| Table 97.  | Synchronous non-multiplexed PSRAM write timings                                |

| Table 98.  | Switching characteristics for NAND Flash read cycles                           |

| Table 99.  | Switching characteristics for NAND Flash write cycles                          |

| Table 100. | SDRAM read timings                                                             |

| Table 101. | LPSDR SDRAM read timings                                                       |

| Table 102. | SDRAM write timings                                                            |

| Table 103. | LPSDR SDRAM write timings                                                      |

| Table 104. | DCMI characteristics                                                           |

| Table 105. | Dynamic characteristics: SD / MMC characteristics                              |

| Table 106. | Dynamic characteristics: eMMC characteristics VDD = 1.7 V to 1.9 V             |

| Table 107. | RTC characteristics                                                            |

| Table 108. | LQFP64 – 10 x 10 mm low-profile quad flat package mechanical data              |

| Table 109. | LQPF100, 14 x 14 mm 100-pin low-profile quad flat                              |

|            | package mechanical data                                                        |

| Table 110. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data 183 |

| Table 111. | UFBGA144 - 144-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball             |

|            | grid array package mechanical data                                             |

| Table 112. | UFBGA144 recommended PCB design rules (0.50 mm pitch BGA)                      |

| Table 113. | UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball           |

|            | grid array package mechanical data                                             |

| Table 114. | UFBGA144 recommended PCB design rules (0.80 mm pitch BGA)                      |

| Table 115. | WLCSP81- 81-pin, 3.693 x 3.815 mm, 0.4 mm pitch wafer level chip scale         |

|            | package mechanical data                                                        |

| Table 116. | WLCSP81 recommended PCB design rules (0.4 mm pitch) 193                        |

| Table 117. | Package thermal characteristics                                                |

| Table 118. | Ordering information scheme                                                    |

| Table 119. | Document revision history                                                      |

## **3** Functional overview

# 3.1 **ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU and embedded Flash and SRAM**

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core is a 32-bit RISC processor that features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F446xC/E family is compatible with all ARM tools and software.

*Figure 3* shows the general block diagram of the STM32F446xC/E family.

Note: Cortex-M4 with FPU core is binary compatible with the Cortex-M3 core.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 225 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART Accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 180 MHz.

## 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDIO

- Camera interface (DCMI)

- ADC

- SAI1/SAI2

- SPDIF Receiver (SPDIFRx)

- QuadSPI

## **3.9** Flexible memory controller (FMC)

All devices embed an FMC. It has seven Chip Select outputs supporting the following modes: SDRAM/LPSDR SDRAM, SRAM, PSRAM, NOR Flash and NAND Flash. With the possibility to remap FMC bank 1 (NOR/PSRAM 1 and 2) and FMC SDRAM bank 1/2 in the Cortex-M4 code area.

Functionality overview:

- 8-,16-bit data bus width

- Read FIFO for SDRAM controller

- Write FIFO

- Maximum FMC\_CLK/FMC\_SDCLK frequency for synchronous accesses is 90 MHz.

#### LCD parallel interface

The FMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

## 3.10 Quad SPI memory interface (QUADSPI)

All devices embed a Quad SPI memory interface, which is a specialized communication interface targeting Single, Dual or Quad SPI flash memories. It can work in direct mode through registers, external flash status register polling mode and memory mapped mode. Up to 256 Mbytes external flash are memory mapped, supporting 8, 16 and 32-bit access. Code execution is supported. The opcode and the frame format are fully programmable. Communication can be either in Single Data Rate or Dual Data Rate.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

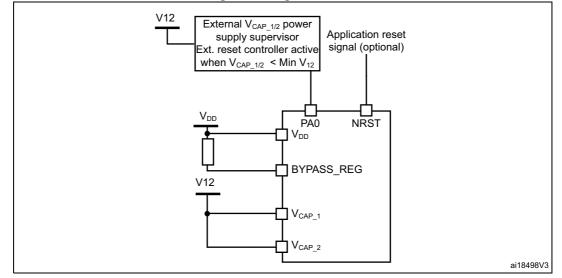

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

#### Figure 7. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach  $V_{12}$  minimum value is faster than the time for  $V_{DD}$  to reach 1.7 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach  $V_{12}$  minimum value and until  $V_{DD}$  reaches 1.7 V (see *Figure 8*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 9*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application.

## 3.21.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

## 3.21.2 General-purpose timers (TIMx)

There are ten synchronized general-purpose timers embedded in the STM32F446xC/E devices (see *Table 6* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F446xC/E include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

## 3.21.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

#### 3.21.4 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### 3.21.5 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.21.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

# 3.22 Inter-integrated circuit interface (I<sup>2</sup>C)

Four I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. Three I<sup>2</sup>C can support the standard (up to 100 KHz) and fast (up to 400 KHz) modes.

One I<sup>2</sup>C can support the standard (up to 100 KHz), fast (up to 400 KHz) and fast mode plus (up to 1MHz) modes.

They (all I<sup>2</sup>C) support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave).

A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see Table 7).

| -                                   | Analog filter | Digital filter                                            |  |  |  |  |

|-------------------------------------|---------------|-----------------------------------------------------------|--|--|--|--|

| Pulse width of<br>suppressed spikes |               | Programmable length from 1 to 15<br>I2C peripheral clocks |  |  |  |  |

#### Table 7. Comparison of I2C analog and digital filters

|        | Pin Number |          |          |         |                                    |          |               |       |                                                                                                |                         |

|--------|------------|----------|----------|---------|------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100    | WLCSP 81 | UFBGA144 | LQFP144 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                            | Additional<br>functions |

| 51     | 78         | D3       | B11      | 111     | PC10                               | I/O      | FT            | -     | SPI3_SCK/I2S3_CK,<br>USART3_TX, UART4_TX,<br>QUADSPI_BK1_IO1,<br>SDIO_D2, DCMI_D8,<br>EVENTOUT | -                       |

| 52     | 79         | D4       | B10      | 112     | PC11                               | I/O      | FT            | -     | SPI3_MISO, USART3_RX,<br>UART4_RX,<br>QUADSPI_BK2_NCS,<br>SDIO_D3, DCMI_D4,<br>EVENTOUT        | -                       |

| 53     | 80         | A2       | C10      | 113     | PC12                               | I/O      | FT            | Ι     | I2C2_SDA,<br>SPI3_MOSI/I2S3_SD,<br>USART3_CK, UART5_TX,<br>SDIO_CK, DCMI_D9,<br>EVENTOUT       | -                       |

| -      | 81         | В3       | E10      | 114     | PD0                                | I/O      | FT            | -     | SPI4_MISO,<br>SPI3_MOSI/I2S3_SD,<br>CAN1_RX, FMC_D2,<br>EVENTOUT                               | -                       |

| -      | 82         | C4       | D10      | 115     | PD1                                | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>CAN1_TX, FMC_D3,<br>EVENTOUT                                              | -                       |

| 54     | 83         | D5       | E9       | 116     | PD2                                | I/O      | FT            | -     | TIM3_ETR, UART5_RX,<br>SDIO_CMD, DCMI_D11,<br>EVENTOUT                                         | -                       |

| -      | 84         | -        | D9       | 117     | PD3                                | I/O      | FT            | -     | TRACED1,<br>SPI2_SCK/I2S2_CK,<br>USART2_CTS,<br>QUADSPI_CLK,<br>FMC_CLK, DCMI_D5,<br>EVENTOUT  | -                       |

| -      | 85         | A3       | C9       | 118     | PD4                                | I/O      | FT            | -     | USART2_RTS, FMC_NOE,<br>EVENTOUT                                                               | -                       |

| -      | 86         | -        | B9       | 119     | PD5                                | I/O      | FT            | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                                | -                       |

| -      | -          | -        | E7       | 120     | VSS                                | S        | -             | -     | -                                                                                              | -                       |

| -      | -          | -        | F7       | 121     | VDD                                | S        | -             | -     | -                                                                                              | -                       |

Table 10. STM32F446xx pin and ball descriptions (continued)

STM32F446xC/E

Pinout and pin description

| _ |        |      |             |        |          |                          | 1                  | Table 11.      | Alterna           | te funct                                        | ion (cor                               | tinued)                               |                                          |         |                          |                               |      |                          |

|---|--------|------|-------------|--------|----------|--------------------------|--------------------|----------------|-------------------|-------------------------------------------------|----------------------------------------|---------------------------------------|------------------------------------------|---------|--------------------------|-------------------------------|------|--------------------------|

|   |        |      | AF0         | AF1    | AF2      | AF3                      | AF4                | AF5            | AF6               | AF7                                             | AF8                                    | AF9                                   | AF10                                     | AF11    | AF12                     | AF13                          | AF14 | AF1                      |

| • | Ро     | rt   | SYS         | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11/<br>CEC | I2C1/2/3<br>/4/CEC | SPI1/2/3/<br>4 | SPI2/3/4/<br>SAI1 | SPI2/3/<br>USART1/<br>2/3/UART<br>5/SPDIFR<br>X | SAI/<br>USART6/<br>UART4/5/<br>SPDIFRX | CAN1/2<br>TIM12/13/<br>14/<br>QUADSPI | SAI2/<br>QUADSPI/<br>OTG2_HS/<br>OTG1_FS | OTG1_FS | FMC/<br>SDIO/<br>OTG2_FS | DCMI                          | -    | SYS                      |

|   |        | PG0  | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A10                  | -                             | -    | EVEN<br>OUT              |

|   |        | PG1  | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A11                  | -                             | -    | EVEN<br>OUT              |

|   |        | PG2  | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A12                  | -                             | -    | EVEN<br>OUT              |

|   |        | PG3  | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A13                  | -                             | -    | EVEN<br>OUT              |

|   |        | PG4  | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A14/<br>FMC_BA0      | -                             | -    | EVEN <sup>-</sup><br>OUT |

|   |        | PG5  | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A15/<br>FMC_BA1      | -                             | -    | EVEN<br>OUT              |

|   |        | PG6  | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | QUADSPI_<br>BK1_NCS                      | -       | -                        | DCMI_<br>D12                  | -    | EVEN<br>OUT              |

|   |        | PG7  | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | USART6_C<br>K                          | -                                     | -                                        | -       | FMC_INT                  | DCMI_<br>D13                  | -    | EVEN<br>OUT              |

| F | Port G | PG8  | -           | -      | -        | -                        | -                  | -              | -                 | SPDIFRX_<br>IN2                                 | USART6_R<br>TS                         | -                                     | -                                        | -       | FMC_<br>SDCLK            | -                             | -    | EVEN<br>OUT              |

|   |        | PG9  | -           | -      | -        | -                        | -                  | -              | -                 | SPDIFRX_<br>IN3                                 | USART6_R<br>X                          | QUADSPI_<br>BK2_IO2                   | SAI2_FS_B                                | -       | FMC_NE2/<br>FMC_NCE3     | DCMI_<br>VSYNC <sup>(1)</sup> | -    | EVEN<br>OUT              |

|   |        | PG10 | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | SAI2_SD_B                                | -       | FMC_NE3                  | DCMI_D2                       | -    | EVEN<br>OUT              |

|   |        | PG11 | -           | -      | -        | -                        | -                  | -              | SPI4_<br>SCK      | SPDIFRX_<br>IN0                                 | -                                      | -                                     | -                                        | -       | -                        | DCMI_D3                       | -    | EVEN<br>OUT              |

|   |        | PG12 | -           | -      | -        | -                        | -                  | -              | SPI4_<br>MISO     | SPDIFRX_<br>IN1                                 | USART6_R<br>TS                         | -                                     | -                                        | -       | FMC_NE4                  | -                             | -    | EVEN<br>OUT              |

|   |        | PG13 | TRACE<br>D2 | -      | -        | -                        | -                  | -              | SPI4_<br>MOSI     | -                                               | USART6_C<br>TS                         | -                                     | -                                        | -       | FMC_A24                  | -                             | -    | EVEN<br>OUT              |

|   |        | PG14 | TRACE<br>D3 | -      | -        | -                        | -                  | -              | SPI4_<br>NSS      | -                                               | USART6_T<br>X                          | QUADSPI_<br>BK2_IO3                   | -                                        | -       | FMC_A25                  | -                             | -    | EVEN<br>OUT              |

|   |        | PG15 | -           | -      | -        | -                        | -                  | -              | -                 | -                                               | USART6_C<br>TS                         | -                                     | -                                        | -       | FMC_<br>SDNCAS           | DCMI_<br>D13                  | -    | EVEN<br>OUT              |

65/202

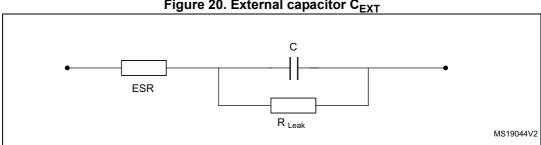

Figure 20. External capacitor C<sub>EXT</sub>

1. Legend: ESR is the equivalent series resistance.

| Symbol           | Parameter                                                                      | Conditions |

|------------------|--------------------------------------------------------------------------------|------------|

| C <sub>EXT</sub> | Capacitance of external capacitor                                              | 2.2 μF     |

| ESR              | ESR of external capacitor                                                      | < 2 Ω      |

| C <sub>EXT</sub> | Capacitance of external capacitor with a single $V_{\text{CAP}}$ pin available | 4.7 µF     |

| ESR              | ESR of external capacitor with a single $V_{\mbox{CAP}}$ pin available         | < 1 Ω      |

#### Table 18. VCAP\_1/VCAP\_2 operating conditions<sup>(1)</sup>

When bypassing the voltage regulator, the two 2.2  $\mu F$  V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors. 1.

#### 6.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for T<sub>A</sub>.

#### Table 19. Operating conditions at power-up/power-down (regulator ON)

| Symbol           | Parameter                      | Min | Max |

|------------------|--------------------------------|-----|-----|

| 4                | V <sub>DD</sub> rise time rate | 20  | ∞   |

| <sup>L</sup> VDD | V <sub>DD</sub> fall time rate | 20  | ∞   |

#### Operating conditions at power-up / power-down (regulator OFF) 6.3.4

Subject to general operating conditions for T<sub>A</sub>.

#### Table 20. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit  |

|-------------------|----------------------------------------------|------------|-----|-----|-------|

| t                 | V <sub>DD</sub> rise time rate               | Power-up   | 20  | ~   |       |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate               | Power-down | 20  | 8   | µs/V  |

| +                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | 8   | μ5/ ν |

| <sup>t</sup> VCAP | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | 8   |       |

To reset the internal logic at power-down, a reset must be applied on pin PA0 when V<sub>DD</sub> reach below 1.08 V. 1.

|                 |                   |                                                                             |                         |     |                    | Max <sup>(1)</sup> |           |       |       |  |

|-----------------|-------------------|-----------------------------------------------------------------------------|-------------------------|-----|--------------------|--------------------|-----------|-------|-------|--|

| Symbol          | Parameter         | Conditions                                                                  | f <sub>HCLK</sub> (MHz) | Тур | TA=<br>25 °C       | TA=85 °C           | TA=105 °C | Unit  |       |  |

|                 |                   |                                                                             | 180                     | 81  | 89.0               | 110.0              | 120.0     |       |       |  |

|                 |                   |                                                                             |                         |     | 168 <sup>(4)</sup> | 74                 | 80.2      | 105.7 | 112.0 |  |

|                 |                   |                                                                             | 150                     | 69  | 74.9               | 99.5               | 105.6     |       |       |  |

|                 |                   | External clock,                                                             | 144 <sup>(4)</sup>      | 63  | 69.3               | 92.4               | 98.1      |       |       |  |

|                 |                   | PLL ON,<br>all peripherals                                                  | 120                     | 51  | 56.3               | 76.1               | 81.1      |       |       |  |

|                 |                   | enabled <sup>(2)(3)</sup>                                                   | 90                      | 40  | 45.32              | 63.19              | 67.63     |       |       |  |

|                 |                   |                                                                             | 60                      | 28  | 33.1               | 48.7               | 52.6      |       |       |  |

|                 |                   |                                                                             | 30                      | 16  | 20.8               | 34.0               | 37.4      |       |       |  |

|                 |                   |                                                                             | 25                      | 13  | 18.4               | 31.2               | 34.5      | - mA  |       |  |

|                 |                   | External clock,<br>PLL ON,<br>all Peripherals<br>disabled <sup>(2)(3)</sup> | 16                      | 8   | 13.8               | 25.0               | 28.2      |       |       |  |

|                 |                   |                                                                             | 8                       | 5   | 10.8               | 21.1               | 24.2      |       |       |  |

|                 |                   |                                                                             | 4                       | 3.0 | 9.1                | 19.0               | 22.0      |       |       |  |

| 1               | Supply current in |                                                                             | 2                       | 2.1 | 8.1                | 17.9               | 20.9      |       |       |  |

| I <sub>DD</sub> | RUN mode          |                                                                             | 180                     | 41  | 47.0               | 69.0               | 79.0      |       |       |  |

|                 |                   |                                                                             | 168                     | 38  | 43.2               | 61.9               | 67.1      |       |       |  |

|                 |                   |                                                                             | 150                     | 37  | 41.8               | 60.3               | 65.4      |       |       |  |

|                 |                   |                                                                             | 144 <sup>(4)</sup>      | 34  | 39.3               | 56.9               | 61.6      |       |       |  |

|                 |                   |                                                                             | 120                     | 29  | 34.3               | 50.2               | 54.4      |       |       |  |

|                 |                   |                                                                             | 90                      | 24  | 28.8               | 43.6               | 47.5      |       |       |  |

|                 |                   | HSI, PLL OFF,                                                               | 60                      | 17  | 22.0               | 35.6               | 39.2      |       |       |  |

|                 |                   | all peripherals disabled <sup>(3)</sup>                                     | 30                      | 10  | 14.8               | 27.0               | 30.1      |       |       |  |

|                 |                   |                                                                             | 25                      | 8   | 13.51              | 25.36              | 28.47     |       |       |  |

|                 |                   |                                                                             | 16                      | 5   | 11.1               | 21.8               | 24.9      |       |       |  |

|                 |                   | HSI, PLL OFF,                                                               | 8                       | 3   | 9.5                | 19.4               | 22.5      |       |       |  |

|                 |                   | all Peripherals disabled <sup>(3)</sup>                                     | 4                       | 2.3 | 8.35               | 18.12              | 21.17     |       |       |  |

|                 |                   |                                                                             | 2                       | 1.8 | 7.78               | 17.42              | 20.51     |       |       |  |

# Table 25. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled)

1. Guaranteed based on test during characterization unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

4. Overdrive OFF

|                                    |                                                                                                               |                                                                                                                                         | Tvn                       |                                          | Max                       |                                           |    |

|------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------|---------------------------|-------------------------------------------|----|

| Symbol                             | Parameter                                                                                                     | Conditions                                                                                                                              | Тур                       | v                                        | Unit                      |                                           |    |

|                                    |                                                                                                               |                                                                                                                                         | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> |    |

|                                    | Supply current in<br>Stop mode with                                                                           | Flash memory in Stop mode, all<br>oscillators OFF, no independent<br>watchdog                                                           | 0.234                     | 1.2                                      | 10                        | 16                                        |    |

| I <sub>DD_STOP_NM</sub><br>(normal | voltage regulator in main regulator mode                                                                      | Flash memory in Deep power<br>down mode, all oscillators OFF,<br>no independent watchdog                                                | 0.205                     | 1                                        | 9.5                       | 15                                        |    |

| mode)                              | Supply current in Stop mode with                                                                              | Flash memory in Stop mode, all<br>oscillators OFF, no independent<br>watchdog                                                           | 0.15                      | 0.95                                     | 8.5                       | 14                                        |    |

|                                    | voltage regulator in<br>Low Power regulator<br>mode                                                           | Flash memory in Deep power<br>down mode, all oscillators OFF,<br>no independent watchdog                                                | 0.121                     | 0.9                                      | 6                         | 12                                        | mA |

| IDD STOP UD                        | Supply current in<br>Stop mode with<br>voltage regulator in<br>main regulator and<br>under-drive mode         | Flash memory in Deep power<br>down mode, main regulator in<br>under-drive mode, all oscillators<br>OFF, no independent watchdog         | 0.119                     | 0.4                                      | 3                         | 5                                         |    |

| M(under-<br>drive mode)            | Supply current in<br>Stop mode with<br>voltage regulator in<br>Low Power regulator<br>and under-drive<br>mode | Flash memory in Deep power<br>down mode, Low Power<br>regulator in under-drive mode,<br>all oscillators OFF, no<br>independent watchdog | 0.055                     | 0.35                                     | 3                         | 5                                         |    |

1. Data based on characterization, tested in production.

|                 |                                 |                            |                         |       |                           | Мах                       |                            |      |

|-----------------|---------------------------------|----------------------------|-------------------------|-------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter                       | Conditions                 | f <sub>HCLK</sub> (MHz) | Тур   | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                                 |                            | 168                     | 65.11 | 70.0                      | 79.7                      | 90.0                       |      |

|                 |                                 | All Peripherals<br>enabled | 150                     | 58.31 | 62.8                      | 73.4                      | 79.9                       |      |

|                 |                                 |                            | 144                     | 53.14 | 57.1                      | 69.9                      | 75.3                       |      |

|                 |                                 |                            | 120                     | 39.58 | 47.2                      | 60.7                      | 71.4                       |      |

|                 |                                 |                            | 90                      | 29.99 | 34.70                     | 45.23                     | 49.34                      | -    |

|                 |                                 |                            | 60                      | 20.37 | 25.2                      | 35.2                      | 38.2                       |      |

|                 |                                 |                            | 30                      | 11.37 | 12.9                      | 28.4                      | 33.2                       |      |

|                 | Supply current in Run mode from |                            |                         | 25    | 9.65                      | 10.9                      | 17.8                       | 24.3 |

| I <sub>DD</sub> | V <sub>DD</sub> supply          |                            | 168                     | 29.74 | 32.43                     | 42.4                      | 48.5                       | -    |

|                 |                                 |                            | 150                     | 25.81 | 29.12                     | 39.4                      | 43.8                       |      |

|                 |                                 |                            | 144                     | 24.57 | 26.61                     | 36.0                      | 41.9                       |      |

|                 |                                 | All Peripherals            | 120                     | 17.69 | 22.09                     | 32.9                      | 40.8                       |      |

|                 |                                 | disabled                   | 90                      | 13.58 | 15.92                     | 30.0                      | 36.5                       |      |

|                 |                                 |                            | 60                      | 9.41  | 11.05                     | 24.4                      | 30.2                       |      |

|                 |                                 |                            | 30                      | 5.44  | 6.64                      | 15.0                      | 22.0                       |      |

|                 |                                 |                            | 25                      | 4.73  | 5.72                      | 12.57                     | 19.06                      |      |

#### Table 30. Typical current consumption in Run mode, code with data processing running from Flash memory or RAM, regulator ON (ART accelerator enabled except prefetch), VDD=1.7 V<sup>(1)</sup>

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

| Symbol                             | Parameter                               | Conditions                                                            | Min  | Тур | Max | Unit |  |  |  |

|------------------------------------|-----------------------------------------|-----------------------------------------------------------------------|------|-----|-----|------|--|--|--|

| f <sub>OSC_IN</sub>                | Oscillator frequency                    | -                                                                     | 4    | -   | 26  | MHz  |  |  |  |

| R <sub>F</sub>                     | Feedback resistor                       | -                                                                     | -    | 200 | -   | kΩ   |  |  |  |

|                                    | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF@25 MHz  | -    | 450 | -   |      |  |  |  |

| IDD                                |                                         | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF@25 MHz | -    | 530 | -   | μA   |  |  |  |

| ACC <sub>HSE</sub> <sup>(2)</sup>  | HSE accuracy                            | -                                                                     | -500 | -   | 500 | ppm  |  |  |  |

| G <sub>m</sub> _crit_max           | Maximum critical crystal g <sub>m</sub> | Startup                                                               | -    | -   | 1   | mA/V |  |  |  |

| t <sub>SU(HSE</sub> <sup>(3)</sup> | Startup time                            | $V_{\text{DD}}$ is stabilized                                         | -    | 2   | -   | ms   |  |  |  |

Table 39 HSF 4-26 MHz oscillator characteristics <sup>(1)</sup>

1. Guaranteed by design.

This parameter depends on the crystal used in the application. The minimum and maximum values must 2. be respected to comply with USB standard specifications.

$t_{{\sf SU}({\sf HSE})}$  is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is Guaranteed based on test during characterization. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. 3.

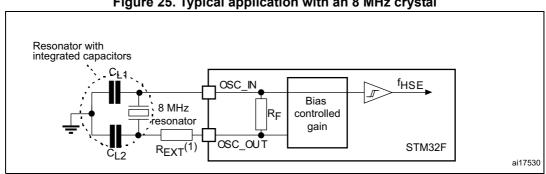

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see Figure 25).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>I 1</sub> and C<sub>I 2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{l,1}$  and  $C_{l,2}$ .

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 25. Typical application with an 8 MHz crystal

R<sub>EXT</sub> value depends on the crystal characteristics. 1.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in Table 40. In the application, the resonator and the load capacitors have to be placed as close as

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> –1 | -    |

Table 46. SSCG parameters constraint

1. Guaranteed by design.

Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL IN} / (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL\_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round $[10^{6}/(4 \times 10^{3})] = 250$

Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

. -

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

$f_{VCO\ OUT}$  must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[

$$((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$$

] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$$md_{quantized}$$

% =  $(250 \times 126 \times 100 \times 5)/((2^{15} - 1) \times 240) = 2.002\%$ (peak)

. \_

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|--|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |  |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | -                                                | 300                | 600  | ms                 |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |  |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | - 700 140          |      |                    | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |  |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 8    | 16                 |      |  |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 5.5  | 11                 | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 8    | 16                 |      |  |

|                         |                            | 32-bit program operation                         | 2.7                | -    | 3.6                | V    |  |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation 2.1 -                   |                    |      |                    | V    |  |

|                         |                            | 8-bit program operation                          | 1.7                | -    | 3.6                | V    |  |

Table 48. Flash memory programming

1. Guaranteed based on test during characterization.

2. The maximum programming time is measured after 100K erase operations.

| Symbol                  | Parameter                  | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>       | Double word programming    |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |

| t <sub>ME</sub>         | Mass erase time            |                              | -                  | 3.5 | -                  | s    |

| V <sub>prog</sub>       | Programming voltage        | -                            | 2.7                | -   | 3.6                | V    |

| Symbol Para      | Parameter  | Conditions                                                                                                                                                   | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ] | Unit |  |

|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|------|--|

|                  |            |                                                                                                                                                              | noquonoy bana               | 8/180 MHz                                        |      |  |

|                  |            | $V_{1} = 2.2 V_{1} T_{2} = 25 \circ C_{1} OED144$                                                                                                            | 0.1 to 30 MHz               | 11                                               |      |  |

|                  |            | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C, LQFP144<br>package, conforming to SAE J1752/3<br>EEMBC, ART ON, all peripheral clocks<br>enabled, clock dithering disabled. | 30 to 130 MHz               | 10                                               | dBµV |  |

|                  |            |                                                                                                                                                              | 130 MHz to 1GHz             | 11                                               |      |  |

| 6                |            |                                                                                                                                                              | SAE EMI Level               | 3                                                | -    |  |

| S <sub>EMI</sub> | Feak level | $V_{DD} = 3.3 \text{ V}, T_A = 25 \text{ °C}, LQFP144$<br>package, conforming to SAE J1752/3                                                                 | 0.1 to 30 MHz               | 24                                               |      |  |

|                  |            |                                                                                                                                                              | 30 to 130 MHz               | 25                                               | dBµV |  |

|                  |            | EEMBC, ART ON, all peripheral clocks enabled, clock dithering enabled                                                                                        | 130 MHz to 1GHz             | 20                                               | ]    |  |

|                  |            |                                                                                                                                                              | SAE EMI level               | 4                                                | -    |  |

#### Table 52. EMI characteristics

## 6.3.15 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings Conditions                                       |                                                                                                               | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model) | $T_A = + 25 \text{ °C conforming to ANSI/JEDEC JS-001}$                                                       | 2     | 2000                            |      |

|                       | Electrostatic                                            | $T_A = +25$ °C conforming to ANSI/ESD STM5.3.1,<br>LQFP64, LQFP100, WLCSP81 packages                          | C4    | 500                             | v    |

| V <sub>ESD(CDM)</sub> | discharge voltage<br>(charge device model)               | $T_A$ = + 25 °C conforming to ANSI/ESD STM5.3.1,<br>LQFP144, UFBGA144 (7 x 7), UFBGA144 (10 x 10)<br>packages | C3    | 250                             |      |

| Table 53. ESD | ) absolute | maximum | ratings |

|---------------|------------|---------|---------|

|---------------|------------|---------|---------|

1. Guaranteed based on test during characterization.

## Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

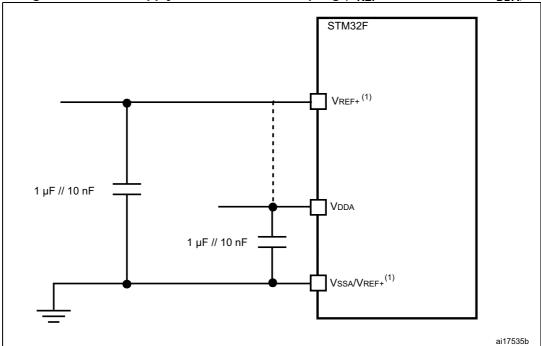

#### General PCB design guidelines

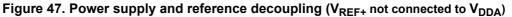

Power supply decoupling should be performed as shown in *Figure 47* or *Figure 48*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are both available on UFBGA144.  $V_{REF+}$  is also available on LQFP100, LQFP144, and WLCSP81. When  $V_{REF+}$  and  $V_{REF-}$  are not available, they are internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

| Symbol                             | Parameter                                                                                                                        | Conditions | Min | Тур  | Max  | Unit     | Comments                                                                                               |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|------|----------|--------------------------------------------------------------------------------------------------------|

|                                    | Integral non<br>linearity (difference                                                                                            | -          | -   | -    | ±1   | LSB      | Given for the DAC in 10-bit configuration.                                                             |

| INL <sup>(4)</sup>                 | between<br>measured value at<br>Code i and the<br>value at Code i on<br>a line drawn<br>between Code 0<br>and last Code<br>1023) | -          | -   | -    | ±4   | LSB      | Given for the DAC in 12-bit configuration.                                                             |

|                                    | Offset error<br>(difference                                                                                                      | -          | -   | -    | ±10  | mV       | Given for the DAC in 12-bit configuration                                                              |

| Offset <sup>(4)</sup>              | between<br>measured value at<br>Code (0x800) and                                                                                 | -          | -   | -    | ±3   | LSB      | Given for the DAC in 10-bit at $V_{REF+}$ = 3.6 V                                                      |

|                                    | the ideal value =<br>V <sub>REF+</sub> /2)                                                                                       | -          | -   | -    | ±12  | LSB      | Given for the DAC in 12-bit at $V_{REF+}$ = 3.6 V                                                      |

| Gain<br>error <sup>(4)</sup>       | Gain error                                                                                                                       | -          | -   | -    | ±0.5 | %        | Given for the DAC in 12-bit configuration                                                              |

| tsettfing <sup>(4</sup>            | Total Harmonic<br>Distortion<br>Buffer ON                                                                                        | -          | -   | 3    | 6    | μs       | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                      |

| THD <sup>(4)</sup>                 | -                                                                                                                                | -          | -   | -    | -    | dB       | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                      |

| Update<br>rate <sup>(2)</sup>      | Max frequency for<br>a correct<br>DAC_OUT change<br>when small<br>variation in the<br>input code (from<br>code i to i+1LSB)      | -          | -   | -    | 1    | MS/<br>s | C <sub>LOAD</sub> ≤50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                  |

| t <sub>WAKEUP</sub> <sup>(4)</sup> | Wakeup time from<br>off state (Setting<br>the ENx bit in the<br>DAC Control<br>register)                                         | -          | -   | 6.5  | 10   | μs       | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5$ k $\Omega$ input code between lowest and highest possible ones. |

| PSRR+ <sup>(2)</sup>               | Power supply<br>rejection ratio (to<br>V <sub>DDA</sub> ) (static DC<br>measurement)                                             | -          | -   | - 67 | - 40 | dB       | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                       |

Table 85. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.16.2: Internal reset OFF).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed based on test during characterization.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

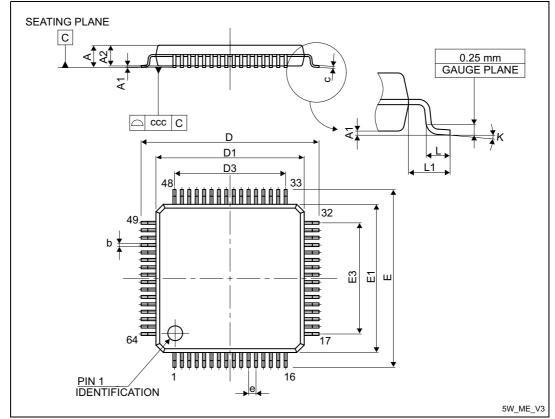

## 7.1 LQFP64 package information

Figure 67. LQFP64-10x10 mm 64 pin low-profile quad flat package outline

1. Drawing is not to scale

#### Table 108. LQFP64 – 10 x 10 mm low-profile quad flat package mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| с      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

# Appendix A Application block diagrams

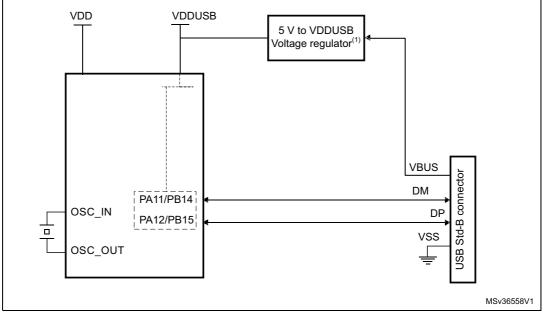

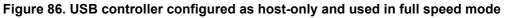

## A.1 USB OTG full speed (FS) interface solutions

1. External voltage regulator only needed when building a  $V_{\mbox{BUS}}$  powered device.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.