# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                                |

| Speed                      | 180MHz                                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 81                                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                             |

| EEPROM Size                | -                                                                                                 |

| RAM Size                   | 128K x 8                                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                       |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                             |

| Oscillator Type            | Internal                                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                |

| Mounting Type              | Surface Mount                                                                                     |

| Package / Case             | 100-LQFP                                                                                          |

| Supplier Device Package    | 100-LQFP (14x14)                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f446vct7                             |

|                            |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | Compatible board design for LQFP100 package                              | 14  |

|------------|--------------------------------------------------------------------------|-----|

| Figure 2.  | Compatible board for LQFP64 package                                      | 15  |

| Figure 3.  | STM32F446xC/E block diagram                                              | 16  |

| Figure 4.  | STM32F446xC/E and Multi-AHB matrix                                       | 19  |

| Figure 5.  | VDDUSB connected to an external independent power supply                 | 23  |

| Figure 6.  | Power supply supervisor interconnection with internal reset OFF          |     |

| Figure 7.  | Regulator OFF                                                            |     |

| Figure 8.  | Startup in regulator OFF: slow V <sub>DD</sub> slope                     |     |

| -          | power-down reset risen after $V_{CAP_1}/V_{CAP_2}$ stabilization         | 27  |

| Figure 9.  | Startup in regulator OFF mode: fast V <sub>DD</sub> slope                |     |

| -          | power-down reset risen before $V_{CAP_1} N_{CAP_2}$ stabilization        | 27  |

| Figure 10. | STM32F446xC/xE LQFP64 pinout                                             | 41  |

| Figure 11. | STM32F446xC/xE LQFP100 pinout                                            |     |

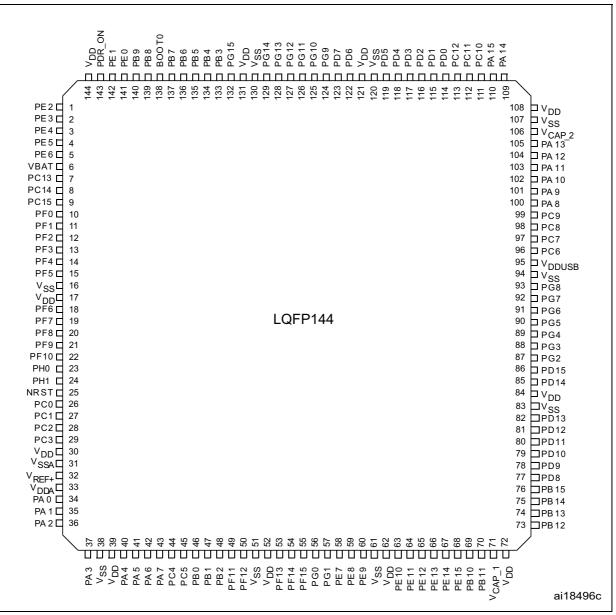

| Figure 12. | STM32F446xC LQFP144 pinout                                               |     |

| Figure 13. | STM32F446xC/xE WLCSP81 ballout                                           |     |

| Figure 14. | STM32F446xC/xE UFBGA144 ballout                                          |     |

| Figure 15. | Memory map                                                               |     |

| Figure 16. | Pin loading conditions                                                   |     |

| Figure 17. | Pin input voltage                                                        |     |

| Figure 18. | Power supply scheme                                                      |     |

| Figure 19. | Current consumption measurement scheme                                   |     |

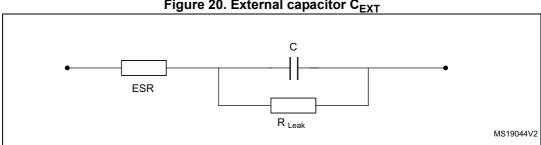

| Figure 20. | External capacitor C <sub>FXT</sub>                                      |     |

| Figure 21. | Typical V <sub>BAT</sub> current consumption                             |     |

|            | (RTC ON/backup RAM OFF and LSE in low power mode)                        | 91  |

| Figure 22. | Typical V <sub>BAT</sub> current consumption                             |     |

|            | (RTC ON/backup RAM OFF and LSE in high drive mode)                       | 92  |

| Figure 23. | High-speed external clock source AC timing diagram                       |     |

| Figure 24. | Low-speed external clock source AC timing diagram                        |     |

| Figure 25. | Typical application with an 8 MHz crystal                                |     |

| Figure 26. | Typical application with a 32.768 kHz crystal                            |     |

| Figure 27. | LACC <sub>HSI</sub> versus temperature                                   |     |

| Figure 28. | ACC <sub>LSI</sub> versus temperature                                    |     |

| Figure 29. | PLL output clock waveforms in center spread mode                         |     |

| Figure 30. | PLL output clock waveforms in down spread mode                           |     |

| Figure 31. | FT I/O input characteristics.                                            |     |

| Figure 32. | I/O AC characteristics definition                                        |     |

| Figure 33. | Recommended NRST pin protection                                          |     |

| Figure 34. | I <sup>2</sup> C bus AC waveforms and measurement circuit                |     |

| Figure 35. | FMPI <sup>2</sup> C timing diagram and measurement circuit               |     |

| Figure 36. | SPI timing diagram - slave mode and CPHA = 0                             |     |

| Figure 37. | SPI timing diagram - slave mode and CPHA = 1                             |     |

| Figure 38. |                                                                          |     |

| Figure 39. | SPI timing diagram - master mode                                         | 135 |

| Figure 40. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup> | 135 |

| Figure 41. | SAI master timing waveforms                                              |     |

| Figure 42. | SAI slave timing waveforms                                               |     |

| Figure 43. | USB OTG full speed timings: definition of data signal rise and fall time |     |

| Figure 44. | ULPI timing diagram                                                      |     |

|            |                                                                          |     |

# 2 Description

The STM32F446xC/E devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 180 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F446xC/E devices incorporate high-speed embedded memories (Flash memory up to 512 Kbyte, up to 128 Kbyte of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers.

They also feature standard and advanced communication interfaces.

- Up to four I<sup>2</sup>Cs;

- Four SPIs, three I<sup>2</sup>Ss full simplex. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization;

- Four USARTs plus two UARTs;

- An USB OTG full-speed and an USB OTG high-speed with full-speed capability (with the ULPI), both with dedicated power rails allowing to use them throughout the entire power range;

- Two CANs;

- Two SAIs serial audio interfaces. To achieve audio class accuracy, the SAIs can be clocked via a dedicated internal audio PLL;

- An SDIO/MMC interface;

- Camera interface;

- HDMI-CEC;

- SPDIF Receiver (SPDIFRx);

- QuadSPI.

Advanced peripherals include an SDIO, a flexible memory control (FMC) interface, a camera interface for CMOS sensors. Refer to *Table 2: STM32F446xC/E features and peripheral counts* for the list of peripherals available on each part number.

The STM32F446xC/E devices operates in the -40 to +105 °C temperature range from a 1.7 to 3.6 V power supply.

The supply voltage can drop to 1.7 V with the use of an external power supply supervisor (refer to *Section 3.16.2: Internal reset OFF*). A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F446xC/E devices offer devices in 6 packages ranging from 64 pins to 144 pins. The set of included peripherals changes with the device chosen.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

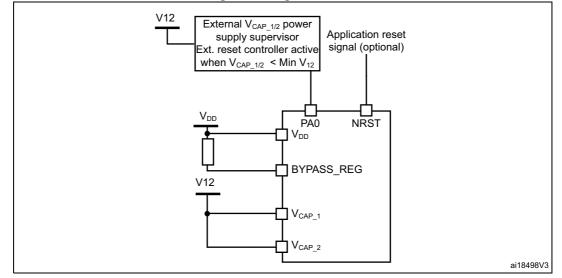

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

### Figure 7. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach  $V_{12}$  minimum value is faster than the time for  $V_{DD}$  to reach 1.7 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach  $V_{12}$  minimum value and until  $V_{DD}$  reaches 1.7 V (see *Figure 8*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 9*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application.

# 3.23 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and four universal asynchronous receiver transmitters (UART4, and UART5).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 11.25 Mbit/s. The other available interfaces communicate at up to 5.62 bit/s.

USART1, USART2, USART3 and USART6 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

| USART<br>name | Standard<br>features | Modem<br>(RTS/CTS) | LIN | SPI<br>maste<br>r | irD<br>A | Smartcard<br>(ISO 7816) | Max. baud<br>rate in Mbit/s<br>(oversamplin<br>g by 16) | Max. baud<br>rate in Mbit/s<br>(oversamplin<br>g by 8) | APB<br>mapping           |

|---------------|----------------------|--------------------|-----|-------------------|----------|-------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------|

| USART1        | х                    | х                  | х   | х                 | х        | х                       | 5.62                                                    | 11.25                                                  | APB2<br>(max.<br>90 MHz) |

| USART2        | х                    | х                  | х   | х                 | х        | х                       | 2.81                                                    | 5.62                                                   | APB1<br>(max.<br>45 MHz) |

| USART3        | х                    | х                  | х   | х                 | х        | х                       | 2.81                                                    | 5.62                                                   | APB1<br>(max.<br>45 MHz) |

| UART4         | х                    | х                  | х   | -                 | х        | -                       | 2.81                                                    | 5.62                                                   | APB1<br>(max.<br>45 MHz) |

| UART5         | х                    | х                  | х   | -                 | х        | -                       | 2.81                                                    | 5.62                                                   | APB1<br>(max.<br>45 MHz) |

| USART6        | х                    | Х                  | х   | х                 | х        | Х                       | 5.62                                                    | 11.25                                                  | APB2<br>(max.<br>90 MHz) |

| T-1-1-0  |       | f       | comparison <sup>(1</sup> | ١ |

|----------|-------|---------|--------------------------|---|

| Table 8. | USARI | teature | comparison               | , |

1. X = feature supported.

# 3.24 Serial peripheral interface (SPI)

The devices feature up to four SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1, and SPI4 can communicate at up to 45 Mbits/s, SPI2 and SPI3 can communicate at up to 22.5 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

DocID027107 Rev 6

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

# 3.32 Controller area network (bxCAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). 256 bytes of SRAM are allocated for each CAN.

# 3.33 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The USB has dedicated power rails allowing its use throughout the entire power range. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

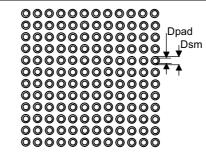

# 3.34 Universal serial bus on-the-go high-speed (OTG\_HS)

The devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The USB has dedicated power rails allowing its use throughout the entire power range.

Figure 12. STM32F446xC LQFP144 pinout

1. The above figure shows the package top view.

|        | Piı     | n Nun    | nber     |         |                                    |          |               |       |                                                                                                |                         |

|--------|---------|----------|----------|---------|------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | WLCSP 81 | UFBGA144 | LQFP144 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                            | Additional<br>functions |

| 51     | 78      | D3       | B11      | 111     | PC10                               | I/O      | FT            | -     | SPI3_SCK/I2S3_CK,<br>USART3_TX, UART4_TX,<br>QUADSPI_BK1_IO1,<br>SDIO_D2, DCMI_D8,<br>EVENTOUT | -                       |

| 52     | 79      | D4       | B10      | 112     | PC11                               | I/O      | FT            | -     | SPI3_MISO, USART3_RX,<br>UART4_RX,<br>QUADSPI_BK2_NCS,<br>SDIO_D3, DCMI_D4,<br>EVENTOUT        | -                       |

| 53     | 80      | A2       | C10      | 113     | PC12                               | I/O      | FT            | Ι     | I2C2_SDA,<br>SPI3_MOSI/I2S3_SD,<br>USART3_CK, UART5_TX,<br>SDIO_CK, DCMI_D9,<br>EVENTOUT       | -                       |

| -      | 81      | В3       | E10      | 114     | PD0                                | I/O      | FT            | -     | SPI4_MISO,<br>SPI3_MOSI/I2S3_SD,<br>CAN1_RX, FMC_D2,<br>EVENTOUT                               | -                       |

| -      | 82      | C4       | D10      | 115     | PD1                                | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>CAN1_TX, FMC_D3,<br>EVENTOUT                                              | -                       |

| 54     | 83      | D5       | E9       | 116     | PD2                                | I/O      | FT            | -     | TIM3_ETR, UART5_RX,<br>SDIO_CMD, DCMI_D11,<br>EVENTOUT                                         | -                       |

| -      | 84      | -        | D9       | 117     | PD3                                | I/O      | FT            | -     | TRACED1,<br>SPI2_SCK/I2S2_CK,<br>USART2_CTS,<br>QUADSPI_CLK,<br>FMC_CLK, DCMI_D5,<br>EVENTOUT  | -                       |

| -      | 85      | A3       | C9       | 118     | PD4                                | I/O      | FT            | -     | USART2_RTS, FMC_NOE,<br>EVENTOUT                                                               | -                       |

| -      | 86      | -        | B9       | 119     | PD5                                | I/O      | FT            | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                                | -                       |

| -      | -       | -        | E7       | 120     | VSS                                | S        | -             | -     | -                                                                                              | -                       |

| -      | -       | -        | F7       | 121     | VDD                                | S        | -             | -     | -                                                                                              | -                       |

Table 10. STM32F446xx pin and ball descriptions (continued)

Figure 20. External capacitor C<sub>EXT</sub>

1. Legend: ESR is the equivalent series resistance.

| Symbol           | Parameter                                                                      | Conditions |

|------------------|--------------------------------------------------------------------------------|------------|

| C <sub>EXT</sub> | Capacitance of external capacitor                                              | 2.2 μF     |

| ESR              | ESR of external capacitor                                                      | < 2 Ω      |

| C <sub>EXT</sub> | Capacitance of external capacitor with a single $V_{\text{CAP}}$ pin available | 4.7 µF     |

| ESR              | ESR of external capacitor with a single $V_{\mbox{CAP}}$ pin available         | < 1 Ω      |

## Table 18. VCAP\_1/VCAP\_2 operating conditions<sup>(1)</sup>

When bypassing the voltage regulator, the two 2.2  $\mu F$  V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors. 1.

#### 6.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for T<sub>A</sub>.

### Table 19. Operating conditions at power-up/power-down (regulator ON)

|  | Symbol           | Parameter                      | Min | Max |

|--|------------------|--------------------------------|-----|-----|

|  | t <sub>VDD</sub> | V <sub>DD</sub> rise time rate | 20  | ∞   |

|  |                  | V <sub>DD</sub> fall time rate | 20  | ∞   |

#### Operating conditions at power-up / power-down (regulator OFF) 6.3.4

Subject to general operating conditions for T<sub>A</sub>.

## Table 20. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit  |

|-------------------|----------------------------------------------|------------|-----|-----|-------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate               | Power-up   | 20  | ~   |       |

|                   | V <sub>DD</sub> fall time rate               | Power-down | 20  | 8   | µs/V  |

| +                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | 8   | μ5/ ν |

| <sup>t</sup> VCAP | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | 8   |       |

To reset the internal logic at power-down, a reset must be applied on pin PA0 when V<sub>DD</sub> reach below 1.08 V. 1.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> –1 | -    |

Table 46. SSCG parameters constraint

1. Guaranteed by design.

Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL IN} / (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL\_IN}$  = 1 MHz, and  $f_{MOD}$  = 1 kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round $[10^{6}/(4 \times 10^{3})] = 250$

Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

. -

. -

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

$f_{VCO\ OUT}$  must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[

$$((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$$

] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$$md_{quantized}$$

% =  $(250 \times 126 \times 100 \times 5)/((2^{15} - 1) \times 240) = 2.002\%$ (peak)

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |

| t <sub>erase64kb</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |

|                         | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |

| t <sub>ERASE128KB</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 8    | 16                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 5.5  | 11                 | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 8    | 16                 |      |

|                         |                            | 32-bit program operation                         | 2.7                | -    | 3.6                | V    |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation                         | 2.1                | -    | 3.6                | V    |

|                         |                            | 8-bit program operation                          | 1.7                | -    | 3.6                | V    |

Table 48. Flash memory programming

1. Guaranteed based on test during characterization.

2. The maximum programming time is measured after 100K erase operations.

| Table 49. Flash memory | programming v | with V <sub>PP</sub> |

|------------------------|---------------|----------------------|

|------------------------|---------------|----------------------|

|                         | 1                          |                                                         |                    | · · · · · · · · · · · · · · · · · · · |                    |      |

|-------------------------|----------------------------|---------------------------------------------------------|--------------------|---------------------------------------|--------------------|------|

| Symbol                  | Parameter                  | Conditions                                              | Min <sup>(1)</sup> | Тур                                   | Max <sup>(1)</sup> | Unit |

| t <sub>prog</sub>       | Double word programming    | T <sub>A</sub> = 0 to +40 °C<br>V <sub>DD</sub> = 3.3 V | -                  | 16                                    | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  |                                                         | -                  | 230                                   | -                  |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  |                                                         | -                  | 490                                   | -                  | ms   |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | V <sub>PP</sub> = 8.5 V                                 | -                  | 875                                   | -                  |      |

| t <sub>ME</sub>         | Mass erase time            |                                                         | -                  | 3.5                                   | -                  | s    |

| V <sub>prog</sub>       | Programming voltage        | -                                                       | 2.7                | -                                     | 3.6                | V    |

# 6.3.17 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 56: I/O static characteristics* are derived from tests performed under the conditions summarized in *Table 16*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                                         | Conditions Min                                                                                                    |                                                                              | Тур                | Мах                                                                         | Unit |

|------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------|------|

|                  | FT, FTf, TTa and NRST I/O input low level voltage                 | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                                                                      | -                                                                            | -                  | $0.35V_{DD} - 0.04^{(1)}$                                                   |      |

| V <sub>IL</sub>  | BOOT0 I/O input low level voltage                                 | $1.75 V \le V_{DD} \le$<br>3.6 V,<br>- 40 °C $\le T_A \le$<br>105 °C                                              | 3.6 V,<br>- 40 $^{\circ}C \le T_{A} \le$ -                                   |                    | 0.3V <sub>DD</sub> <sup>(2)</sup><br>0.1V <sub>DD</sub> +0.1 <sup>(1)</sup> | v    |

|                  |                                                                   | $\begin{array}{l} 1.7 \ V \leq V_{DD} \leq 3.6 \ V, \\ 0 \ ^{\circ}C \leq T_{A} \leq 105 \ ^{\circ}C \end{array}$ | -                                                                            | -                  |                                                                             |      |

|                  | FT, FTf, TTa and NRST I/O input high level voltage <sup>(4)</sup> | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                                                                      | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup><br>0.7V <sub>DD</sub> <sup>(2)</sup> | -                  |                                                                             |      |

| V <sub>IH</sub>  | BOOT0 I/O input high level voltage                                | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>– 40 °C≤T <sub>A</sub> ≤105 °C                                                  | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup>                                      | _                  | _                                                                           | V    |

|                  |                                                                   | 1.7 V⊴V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C                                                      | 0.17 000.0.7                                                                 |                    |                                                                             |      |

|                  | FT, FTf, TTa and NRST I/O input hysteresis                        | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                                                                      | -                                                                            | 10%V <sub>DD</sub> | -                                                                           |      |

| V <sub>HYS</sub> | BOOT0 I/O input hysteresis                                        | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>–40 °C≤T <sub>A</sub> ≤105 °C                                                   | -                                                                            | 100m               | -                                                                           | v    |

|                  |                                                                   | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C                                                      | -                                                                            | TUUIII             | -                                                                           |      |

|                  | I/O input leakage current <sup>(3)</sup>                          | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>                                                                 | -                                                                            | -                  | ±1                                                                          |      |

| l <sub>lkg</sub> | I/O FT input leakage current                                      | V <sub>IN</sub> = 5 V                                                                                             | -                                                                            | -                  | 3                                                                           | μA   |

| Table 56 | I/O static | characteristics |

|----------|------------|-----------------|

| 10010 00 |            |                 |

### **Electrical characteristics**

| OSPEEDR<br>y[1:0] bit<br>value <sup>(1)</sup> | Symbol                      | Parameter                                                       | Conditions                                      | Min                                             | Тур    | Мах                | Unit               |     |

|-----------------------------------------------|-----------------------------|-----------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------|--------------------|--------------------|-----|

| value                                         |                             |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 25                 |                    |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.8 V | -                                               | -      | 12.5               |                    |     |

|                                               |                             | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 10                 |                    |     |

|                                               | f <sub>max(IO)</sub> out    |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 50                 | MHz                |     |

| 04                                            |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -                                               | -      | 20                 |                    |     |

| 01                                            |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 12.5               |                    |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 10                 |                    |     |

|                                               | t <sub>f(IO)out</sub> /     | Output high to low level fall                                   | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 6                  |                    |     |

|                                               | t <sub>r(IO)out</sub>       | time and output low to high level rise time                     | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 20                 | ns                 |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 10                 |                    |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 50 <sup>(4)</sup>  |                    |     |

|                                               |                             | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 100 <sup>(4)</sup> |                    |     |

|                                               | f <sub>max(IO)out</sub>     |                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 25                 | MHz                |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -                                               | -      | 50                 |                    |     |

| 10                                            |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 42.5               |                    |     |

|                                               |                             | Output high to low level fall                                   | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥2.7 V  | -                                               | -      | 6                  |                    |     |

|                                               | t <sub>f(IO)out</sub> /     |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 4                  |                    |     |

|                                               | t <sub>r(IO)out</sub>       | time and output low to high level rise time                     | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 10                 | ns                 |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 6                  |                    |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 100 <sup>(4)</sup> |                    |     |

|                                               | f <sub>max(IO)out</sub> Max |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.8 V | -                                               | -      | 50                 |                    |     |

|                                               |                             | f <sub>max(IO)out</sub> Maximum frequency <sup>(3)</sup>        | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | -      | 42.5               |                    |     |

|                                               |                             |                                                                 | Maximum frequency.                              | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -      | -                  | 180 <sup>(4)</sup> | MHz |

|                                               |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -                                               | -      | 100                |                    |     |

| 44                                            |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -                                               | - 72.5 | 72.5               |                    |     |

| 11                                            |                             |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 4                  |                    |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.8 V  | -                                               | -      | 6                  |                    |     |

|                                               | t <sub>f(IO)out</sub> /     | Output high to low level fall                                   | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.7 V  | -                                               | -      | 7                  |                    |     |

|                                               | t <sub>r(IO)out</sub>       | time and output low to high level rise time                     | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -                                               | -      | 2.5                | ns                 |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.8 V  | -                                               | -      | 3.5                |                    |     |

|                                               |                             |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.7 V  | -                                               | -      | 4                  |                    |     |

| -                                             | t <sub>EXTIpw</sub>         | Pulse width of external signals detected by the EXTI controller | -                                               | 10                                              | -      | -                  | ns                 |     |

Table 58. I/O AC characteristics<sup>(1)(2)</sup> (continued)

DocID027107 Rev 6

- 1. Guaranteed by design.

- 2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

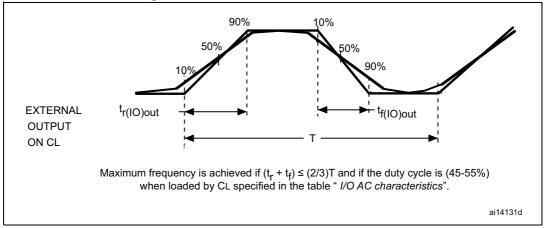

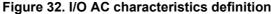

- 3. The maximum frequency is defined in *Figure* 32.

- 4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

## 6.3.18 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 56: I/O static characteristics*).

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 59. NRST pin characteristics

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

2. Guaranteed by design.

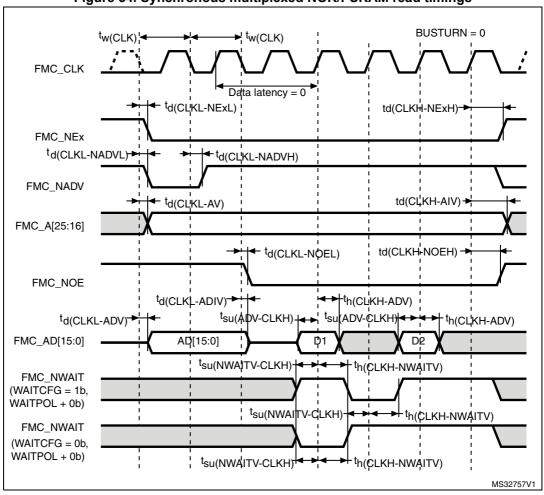

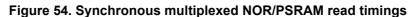

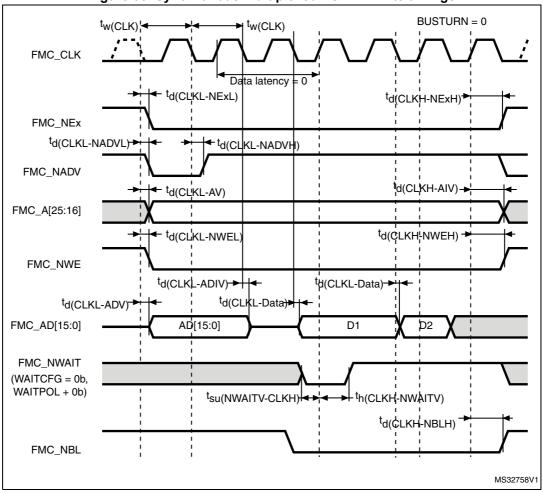

In all timing tables, the T<sub>HCLK</sub> is the HCLK clock period (with maximum FMC\_CLK = 90 MHz).

Figure 55. Synchronous multiplexed PSRAM write timings

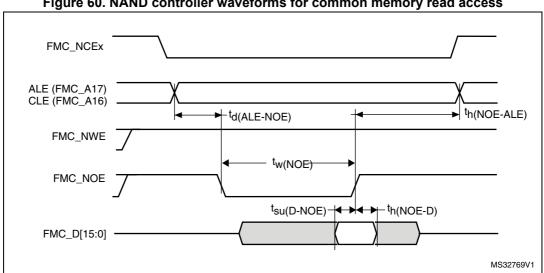

Figure 60. NAND controller waveforms for common memory read access

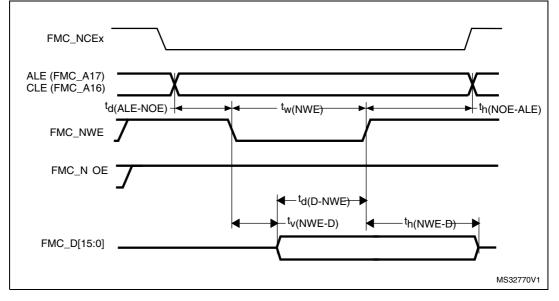

Figure 61. NAND controller waveforms for common memory write access

Table 98. Switching characteristics for NAND Flash read cycles<sup>(1)</sup>

| Symbol                  | Parameter                                  | Min                      | Max                      | Unit |

|-------------------------|--------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(N0E)</sub>     | FMC_NOE low width                          | 4T <sub>HCLK</sub> – 0.5 | 4T <sub>HCLK</sub> + 0.5 |      |

| t <sub>su(D-NOE)</sub>  | FMC_D[15-0] valid data before FMC_NOE high | 9                        | -                        |      |

| t <sub>h(NOE-D)</sub>   | FMC_D[15-0] valid data after FMC_NOE high  | 2.5                      | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> | FMC_ALE valid before FMC_NOE low           | -                        | 3T <sub>HCLK</sub> - 0.5 |      |

| t <sub>h(NOE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid            | 3T <sub>HCLK</sub> – 2   | -                        |      |

1. C<sub>L</sub> = 30 pF.

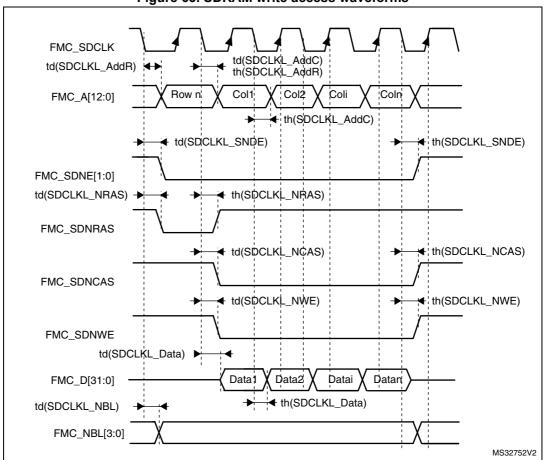

Figure 63. SDRAM write access waveforms

| Symbol                        | Parameter              | Min                      | Max                      | Unit |

|-------------------------------|------------------------|--------------------------|--------------------------|------|

| F <sub>(SDCLK)</sub>          | Frequency of operation | -                        | 90                       | MHz  |

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> - 0.5 | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>d(SDCLKL _Data)</sub>  | Data output valid time | -                        | 2                        |      |

| t <sub>h(SDCLKL</sub> _Data)  | Data output hold time  | 0.5                      | -                        |      |

| t <sub>d(SDCLK _Add)</sub>    | Address valid time     | -                        | 3                        |      |

| $t_{d(SDCLKL SDNWE)}$         | SDNWE valid time       | -                        | 1.5                      |      |

| t <sub>h(SDCLKL_SDNWE))</sub> | SDNWE hold time        | 0                        | -                        | ns   |

| $t_{d(SDCLKL_SDNE)}$          | Chip select valid time | -                        | 1.5                      | 115  |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0                        | -                        |      |

| $t_{d(SDCLKL\_SDNRAS)}$       | SDNRAS valie time      | -                        | 1                        |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                        | ]    |

| $t_{d(SDCLKL\_SDNCAS)}$       | SDNCAS valid time      | -                        | 1                        | ]    |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                        | -                        |      |

1.  $C_L = 10 \text{ pF}$  on data and address line.  $C_L = 15 \text{ pF}$  on FMC\_SDCLK.

2. Guaranteed based on test during characterization.

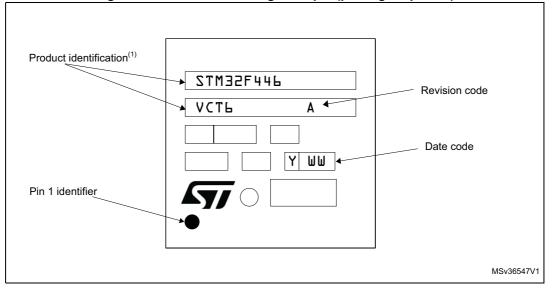

## Device marking for LQFP100 package

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# Table 113. UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ballgrid array package mechanical data (continued)

| Symbol |       | millimeters |       |        |        |        |

|--------|-------|-------------|-------|--------|--------|--------|

| Symbol | Min.  | Тур.        | Max.  | Min.   | Тур.   | Max.   |

| F      | 0.550 | 0.600       | 0.650 | 0.0177 | 0.0197 | 0.0217 |

| ddd    | -     | -           | 0.080 | -      | -      | 0.0039 |

| eee    | -     | -           | 0.150 | -      | -      | 0.0059 |

| fff    | -     | -           | 0.080 | -      | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

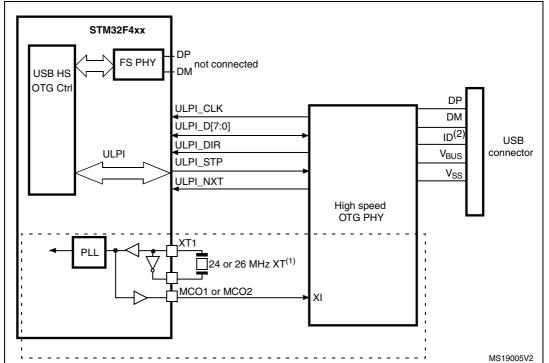

# Figure 80. UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball grid array package recommended footprint

A02Y\_FP\_V1

### Table 114. UFBGA144 recommended PCB design rules (0.80 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.80 mm                                                          |

| Dpad              | 0.400 mm                                                         |

| Dsm               | 0.550 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.400 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Pad trace width   | 0.120 mm                                                         |

# A.2 USB OTG high speed (HS) interface solutions

Figure 88. USB controller configured as peripheral, host, or dual-mode and used in high speed mode

It is possible to use MCO1 or MCO2 to save a crystal. It is however not mandatory to clock the STM32F446xx with a 24 or 26 MHz crystal when using USB HS. The above figure only shows an example of a possible connection.

2. The ID pin is required in dual role only.