Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                                |

| Speed                      | 180MHz                                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 114                                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                             |

| EEPROM Size                | -                                                                                                 |

| RAM Size                   | 128K x 8                                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                             |

| Oscillator Type            | Internal                                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                     |

| Package / Case             | 144-UFBGA                                                                                         |

| Supplier Device Package    | -                                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f446zch6                             |

|                            |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.  | Device summary                                                                 | 1     |

|-----------|--------------------------------------------------------------------------------|-------|

| Table 2.  | STM32F446xC/E features and peripheral counts                                   | 13    |

| Table 3.  | Voltage regulator configuration mode versus device operating mode              | 25    |

| Table 4.  | Regulator ON/OFF and internal reset ON/OFF availability.                       | 27    |

| Table 5.  | Voltage regulator modes in stop mode                                           | 29    |

| Table 6.  | Timer feature comparison                                                       | 31    |

| Table 7.  | Comparison of I2C analog and digital filters                                   | 33    |

| Table 8.  | USART feature comparison                                                       | 34    |

| Table 9.  | Legend/abbreviations used in the pinout table                                  | 46    |

| Table 10. | STM32F446xx pin and ball descriptions                                          | 46    |

| Table 11. | Alternate function                                                             | 59    |

| Table 12. | STM32F446xC/E register boundary addresses                                      | 68    |

| Table 13. | Voltage characteristics                                                        | 74    |

| Table 14. | Current characteristics                                                        | 75    |

| Table 15. | Thermal characteristics.                                                       | 75    |

| Table 16. | General operating conditions                                                   | 76    |

| Table 17. | Limitations depending on the operating power supply range                      | 78    |

| Table 18. | VCAP_1/VCAP_2 operating conditions                                             |       |

| Table 19. | Operating conditions at power-up/power-down (regulator ON)                     |       |

| Table 20. | Operating conditions at power-up / power-down (regulator OFF).                 |       |

| Table 21. | reset and power control block characteristics                                  |       |

| Table 22. | Over-drive switching characteristics                                           |       |

| Table 23. | Typical and maximum current consumption in Run mode, code with data processing |       |

|           | running from Flash memory (ART accelerator enabled except prefetch) or RAM.    | 83    |

| Table 24. | Typical and maximum current consumption in Run mode, code with data processing |       |

|           | running from Flash memory (ART accelerator enabled with prefetch) or RAM       | 84    |

| Table 25. | Typical and maximum current consumption in Run mode, code with data processing |       |

|           | running from Flash memory (ART accelerator disabled)                           | 85    |

| Table 26. | Typical and maximum current consumption in Sleep mode                          | 86    |

| Table 27. | Typical and maximum current consumptions in Stop mode                          |       |

| Table 28. | Typical and maximum current consumptions in Standby mode                       | 90    |

| Table 29. | Typical and maximum current consumptions in V <sub>BAT</sub> mode              | 91    |

| Table 30. | Typical current consumption in Run mode, code with data processing             |       |

|           | running from Flash memory or RAM, regulator ON                                 |       |

|           | (ART accelerator enabled except prefetch), VDD=1.7 V                           | 93    |

| Table 31. | Typical current consumption in Run mode, code with data processing running     |       |

|           | from Flash memory, regulator OFF (ART accelerator enabled except prefetch)     | 94    |

| Table 32. | Typical current consumption in Sleep mode, regulator ON, VDD=1.7 V             | 95    |

| Table 33. | Typical current consumption in Sleep mode, regulator OFF.                      |       |

| Table 34. | Switching output I/O current consumption                                       |       |

| Table 35. | Peripheral current consumption                                                 | 99    |

| Table 36. | Low-power mode wakeup timings                                                  | . 102 |

| Table 37. | High-speed external user clock characteristics.                                |       |

| Table 38. | Low-speed external user clock characteristics                                  |       |

| Table 39. | HSE 4-26 MHz oscillator characteristics                                        |       |

| Table 40. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                 |       |

| Table 41. | HSI oscillator characteristics                                                 |       |

| Table 42. | LSI oscillator characteristics                                                 | . 108 |

# 1 Introduction

This document provides the description of the STM32F446xC/E products.

The STM32F446xC/E document should be read in conjunction with the STM32F4xx reference manual.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214), available from the *www.st.com*.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

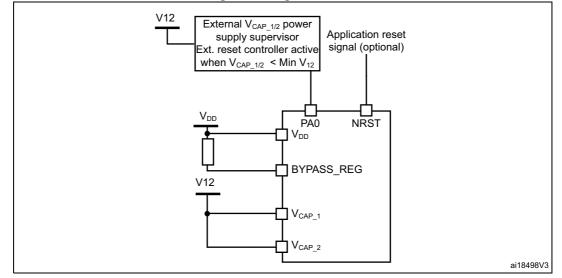

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

#### Figure 7. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach  $V_{12}$  minimum value is faster than the time for  $V_{DD}$  to reach 1.7 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach  $V_{12}$  minimum value and until  $V_{DD}$  reaches 1.7 V (see *Figure 8*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 9*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application.

The SPDIF-RX also offers a signal named spdifrx\_frame\_sync, which toggles at the S/PDIF sub-frame rate that will be used to compute the exact sample rate for clock drift algorithms.

## 3.28 Serial Audio interface (SAI)

The devices feature two serial audio interfaces (SAI1 and SAI2). Each serial audio interfaces based on two independent audio sub blocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both sub blocks can be configured in master or in slave mode. The SAIs use a PLL to achieve audio class accuracy.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub blocks can be configured in synchronous mode when full-duplex mode is required.

SAI1 and SA2 can be served by the DMA controller.

# 3.29 Audio PLL (PLLI<sup>2</sup>S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the  $I^2S/SAI$  flow with an external PLL (or Codec output).

## 3.30 Serial Audio Interface PLL(PLLSAI)

An additional PLL dedicated to audio and USB is used for SAI1 and SAI2 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the 48MHz clock for USB FS and SDIO in case the system PLL is programmed with factors not multiple of 48MHz.

## 3.31 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 3.41 Embedded Trace Macrocell<sup>™</sup>

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F446xx through a small number of ETM pins to an external hardware trace port analyser (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

5

DocID027107 Rev 6

59/202

|        |      |                |                       |          |                          |                    | Tab                       | ole 11. A                | Iternate                                        | functio                                | n                                     |                                          |         |                          |                 |      |              |

|--------|------|----------------|-----------------------|----------|--------------------------|--------------------|---------------------------|--------------------------|-------------------------------------------------|----------------------------------------|---------------------------------------|------------------------------------------|---------|--------------------------|-----------------|------|--------------|

|        |      | AF0            | AF1                   | AF2      | AF3                      | AF4                | AF5                       | AF6                      | AF7                                             | AF8                                    | AF9                                   | AF10                                     | AF11    | AF12                     | AF13            | AF14 | AF15         |

| Po     | ort  | SYS            | TIM1/2                | TIM3/4/5 | TIM8/9/<br>10/11/<br>CEC | I2C1/2/3<br>/4/CEC | SPI1/2/3/<br>4            | SPI2/3/4/<br>SAI1        | SPI2/3/<br>USART1/<br>2/3/UART<br>5/SPDIFR<br>X | SAI/<br>USART6/<br>UART4/5/<br>SPDIFRX | CAN1/2<br>TIM12/13/<br>14/<br>QUADSPI | SAI2/<br>QUADSPI/<br>OTG2_HS/<br>OTG1_FS | OTG1_FS | FMC/<br>SDIO/<br>OTG2_FS | DCMI            | -    | SYS          |

|        | PA0  | -              | TIM2_CH1/<br>TIM2_ETR | TIM5_CH1 | TIM8_ETR                 | -                  | -                         | -                        | USART2_<br>CTS                                  | UART4_<br>TX                           | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA1  | -              | TIM2_CH2              | TIM5_CH2 | -                        | -                  | -                         | -                        | USART2_<br>RTS                                  | UART4_<br>RX                           | QUADSPI_<br>BK1_IO3                   | SAI2_<br>MCLK_B                          | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA2  | -              | TIM2_CH3              | ТІМ5_СНЗ | TIM9_CH1                 | -                  | -                         | -                        | USART2_<br>TX                                   | SAI2_<br>SCK_B                         | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA3  | -              | TIM2_CH4              | TIM5_CH4 | TIM9_CH2                 | -                  | -                         | SAI1_<br>FS_A            | USART2_<br>RX                                   | -                                      | -                                     | OTG_HS_<br>ULPI_D0                       | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA4  | -              | -                     | -        | -                        | -                  | SPI1_NSS/I<br>2S1_WS      | SPI3_NSS<br>/<br>I2S3_WS | USART2_<br>CK                                   | -                                      | -                                     | -                                        | -       | OTG_HS_<br>SOF           | DCMI_<br>HSYNC  | -    | EVENT<br>OUT |

|        | PA5  | -              | TIM2_CH1/<br>TIM2_ETR | -        | TIM8_<br>CH1N            | -                  | SPI1_SCK/I<br>2S1_CK      | -                        | -                                               | -                                      | -                                     | OTG_HS_<br>ULPI_CK                       | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA6  | -              | TIM1_<br>BKIN         | TIM3_CH1 | TIM8_<br>BKIN            | -                  | SPI1_MISO                 | I2S2_<br>MCK             | -                                               | -                                      | TIM13_CH1                             | -                                        | -       | -                        | DCMI_<br>PIXCLK | -    | EVENT<br>OUT |

| Port A | PA7  | -              | TIM1_<br>CH1N         | TIM3_CH2 | TIM8_<br>CH1N            | -                  | SPI1_MOSI<br>/<br>I2S1_SD | -                        | -                                               | -                                      | TIM14_CH1                             | -                                        | -       | FMC_<br>SDNWE            | -               | -    | EVENT<br>OUT |

|        | PA8  | MCO1           | TIM1_CH1              | -        | -                        | I2C3_<br>SCL       | -                         | -                        | USART1_<br>CK                                   | -                                      | -                                     | OTG_FS_<br>SOF                           | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA9  | -              | TIM1_CH2              | -        | -                        | I2C3_<br>SMBA      | SPI2_SCK<br>/I2S2_CK      | SAI1_<br>SD_B            | USART1_<br>TX                                   | -                                      | -                                     | -                                        | -       | -                        | DCMI_D0         | -    | EVENT<br>OUT |

|        | PA10 | -              | TIM1_CH3              | -        | -                        | -                  | -                         | -                        | USART1_<br>RX                                   | -                                      | -                                     | OTG_FS_<br>ID                            | -       | -                        | DCMI_D1         | -    | EVENT<br>OUT |

|        | PA11 | -              | TIM1_CH4              | -        | -                        | -                  | -                         | -                        | USART1_<br>CTS                                  | -                                      | CAN1_RX                               | OTG_FS_<br>DM                            | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA12 | -              | TIM1_ETR              | -        | -                        | -                  | -                         | -                        | USART1_<br>RTS                                  | SAI2_<br>FS_B                          | CAN1_TX                               | OTG_FS_<br>DP                            | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA13 | JTMS-<br>SWDIO | -                     | -        | -                        | -                  | -                         | -                        | -                                               | -                                      | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA14 | JTCK-<br>SWCLK | -                     | -        | -                        | -                  | -                         | -                        | -                                               | -                                      | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA15 | JTDI           | TIM2_CH1/<br>TIM2_ETR | -        | -                        | HDMI_<br>CEC       | SPI1_NSS/<br>I2S1_WS      | SPI3_<br>NSS/<br>I2S3_WS | -                                               | UART4_RT<br>S                          | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

STM32F446xC/E

Pinout and pin description

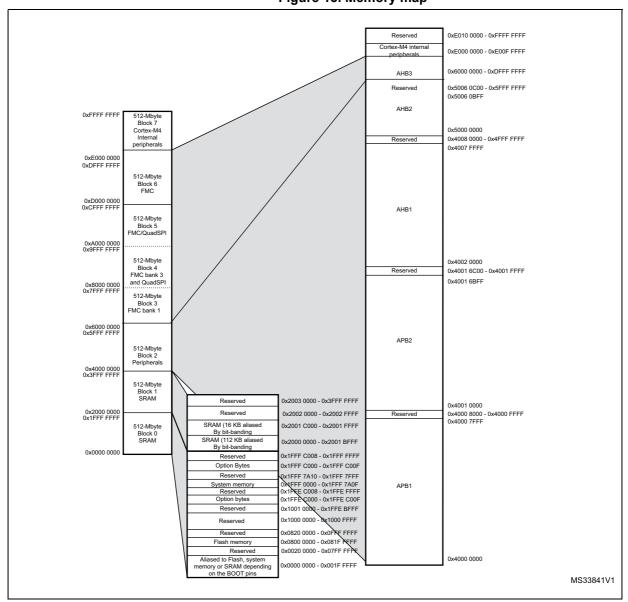

# 5 Memory mapping

The memory map is shown in Figure 15

Figure 15. Memory map

DocID027107 Rev 6

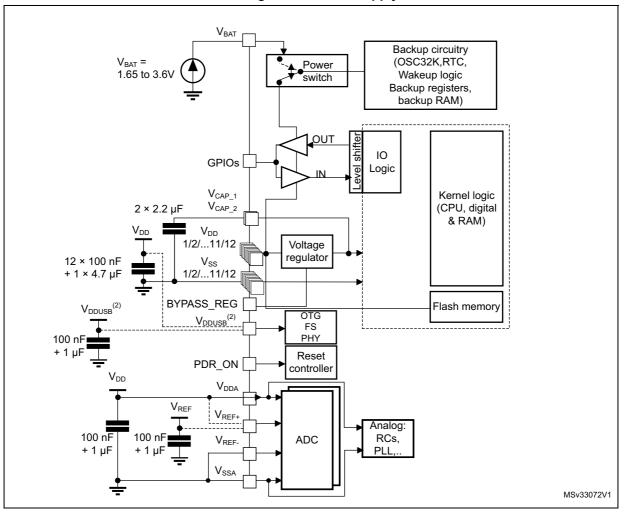

## 6.1.6 Power supply scheme

#### Figure 18. Power supply scheme

- 1.  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

- V<sub>DDUSB</sub> is a dedicated independent USB power supply for the on-chip full-speed OTG PHY module and associated DP/DM GPIOs. Its value is independent from the V<sub>DD</sub> and V<sub>DDA</sub> values, but must be the last supply to be provided and the first to disappear. If V<sub>DD</sub> is different from V<sub>DDUSB</sub> and only one on-chip OTG PHY is used, the second OTG PHY GPIOs (DP/DM) are still supplied at <sub>VDDUSB</sub> (3.3V).

- 3.  $V_{DDUSB}$  is available only on WLCSP81, UFBGA144 and LQFP144 packages. For packages where  $V_{DDUSB}$  pin is not available, it is internally connected to  $V_{DD}$ .

- 4. V<sub>CAP 2</sub> pad is not available on LQFP64.

- **Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub>...) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure good operation of the device. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect operation of the device.

| Symbol                             | Parameter                                                      | Conditions                  | f (MU-)                 | VDD=              | =3.3 V          | VDD=              | =1.7 V          | Unit |

|------------------------------------|----------------------------------------------------------------|-----------------------------|-------------------------|-------------------|-----------------|-------------------|-----------------|------|

| Symbol                             | Parameter                                                      | Conditions                  | f <sub>HCLK</sub> (MHz) | I <sub>DD12</sub> | I <sub>DD</sub> | I <sub>DD12</sub> | I <sub>DD</sub> | -    |

|                                    |                                                                |                             | 180                     | 47.605            | 1.2             | NA                | NA              |      |

|                                    |                                                                |                             | 168                     | 44.35             | 1.0             | 41.53             | 0.8             |      |

|                                    |                                                                |                             | 150                     | 40.58             | 0.9             | 39.96             | 0.8             |      |

|                                    |                                                                |                             | 144                     | 35.68             | 0.9             | 34.60             | 0.7             |      |

|                                    |                                                                | All Peripherals enabled     | 120                     | 27.30             | 0.9             | 29.11             | 0.7             |      |

|                                    | Supply current in Sleep mode from $V_{12}$ and $V_{DD}$ supply |                             | 90                      | 20.69             | 0.8             | 19.78             | 0.6             | -    |

|                                    |                                                                |                             | 60                      | 13.88             | 0.7             | 13.36             | 0.6             |      |

|                                    |                                                                |                             | 30                      | 7.66              | 0.7             | 7.85              | 0.6             |      |

| 1 /1                               |                                                                |                             |                         | 25                | 6.49            | 0.7               | 6.66            | 0.5  |

| I <sub>DD12</sub> /I <sub>DD</sub> |                                                                | All Peripherals<br>disabled | 180                     | 8.71              | 1.2             | NA                | NA              | -    |

|                                    |                                                                |                             | 168                     | 7.00              | 0.9             | 8.42              | 0.8             |      |

|                                    |                                                                |                             | 150                     | 6.88              | 0.9             | 7.61              | 0.8             |      |

|                                    |                                                                |                             | 144                     | 6.29              | 0.9             | 6.99              | 0.7             |      |

|                                    |                                                                |                             | 120                     | 4.87              | 0.9             | 5.95              | 0.7             |      |

|                                    |                                                                |                             | 90                      | 3.78              | 0.8             | 3.96              | 0.6             |      |

|                                    |                                                                |                             | 60                      | 2.66              | 0.7             | 2.80              | 0.6             |      |

|                                    |                                                                |                             | 30                      | 1.65              | 0.7             | 1.74              | 0.6             |      |

|                                    |                                                                |                             | 25                      | 1.45              | 0.7             | 1.52              | 0.5             |      |

| Table 33. Typical current consum | ption in Sleep mode, regulator OFF <sup>(1)</sup> |

|----------------------------------|---------------------------------------------------|

|                                  |                                                   |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

## I/O system current consumption

# The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 56: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

| Symbol                                  | Parameter                                                                                             | Conditions                                                                               | Тур <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------|--------------------|-----------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>     | Wakeup from Sleep                                                                                     | -                                                                                        | 6                  | 6                  | CPU<br>clock<br>cycle |

| T <sub>WUSLEEPFDSM</sub> <sup>(1)</sup> | Wakeup from Sleep<br>with Flash memory in<br>Deep power down<br>mode                                  | -                                                                                        | 33.5               | 50                 |                       |

|                                         |                                                                                                       | Main regulator is ON                                                                     | 12.8               | 15                 |                       |

| t <sub>WUSTOP</sub> <sup>(2)</sup>      | t <sub>WUSTOP</sub> <sup>(2)</sup> Wakeup from Stop<br>mode with MR/LP<br>regulator in normal<br>mode | Main regulator is ON and Flash<br>memory in Deep power down mode                         | 104.9              | 115                |                       |

|                                         |                                                                                                       | Low power regulator is ON                                                                | 20.6               | 28                 |                       |

|                                         |                                                                                                       | Low power regulator is ON and<br>Flash memory in Deep power down<br>mode                 | 112.8              | 120                | μs                    |

|                                         | Wakeup from Stop                                                                                      | Main regulator in under-drive mode<br>(Flash memory in Deep power-<br>down mode)         | 110                | 140                |                       |

| t <sub>wustop</sub> (2)                 | mode with MR/LP<br>regulator in Under-drive<br>mode                                                   | Low power regulator in under-drive<br>mode<br>(Flash memory in Deep power-<br>down mode) | 114.4              | 128                |                       |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup>  | Wakeup from Standby mode                                                                              | -                                                                                        | 325                | 400                |                       |

1. Guaranteed based on test during characterization.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  maximum value is given at -40 °C.

## 6.3.9 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 56: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 23*.

The characteristics given in *Table 37* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 16*.

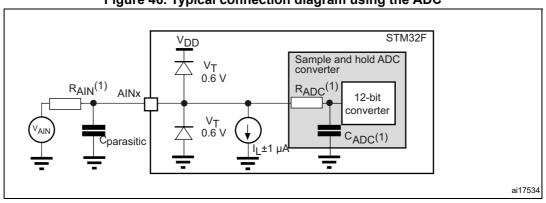

Figure 46. Typical connection diagram using the ADC

- 1. Refer to Table 74 for the values of  $R_{AIN}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

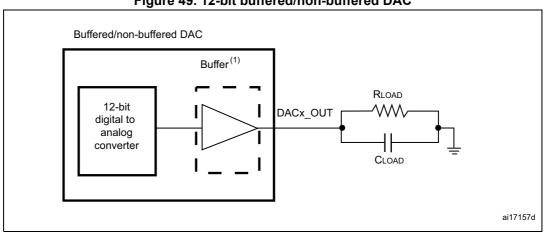

Figure 49. 12-bit buffered/non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol                    | Parameter                                               | Min                      | Max                     | Unit |

|---------------------------|---------------------------------------------------------|--------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                         | 3T <sub>HCLK</sub> – 2   | 3T <sub>HCLK</sub> +0.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low                              | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub>      |      |

| t <sub>tw(NOE)</sub>      | FMC_NOE low time                                        | T <sub>HCLK</sub> – 1    | T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time                   | 0                        | -                       |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                              | -                        | 2                       |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                             | 0                        | 2                       |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                       | T <sub>HCLK</sub> – 0.5  | T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(address) valid hold time after<br>FMC_NADV high) | 0                        | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high                    | T <sub>HCLK</sub> – 0.5  | -                       |      |

| t <sub>h(BL_NOE)</sub>    | FMC_BL time after FMC_NOE high                          | 0                        | -                       |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                             | -                        | 2                       |      |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time                         | T <sub>HCLK</sub> + 1.5  | -                       |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOE high setup time                         | T <sub>HCLK</sub> + 1    | -                       |      |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high                       | 0                        | -                       |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high                       | 0                        | -                       |      |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

| Symbol                    | Parameter                                 | Min                      | Мах                    | Unit |

|---------------------------|-------------------------------------------|--------------------------|------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> - 1   | 8T <sub>HCLK</sub> + 2 |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> – 1   | 5T <sub>HCLK</sub> + 1 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> + 1.5 | -                      |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> + 1   | -                      |      |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

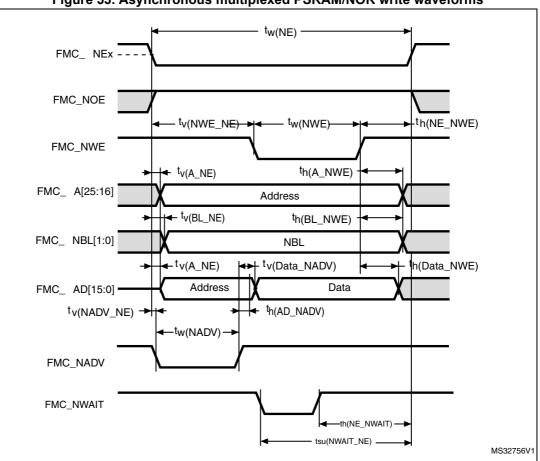

Figure 53. Asynchronous multiplexed PSRAM/NOR write waveforms

| Symbol                    | Parameter                                              | Min                     | Max                      | Unit |

|---------------------------|--------------------------------------------------------|-------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                        | 4T <sub>HCLK</sub> - 2  | 4T <sub>HCLK</sub> +0.5  |      |

| t <sub>v(NWE_NE)</sub>    | FMC_NEx low to FMC_NWE low                             | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5  |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                                       | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NWE)</sub>    | FMC_NWE high to FMC_NE high hold time                  | T <sub>HCLK</sub>       | -                        |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                             | -                       | 0                        |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                            | 0.5                     | 1                        |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                      | T <sub>HCLK</sub> -0.5  | T <sub>HCLK</sub> + 0.5  | ns   |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(adress) valid hold time after<br>FMC_NADV high) | T <sub>HCLK</sub> -2    | -                        |      |

| t <sub>h(A_NWE)</sub>     | Address hold time after FMC_NWE high                   | T <sub>HCLK</sub>       | -                        |      |

| t <sub>h(BL_NWE)</sub>    | FMC_BL hold time after FMC_NWE high                    | T <sub>HCLK</sub> –2    | -                        |      |

| $t_{v(BL_NE)}$            | FMC_NEx low to FMC_BL valid                            | -                       | 2                        |      |

| t <sub>v(Data_NADV)</sub> | FMC_NADV high to Data valid                            | -                       | T <sub>HCLK</sub> + 1.5  |      |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FMC_NWE high                      | T <sub>HCLK</sub> + 0.5 | -                        |      |

Table 92. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

| Symbol                    | Parameter                                                      | Min                | Max                      | Unit |

|---------------------------|----------------------------------------------------------------|--------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                                | 9T <sub>HCLK</sub> | 9T <sub>HCLK</sub> + 0.5 |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time 7T <sub>HCLK</sub> 7T <sub>HCLK</sub>         |                    | 7T <sub>HCLK</sub> + 2   | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high 6T <sub>HCLK</sub> + 1.5 - |                    | -                        |      |

| t <sub>h(NE_NWAIT)</sub>  | h(NE_NWAIT) FMC_NEx hold time after FMC_NWAIT // invalid       |                    | -                        |      |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

### Synchronous waveforms and timings

*Figure 54* through *Figure 57* represent synchronous waveforms and *Table 94* through *Table 97* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F446 reference manual: RM0390)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

| Symbol                      | Parameter                                            | Min                     | Мах | Unit |

|-----------------------------|------------------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                                       | 2T <sub>HCLK</sub> – 1  | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)                    | -                       | 2.5 |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)                 | T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                          | -                       | 2   |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high                         | 0                       | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)                 | -                       | 2   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)              | 0                       | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                           |                         | 3   | 115  |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high T <sub>HCLK</sub> + 1   |                         | -   |      |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low -           |                         | 2.5 |      |

| $t_{d(CLKL-NBLL)}$          | FMC_CLK low to FMC_NBL low 3                         |                         | -   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high T <sub>HCLK</sub> + 1.5 |                         | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high                  | 1.5                     | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high                   | 0                       | -   |      |

Table 97. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

#### NAND controller waveforms and timings

*Figure 58* through *Figure 61* represent synchronous waveforms, and *Table 98* and *Table 99* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FSMC\_SetupTime = 0x01;

- COM.FMC\_WaitSetupTime = 0x03;

- COM.FMC\_HoldSetupTime = 0x02;

- COM.FMC\_HiZSetupTime = 0x01;

- ATT.FMC\_SetupTime = 0x01;

- ATT.FMC\_WaitSetupTime = 0x03;

- ATT.FMC\_HoldSetupTime = 0x02;

- ATT.FMC\_HiZSetupTime = 0x01;

- Bank = FMC\_Bank\_NAND;

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b;

- ECC = FMC\_ECC\_Enable;

- ECCPageSize = FMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

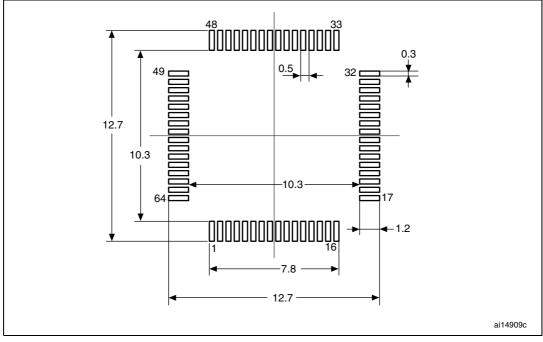

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Мах    |

| D      | 11.800      | 12.000 | 12.200 | 0.4646                | 0.4724 | 0.4803 |

| D1     | 9.800       | 10.000 | 10.200 | 0.3858                | 0.3937 | 0.4016 |

| D3     | -           | 7.500  | -      | -                     | 0.2953 | -      |

| Е      | 11.800      | 12.000 | 12.200 | 0.4646                | 0.4724 | 0.4803 |

| E1     | 9.800       | 10.000 | 10.200 | 0.3858                | 0.3937 | 0.4016 |

| E3     | -           | 7.500  | -      | -                     | 0.2953 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| К      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

#### Table 108. LQFP64 – 10 x 10 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### Figure 68. LQFP64 Recommended footprint

1. Drawing is not to scale.

2. Dimensions are in millimeters.

## 7.7 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                        | Value | Unit |  |

|-----------------|----------------------------------------------------------------------------------|-------|------|--|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm                       | 46    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch       | 42    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch       | 33    | °C/W |  |

|                 | <b>Thermal resistance junction-ambient</b><br>UFBGA144 - 7 × 7 mm / 0.5 mm pitch | 51    | C/W  |  |

|                 | Thermal resistance junction-ambient<br>UFBGA144 - 10 × 10 mm / 0.8 mm pitch      | 48    |      |  |

|                 | Thermal resistance junction-ambient<br>WLCSP81                                   | 48    |      |  |

Table 117. Package thermal characteristics

#### **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

# **Revision history**

| Date          | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 17-Feb-2015   | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 16-Mar-2015   | 2        | Added note 2 inside Table 2<br>Updated Table 11, Table 23, Table 24, Table 25, Table 26, Table 30,<br>Table 51, Table 52, Table 53, and Table 61<br>Added condition inside Typical and maximum current consumption and<br>Additional current consumption<br>Added FMPI2C characteristics<br>Added Table 62 and Figure 35                                                                                                                                                                                                                                                                                                           |  |  |

| 29-May-2015   | 3        | <ul> <li>Updated:</li> <li>Section 6.3.15: Absolute maximum ratings (electrical sensitivity)</li> <li>Section 7: Package information</li> <li>Table 2: STM32F446xC/E features and peripheral counts</li> <li>Table 13: STM32F446xC/xE WLCSP81 ballout</li> <li>Figure 53: ESD absolute maximum ratings</li> <li>Figure 54: Synchronous multiplexed NOR/PSRAM read timings</li> <li>Added:</li> <li>Figure 78: UQFP144 7 x 7 mm marking example (package top view),</li> <li>Figure 81: UQFP144 10 x 10 mm marking example (package top view),</li> <li>Figure 84: WLCSP81 10 x 10 mm marking example (package top view)</li> </ul> |  |  |

| 10-Aug-2015 4 |          | Updated:<br>- Figure 14: STM32F446xC/xE UFBGA144 ballout<br>- Table 10: STM32F446xx pin and ball descriptions<br>- Table 18: VCAP_1/VCAP_2 operating conditions<br>- Section 3.15: Power supply schemes<br>- Section 6.3.2: VCAP_1/VCAP_2 external capacitor<br>Added:<br>- Figure 5: VDDUSB connected to an external independent power<br>supply<br>- Notes 3 and 4 below Figure 18: Power supply scheme                                                                                                                                                                                                                          |  |  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027107 Rev 6