#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Active                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                                |

| Speed                      | 180MHz                                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 114                                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                             |

| EEPROM Size                | -                                                                                                 |

| RAM Size                   | 128K x 8                                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                             |

| Oscillator Type            | Internal                                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                     |

| Package / Case             | 144-LQFP                                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f446zct6jtr                          |

|                            |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.4 Embedded Flash memory

The devices embed a Flash memory of 512KB available for storing programs and data.

# 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.6 Embedded SRAM

All devices embed:

- Up to 128Kbytes of system SRAM.

RAM memory is accessed (read/write) at CPU clock speed with 0 wait states.

- 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

# 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, USB HS) and the slaves Flash memory, RAM, QuadSPI, FMC, AHB and APB peripherals and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

There are three power modes configured by software when the regulator is ON:

- MR mode used in Run/sleep modes or in Stop modes

- In Run/Sleep mode

The MR mode is used either in the normal mode (default mode) or the over-drive mode (enabled by software). Different voltages scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption. The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during stop mode:

- MR operates in normal mode (default mode of MR in stop mode)

- MR operates in under-drive mode (reduced leakage mode).

- LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to *Table 3* for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pin.

All packages have the regulator ON feature.

|                                   | J        | J          |           | J            |

|-----------------------------------|----------|------------|-----------|--------------|

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down<br>mode                | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. '-' means that the corresponding configuration is not available.

2. The over-drive mode is not available when  $V_{DD}$  = 1.7 to 2.1 V.

## 3.17.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

DocID027107 Rev 6

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

# 3.32 Controller area network (bxCAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). 256 bytes of SRAM are allocated for each CAN.

# 3.33 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The USB has dedicated power rails allowing its use throughout the entire power range. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

# 3.34 Universal serial bus on-the-go high-speed (OTG\_HS)

The devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The USB has dedicated power rails allowing its use throughout the entire power range.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 3.41 Embedded Trace Macrocell<sup>™</sup>

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F446xx through a small number of ETM pins to an external hardware trace port analyser (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

|        | Piı     | n Nun    | nber     |         |                                    |          |               |       |                                                                                                |                         |

|--------|---------|----------|----------|---------|------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | WLCSP 81 | UFBGA144 | LQFP144 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                            | Additional<br>functions |

| 51     | 78      | D3       | B11      | 111     | PC10                               | I/O      | FT            | -     | SPI3_SCK/I2S3_CK,<br>USART3_TX, UART4_TX,<br>QUADSPI_BK1_IO1,<br>SDIO_D2, DCMI_D8,<br>EVENTOUT | -                       |

| 52     | 79      | D4       | B10      | 112     | PC11                               | I/O      | FT            | -     | SPI3_MISO, USART3_RX,<br>UART4_RX,<br>QUADSPI_BK2_NCS,<br>SDIO_D3, DCMI_D4,<br>EVENTOUT        | -                       |

| 53     | 80      | A2       | C10      | 113     | PC12                               | I/O      | FT            | Ι     | I2C2_SDA,<br>SPI3_MOSI/I2S3_SD,<br>USART3_CK, UART5_TX,<br>SDIO_CK, DCMI_D9,<br>EVENTOUT       | -                       |

| -      | 81      | В3       | E10      | 114     | PD0                                | I/O      | FT            | -     | SPI4_MISO,<br>SPI3_MOSI/I2S3_SD,<br>CAN1_RX, FMC_D2,<br>EVENTOUT                               | -                       |

| -      | 82      | C4       | D10      | 115     | PD1                                | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>CAN1_TX, FMC_D3,<br>EVENTOUT                                              | -                       |

| 54     | 83      | D5       | E9       | 116     | PD2                                | I/O      | FT            | -     | TIM3_ETR, UART5_RX,<br>SDIO_CMD, DCMI_D11,<br>EVENTOUT                                         | -                       |

| -      | 84      | -        | D9       | 117     | PD3                                | I/O      | FT            | -     | TRACED1,<br>SPI2_SCK/I2S2_CK,<br>USART2_CTS,<br>QUADSPI_CLK,<br>FMC_CLK, DCMI_D5,<br>EVENTOUT  | -                       |

| -      | 85      | A3       | C9       | 118     | PD4                                | I/O      | FT            | -     | USART2_RTS, FMC_NOE,<br>EVENTOUT                                                               | -                       |

| -      | 86      | -        | B9       | 119     | PD5                                | I/O      | FT            | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                                | -                       |

| -      | -       | -        | E7       | 120     | VSS                                | S        | -             | -     | -                                                                                              | -                       |

| -      | -       | -        | F7       | 121     | VDD                                | S        | -             | -     | -                                                                                              | -                       |

Table 10. STM32F446xx pin and ball descriptions (continued)

5

DocID027107 Rev 6

59/202

|        |      |                |                       |          |                          |                    | Tab                       | ole 11. A                | Iternate                                        | functio                                | n                                     |                                          |         |                          |                 |      |              |

|--------|------|----------------|-----------------------|----------|--------------------------|--------------------|---------------------------|--------------------------|-------------------------------------------------|----------------------------------------|---------------------------------------|------------------------------------------|---------|--------------------------|-----------------|------|--------------|

|        |      | AF0            | AF1                   | AF2      | AF3                      | AF4                | AF5                       | AF6                      | AF7                                             | AF8                                    | AF9                                   | AF10                                     | AF11    | AF12                     | AF13            | AF14 | AF15         |

| Po     | ort  | SYS            | TIM1/2                | TIM3/4/5 | TIM8/9/<br>10/11/<br>CEC | I2C1/2/3<br>/4/CEC | SPI1/2/3/<br>4            | SPI2/3/4/<br>SAI1        | SPI2/3/<br>USART1/<br>2/3/UART<br>5/SPDIFR<br>X | SAI/<br>USART6/<br>UART4/5/<br>SPDIFRX | CAN1/2<br>TIM12/13/<br>14/<br>QUADSPI | SAI2/<br>QUADSPI/<br>OTG2_HS/<br>OTG1_FS | OTG1_FS | FMC/<br>SDIO/<br>OTG2_FS | DCMI            | -    | SYS          |

|        | PA0  | -              | TIM2_CH1/<br>TIM2_ETR | TIM5_CH1 | TIM8_ETR                 | -                  | -                         | -                        | USART2_<br>CTS                                  | UART4_<br>TX                           | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA1  | -              | TIM2_CH2              | TIM5_CH2 | -                        | -                  | -                         | -                        | USART2_<br>RTS                                  | UART4_<br>RX                           | QUADSPI_<br>BK1_IO3                   | SAI2_<br>MCLK_B                          | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA2  | -              | TIM2_CH3              | ТІМ5_СНЗ | TIM9_CH1                 | -                  | -                         | -                        | USART2_<br>TX                                   | SAI2_<br>SCK_B                         | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA3  | -              | TIM2_CH4              | TIM5_CH4 | TIM9_CH2                 | -                  | -                         | SAI1_<br>FS_A            | USART2_<br>RX                                   | -                                      | -                                     | OTG_HS_<br>ULPI_D0                       | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA4  | -              | -                     | -        | -                        | -                  | SPI1_NSS/I<br>2S1_WS      | SPI3_NSS<br>/<br>I2S3_WS | USART2_<br>CK                                   | -                                      | -                                     | -                                        | -       | OTG_HS_<br>SOF           | DCMI_<br>HSYNC  | -    | EVENT<br>OUT |

|        | PA5  | -              | TIM2_CH1/<br>TIM2_ETR | -        | TIM8_<br>CH1N            | -                  | SPI1_SCK/I<br>2S1_CK      | -                        | -                                               | -                                      | -                                     | OTG_HS_<br>ULPI_CK                       | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA6  | -              | TIM1_<br>BKIN         | TIM3_CH1 | TIM8_<br>BKIN            | -                  | SPI1_MISO                 | I2S2_<br>MCK             | -                                               | -                                      | TIM13_CH1                             | -                                        | -       | -                        | DCMI_<br>PIXCLK | -    | EVENT<br>OUT |

| Port A | PA7  | -              | TIM1_<br>CH1N         | TIM3_CH2 | TIM8_<br>CH1N            | -                  | SPI1_MOSI<br>/<br>I2S1_SD | -                        | -                                               | -                                      | TIM14_CH1                             | -                                        | -       | FMC_<br>SDNWE            | -               | -    | EVENT<br>OUT |

|        | PA8  | MCO1           | TIM1_CH1              | -        | -                        | I2C3_<br>SCL       | -                         | -                        | USART1_<br>CK                                   | -                                      | -                                     | OTG_FS_<br>SOF                           | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA9  | -              | TIM1_CH2              | -        | -                        | I2C3_<br>SMBA      | SPI2_SCK<br>/I2S2_CK      | SAI1_<br>SD_B            | USART1_<br>TX                                   | -                                      | -                                     | -                                        | -       | -                        | DCMI_D0         | -    | EVENT<br>OUT |

|        | PA10 | -              | TIM1_CH3              | -        | -                        | -                  | -                         | -                        | USART1_<br>RX                                   | -                                      | -                                     | OTG_FS_<br>ID                            | -       | -                        | DCMI_D1         | -    | EVENT<br>OUT |

|        | PA11 | -              | TIM1_CH4              | -        | -                        | -                  | -                         | -                        | USART1_<br>CTS                                  | -                                      | CAN1_RX                               | OTG_FS_<br>DM                            | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA12 | -              | TIM1_ETR              | -        | -                        | -                  | -                         | -                        | USART1_<br>RTS                                  | SAI2_<br>FS_B                          | CAN1_TX                               | OTG_FS_<br>DP                            | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA13 | JTMS-<br>SWDIO | -                     | -        | -                        | -                  | -                         | -                        | -                                               | -                                      | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA14 | JTCK-<br>SWCLK | -                     | -        | -                        | -                  | -                         | -                        | -                                               | -                                      | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA15 | JTDI           | TIM2_CH1/<br>TIM2_ETR | -        | -                        | HDMI_<br>CEC       | SPI1_NSS/<br>I2S1_WS      | SPI3_<br>NSS/<br>I2S3_WS | -                                               | UART4_RT<br>S                          | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

STM32F446xC/E

Pinout and pin description

64/202

DocID027107 Rev 6

|        |      |     |        | 1        |                          | ٦                  | able 11.       | Alterna           | te funct                                        | ion (cor                               | ntinued)            |                     |         | 1                        |              |      |              |

|--------|------|-----|--------|----------|--------------------------|--------------------|----------------|-------------------|-------------------------------------------------|----------------------------------------|---------------------|---------------------|---------|--------------------------|--------------|------|--------------|

|        |      | AF0 | AF1    | AF2      | AF3                      | AF4                | AF5            | AF6               | AF7                                             | AF8                                    | AF9                 | AF10                | AF11    | AF12                     | AF13         | AF14 | AF15         |

| Port   | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11/<br>CEC | I2C1/2/3<br>/4/CEC | SPI1/2/3/<br>4 | SPI2/3/4/<br>SAI1 | SPI2/3/<br>USART1/<br>2/3/UART<br>5/SPDIFR<br>X | ART USART6/<br>UART4/5/<br>UFR SPDIERY | / 14/               | OTG2_HS/            | OTG1_FS | FMC/<br>SDIO/<br>OTG2_FS | DCMI         | -    | SYS          |

|        | PF0  | -   | -      | -        | -                        | I2C2_<br>SDA       | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A0                   | -            | -    | EVENT<br>OUT |

|        | PF1  | -   | -      | -        | -                        | I2C2_<br>SCL       | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A1                   | -            | -    | EVENT<br>OUT |

|        | PF2  | -   | -      | -        | -                        | I2C2_<br>SMBA      | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A2                   | -            | -    | EVENT<br>OUT |

|        | PF3  | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A3                   | -            | -    | EVENT<br>OUT |

|        | PF4  | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A4                   | -            | -    | EVENT<br>OUT |

|        | PF5  | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A5                   | -            | -    | EVEN<br>OUT  |

|        | PF6  | -   | -      | -        | TIM10_<br>CH1            | -                  | -              | SAI1_<br>SD_B     | -                                               | -                                      | QUADSPI_<br>BK1_IO3 | -                   | -       | -                        | -            | -    | EVENT<br>OUT |

|        | PF7  | -   | -      | -        | TIM11_<br>CH1            | -                  | -              | SAI1_<br>MCLK_B   | -                                               | -                                      | QUADSPI_<br>BK1_IO2 | -                   | -       | -                        | -            | -    | EVENT<br>OUT |

| Port F | PF8  | -   | -      | -        | -                        | -                  | -              | SAI1_<br>SCK_B    | -                                               | -                                      | TIM13_CH1           | QUADSPI_<br>BK1_IO0 | -       | -                        | -            | -    | EVENT<br>OUT |

|        | PF9  | -   | -      | -        | -                        | -                  | -              | SAI1_<br>FS_B     | -                                               | -                                      | TIM14_CH1           | QUADSPI_<br>BK1_IO1 | -       | -                        | -            | -    | EVENT<br>OUT |

|        | PF10 | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                   | -                   | -       | -                        | DCMI_<br>D11 | -    | EVENT<br>OUT |

|        | PF11 | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                   | SAI2_SD_B           | -       | FMC_<br>SDNRAS           | DCMI_<br>D12 | -    | EVEN<br>OUT  |

|        | PF12 | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A6                   | -            | -    | EVEN<br>OUT  |

|        | PF13 | -   | -      | -        | -                        | FMPI2C1<br>_SMBA   | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A7                   | -            | -    | EVEN<br>OUT  |

|        | PF14 | -   | -      | -        | -                        | FMPI2C1<br>_SCL    | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A8                   | -            | -    | EVEN<br>OUT  |

|        | PF15 | -   | -      | -        | -                        | FMPI2C1<br>_SDA    | -              | -                 | -                                               | -                                      | -                   | -                   | -       | FMC_A9                   | -            | -    | EVEN<br>OUT  |

# Pinout and pin description

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

| -    | 0x4000 8000- 0x4000 FFFF  |                     |

|      | 0x4000 7C00 - 0x4000 7FFF | Reserved            |

|      | 0x4000 7800 - 0x4000 7BFF |                     |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | HDMI-CEC            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | FMPI2C1             |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | 12C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

| APB1 | 0x4000 4000 - 0x4000 43FF | SPDIFRX             |

| APDI | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | Reserved            |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | Reserved            |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

# Table 12. STM32F446xC/E register boundary addresses<sup>(1)</sup> (continued)

1. The grey color is used for reserved boundary addresses.

|                                    |                                                                                                               |                                                                                                                                         | Tvn                       |                                          | Max                       |                                           |    |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------|---------------------------|-------------------------------------------|----|--|

| Symbol                             | Parameter                                                                                                     | Conditions                                                                                                                              | Тур                       | v                                        | Unit                      |                                           |    |  |

|                                    |                                                                                                               |                                                                                                                                         | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> |    |  |

|                                    | Supply current in<br>Stop mode with                                                                           | Flash memory in Stop mode, all<br>oscillators OFF, no independent<br>watchdog                                                           | 0.234                     | 1.2                                      | 10                        | 16                                        |    |  |

| I <sub>DD_STOP_NM</sub><br>(normal | voltage regulator in main regulator mode                                                                      | Flash memory in Deep power<br>down mode, all oscillators OFF,<br>no independent watchdog                                                | 0.205                     | 1                                        | 9.5                       | 15                                        |    |  |

| mode)                              | Supply current in Stop mode with                                                                              | Flash memory in Stop mode, all<br>oscillators OFF, no independent<br>watchdog                                                           | 0.15                      | 0.95                                     | 8.5                       | 14                                        |    |  |

|                                    | voltage regulator in<br>Low Power regulator<br>mode                                                           | Flash memory in Deep power<br>down mode, all oscillators OFF,<br>no independent watchdog                                                | 0.121                     | 0.9                                      | 6                         | 12                                        | mA |  |

| IDD STOP UD                        | Supply current in<br>Stop mode with<br>voltage regulator in<br>main regulator and<br>under-drive mode         | Flash memory in Deep power<br>down mode, main regulator in<br>under-drive mode, all oscillators<br>OFF, no independent watchdog         | 0.119                     | 0.4                                      | 3                         | 5                                         |    |  |

| M(under-<br>drive mode)            | Supply current in<br>Stop mode with<br>voltage regulator in<br>Low Power regulator<br>and under-drive<br>mode | Flash memory in Deep power<br>down mode, Low Power<br>regulator in under-drive mode,<br>all oscillators OFF, no<br>independent watchdog | 0.055                     | 0.35                                     | 3                         | 5                                         |    |  |

1. Data based on characterization, tested in production.

| Symbol                             | Parameter                                            | Conditions               | f (MU-)                 | VDD=              | =3.3 V          | VDD:              | =1.7 V          | Unit |

|------------------------------------|------------------------------------------------------|--------------------------|-------------------------|-------------------|-----------------|-------------------|-----------------|------|

| Symbol                             | Parameter                                            | Conditions               | f <sub>HCLK</sub> (MHz) | I <sub>DD12</sub> | I <sub>DD</sub> | I <sub>DD12</sub> | I <sub>DD</sub> | -    |

|                                    |                                                      |                          | 180                     | 47.605            | 1.2             | NA                | NA              |      |

|                                    |                                                      |                          | 168                     | 44.35             | 1.0             | 41.53             | 0.8             |      |

|                                    |                                                      |                          | 150                     | 40.58             | 0.9             | 39.96             | 0.8             |      |

|                                    |                                                      |                          | 144                     | 35.68             | 0.9             | 34.60             | 0.7             |      |

|                                    |                                                      | All Peripherals enabled  | 120                     | 27.30             | 0.9             | 29.11             | 0.7             |      |

|                                    |                                                      |                          | 90                      | 20.69             | 0.8             | 19.78             | 0.6             | - mA |

|                                    | Supply current<br>in Sleep mode<br>from $V_{12}$ and |                          | 60                      | 13.88             | 0.7             | 13.36             | 0.6             |      |

|                                    |                                                      |                          | 30                      | 7.66              | 0.7             | 7.85              | 0.6             |      |

| 1 /1                               |                                                      |                          | 25                      | 6.49              | 0.7             | 6.66              | 0.5             |      |

| I <sub>DD12</sub> /I <sub>DD</sub> |                                                      |                          | 180                     | 8.71              | 1.2             | NA                | NA              |      |

|                                    | $V_{DD}$ supply                                      |                          | 168                     | 7.00              | 0.9             | 8.42              | 0.8             |      |

|                                    |                                                      |                          | 150                     | 6.88              | 0.9             | 7.61              | 0.8             |      |

|                                    |                                                      |                          | 144                     | 6.29              | 0.9             | 6.99              | 0.7             | 1    |

|                                    |                                                      | All Peripherals disabled | 120                     | 4.87              | 0.9             | 5.95              | 0.7             |      |

|                                    |                                                      | uisableu                 | 90                      | 3.78              | 0.8             | 3.96              | 0.6             | -    |

|                                    |                                                      |                          | 60                      | 2.66              | 0.7             | 2.80              | 0.6             |      |

|                                    |                                                      |                          | 30                      | 1.65              | 0.7             | 1.74              | 0.6             |      |

|                                    |                                                      |                          | 25                      | 1.45              | 0.7             | 1.52              | 0.5             |      |

| Table 33. Typical current consum | ption in Sleep mode, regulator OFF <sup>(1)</sup> |

|----------------------------------|---------------------------------------------------|

|                                  |                                                   |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

## I/O system current consumption

# The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 56: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

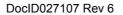

Figure 23. High-speed external clock source AC timing diagram

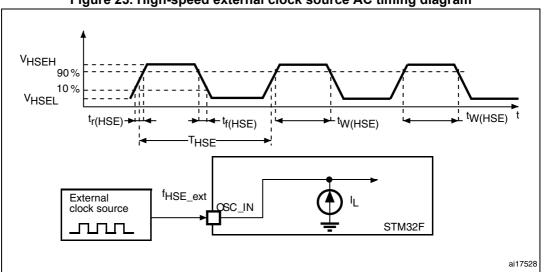

Figure 24. Low-speed external clock source AC timing diagram

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

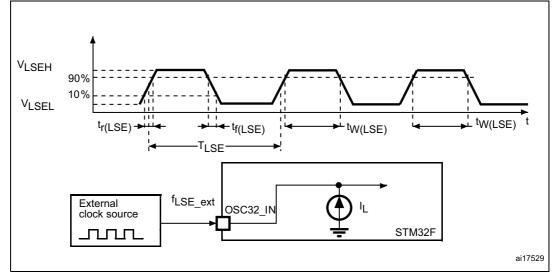

Figure 31. FT I/O input characteristics

## **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 14*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 14*).

## Output voltage levels

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*. All I/Os are CMOS and TTL compliant.

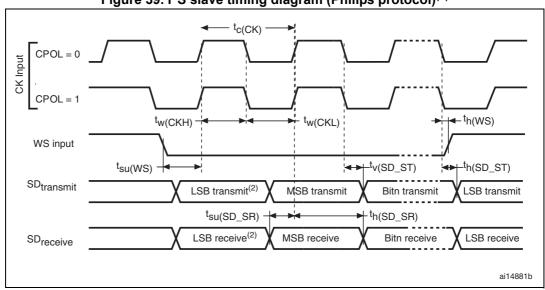

Figure 39. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

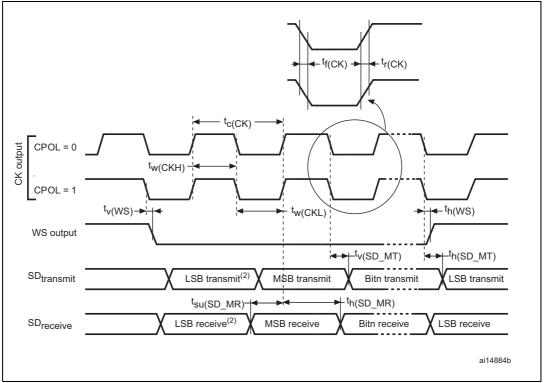

# Figure 40. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Symbol                            | Parameter                                                             | Conditions                                         | Min | Тур | Max  | Unit |

|-----------------------------------|-----------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|------|

| f <sub>S</sub> <sup>(2)</sup>     | Sampling rate<br>( $f_{ADC}$ = 30 MHz, and<br>$t_{S}$ = 3 ADC cycles) | 12-bit resolution<br>Single ADC                    | -   | -   | 2    | Msps |

|                                   |                                                                       | 12-bit resolution<br>Interleave Dual ADC<br>mode   | -   | -   | 3.75 | Msps |

|                                   |                                                                       | 12-bit resolution<br>Interleave Triple ADC<br>mode | -   | -   | 6    | Msps |

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode  | -                                                  | -   | 300 | 500  | μA   |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode  | -                                                  | -   | 1.6 | 1.8  | mA   |

Table 74. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.16.2: Internal reset OFF).

2. Guaranteed based on test during characterization.

3.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

- 4.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.7 V, and minimum value for V<sub>DD</sub>=3.3 V.

- 5. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table 74*.

## Equation 1: R<sub>AIN</sub> max formula

$$\mathsf{R}_{\mathsf{AIN}} = \frac{(\mathsf{k} - 0.5)}{\mathsf{f}_{\mathsf{ADC}} \times \mathsf{C}_{\mathsf{ADC}} \times \mathsf{ln}(2^{\mathsf{N}+2})} - \mathsf{R}_{\mathsf{ADC}}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       |                                                             | ±3  | ±4                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±2  | ±3                 |      |

| EG     | Gain error                   | $V_{\text{REF}}$ = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V                  | ±1  | ±2                 |      |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |

Table 75. ADC static accuracy at  $f_{ADC} = 18 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $V_{\text{DD}}$ , frequency and temperature ranges.

2. Guaranteed based on test during characterization.

| Symbol                      | Parameter                                          | Min                                     | Max | Unit     |

|-----------------------------|----------------------------------------------------|-----------------------------------------|-----|----------|

| t <sub>w(CLK)</sub>         | FMC_CLK period, VDD range= 2.7 to 3.6 V            | 2T <sub>HCLK</sub> - 1                  | -   |          |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)                  | x=02) -                                 |     |          |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)               | -                                       |     |          |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                        | 2                                       |     |          |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high                       | -                                       |     |          |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)               | 2                                       |     |          |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)            | C_Ax invalid (x=1625) T <sub>HCLK</sub> |     |          |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low -                       |                                         | 0   | <b>_</b> |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high T <sub>HCLK</sub> - 0 |                                         | -   | ns       |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid -                |                                         | 3   |          |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid                | _CLK low to FMC_AD[15:0] invalid 0      |     |          |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low -       |                                         | 3   |          |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low 0                       |                                         | -   |          |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high T <sub>HCLK</sub> -   |                                         | -   |          |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high                | 4                                       | -   |          |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high                 | 0                                       | -   |          |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 7.1 LQFP64 package information

Figure 67. LQFP64-10x10 mm 64 pin low-profile quad flat package outline

1. Drawing is not to scale

## Table 108. LQFP64 – 10 x 10 mm low-profile quad flat package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

DocID027107 Rev 6

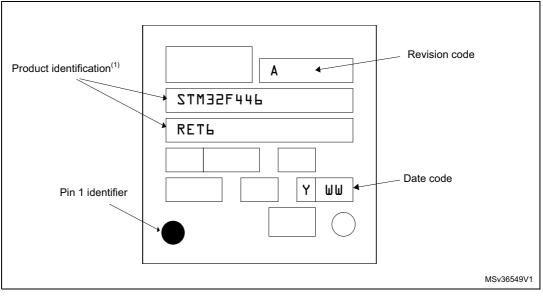

## **Device marking for LQFP64**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

## Figure 69. LQFP64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

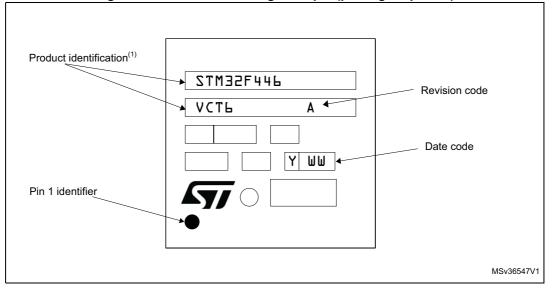

## Device marking for LQFP100 package

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

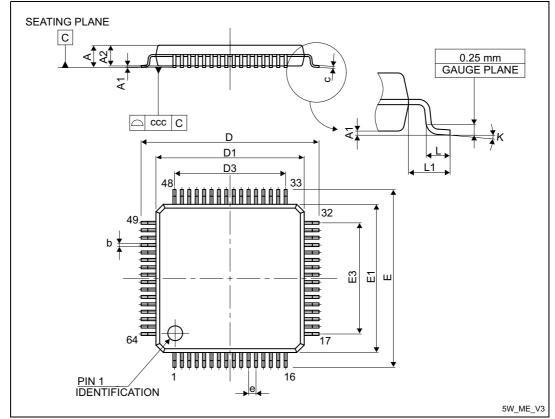

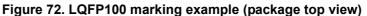

# 7.3 LQFP144 package information.

Figure 73. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline

1. Drawing is not to scale.

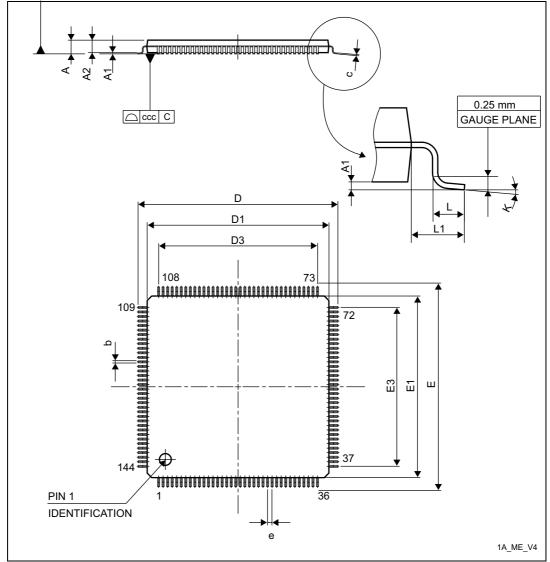

# 7.5 UFBGA144 10 x 10 mm package information

Figure 79. UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 113. UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball |  |  |  |  |

|---------------------------------------------------------------------------------|--|--|--|--|

| grid array package mechanical data                                              |  |  |  |  |

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min.        | Тур.   | Max.   | Min.                  | Тур.   | Max.   |

| А      | 0.460       | 0.530  | 0.600  | 0.0181                | 0.0209 | 0.0236 |

| A1     | 0.050       | 0.080  | 0.110  | 0.0020                | 0.0031 | 0.0043 |

| A2     | 0.400       | 0.450  | 0.500  | 0.0157                | 0.0177 | 0.0197 |

| A3     | 0.050       | 0.080  | 0.110  | -                     | 0.0051 | -      |

| A4     | 0.270       | 0.320  | 0.370  | 0.0106                | 0.0126 | 0.0146 |

| b      | 0.360       | 0.400  | 0.440  | 0.0091                | 0.0110 | 0.0130 |

| D      | 9.950       | 10.000 | 10.050 | 0.2736                | 0.2756 | 0.2776 |

| D1     | 8.750       | 8.800  | 8.850  | 0.2343                | 0.2362 | 0.2382 |

| E      | 9.950       | 10.000 | 10.050 | 0.2736                | 0.2756 | 0.2776 |

| E1     | 8.750       | 8.800  | 8.850  | 0.2343                | 0.2362 | 0.2382 |

| е      | 0.750       | 0.800  | 0.850  | -                     | 0.0197 | -      |

DocID027107 Rev 6