Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                                |

| Speed                      | 180MHz                                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 114                                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                             |

| EEPROM Size                | -                                                                                                 |

| RAM Size                   | 128K x 8                                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                             |

| Oscillator Type            | Internal                                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                     |

| Package / Case             | 144-UFBGA                                                                                         |

| Supplier Device Package    | 144-UFBGA (10x10)                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f446zej6tr                           |

|                            |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 45.            | ADC accuracy characteristics                                                                 | 144 |

|-----------------------|----------------------------------------------------------------------------------------------|-----|

| Figure 46.            | Typical connection diagram using the ADC                                                     |     |

| Figure 47.            | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |     |

| Figure 48.            | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     |     |

| Figure 49.            | 12-bit buffered/non-buffered DAC                                                             |     |

| Figure 50.            | Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms                                   |     |

| Figure 51.            | Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms                                  |     |

| Figure 52.            | Asynchronous multiplexed PSRAM/NOR read waveforms.                                           |     |

| Figure 53.            | Asynchronous multiplexed PSRAM/NOR write waveforms                                           |     |

| Figure 54.            | Synchronous multiplexed NOR/PSRAM read timings                                               |     |

| Figure 55.            | Synchronous multiplexed PSRAM write timings                                                  |     |

| Figure 56.            | Synchronous non-multiplexed NOR/PSRAM read timings                                           |     |

| Figure 57.            | Synchronous non-multiplexed PSRAM write timings                                              |     |

| Figure 58.            | NAND controller waveforms for read access                                                    |     |

| Figure 59.            | NAND controller waveforms for write access                                                   |     |

| Figure 60.            | NAND controller waveforms for common memory read access                                      |     |

| Figure 61.            | NAND controller waveforms for common memory write access                                     |     |

| Figure 62.            | SDRAM read access waveforms (CL = 1)                                                         |     |

| Figure 63.            | SDRAM write access waveforms                                                                 |     |

| Figure 64.            | DCMI timing diagram                                                                          |     |

| Figure 65.            | SDIO high-speed mode                                                                         |     |

| Figure 66.            | SD default mode                                                                              |     |

| Figure 67.            | LQFP64-10x10 mm 64 pin low-profile quad flat package outline                                 |     |

| Figure 68.            | LQFP64 Recommended footprint                                                                 |     |

| Figure 69.            | LQFP64 marking example (package top view)                                                    |     |

| Figure 70.            | LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline                            | 179 |

| Figure 71.            | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                                          |     |

|                       | recommended footprint.                                                                       |     |

| Figure 72.            | LQFP100 marking example (package top view)                                                   |     |

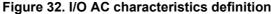

| Figure 73.            | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline                           |     |

| Figure 74.            | LQFP144 recommended footprint                                                                |     |

| Figure 75.            | LQFP144 marking example (package top view).                                                  | 185 |

| Figure 76.            | UFBGA144 - 144-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball                           | 400 |

| <b>-</b> :            | grid array package outline                                                                   | 186 |

| Figure 77.            | UFBGA144 - 144-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball                          | 407 |

| <b>-</b> : <b>-</b> 0 | grid array package recommended footprint                                                     |     |

| Figure 78.            | UQFP144 7 x 7 mm marking example (package top view).                                         | 188 |

| Figure 79.            | UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball                         |     |

|                       | grid array package outline                                                                   | 189 |

| Figure 80.            | UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball                         |     |

| =                     | grid array package recommended footprint                                                     |     |

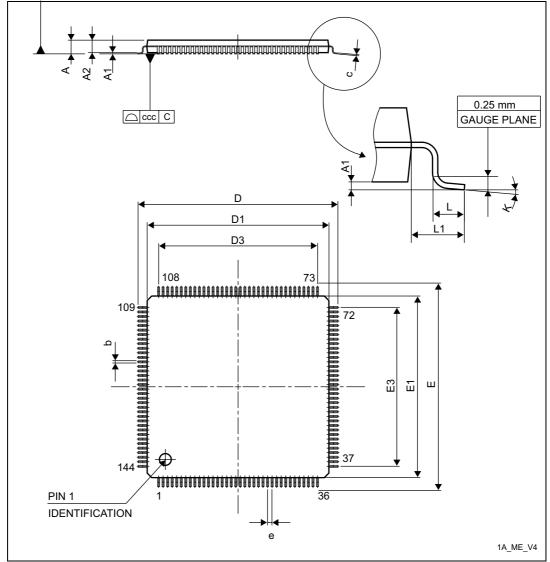

| Figure 81.            | UQFP144 10 x 10 mm marking example (package top view).                                       | 191 |

| Figure 82.            | WLCSP81 - 81-pin, 3.693 x 3.815 mm, 0.4 mm pitch wafer level chip scale                      |     |

|                       | package outline.                                                                             | 192 |

| Figure 83.            | WLCSP81- 81-pin, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip scale                     |     |

|                       | package recommended footprint                                                                |     |

| Figure 84.            | WLCSP81 10 x 10 mm marking example (package top view)                                        |     |

| Figure 85.            | USB controller configured as peripheral-only and used in Full speed mode                     |     |

| Figure 86.            | USB controller configured as host-only and used in full speed mode.                          |     |

| Figure 87.            | USB controller configured in dual mode and used in full speed mode                           | 198 |

| Figure 88.            | USB controller configured as peripheral, host, or dual-mode                                  | 405 |

|                       | and used in high speed mode                                                                  | 199 |

DocID027107 Rev 6

# 3.11 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 91 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\$}$ -M4 with FPU core.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

# 3.12 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 114 GPIOs can be connected to the 16 external interrupt lines.

# 3.13 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy at 25 °C. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 180 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 180 MHz while the maximum frequency of the high-speed APB domains is 90 MHz. The maximum allowed frequency of the low-speed APB domain is 45 MHz.

The devices embed a dedicated PLL (PLLI2S) and PLLSAI which allows to achieve audio class performance. In this case, the I<sup>2</sup>S master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR ON pin is not connected to  $V_{DD}$  (Internal Reset OFF), the  $V_{BAT}$  functionality is

When PDR\_ON pin is not connected to  $V_{DD}$  (Internal Reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to VDD.

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

# 3.25 HDMI (high-definition multimedia interface) consumer electronics control (CEC)

The devices embeds a HDMI-CEC controller that provides hardware support of consumer electronics control (CEC) (Appendix supplement 1 to the HDMI standard). This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead.

# 3.26 Inter-integrated sound (I<sup>2</sup>S)

Three standard  $I^2S$  interfaces (multiplexed with SPI1, SPI2 and SPI3) are available. They can be operated in master or slave mode, in simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the  $I^2S$  interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

# 3.27 SPDIF-RX Receiver Interface (SPDIFRX)

The SPDIF-RX peripheral, is designed to receive an S/PDIF flow compliant with IEC-60958 and IEC-61937. These standards support simple stereo streams up to high sample rate, and compressed multi-channel surround sound, such as those defined by Dolby or DTS (up to 5.1).

The main features of the SPDIF-RX are the following:

- Up to 4 inputs available

- Automatic symbol rate detection

- Maximum symbol rate: 12.288 MHz

- Stereo stream from 32 to 192 kHz supported

- Supports Audio IEC-60958 and IEC-61937, consumer applications

- Parity bit management

- Communication using DMA for audio samples

- Communication using DMA for control and user channel information

- Interrupt capabilities

The SPDIF-RX receiver provides all the necessary features to detect the symbol rate, and decode the incoming data stream.

The user can select the wanted SPDIF input, and when a valid signal will be available, the SPDIF-RX will re-sample the incoming signal, decode the Manchester stream, recognize frames, sub-frames and blocks elements. It delivers to the CPU decoded data, and associated status flags.

DocID027107 Rev 6

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 3.41 Embedded Trace Macrocell<sup>™</sup>

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F446xx through a small number of ETM pins to an external hardware trace port analyser (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

|        | Pin Number |          |          |         |                                    |          |               |       |                                                                                                                     |                         |

|--------|------------|----------|----------|---------|------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100    | WLCSP 81 | UFBGA144 | LQFP144 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                 | Additional<br>functions |

| 40     | 66         | D1       | E11      | 99      | PC9                                | I/O      | FT            | _     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, UART5_CTS,<br>QUADSPI_BK1_IO0,<br>SDIO_D1, DCMI_D3,<br>EVENTOUT | -                       |

| 41     | 67         | E2       | E12      | 100     | PA8                                | I/O      | FT            | -     | MCO1, TIM1_CH1,<br>I2C3_SCL, USART1_CK,<br>OTG_FS_SOF,<br>EVENTOUT                                                  | -                       |

| 42     | 68         | F4       | D12      | 101     | PA9                                | I/O      | FT            | -     | TIM1_CH2, I2C3_SMBA,<br>SPI2_SCK/I2S2_CK,<br>SAI1_SD_B, USART1_TX,<br>DCMI_D0, EVENTOUT                             | OTG_FS_VBUS             |

| 43     | 69         | E3       | D11      | 102     | PA10                               | I/O      | FT            | -     | TIM1_CH3, USART1_RX,<br>OTG_FS_ID, DCMI_D1,<br>EVENTOUT                                                             | -                       |

| 44     | 70         | C1       | C12      | 103     | PA11 <sup>(1)</sup>                | I/O      | FT            | -     | TIM1_CH4, USART1_CTS,<br>CAN1_RX, OTG_FS_DM,<br>EVENTOUT                                                            | -                       |

| 45     | 71         | E4       | B12      | 104     | PA12 <sup>(1)</sup>                | I/O      | FT            | -     | TIM1_ETR, USART1_RTS,<br>SAI2_FS_B, CAN1_TX,<br>OTG_FS_DP, EVENTOUT                                                 | -                       |

| 46     | 72         | D2       | A12      | 105     | PA13(JTMS-SWDIO)                   | I/O      | FT            | -     | JTMS-SWDIO,<br>EVENTOUT                                                                                             | -                       |

| -      | 73         | C2       | G9       | 106     | VCAP_2                             | S        | -             | -     | -                                                                                                                   | -                       |

| 47     | 74         | B1       | G10      | 107     | VSS                                | S        | -             | -     | -                                                                                                                   | -                       |

| 48     | 75         | A1       | F9       | 108     | VDD                                | S        | -             | -     | -                                                                                                                   | -                       |

| 49     | 76         | C3       | A11      | 109     | PA14(JTCK-SWCLK)                   | I/O      | FT            | -     | JTCK-SWCLK,<br>EVENTOUT                                                                                             | -                       |

| 50     | 77         | B2       | A10      | 110     | PA15(JTDI)                         | I/O      | FT            | _     | JTDI,<br>TIM2_CH1/TIM2_ETR,<br>HDMI_CEC,<br>SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>UART4_RTS, EVENTOUT           | -                       |

| Table | 10. STM32F446xx pi | n an | d ba | ll de | escriptions (continued) |

|-------|--------------------|------|------|-------|-------------------------|

|       |                    |      |      |       |                         |

5

DocID027107 Rev 6

59/202

|        |      |                |                       |          |                          |                    | Tab                       | ole 11. A                | Iternate                                        | functio                                | n                                     |                                          |         |                          |                 |      |              |

|--------|------|----------------|-----------------------|----------|--------------------------|--------------------|---------------------------|--------------------------|-------------------------------------------------|----------------------------------------|---------------------------------------|------------------------------------------|---------|--------------------------|-----------------|------|--------------|

|        |      | AF0            | AF1                   | AF2      | AF3                      | AF4                | AF5                       | AF6                      | AF7                                             | AF8                                    | AF9                                   | AF10                                     | AF11    | AF12                     | AF13            | AF14 | AF15         |

| Po     | ort  | SYS            | TIM1/2                | TIM3/4/5 | TIM8/9/<br>10/11/<br>CEC | I2C1/2/3<br>/4/CEC | SPI1/2/3/<br>4            | SPI2/3/4/<br>SAI1        | SPI2/3/<br>USART1/<br>2/3/UART<br>5/SPDIFR<br>X | SAI/<br>USART6/<br>UART4/5/<br>SPDIFRX | CAN1/2<br>TIM12/13/<br>14/<br>QUADSPI | SAI2/<br>QUADSPI/<br>OTG2_HS/<br>OTG1_FS | OTG1_FS | FMC/<br>SDIO/<br>OTG2_FS | DCMI            | -    | SYS          |

|        | PA0  | -              | TIM2_CH1/<br>TIM2_ETR | TIM5_CH1 | TIM8_ETR                 | -                  | -                         | -                        | USART2_<br>CTS                                  | UART4_<br>TX                           | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA1  | -              | TIM2_CH2              | TIM5_CH2 | -                        | -                  | -                         | -                        | USART2_<br>RTS                                  | UART4_<br>RX                           | QUADSPI_<br>BK1_IO3                   | SAI2_<br>MCLK_B                          | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA2  | -              | TIM2_CH3              | ТІМ5_СНЗ | TIM9_CH1                 | -                  | -                         | -                        | USART2_<br>TX                                   | SAI2_<br>SCK_B                         | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA3  | -              | TIM2_CH4              | TIM5_CH4 | TIM9_CH2                 | -                  | -                         | SAI1_<br>FS_A            | USART2_<br>RX                                   | -                                      | -                                     | OTG_HS_<br>ULPI_D0                       | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA4  | -              | -                     | -        | -                        | -                  | SPI1_NSS/I<br>2S1_WS      | SPI3_NSS<br>/<br>I2S3_WS | USART2_<br>CK                                   | -                                      | -                                     | -                                        | -       | OTG_HS_<br>SOF           | DCMI_<br>HSYNC  | -    | EVENT<br>OUT |

|        | PA5  | -              | TIM2_CH1/<br>TIM2_ETR | -        | TIM8_<br>CH1N            | -                  | SPI1_SCK/I<br>2S1_CK      | -                        | -                                               | -                                      | -                                     | OTG_HS_<br>ULPI_CK                       | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA6  | -              | TIM1_<br>BKIN         | TIM3_CH1 | TIM8_<br>BKIN            | -                  | SPI1_MISO                 | I2S2_<br>MCK             | -                                               | -                                      | TIM13_CH1                             | -                                        | -       | -                        | DCMI_<br>PIXCLK | -    | EVENT<br>OUT |

| Port A | PA7  | -              | TIM1_<br>CH1N         | TIM3_CH2 | TIM8_<br>CH1N            | -                  | SPI1_MOSI<br>/<br>I2S1_SD | -                        | -                                               | -                                      | TIM14_CH1                             | -                                        | -       | FMC_<br>SDNWE            | -               | -    | EVENT<br>OUT |

|        | PA8  | MCO1           | TIM1_CH1              | -        | -                        | I2C3_<br>SCL       | -                         | -                        | USART1_<br>CK                                   | -                                      | -                                     | OTG_FS_<br>SOF                           | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA9  | -              | TIM1_CH2              | -        | -                        | I2C3_<br>SMBA      | SPI2_SCK<br>/I2S2_CK      | SAI1_<br>SD_B            | USART1_<br>TX                                   | -                                      | -                                     | -                                        | -       | -                        | DCMI_D0         | -    | EVENT<br>OUT |

|        | PA10 | -              | TIM1_CH3              | -        | -                        | -                  | -                         | -                        | USART1_<br>RX                                   | -                                      | -                                     | OTG_FS_<br>ID                            | -       | -                        | DCMI_D1         | -    | EVENT<br>OUT |

|        | PA11 | -              | TIM1_CH4              | -        | -                        | -                  | -                         | -                        | USART1_<br>CTS                                  | -                                      | CAN1_RX                               | OTG_FS_<br>DM                            | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA12 | -              | TIM1_ETR              | -        | -                        | -                  | -                         | -                        | USART1_<br>RTS                                  | SAI2_<br>FS_B                          | CAN1_TX                               | OTG_FS_<br>DP                            | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA13 | JTMS-<br>SWDIO | -                     | -        | -                        | -                  | -                         | -                        | -                                               | -                                      | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA14 | JTCK-<br>SWCLK | -                     | -        | -                        | -                  | -                         | -                        | -                                               | -                                      | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

|        | PA15 | JTDI           | TIM2_CH1/<br>TIM2_ETR | -        | -                        | HDMI_<br>CEC       | SPI1_NSS/<br>I2S1_WS      | SPI3_<br>NSS/<br>I2S3_WS | -                                               | UART4_RT<br>S                          | -                                     | -                                        | -       | -                        | -               | -    | EVENT<br>OUT |

STM32F446xC/E

Pinout and pin description

64/202

DocID027107 Rev 6

|        |      |     |        | 1        |                          | ٦                  | Table 11.      | Alterna           | te funct                                        | ion (cor                               | ntinued)                              |                                          |         | 1                        |              |      |              |

|--------|------|-----|--------|----------|--------------------------|--------------------|----------------|-------------------|-------------------------------------------------|----------------------------------------|---------------------------------------|------------------------------------------|---------|--------------------------|--------------|------|--------------|

|        |      | AF0 | AF1    | AF2      | AF3                      | AF4                | AF5            | AF6               | AF7                                             | AF8                                    | AF9                                   | AF10                                     | AF11    | AF12                     | AF13         | AF14 | AF15         |

| Port   | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11/<br>CEC | I2C1/2/3<br>/4/CEC | SPI1/2/3/<br>4 | SPI2/3/4/<br>SAI1 | SPI2/3/<br>USART1/<br>2/3/UART<br>5/SPDIFR<br>X | SAI/<br>USART6/<br>UART4/5/<br>SPDIFRX | CAN1/2<br>TIM12/13/<br>14/<br>QUADSPI | SAI2/<br>QUADSPI/<br>OTG2_HS/<br>OTG1_FS | OTG1_FS | FMC/<br>SDIO/<br>OTG2_FS | DCMI         | -    | SYS          |

|        | PF0  | -   | -      | -        | -                        | I2C2_<br>SDA       | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A0                   | -            | -    | EVENT<br>OUT |

|        | PF1  | -   | -      | -        | -                        | I2C2_<br>SCL       | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A1                   | -            | -    | EVENT<br>OUT |

|        | PF2  | -   | -      | -        | -                        | I2C2_<br>SMBA      | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A2                   | -            | -    | EVENT<br>OUT |

|        | PF3  | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A3                   | -            | -    | EVENT<br>OUT |

|        | PF4  | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A4                   | -            | -    | EVENT<br>OUT |

|        | PF5  | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A5                   | -            | -    | EVEN<br>OUT  |

|        | PF6  | -   | -      | -        | TIM10_<br>CH1            | -                  | -              | SAI1_<br>SD_B     | -                                               | -                                      | QUADSPI_<br>BK1_IO3                   | -                                        | -       | -                        | -            | -    | EVENT<br>OUT |

|        | PF7  | -   | -      | -        | TIM11_<br>CH1            | -                  | -              | SAI1_<br>MCLK_B   | -                                               | -                                      | QUADSPI_<br>BK1_IO2                   | -                                        | -       | -                        | -            | -    | EVENT<br>OUT |

| Port F | PF8  | -   | -      | -        | -                        | -                  | -              | SAI1_<br>SCK_B    | -                                               | -                                      | TIM13_CH1                             | QUADSPI_<br>BK1_IO0                      | -       | -                        | -            | -    | EVENT<br>OUT |

|        | PF9  | -   | -      | -        | -                        | -                  | -              | SAI1_<br>FS_B     | -                                               | -                                      | TIM14_CH1                             | QUADSPI_<br>BK1_IO1                      | -       | -                        | -            | -    | EVENT<br>OUT |

|        | PF10 | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | -                        | DCMI_<br>D11 | -    | EVENT<br>OUT |

|        | PF11 | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | SAI2_SD_B                                | -       | FMC_<br>SDNRAS           | DCMI_<br>D12 | -    | EVEN<br>OUT  |

|        | PF12 | -   | -      | -        | -                        | -                  | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A6                   | -            | -    | EVEN<br>OUT  |

|        | PF13 | -   | -      | -        | -                        | FMPI2C1<br>_SMBA   | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A7                   | -            | -    | EVEN<br>OUT  |

|        | PF14 | -   | -      | -        | -                        | FMPI2C1<br>_SCL    | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A8                   | -            | -    | EVEN<br>OUT  |

|        | PF15 | -   | -      | -        | -                        | FMPI2C1<br>_SDA    | -              | -                 | -                                               | -                                      | -                                     | -                                        | -       | FMC_A9                   | -            | -    | EVEN<br>OUT  |

# Pinout and pin description

| Symbol                                                     | Parameter                                                                              | Conditions <sup>(1)</sup>                                                                                                                       | Min                | Тур  | Max                   | Unit  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-----------------------|-------|

| V <sub>DD</sub>                                            | Standard operating voltage                                                             | -                                                                                                                                               | 1.7 <sup>(2)</sup> | -    | 3.6                   |       |

| (3)(4)                                                     | Analog operating voltage<br>(ADC limited to 1.2 M samples)                             | Must be the same potential as $V_{DD}^{(5)}$                                                                                                    | 1.7 <sup>(2)</sup> | -    | 2.4                   |       |

| Analog operating voltage<br>(ADC limited to 2.4 M samples) |                                                                                        |                                                                                                                                                 | 2.4                | -    | 3.6                   |       |

| $V_{BAT}$                                                  | Backup operating voltage                                                               | -                                                                                                                                               | 1.65               | -    | 3.6                   |       |

|                                                            | USB supply voltage (supply                                                             | USB not used                                                                                                                                    | 1.7                | -    | 3.6                   |       |

| VDDUSB                                                     | voltage for PA11,PA12, PB14<br>and PB15 pins)                                          | USB used                                                                                                                                        | 3                  | -    | 3.6                   |       |

|                                                            |                                                                                        | Power Scale 3 ((VOS[1:0] bits in<br>PWR_CR register = 0x01), 120 MHz<br>HCLK max frequency                                                      | 1.08               | 1.14 | 1.20                  | v     |

|                                                            | Regulator ON: 1.2 V internal voltage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins    | Power Scale 2 ((VOS[1:0] bits in<br>PWR_CR register = 0x10), 144 MHz<br>HCLK max frequency with over-drive<br>OFF or 168 MHz with over-drive ON | 1.20               | 1.26 | 1.32                  |       |

| V <sub>12</sub>                                            |                                                                                        | Power Scale 1 ((VOS[1:0] bits in<br>PWR_CR register = 0x11), 168 MHz<br>HCLK max frequency with over-drive<br>OFF or 180 MHz with over-drive ON | 1.26               | 1.32 | 1.40                  |       |

|                                                            | Regulator OFF: 1.2 V external                                                          | Max frequency 120 MHz                                                                                                                           | 1.10               | 1.14 | 1.20                  |       |

|                                                            | voltage must be supplied from external regulator on                                    | Max frequency 144 MHz                                                                                                                           | 1.20               | 1.26 | 1.32                  |       |

|                                                            | V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins <sup>(6)</sup>                             | Max frequency 168 MHz                                                                                                                           | 1.26               | 1.32 | 1.38                  |       |

|                                                            | Input voltage on RST, FTf and                                                          | $2 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$                                                                                      | -0.3               | -    | 5.5                   |       |

| M                                                          | FT pins <sup>(7)</sup>                                                                 | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2 \text{ V}$                                                                                        | -0.3               | -    | 5.2                   | V     |

| V <sub>IN</sub>                                            | Input voltage on TTa pins                                                              | -                                                                                                                                               | -0.3               | -    | V <sub>DDA</sub> +0.3 | v     |

|                                                            | Input voltage on BOOT0 pin                                                             | -                                                                                                                                               | 0                  | -    | 9                     |       |

|                                                            |                                                                                        | LQFP64                                                                                                                                          | -                  | -    | 345                   |       |

|                                                            |                                                                                        | WLCSP81                                                                                                                                         | -                  | -    | 417                   |       |

| D                                                          | Power dissipation at $T_A = 85 \degree C$<br>for suffix 6 or $T_A = 105 \degree C$ for | LQFP100                                                                                                                                         | -                  | -    | 476                   | mW    |

| PD                                                         | suffix $7^{(8)}$                                                                       | LQFP 144                                                                                                                                        | -                  | -    | 606                   | IIIVV |

|                                                            |                                                                                        | UFBGA144 (7x7)                                                                                                                                  | -                  | -    | 392                   |       |

|                                                            |                                                                                        | UFBGA144(10x10)                                                                                                                                 | -                  | -    | 417                   |       |

|                                                            | Ambient temperature for 6 suffix                                                       | Maximum power dissipation                                                                                                                       | -40                | -    | 85                    | °C    |

| Та                                                         | version                                                                                | Low power dissipation <sup>(9)</sup>                                                                                                            | -40                | -    | 105                   |       |

| IA                                                         | Ambient temperature for 7 suffix                                                       | Maximum power dissipation                                                                                                                       | -40                | -    | 105                   | °C    |

|                                                            | version                                                                                | Low power dissipation <sup>(9)</sup>                                                                                                            | -40                | -    | 125                   |       |

| TJ                                                         | Junction temperature range                                                             | 6 suffix version                                                                                                                                | -40                | -    | 105                   | °C    |

| IJ                                                         | ounction temperature range                                                             | 7 suffix version                                                                                                                                | -40                | -    | 125                   |       |

| Table 16 | General | operating | conditions | (continued) |  |

|----------|---------|-----------|------------|-------------|--|

|          | General | operating | conditions | (continucu) |  |

## **Electrical characteristics**

- 1. The over-drive mode is not supported at the voltage ranges from 1.7 to 2.1 V.

- V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.16.2: Internal reset OFF).

- 3. When the ADC is used, refer to *Table 74: ADC characteristics*.

- 4. If  $V_{REF+}$  pin is present, it must respect the following condition:  $V_{DDA}-V_{REF+} < 1.2 \text{ V}$ .

- 5. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and power-down operation.

- 6. The over-drive mode is not supported when the internal regulator is OFF.

- 7. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 8. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 9. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

| Operating<br>power supply<br>range                | ADC operation                     | Maximum Flash<br>memory access<br>frequency with<br>no wait states<br>(f <sub>Flashmax</sub> ) | Maximum HCLK<br>frequency vs Flash<br>memory wait states<br>(1)(2) | I/O operation                               | Possible Flash<br>memory<br>operations        |

|---------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup>   | Conversion time<br>up to 1.2 Msps | 20 MHz <sup>(4)</sup>                                                                          | 168 MHz with 8 wait<br>states and over-drive<br>OFF                | <ul> <li>No I/O<br/>compensation</li> </ul> | 8-bit erase and<br>program<br>operations only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                 | Conversion time<br>up to 1.2 Msps | 22 MHz                                                                                         | 180 MHz with 8 wait<br>states and over-drive<br>ON                 | <ul> <li>No I/O<br/>compensation</li> </ul> | 16-bit erase and<br>program<br>operations     |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                 | Conversion time<br>up to 2.4 Msps | 24 MHz                                                                                         | 180 MHz with 7 wait<br>states and over-drive<br>ON                 | <ul> <li>I/O compensation works</li> </ul>  | 16-bit erase and<br>program<br>operations     |

| $V_{DD} = 2.7 \text{ to}$<br>3.6 V <sup>(5)</sup> | Conversion time<br>up to 2.4 Msps | 30 MHz                                                                                         | 180 MHz with 5 wait<br>states and over-drive<br>ON                 | <ul> <li>I/O compensation works</li> </ul>  | 32-bit erase and program operations           |

## Table 17. Limitations depending on the operating power supply range

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.16.2: Internal reset OFF).

4. Prefetch is not available.

5. The voltage range for USB full speed PHYs can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

## 6.3.2 VCAP\_1/VCAP\_2 external capacitor

Stabilization for the main regulator is achieved by connecting external capacitor  $C_{EXT}$  to the  $V_{CAP\_1}$  and  $V_{CAP\_2}$  pin. For packages supporting only 1  $V_{CAP}$  pin, the 2  $C_{EXT}$  capacitors are replaced by a single capacitor.  $C_{EXT}$  is specified in *Table 18*.

|                 |                        | ash memory (/                                                 |                         |                    |                           | Max <sup>(2)</sup>        |                            |       |

|-----------------|------------------------|---------------------------------------------------------------|-------------------------|--------------------|---------------------------|---------------------------|----------------------------|-------|

| Symbol          | Parameter              | Conditions                                                    | f <sub>HCLK</sub> (MHz) | Тур                | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit  |

|                 |                        |                                                               | 180                     | 86                 | 93.0                      | 115.0                     | 125.0                      |       |

|                 |                        |                                                               |                         | 168 <sup>(5)</sup> | 79                        | 85.1                      | 111.2                      | 117.7 |

|                 |                        |                                                               | 150                     | 73                 | 79.6                      | 104.8                     | 111.2                      |       |

|                 |                        | External clock,                                               | 144 <sup>(5)</sup>      | 68                 | 73.5                      | 97.3                      | 103.3                      |       |

|                 |                        | PLL ON,<br>all peripherals                                    | 120                     | 54                 | 59.3                      | 79.7                      | 84.7                       |       |

|                 |                        | enabled <sup>(3)(4)</sup>                                     | 90                      | 42                 | 47.23                     | 65.50                     | 70.10                      |       |

|                 |                        |                                                               | 60                      | 29                 | 33.7                      | 49.5                      | 53.4                       |       |

|                 |                        |                                                               | 30                      | 16                 | 20.8                      | 34.0                      | 37.4                       |       |

|                 |                        |                                                               | 25                      | 13                 | 18.4                      | 31.2                      | 34.5                       |       |

|                 | Supply                 | HSI, PLL OFF,<br>all peripherals<br>enabled <sup>(3)(4)</sup> | 16                      | 8                  | 13.8                      | 25.0                      | 28.3                       |       |

|                 |                        |                                                               | 8                       | 5                  | 10.8                      | 21.1                      | 24.2                       |       |

|                 |                        |                                                               | 4                       | 3.0                | 9.1                       | 18.9                      | 22.0                       |       |

|                 |                        |                                                               | 2                       | 2.1                | 8.1                       | 17.8                      | 20.9                       | mA    |

| I <sub>DD</sub> | current in<br>RUN mode |                                                               | 180                     | 46                 | 55.0                      | 75.0                      | 86.0                       |       |

|                 |                        |                                                               | 168                     | 43                 | 49.6                      | 67.5                      | 72.6                       |       |

|                 |                        |                                                               | 150                     | 41                 | 48.2                      | 65.8                      | 70.8                       |       |

|                 |                        | External clock,                                               | 144 <sup>(5)</sup>      | 38                 | 43.6                      | 61.9                      | 66.8                       |       |

|                 |                        | PLL ON,<br>all Peripherals                                    | 120                     | 32                 | 37.3                      | 53.7                      | 58.0                       |       |

|                 |                        | disabled <sup>(3)</sup>                                       | 90                      | 26                 | 30.7                      | 46.0                      | 50.0                       |       |

|                 |                        |                                                               | 60                      | 18                 | 22.8                      | 36.4                      | 40.1                       |       |

|                 |                        |                                                               | 30                      | 10                 | 14.9                      | 27.1                      | 30.2                       |       |

|                 |                        |                                                               | 25                      | 9                  | 13.55                     | 25.40                     | 28.54                      |       |

|                 |                        |                                                               | 16                      | 5                  | 11.1                      | 21.8                      | 25.0                       |       |

|                 |                        | HSI, PLL OFF,                                                 | 8                       | 3                  | 9.5                       | 19.4                      | 22.5                       |       |

|                 |                        | all peripherals disabled <sup>(3)</sup>                       | 4                       | 2.4                | 8.34                      | 18.10                     | 21.17                      |       |

|                 |                        |                                                               | 2                       | 1.8                | 7.77                      | 17.39                     | 20.50                      |       |

# Table 24. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled with prefetch) or RAM<sup>(1)</sup>

1. Code and data processing running from SRAM1 using boot pins.

2. Guaranteed based on test during characterization.

3. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

5. Overdrive OFF

|                 |                                                                |                                  | _                       |      |                           | Max                       |                            |      |

|-----------------|----------------------------------------------------------------|----------------------------------|-------------------------|------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter                                                      | Conditions                       | f <sub>HCLK</sub> (MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                                                                |                                  | 168                     | 43.7 | 47.5                      | 66.5                      | 79.3                       |      |

|                 |                                                                |                                  | 150                     | 39.2 | 42.7                      | 60.7                      | 73.3                       |      |

|                 |                                                                |                                  | 144                     | 35.7 | 38.8                      | 55.3                      | 66.9                       |      |

|                 |                                                                | All Peripherals<br>enabled Flash | 120                     | 26.5 | 28.6                      | 41.8                      | 51.6                       |      |

|                 |                                                                | on                               | 90                      | 20.0 | 21.91                     | 33.85                     | 43.20                      |      |

|                 | Supply current in<br>Sleep mode from<br>V <sub>DD</sub> supply |                                  | 60                      | 13.6 | 15.2                      | 25.8                      | 34.9                       |      |

|                 |                                                                |                                  | 30                      | 7.4  | 8.5                       | 18.4                      | 27.0                       |      |

|                 |                                                                |                                  | 25                      | 6.3  | 7.5                       | 16.9                      | 25.5                       | mA   |

| I <sub>DD</sub> |                                                                |                                  | 168                     | 7.3  | 8.6                       | 21.2                      | 31.9                       |      |

|                 |                                                                |                                  | 150                     | 6.6  | 7.94                      | 20.4                      | 31.0                       |      |

|                 |                                                                |                                  | 144                     | 6.0  | 7.3                       | 18.6                      | 28.5                       |      |

|                 |                                                                | All Peripherals                  | 120                     | 4.6  | 5.5                       | 14.9                      | 23.4                       |      |

|                 |                                                                | disabled, flash<br>on            | 90                      | 3.6  | 4.6                       | 13.6                      | 22.1                       | 1    |

|                 |                                                                |                                  | 60                      | 2.6  | 3.4                       | 12.5                      | 20.8                       | 1    |

|                 |                                                                |                                  | 30                      | 1.8  | 2.7                       | 11.3                      | 19.7                       |      |

|                 |                                                                |                                  | 25                      | 1.6  | 2.49                      | 11.09                     | 19.42                      |      |

|                                  |                     | (4)                                    |

|----------------------------------|---------------------|----------------------------------------|

| Table 32. Typical current consum | ption in Sleep mode | regulator ON, Vpp=1.7 V <sup>(1)</sup> |

|                                  |                     |                                        |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 35: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{\mbox{SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

$V_{DD}$  is the MCU supply voltage

$f_{\mbox{SW}}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

| Symbol | Parameter                                                                                        | Conditions                                               | I/O toggling<br>frequency<br>(fsw)                               | Тур           | Unit   |  |        |        |     |    |

|--------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|---------------|--------|--|--------|--------|-----|----|

|        |                                                                                                  |                                                          | 2 MHz                                                            | 0.0           |        |  |        |        |     |    |

|        |                                                                                                  |                                                          | 8 MHz                                                            | 0.2           |        |  |        |        |     |    |

|        |                                                                                                  |                                                          | 25 MHz                                                           | 0.6           |        |  |        |        |     |    |

|        | $I_{DDIO} = 3.3 V$ $C = C_{INT}^{(2)}$ $I_{UDIO} = 0.000 \text{ J/O switching}$ $V_{DD} = 3.3 V$ | $V_{DD} = 3.3 V$<br>C = C <sub>INIT</sub> <sup>(2)</sup> | 50 MHz                                                           | 1.1           |        |  |        |        |     |    |

|        |                                                                                                  |                                                          |                                                                  |               | O OINT |  | 60 MHz | 1.3    |     |    |

|        |                                                                                                  | 84 N                                                     | 84 MHz                                                           | 1.8           |        |  |        |        |     |    |

|        |                                                                                                  | I/O switching                                            | I/O switching                                                    | I/O switching |        |  |        | 90 MHz | 1.9 | mA |

| 'DDIO  |                                                                                                  |                                                          | 2 MHz                                                            | 0.1           | ША     |  |        |        |     |    |

|        |                                                                                                  |                                                          | 8 MHz                                                            | 0.4           |        |  |        |        |     |    |

|        |                                                                                                  |                                                          | 25 MHz                                                           | 1.23          |        |  |        |        |     |    |

|        |                                                                                                  | $C_{EXT} = 0 pF$                                         | $C_{EXT} = 0 \text{ p} + 50 \text{ MHz}$ $C = C_{INT} + C_{EXT}$ | 50 MHz        | 2.43   |  |        |        |     |    |

|        |                                                                                                  | $+ C_S$                                                  | 60 MHz                                                           | 2.93          |        |  |        |        |     |    |

|        |                                                                                                  |                                                          | 84 MHz                                                           | 3.86          |        |  |        |        |     |    |

|        |                                                                                                  |                                                          | 90 MHz                                                           | 4.07          |        |  |        |        |     |    |

| Table 34. Switching output I/O current consumption <sup>(1)</sup> |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

| Cumhal                          | Devementer                                       |            | Min <sup>(1)</sup> |     | Max <sup>(1)</sup> | 11   |

|---------------------------------|--------------------------------------------------|------------|--------------------|-----|--------------------|------|

| Symbol                          | Parameter                                        | Conditions | WIN                | Тур | wax."              | Unit |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -          | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -          | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -          | -                  | -   | 1                  | hour |

Table 49. Flash memory programming with V<sub>PP</sub> (continued)

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3. V<sub>PP</sub> should only be connected during programming/erasing.

| Symbol           | Parameter      | Value                                                                                   |                    |         |  | 11 |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|---------|--|----|

| -                | -              | - Conditions                                                                            | Min <sup>(1)</sup> | Unit    |  |    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | Kcycles |  |    |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |  |    |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |  |    |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 | 1       |  |    |

## Table 50. Flash memory endurance and data retention

1. Guaranteed based on test during characterization.

2. Cycling performed over the whole temperature range.

## 6.3.14 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

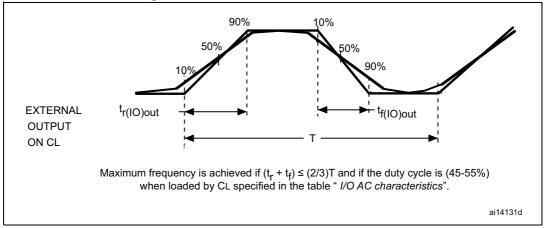

- 1. Guaranteed by design.

- 2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

- 3. The maximum frequency is defined in *Figure* 32.

- 4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

## 6.3.18 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 56: I/O static characteristics*).

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 59. NRST pin characteristics

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

2. Guaranteed by design.

| Symbol                    | Parameter                                              | Min                     | Max                      | Unit |

|---------------------------|--------------------------------------------------------|-------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                        | 4T <sub>HCLK</sub> - 2  | 4T <sub>HCLK</sub> +0.5  |      |

| t <sub>v(NWE_NE)</sub>    | FMC_NEx low to FMC_NWE low                             | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5  |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                                       | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NWE)</sub>    | FMC_NWE high to FMC_NE high hold time                  | T <sub>HCLK</sub>       | -                        |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                             | -                       | 0                        |      |