Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                                |

| Speed                      | 180MHz                                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 114                                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                             |

| EEPROM Size                | -                                                                                                 |

| RAM Size                   | 128K x 8                                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                             |

| Oscillator Type            | Internal                                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                |

| Mounting Type              | Surface Mount                                                                                     |

| Package / Case             | 144-UFBGA                                                                                         |

| Supplier Device Package    | 144-UFBGA (10x10)                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f446zej7                             |

|                            |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This document provides the description of the STM32F446xC/E products.

The STM32F446xC/E document should be read in conjunction with the STM32F4xx reference manual.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214), available from the *www.st.com*.

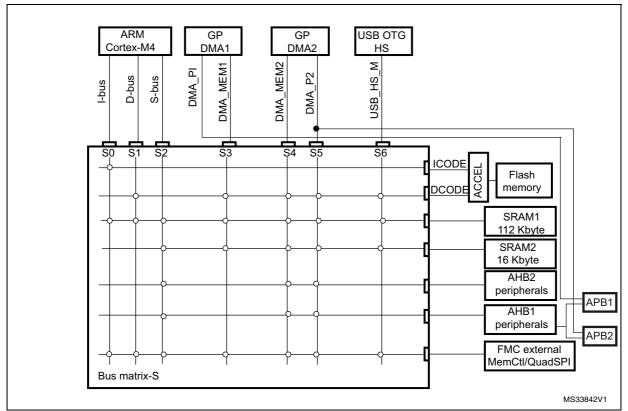

Figure 4. STM32F446xC/E and Multi-AHB matrix

## 3.8 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR ON pin is not connected to  $V_{DD}$  (Internal Reset OFF), the  $V_{BAT}$  functionality is

When PDR\_ON pin is not connected to  $V_{DD}$  (Internal Reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to VDD.

The SPDIF-RX also offers a signal named spdifrx\_frame\_sync, which toggles at the S/PDIF sub-frame rate that will be used to compute the exact sample rate for clock drift algorithms.

## 3.28 Serial Audio interface (SAI)

The devices feature two serial audio interfaces (SAI1 and SAI2). Each serial audio interfaces based on two independent audio sub blocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both sub blocks can be configured in master or in slave mode. The SAIs use a PLL to achieve audio class accuracy.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub blocks can be configured in synchronous mode when full-duplex mode is required.

SAI1 and SA2 can be served by the DMA controller.

# 3.29 Audio PLL (PLLI<sup>2</sup>S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the  $I^2S/SAI$  flow with an external PLL (or Codec output).

## 3.30 Serial Audio Interface PLL(PLLSAI)

An additional PLL dedicated to audio and USB is used for SAI1 and SAI2 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the 48MHz clock for USB FS and SDIO in case the system PLL is programmed with factors not multiple of 48MHz.

## 3.31 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

|        | Piı     | n Nun    | nber     |         |                                    |          |               |       |                                                                                                                                |                         |

|--------|---------|----------|----------|---------|------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | WLCSP 81 | UFBGA144 | LQFP144 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                            | Additional<br>functions |

| -      | 61      | -        | K11      | 85      | PD14                               | I/O      | FTf           | -     | TIM4_CH3,<br>FMPI2C1_SCL,<br>SAI2_SCK_A, FMC_D0,<br>EVENTOUT                                                                   | -                       |

| -      | 62      | -        | K12      | 86      | PD15                               | I/O      | FTf           | -     | TIM4_CH4,<br>FMPI2C1_SDA, FMC_D1,<br>EVENTOUT                                                                                  | -                       |

| -      | -       | -        | J12      | 87      | PG2                                | I/O      | FT            | -     | FMC_A12, EVENTOUT                                                                                                              | -                       |

| -      | -       | -        | J11      | 88      | PG3                                | I/O      | FT            | -     | FMC_A13, EVENTOUT                                                                                                              | -                       |

| -      | -       | -        | J10      | 89      | PG4                                | I/O      | FT            | -     | FMC_A14/FMC_BA0,<br>EVENTOUT                                                                                                   | -                       |

| -      | -       | -        | H12      | 90      | PG5                                | I/O      | FT            | -     | FMC_A15/FMC_BA1,<br>EVENTOUT                                                                                                   | -                       |

| -      | -       | -        | H11      | 91      | PG6                                | I/O      | FT            | -     | QUADSPI_BK1_NCS,<br>DCMI_D12, EVENTOUT                                                                                         | -                       |

| -      | -       | -        | H10      | 92      | PG7                                | I/O      | FT            | -     | USART6_CK, FMC_INT,<br>DCMI_D13, EVENTOUT                                                                                      | -                       |

| -      | -       | -        | G11      | 93      | PG8                                | I/O      | FT            | -     | SPDIFRX_IN2,<br>USART6_RTS,<br>FMC_SDCLK, EVENTOUT                                                                             | -                       |

| -      | -       | -        | -        | 94      | VSS                                | S        | -             | -     | -                                                                                                                              | -                       |

| -      | I       | -        | F10      | I       | VDD                                | S        | -             | -     | -                                                                                                                              | -                       |

| -      | I       | E1       | C11      | 95      | VDDUSB                             | S        | -             | -     | -                                                                                                                              | -                       |

| 37     | 63      | F1       | G12      | 96      | PC6                                | I/O      | FTf           | -     | TIM3_CH1, TIM8_CH1,<br>FMPI2C1_SCL,<br>I2S2_MCK, USART6_TX,<br>SDIO_D6, DCMI_D0,<br>EVENTOUT                                   | -                       |

| 38     | 64      | F2       | F12      | 97      | PC7                                | I/O      | FTf           | -     | TIM3_CH2, TIM8_CH2,<br>FMPI2C1_SDA,<br>SPI2_SCK/I2S2_CK,<br>I2S3_MCK, SPDIFRX_IN1,<br>USART6_RX, SDI0_D7,<br>DCMI_D1, EVENTOUT | -                       |

| 39     | 65      | F3       | F11      | 98      | PC8                                | I/O      | FT            | -     | TRACED0, TIM3_CH3,<br>TIM8_CH3, UART5_RTS,<br>USART6_CK, SDIO_D0,<br>DCMI_D2, EVENTOUT                                         | -                       |

Table 10. STM32F446xx pin and ball descriptions (continued)

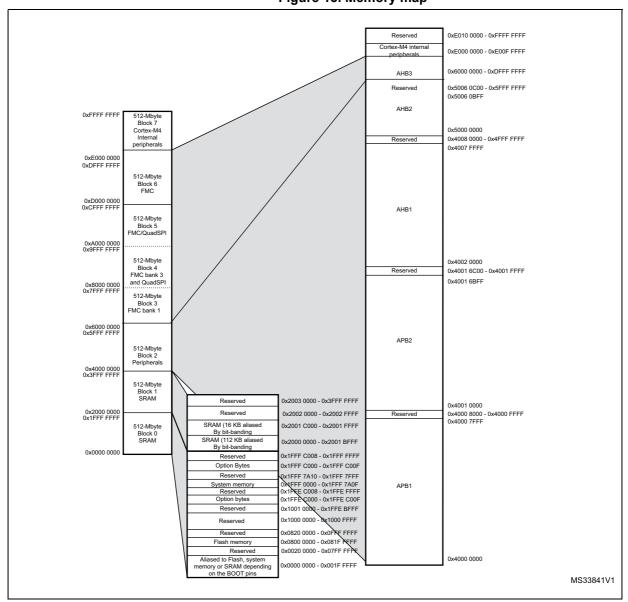

# 5 Memory mapping

The memory map is shown in Figure 15

Figure 15. Memory map

DocID027107 Rev 6

# 6.3 Operating conditions

## 6.3.1 General operating conditions

| Table 16. Genera | l operating | conditions |

|------------------|-------------|------------|

|------------------|-------------|------------|

| Symbol             | Parameter                     | Conditions <sup>(1)</sup>                                                                |                       |      | Тур  | Max | Unit |

|--------------------|-------------------------------|------------------------------------------------------------------------------------------|-----------------------|------|------|-----|------|

|                    | Internal AHB clock frequency  | Power Scale 3 (VOS[1:0] bits<br>PWR_CR register = 0x01),<br>Regulator ON, over-drive OFF | 0                     | -    | 120  |     |      |

|                    |                               | Power Scale 2 (VOS[1:0] bits in PWR_CR register = 0x10),                                 | Over-<br>drive<br>OFF | 0    | -    | 144 |      |

| f <sub>HCLK</sub>  |                               | Regulator ON                                                                             | Over-<br>drive<br>ON  |      | -    | 168 | MHz  |

|                    |                               | Power Scale 1 (VOS[1:0] bits in PWR_CR register= 0x11),                                  | Over-<br>drive<br>OFF | 0    | -    | 168 |      |

|                    |                               | Regulator ON<br>Ove<br>driv<br>ON                                                        |                       | Ū    | -    | 180 |      |

| f                  | Internal APB1 clock frequency | Over-drive OFF                                                                           |                       | 0    | -    | 42  |      |

| f <sub>PCLK1</sub> |                               | Over-drive ON                                                                            | 0                     | - 45 | 45   |     |      |

| franks             | Internal APB2 clock frequency | Over-drive OFF                                                                           |                       | 0    | - 84 | 84  | ]    |

| f <sub>PCLK2</sub> |                               | Over-drive ON                                                                            | 0                     | -    | 90   |     |      |

|                         |                                                                                                               |                                                                                                                                         | Tvn                       |                                          | Unit                      |                                           |    |

|-------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------|---------------------------|-------------------------------------------|----|

| Symbol                  | Parameter                                                                                                     | Conditions                                                                                                                              | Тур                       | v                                        |                           |                                           |    |

|                         |                                                                                                               |                                                                                                                                         | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C <sup>(1)</sup> | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C <sup>(1)</sup> |    |

|                         | Supply current in<br>Stop mode with                                                                           | Flash memory in Stop mode, all<br>oscillators OFF, no independent<br>watchdog                                                           | 0.234                     | 1.2                                      | 10                        | 16                                        |    |

| I <sub>DD_STOP_NM</sub> | voltage regulator in main regulator mode                                                                      | Flash memory in Deep power<br>down mode, all oscillators OFF,<br>no independent watchdog                                                | 0.205                     | 1                                        | 9.5                       | 15                                        |    |

| <b>`</b>                | Supply current in<br>Stop mode with<br>voltage regulator in<br>Low Power regulator<br>mode                    | Flash memory in Stop mode, all<br>oscillators OFF, no independent<br>watchdog                                                           | 0.15                      | 0.95                                     | 8.5                       | 14                                        | mA |

|                         |                                                                                                               | Flash memory in Deep power<br>down mode, all oscillators OFF,<br>no independent watchdog                                                | 0.121                     | 0.9                                      | 6                         | 12                                        |    |

| IDD STOP UD             | Supply current in<br>Stop mode with<br>voltage regulator in<br>main regulator and<br>under-drive mode         | Flash memory in Deep power<br>down mode, main regulator in<br>under-drive mode, all oscillators<br>OFF, no independent watchdog         | 0.119                     | 0.4                                      | 3                         | 5                                         |    |

| M(under-<br>drive mode) | Supply current in<br>Stop mode with<br>voltage regulator in<br>Low Power regulator<br>and under-drive<br>mode | Flash memory in Deep power<br>down mode, Low Power<br>regulator in under-drive mode,<br>all oscillators OFF, no<br>independent watchdog | 0.055                     | 0.35                                     | 3                         | 5                                         |    |

1. Data based on characterization, tested in production.

|      |                     |                        | I <sub>DD</sub> (Typ Appli) | <u> </u> |        |

|------|---------------------|------------------------|-----------------------------|----------|--------|

| Ρ    | eripheral           | Scale 1 +<br>OverDrive | Scale 2                     | Scale 3  | Unit   |

|      | TIM2                | 18.18                  | 16.92                       | 15.07    |        |

|      | TIM3                | 14.49                  | 13.47                       | 12.00    |        |

|      | TIM4                | 15.18                  | 14.11                       | 12.50    |        |

|      | TIM5                | 16.91                  | 15.69                       | 14.07    |        |

|      | TIM6                | 2.69                   | 2.47                        | 2.20     |        |

|      | TIM7                | 2.56                   | 2.44                        | 2.17     |        |

|      | TIM12               | 7.07                   | 6.56                        | 5.83     |        |

|      | TIM13               | 4.96                   | 4.64                        | 4.07     |        |

| -    | TIM14               | 5.09                   | 4.72                        | 4.27     | _      |

| -    | WWDG                | 1.07                   | 1.00                        | 0.93     | _      |

| -    | SPI2 <sup>(2)</sup> | 1.89                   | 1.78                        | 1.57     | _      |

| -    | SPI3 <sup>(2)</sup> | 1.93                   | 1.81                        | 1.67     | _      |

| APB1 | SPDIFRX             | 6.91                   | 6.44                        | 5.80     | µA/MHz |

| -    | USART2              | 4.20                   | 3.83                        | 3.40     | _      |

| -    | USART3              | 4.22                   | 3.94                        | 3.50     | _      |

| -    | UART4               | 4.13                   | 3.89                        | 3.40     | _      |

|      | UART5               | 4.04                   | 3.78                        | 3.33     |        |

| -    | I2C1                | 3.98                   | 3.69                        | 3.33     | _      |

| -    | I2C2                | 3.91                   | 3.61                        | 3.17     | _      |

| -    | I2C3                | 3.76                   | 3.53                        | 3.13     | 1      |

| -    | FMPI2C1             | 5.51                   | 5.19                        | 4.57     | 1      |

| -    | CAN1                | 6.58                   | 6.14                        | 5.43     | 1      |

| -    | CAN2                | 5.91                   | 5.56                        | 4.90     | 1      |

| -    | CEC                 | 0.71                   | 0.69                        | 0.60     | 1      |

|      | DAC                 | 2.96                   | 2.72                        | 2.40     | 1      |

Table 35. Peripheral current consumption (continued)

| Symbol                                  | Parameter                                                            | Conditions                                                                               | Тур <sup>(1)</sup>                                                                      | Max <sup>(1)</sup> | Unit                  |

|-----------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|-----------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>     | Wakeup from Sleep                                                    | -                                                                                        | 6                                                                                       | 6                  | CPU<br>clock<br>cycle |

| T <sub>WUSLEEPFDSM</sub> <sup>(1)</sup> | Wakeup from Sleep<br>with Flash memory in<br>Deep power down<br>mode | -                                                                                        | 33.5                                                                                    | 50                 |                       |

| twustop <sup>(2)</sup>                  |                                                                      | Main regulator is ON                                                                     | 12.8                                                                                    | 15                 |                       |

|                                         | Wakeup from Stop<br>mode with MR/LP<br>regulator in normal<br>mode   | Main regulator is ON and Flash<br>memory in Deep power down mode                         | 104.9                                                                                   | 115                |                       |

|                                         |                                                                      | Low power regulator is ON                                                                | 20.6                                                                                    | 28                 |                       |

|                                         |                                                                      | Low power regulator is ON and<br>Flash memory in Deep power down<br>mode                 | 112.8                                                                                   | 120                | μs                    |

|                                         | Wakeup from Stop                                                     | Main regulator in under-drive mode<br>(Flash memory in Deep power-<br>down mode)         | 110                                                                                     | 140                |                       |

| t <sub>wustop</sub> (2)                 | mode with MR/LP<br>regulator in Under-drive<br>mode                  | Low power regulator in under-drive<br>mode<br>(Flash memory in Deep power-<br>down mode) | 33.5     50       12.8     15       104.9     115       20.6     28       112.8     120 |                    |                       |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup>  | Wakeup from Standby mode                                             | -                                                                                        | 325                                                                                     | 400                |                       |

1. Guaranteed based on test during characterization.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  maximum value is given at -40 °C.

### 6.3.9 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 56: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 23*.

The characteristics given in *Table 37* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 16*.

| Symbol                               | Parameter                     | Conditions                                        |                    | Min          | Тур  | Max          | Unit |

|--------------------------------------|-------------------------------|---------------------------------------------------|--------------------|--------------|------|--------------|------|

| t <sub>LOCK</sub>                    | PLL lock time                 | VCO freq = 100 M                                  | 1Hz                | 75           | -    | 200          |      |

| LOCK                                 |                               | VCO freq = 432 M                                  | 1Hz                | 100          | -    | 300          | μs   |

|                                      |                               |                                                   | RMS                | -            | 25   | -            |      |

|                                      | Cycle-to-cycle jitter         | System clock<br>120 MHz                           | peak<br>to<br>peak | -            | ±150 | -            |      |

| Jitter <sup>(3)</sup>                | Period Jitter                 |                                                   | RMS                | -            | 15   | -            | ps   |

| JILLEI                               |                               |                                                   | peak<br>to<br>peak | -            | ±200 | -            |      |

|                                      | Bit Time CAN jitter           | Cycle to cycle at <sup>2</sup><br>on 1000 samples |                    | -            | 330  | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD  | VCO freq = 100 MHz<br>VCO freq = 432 MHz          |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA | VCO freq = 100 M<br>VCO freq = 432 M              |                    | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

#### Table 43. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed based on test during characterization.

| Symbol                                                                                                                                                                                                                                                                                                                                         | Parameter                                                               | Conditions                                   |                    | Min                 | Тур  | Мах  | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------|--------------------|---------------------|------|------|------|

| f <sub>PLLI2S_IN</sub>                                                                                                                                                                                                                                                                                                                         | PLLI2S input clock <sup>(1)</sup>                                       | -                                            |                    | 0.95 <sup>(2)</sup> | 1    | 2.10 | MHz  |

| f <sub>PLLI2S_OUT</sub>                                                                                                                                                                                                                                                                                                                        | PLLI2S multiplier output clock                                          | -                                            |                    | -                   | -    | 216  | MHz  |

| f <sub>VCO_OUT</sub>                                                                                                                                                                                                                                                                                                                           | PLLI2S VCO output                                                       | -                                            |                    | 100                 | -    | 432  | MHz  |

| 4                                                                                                                                                                                                                                                                                                                                              | DLL I2S look time                                                       | VCO freq = 100 MHz                           |                    | 75                  | -    | 200  |      |

| <sup>t</sup> LOCK                                                                                                                                                                                                                                                                                                                              | PLLI25 lock lime                                                        | VCO freq = 432 MHz                           |                    | 100                 | -    | 300  | μs   |

| fPLLI2S_OUT       PLLI2S multiplier output clock         fVCO_OUT       PLLI2S VCO output         tLOCK       PLLI2S lock time         VCO freq       VCO freq         VCO freq       VCO freq         Jitter <sup>(3)</sup> Master I2S clock jitter         WS I2S clock iitter       Cycle to c         WS I2S clock iitter       Cycle to c | Mastar I2S alaak iittar                                                 | Cycle to cycle at                            | RMS                | -                   | 90   | -    | -    |

|                                                                                                                                                                                                                                                                                                                                                |                                                                         | 12.288 MHz on<br>48KHz period,<br>N=432, R=5 | peak<br>to<br>peak | -                   | ±280 | -    | ps   |

|                                                                                                                                                                                                                                                                                                                                                | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | f                                            | -                  | 90                  | -    | ps   |      |

|                                                                                                                                                                                                                                                                                                                                                | WS I2S clock jitter                                                     | Cycle to cycle at 48<br>on 1000 samples      | -                  | 400                 | -    | ps   |      |

#### Table 44. PLLI2S (audio PLL) characteristics

| Symbol                         | Parameter                                | Conditions                                               | Min                                 | Max                | Unit |

|--------------------------------|------------------------------------------|----------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup>                                 | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = +8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V | V <sub>DD</sub> -0.4                | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup>                                  | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> =+ 8mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V  | 2.4                                 | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +20 mA                                 | -                                   | 1.3 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 2.7 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -1.3 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +6 mA                                  | -                                   | 0.4 <sup>(4)</sup> | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.8 V ≤V <sub>DD</sub> ≤3.6 V                            | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA                                  | -                                   | 0.4 <sup>(5)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | 1.7 V ≤V <sub>DD</sub> ≤3.6V                             | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  | v    |

Table 57. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 14*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 14 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Based on characterization data.

- 5. Guaranteed by design.

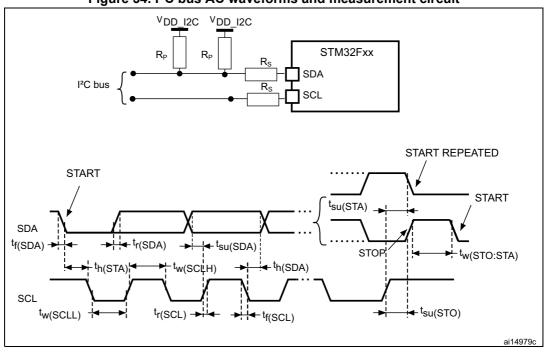

Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 32* and *Table 58*, respectively.

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*.

| OSPEEDR<br>y[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min | Тур | Max | Unit |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

|                                               |                                                  |                                                                                 | $C_L = 50 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$             | -   | -   | 4   |      |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 2   |      |

|                                               | f <sub>max(IO)out</sub>                          | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V             | -   | -   | 8   | MHz  |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V             | -   | -   | 4   |      |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -   | -   | 3   |      |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.7 V<br>to 3.6 V | -   | -   | 100 | ns   |

Table 58. I/O AC characteristics<sup>(1)(2)</sup>

1.  $R_S$  = series protection resistor.

2.  $R_P$  = external pull-up resistor.

3.  $V_{DD_{12C}}$  is the I2C bus power supply.

a

#### **SAI characteristics**

Unless otherwise specified, the parameters given in *Table 67* for SAI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and VDD supply voltage conditions summarized in *Table 16*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C=30 pF

- Measurement points are performed at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (SCK,SD,WS).

| Symbol                   | Parameter                          | Conditions                                                                        | Min      | Max                     | Unit |

|--------------------------|------------------------------------|-----------------------------------------------------------------------------------|----------|-------------------------|------|

| f <sub>MCK</sub>         | SAI Main clock output              | -                                                                                 | 256 x 8K | 256 x Fs                | MHz  |

| 5                        | SAI clock frequency <sup>(2)</sup> | Master data: 32 bits                                                              |          | 128 x Fs <sup>(3)</sup> | MHz  |

| f <sub>CK</sub>          | SAI Clock frequency                | Slave data: 32 bits                                                               | -        | 128 x Fs <sup>(3)</sup> | MHZ  |

| +                        | FS valid time                      | Valid time Master mode $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ |          | 14                      | %    |

| <sup>t</sup> v(FS)       |                                    | Master mode<br>1.71 V ≤ V <sub>DD</sub> ≤3.6 V                                    | -        | 17.5                    |      |

| t <sub>h(FS)</sub>       | FS hold time                       | Master mode                                                                       | 7        | -                       |      |

| t <sub>su(FS)</sub>      | FS setup time                      | Slave mode                                                                        | 1        | -                       |      |

| t <sub>h(FS)</sub>       | FS hold time                       | Slave mode                                                                        | 1        | -                       |      |

| t <sub>su(SD_A_MR)</sub> | Data input actus time              | Master receiver                                                                   | 1        | -                       |      |

| t <sub>su(SD_B_SR)</sub> | Data input setup time              | Slave receiver                                                                    | 1        | -                       |      |

| t <sub>h(SD_A_MR)</sub>  | Data input hald time               | Master receiver                                                                   | 5        | -                       |      |

| t <sub>h(SD_B_SR)</sub>  | Data input hold time               | Slave receiver                                                                    | 1        | -                       | ns   |

|                          | Data output valid time             | Slave trasmitter (after enable edge 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V     | -        | 9.5                     | 115  |

| t <sub>v(SD_B_ST)</sub>  |                                    | Slave transmitter (after enable edge 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V   | -        | 16                      |      |

| t <sub>h(SD_B_ST)</sub>  | Data output hold time              | Slave transmitter (after enable edge                                              | 6        | -                       |      |

| t en n c=                | Data output valid time             | Master transmitter (after enable edge 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V   | -        | 15                      |      |

| t <sub>v(SD_B_ST)</sub>  |                                    | Master transmitter (after enable edge 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V  | -        | 18                      |      |

| t <sub>h(SD_B_ST)</sub>  | Data output hold time              | Master transmitter (after enable edge                                             | 7        | -                       |      |

#### Table 67. SAI characteristics<sup>(1)</sup>

1. Guaranteed based on test during characterization.

2. 256xFs maximum corresponds to 45 MHz (APB2 xaximum frequency)

3. With Fs = 192 KHz

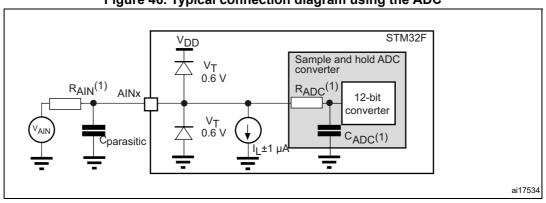

### 6.3.21 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 74* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 16*.

| Symbol                               | Parameter                                       | Conditions                                                                            | Min                                                         | Тур | Мах               | Unit               |

|--------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-------------------|--------------------|

| V <sub>DDA</sub>                     | Power supply                                    | N N 10N                                                                               | 1.7 <sup>(1)</sup>                                          | -   | 3.6               |                    |

| $V_{REF}$ +                          | Positive reference voltage                      | V <sub>DDA</sub> –V <sub>REF+</sub> < 1.2 V                                           | 1.7 <sup>(1)</sup>                                          | -   | V <sub>DDA</sub>  | V                  |

| V <sub>REF-</sub>                    | Negative reference voltage                      | -                                                                                     | -                                                           | 0   | -                 |                    |

| f                                    | ADC clock frequency                             | $V_{DDA} = 1.7^{(1)}$ to 2.4 V                                                        | 0.6                                                         | 15  | 18                | MHz                |

| f <sub>ADC</sub>                     | ADC clock frequency                             | V <sub>DDA</sub> = 2.4 to 3.6 V                                                       | 0.6                                                         | 30  | 36                | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>     | External trigger frequency                      | f <sub>ADC</sub> = 30 MHz,<br>12-bit resolution                                       | -                                                           | -   | 1764              | kHz                |

|                                      |                                                 | -                                                                                     | -                                                           | -   | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                     | Conversion voltage range <sup>(3)</sup>         | -                                                                                     | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -   | V <sub>REF+</sub> | V                  |

| $R_{AIN}^{(2)}$                      | External input impedance                        | See <i>Equation 1</i> for details                                                     | -                                                           | -   | 50                | κΩ                 |

| $R_{ADC}^{(2)(4)}$                   | Sampling switch resistance                      | -                                                                                     | -                                                           | -   | 6                 | κΩ                 |

| $C_{ADC}^{(2)}$                      | Internal sample and hold capacitor              | -                                                                                     | -                                                           | 4   | 7                 | pF                 |

| t <sub>lat</sub> (2)                 | Injection trigger conversion                    | f <sub>ADC</sub> = 30 MHz                                                             | -                                                           | -   | 0.100             | μs                 |

| 'lat` '                              | latency                                         | -                                                                                     | -                                                           | -   | 3 <sup>(5)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)                | Regular trigger conversion                      | f <sub>ADC</sub> = 30 MHz                                                             | -                                                           | -   | 0.067             | μs                 |

| 'latr'                               | latency                                         | -                                                                                     | -                                                           | -   | 2 <sup>(5)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(2)</sup>        | Sampling time                                   | f <sub>ADC</sub> = 30 MHz                                                             | 0.100                                                       | -   | 16                | μs                 |

| ις                                   |                                                 | -                                                                                     | 3                                                           | -   | 480               | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup>     | Power-up time                                   | -                                                                                     | -                                                           | 2   | 3                 | μs                 |

|                                      |                                                 | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution                                        | 0.50                                                        | -   | 16.40             | μs                 |

|                                      |                                                 | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution                                        | 0.43                                                        | -   | 16.34             | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> Tot | Total conversion time (including sampling time) | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution                                         | 0.37                                                        | -   | 16.27             | μs                 |

|                                      |                                                 | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution                                         | 0.30                                                        | -   | 16.20             | μs                 |

|                                      |                                                 | 9 to 492 (t <sub>S</sub> for sampling +n-bit resolution for successive approximation) |                                                             |     |                   |                    |

Figure 46. Typical connection diagram using the ADC

- 1. Refer to Table 74 for the values of  $R_{AIN}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

## 6.3.23 V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                            | Min | Тур | Мах | Unit |

|---------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                 | -   | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                                | -   | 4   | -   | -    |

| Er <sup>(1)</sup>                     | Error on Q                                                           | - 1 | -   | + 1 | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1 mV accuracy | 5   | -   | -   | μs   |

Table 82. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

### 6.3.24 Reference voltage

The parameters given in *Table 83* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*.

| Symbol                                | Parameter                                                        | Conditions                        | Min  | Тур  | Max  | Unit   |

|---------------------------------------|------------------------------------------------------------------|-----------------------------------|------|------|------|--------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                       | –40 °C < T <sub>A</sub> < +105 °C | 1.18 | 1.21 | 1.24 | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the<br>internal reference voltage | -                                 | 10   | -    | -    | μs     |

| V <sub>RERINT_s</sub> <sup>(2)</sup>  | Internal reference voltage spread over the temperature range     | $V_{DD}$ = 3V $\pm$ 10mV          | -    | 3    | 5    | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                          | -                                 | -    | 30   | 50   | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                                     | -                                 | -    | 6    | 10   | μs     |

Table 83. internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

#### Table 84. Internal reference voltage calibration values

| Symbol                 | Parameter                                                                        | Memory address            |

|------------------------|----------------------------------------------------------------------------------|---------------------------|

| V <sub>REFIN_CAL</sub> | Raw data acquired at temperature of 30 $^\circ\text{C}$ $_{\text{VDDA}}$ = 3.3 V | 0x1FFF 7A2A - 0x1FFF 7A2B |

## 6.3.25 DAC electrical characteristics

| Table | 85. | DAC | characteristics |

|-------|-----|-----|-----------------|

|-------|-----|-----|-----------------|

| Symbol            | Parameter                | Conditions | Min                | Тур | Мах | Unit | Comments                            |

|-------------------|--------------------------|------------|--------------------|-----|-----|------|-------------------------------------|

| V <sub>DDA</sub>  | Analog supply voltage    | -          | 1.7 <sup>(1)</sup> | -   | 3.6 | V    | -                                   |

| V <sub>REF+</sub> | Reference supply voltage | -          | 1.7 <sup>(1)</sup> | -   | 3.6 | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub> |

| Symbol                        | Parameter              | Min                      | Max                      | Unit |

|-------------------------------|------------------------|--------------------------|--------------------------|------|

| F <sub>(SDCLK)</sub>          | Frequency of operation | -                        | 84                       | MHz  |

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> - 0.5 | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>d(SDCLKL</sub> _Data)  | Data output valid time | -                        | 5                        |      |

| t <sub>h(SDCLKL</sub> _Data)  | Data output hold time  | 0.5                      | -                        |      |

| t <sub>d(SDCLK_Add)</sub>     | Address valid time     | -                        | 3                        |      |

| t <sub>d(SDCLKL_SDNWE))</sub> | SDNWE valid time       | -                        | 3                        |      |

| t <sub>h(SDCLKL_SDNWE))</sub> | SDNWE hold time        | 0                        | -                        | ns   |

| t <sub>d(SDCLKL_SDNE))</sub>  | Chip select valid time | -                        | 2.5                      | 115  |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0                        | -                        |      |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 2                        |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                        |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 2                        |      |

| $t_{d(SDCLKL\_SDNCAS)}$       | SDNCAS hold time       | 0                        | -                        |      |

1. CL = 10 pF.

2. Guaranteed based on test during characterization.

## 6.3.27 Camera interface (DCMI) timing specifications

Unless otherwise specified, the parameters given in *Table 104* for DCMI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage summarized in *Table 16*, with the following configuration:

- DCMI\_PIXCLK polarity: falling

- DCMI\_VSYNC and DCMI\_HSYNC polarity: high

- Data formats: 14 bits

| Symbol                                           | Parameter                                     | Min | Max | Unit |  |  |  |  |

|--------------------------------------------------|-----------------------------------------------|-----|-----|------|--|--|--|--|

| -                                                | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> | -   | 0.4 | -    |  |  |  |  |

| DCMI_PIXCLK                                      | Pixel clock input                             | -   | 54  | MHz  |  |  |  |  |

| D <sub>Pixel</sub>                               | Pixel clock input duty cycle                  | 30  | 70  | %    |  |  |  |  |

| t <sub>su(DATA)</sub>                            | Data input setup time                         | 1   | -   |      |  |  |  |  |

| t <sub>h(DATA)</sub>                             | Data input hold time                          | 3.5 | -   |      |  |  |  |  |

| t <sub>su(HSYNC)</sub><br>t <sub>su(VSYNC)</sub> | DCMI_HSYNC/DCMI_VSYNC input setup time        | 2   | -   | ns   |  |  |  |  |

| t <sub>h(HSYNC)</sub><br>t <sub>h(VSYNC)</sub>   | DCMI_HSYNC/DCMI_VSYNC input hold time         | 0   | -   |      |  |  |  |  |

#### Table 104. DCMI characteristics

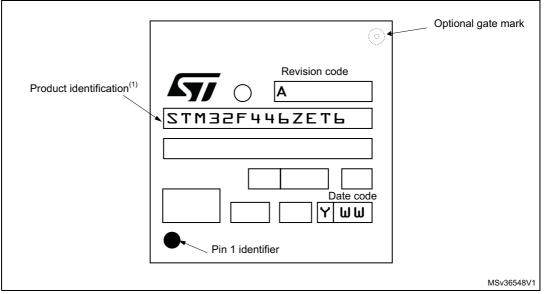

#### Device marking for LQFP144 package

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 75. LQFP144 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# **Revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17-Feb-2015 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16-Mar-2015 | 2        | Added note 2 inside Table 2<br>Updated Table 11, Table 23, Table 24, Table 25, Table 26, Table 30,<br>Table 51, Table 52, Table 53, and Table 61<br>Added condition inside Typical and maximum current consumption and<br>Additional current consumption<br>Added FMPI2C characteristics<br>Added Table 62 and Figure 35                                                                                                                                                                                                                                                                                                           |

| 29-May-2015 | 3        | <ul> <li>Updated:</li> <li>Section 6.3.15: Absolute maximum ratings (electrical sensitivity)</li> <li>Section 7: Package information</li> <li>Table 2: STM32F446xC/E features and peripheral counts</li> <li>Table 13: STM32F446xC/xE WLCSP81 ballout</li> <li>Figure 53: ESD absolute maximum ratings</li> <li>Figure 54: Synchronous multiplexed NOR/PSRAM read timings</li> <li>Added:</li> <li>Figure 78: UQFP144 7 x 7 mm marking example (package top view),</li> <li>Figure 81: UQFP144 10 x 10 mm marking example (package top view),</li> <li>Figure 84: WLCSP81 10 x 10 mm marking example (package top view)</li> </ul> |

| 10-Aug-2015 | 4        | Updated:<br>- Figure 14: STM32F446xC/xE UFBGA144 ballout<br>- Table 10: STM32F446xx pin and ball descriptions<br>- Table 18: VCAP_1/VCAP_2 operating conditions<br>- Section 3.15: Power supply schemes<br>- Section 6.3.2: VCAP_1/VCAP_2 external capacitor<br>Added:<br>- Figure 5: VDDUSB connected to an external independent power<br>supply<br>- Notes 3 and 4 below Figure 18: Power supply scheme                                                                                                                                                                                                                          |