#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                                |

| Speed                      | 180MHz                                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 114                                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                             |

| EEPROM Size                | -                                                                                                 |

| RAM Size                   | 128K x 8                                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                             |

| Oscillator Type            | Internal                                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                |

| Mounting Type              | Surface Mount                                                                                     |

| Package / Case             | 144-LQFP                                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f446zet7                             |

|                            |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F446xC/E devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 180 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

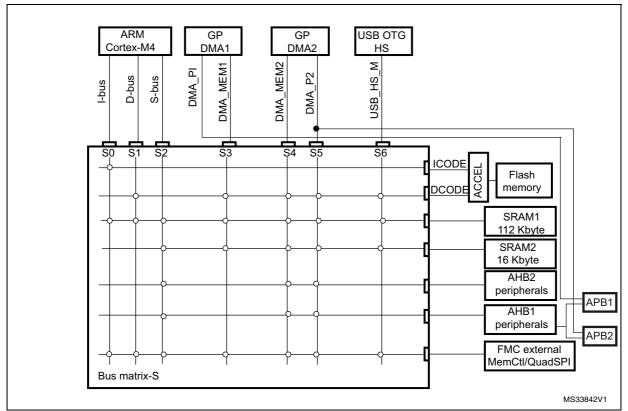

The STM32F446xC/E devices incorporate high-speed embedded memories (Flash memory up to 512 Kbyte, up to 128 Kbyte of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers.

They also feature standard and advanced communication interfaces.

- Up to four I<sup>2</sup>Cs;

- Four SPIs, three I<sup>2</sup>Ss full simplex. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization;

- Four USARTs plus two UARTs;

- An USB OTG full-speed and an USB OTG high-speed with full-speed capability (with the ULPI), both with dedicated power rails allowing to use them throughout the entire power range;

- Two CANs;

- Two SAIs serial audio interfaces. To achieve audio class accuracy, the SAIs can be clocked via a dedicated internal audio PLL;

- An SDIO/MMC interface;

- Camera interface;

- HDMI-CEC;

- SPDIF Receiver (SPDIFRx);

- QuadSPI.

Advanced peripherals include an SDIO, a flexible memory control (FMC) interface, a camera interface for CMOS sensors. Refer to *Table 2: STM32F446xC/E features and peripheral counts* for the list of peripherals available on each part number.

The STM32F446xC/E devices operates in the -40 to +105 °C temperature range from a 1.7 to 3.6 V power supply.

The supply voltage can drop to 1.7 V with the use of an external power supply supervisor (refer to *Section 3.16.2: Internal reset OFF*). A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F446xC/E devices offer devices in 6 packages ranging from 64 pins to 144 pins. The set of included peripherals changes with the device chosen.

- For the LQFP100 package, only FMC Bank1 or Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

- 2. The SPI1, SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

- 3. For the LQFP64 package, the Quad SPI is available with limited features.

- V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section 3.16.2: Internal reset OFF).

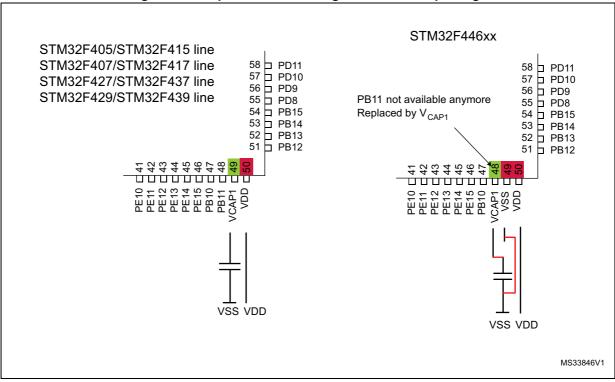

## 2.1 Compatibility with STM32F4 family

The STM32F446xC/xV is software and feature compatible with the STM32F4 family.

The STM32F446xC/xV can be used as drop-in replacement of the other STM32F4 products but some slight changes have to be done on the PCB board.

#### Figure 1. Compatible board design for LQFP100 package

## **3** Functional overview

# 3.1 **ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU and embedded Flash and SRAM**

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core is a 32-bit RISC processor that features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F446xC/E family is compatible with all ARM tools and software.

*Figure 3* shows the general block diagram of the STM32F446xC/E family.

Note: Cortex-M4 with FPU core is binary compatible with the Cortex-M3 core.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 225 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART Accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 180 MHz.

## 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

DocID027107 Rev 6

Figure 4. STM32F446xC/E and Multi-AHB matrix

## 3.8 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

|        | Piı     | n Num    | nber     |         |                                    |          |               |       |                                                                              |                         |

|--------|---------|----------|----------|---------|------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------|-------------------------|

| LQFP64 | LQFP100 | WLCSP 81 | UFBGA144 | LQFP144 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                          | Additional<br>functions |

| -      | 5       | -        | B4       | 5       | PE6                                | I/O      | FT            | -     | TRACED3, TIM9_CH2,<br>SPI4_MOSI, SAI1_SD_A,<br>FMC_A22, DCMI_D7,<br>EVENTOUT | -                       |

| 1      | 6       | B9       | C2       | 6       | VBAT                               | S        | -             | -     | -                                                                            | -                       |

| 2      | 7       | C8       | A1       | 7       | PC13                               | I/O      | FT            | -     | EVENTOUT                                                                     | TAMP_1/WKUP1            |

| 3      | 8       | C9       | B1       | 8       | PC14-<br>OSC32_IN(PC14)            | I/O      | FT            | -     | EVENTOUT                                                                     | OSC32_IN                |

| 4      | 9       | D9       | C1       | 9       | PC15-<br>OSC32_OUT(PC15)           | I/O      | FT            | -     | EVENTOUT                                                                     | OSC32_OUT               |

| -      | -       | -        | C3       | 10      | PF0                                | I/O      | FT            | -     | I2C2_SDA, FMC_A0,<br>EVENTOUT                                                | -                       |

| -      | -       | -        | C4       | 11      | PF1                                | I/O      | FT            | -     | I2C2_SCL, FMC_A1,<br>EVENTOUT                                                | -                       |

| -      | -       | -        | D4       | 12      | PF2                                | I/O      | FT            | -     | I2C2_SMBA, FMC_A2,<br>EVENTOUT                                               | -                       |

| -      | -       | -        | E2       | 13      | PF3                                | I/O      | FT            | -     | FMC_A3, EVENTOUT                                                             | ADC3_IN9                |

| -      | -       | -        | E3       | 14      | PF4                                | I/O      | FT            | -     | FMC_A4, EVENTOUT                                                             | ADC3_IN14               |

| -      | -       | -        | E4       | 15      | PF5                                | I/O      | FT            | -     | FMC_A5, EVENTOUT                                                             | ADC3_IN15               |

| -      | 10      | -        | D2       | 16      | VSS                                | S        | -             | -     | -                                                                            | -                       |

| -      | 11      | -        | D3       | 17      | VDD                                | S        | -             | -     | -                                                                            | -                       |

| -      | -       | -        | F3       | 18      | PF6                                | I/O      | FT            | -     | TIM10_CH1, SAI1_SD_B,<br>QUADSPI_BK1_IO3,<br>EVENTOUT                        | ADC3_IN4                |

| -      | -       | -        | F2       | 19      | PF7                                | I/O      | FT            | -     | TIM11_CH1,<br>SAI1_MCLK_B,<br>QUADSPI_BK1_IO2,<br>EVENTOUT                   | ADC3_IN5                |

| -      | -       | -        | G3       | 20      | PF8                                | I/O      | FT            | -     | SAI1_SCK_B, TIM13_CH1,<br>QUADSPI_BK1_IO0,<br>EVENTOUT                       | ADC3_IN6                |

| -      | -       | -        | G2       | 21      | PF9                                | I/O      | FT            | -     | SAI1_FS_B, TIM14_CH1,<br>QUADSPI_BK1_IO1,<br>EVENTOUT                        | ADC3_IN7                |

| -      | -       | -        | G1       | 22      | PF10                               | I/O      | FT            | -     | DCMI_D11, EVENTOUT                                                           | ADC3_IN8                |

| 5      | 12      | E9       | D1       | 23      | PH0-OSC_IN(PH0)                    | I/O      | FT            | -     | EVENTOUT                                                                     | OSC_IN                  |

|        | Pir     | n Num    | nber     |         |                                    |          |               |       |                     |                         |

|--------|---------|----------|----------|---------|------------------------------------|----------|---------------|-------|---------------------|-------------------------|

| LQFP64 | LQFP100 | WLCSP 81 | UFBGA144 | LQFP144 | Pin name (function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions | Additional<br>functions |

| 63     | 99      | B7       | E6       | -       | VSS                                | S        | -             | -     | -                   | -                       |

| -      | -       | B8       | E5       | 143     | PDR_ON                             | S        | -             | -     | -                   | -                       |

| 64     | 100     | A8       | F5       | 144     | VDD                                | S        | -             | -     | -                   | -                       |

1. PA11, PA12, PB14 and PB15 I/Os are supplied by VDDUSB

STM32F446xC/E

Pinout and pin description

|        |      | AF0         | AF1    | AF2      | AF3                      | AF4                | AF5                       | AF6                       | AF7                                             | AF8                                    | AF9                                   | AF10                                     | AF11    | AF12                     | AF13    | AF14 | AF        |

|--------|------|-------------|--------|----------|--------------------------|--------------------|---------------------------|---------------------------|-------------------------------------------------|----------------------------------------|---------------------------------------|------------------------------------------|---------|--------------------------|---------|------|-----------|

| Po     | ort  | SYS         | TIM1/2 | TIM3/4/5 | TIM8/9/<br>10/11/<br>CEC | I2C1/2/3<br>/4/CEC | SPI1/2/3/<br>4            | SPI2/3/4/<br>SAI1         | SPI2/3/<br>USART1/<br>2/3/UART<br>5/SPDIFR<br>X | SAI/<br>USART6/<br>UART4/5/<br>SPDIFRX | CAN1/2<br>TIM12/13/<br>14/<br>QUADSPI | SAI2/<br>QUADSPI/<br>OTG2_HS/<br>OTG1_FS | OTG1_FS | FMC/<br>SDIO/<br>OTG2_FS | DCMI    | -    | S         |

|        | PC0  | -           | -      | -        | -                        | -                  | -                         | SAI1_<br>MCLK_B           | -                                               | -                                      | -                                     | OTG_HS_<br>ULPI_STP                      | -       | FMC_<br>SDNWE            | -       | -    | EVE       |

|        | PC1  | -           | -      | -        | -                        | -                  | SPI3_MOSI<br>/I2S3_SD     | SAI1_<br>SD_A             | SPI2_MOS<br>I<br>/I2S2_SD                       | -                                      | -                                     | -                                        | -       | -                        | -       | -    | EVE       |

|        | PC2  | -           | -      | -        | -                        | -                  | SPI2_MISO                 | -                         | -                                               | -                                      | -                                     | OTG_HS_<br>ULPI_DIR                      | -       | FMC_<br>SDNE0            | -       | -    | EVE<br>OL |

|        | PC3  | -           | -      | -        | -                        | -                  | SPI2_MOSI<br>/<br>I2S2_SD | -                         | -                                               | -                                      | -                                     | OTG_HS_<br>ULPI_NXT                      | -       | FMC_<br>SDCKE0           | -       | -    | EVE<br>OL |

|        | PC4  | -           | -      | -        | -                        | -                  | I2S1_MCK                  | -                         | -                                               | SPDIF_<br>RX2                          | -                                     | -                                        | -       | FMC_<br>SDNE0            | -       | -    | EVE<br>OL |

|        | PC5  | -           | -      | -        | -                        | -                  | -                         | -                         | USART3_<br>RX                                   | SPDIF_<br>RX3                          | -                                     | -                                        | -       | FMC_<br>SDCKE0           | -       | -    | EVE       |

|        | PC6  | -           | -      | TIM3_CH1 | TIM8_CH1                 | FMPI2C1<br>_SCL    | 12S2_MCK                  | -                         | -                                               | USART6_T<br>X                          | -                                     | -                                        | -       | SDIO_D6                  | DCMI_D0 | -    | EVE<br>OL |

| Port C | PC7  | -           | -      | TIM3_CH2 | TIM8_CH2                 | FMPI2C1<br>_SDA    | SPI2_SCK/<br>I2S2_CK      | I2S3_MCK                  | SPDIF_<br>RX1                                   | USART6_R<br>X                          | -                                     | -                                        | -       | SDIO_D7                  | DCMI_D1 | -    | EVE<br>OL |

|        | PC8  | TRACE<br>D0 | -      | TIM3_CH3 | TIM8_CH3                 | -                  | -                         | -                         | UART5_<br>RTS                                   | USART6_C<br>K                          | -                                     | -                                        | -       | SDIO_D0                  | DCMI_D2 | -    | EVE<br>OL |

|        | PC9  | MCO2        | -      | TIM3_CH4 | TIM8_CH4                 | I2C3_<br>SDA       | I2S_CKIN                  | -                         | UART5_<br>CTS                                   | -                                      | QUADSPI_<br>BK1_IO0                   | -                                        | -       | SDIO_D1                  | DCMI_D3 | -    | EVE<br>OL |

|        | PC10 | -           | -      | -        | -                        | -                  | -                         | SPI3_SCK<br>/<br>I2S3_CK  | USART3_<br>TX                                   | UART4_TX                               | QUADSPI_<br>BK1_IO1                   | -                                        | -       | SDIO_D2                  | DCMI_D8 | -    | EVE<br>OL |

|        | PC11 | -           | -      | -        | -                        | -                  | -                         | SPI3_<br>MISO             | USART3_<br>RX                                   | UART4_RX                               | QUADSPI_<br>BK2_NCS                   | -                                        | -       | SDIO_D3                  | DCMI_D4 | -    | EVE<br>OL |

|        | PC12 | -           | -      | -        | -                        | I2C2_<br>SDA       | -                         | SPI3_<br>MOSI/<br>I2S3_SD | USART3_<br>CK                                   | UART5_TX                               | -                                     | -                                        | -       | SDIO_CK                  | DCMI_D9 | -    | EVE<br>OL |

|        | PC13 | -           | -      | -        | -                        | -                  | -                         | -                         | -                                               | -                                      | -                                     | -                                        | -       | -                        | -       | -    | EVE<br>OL |

|        | PC14 | -           | -      | -        | -                        | -                  | -                         | -                         | -                                               | -                                      | -                                     | -                                        | -       | -                        | -       | -    | EVE<br>OL |

|        | PC15 | -           | -      | -        | -                        | -                  | -                         | -                         | -                                               | -                                      | -                                     | -                                        | -       | -                        | -       | -    | EVE       |

|        |                     |                               |                                           |                    |                    |                           | Max                       |                           |       |  |

|--------|---------------------|-------------------------------|-------------------------------------------|--------------------|--------------------|---------------------------|---------------------------|---------------------------|-------|--|

| Symbol | Parameter           | Condi                         | itions fHCLK<br>(MHz)                     |                    | Тур                | T <sub>A</sub> = 25<br>°C | T <sub>A</sub> = 25<br>°C | T <sub>A</sub> = 25<br>°C | Unit  |  |

|        |                     |                               |                                           | 180                | 51.2               | 59.00                     | 77.25                     | 102.00                    |       |  |

|        |                     |                               | External<br>clock,<br>PLL ON,<br>Flash on | 168 <sup>(2)</sup> | 46.8               | 53.94                     | 66.48                     | 79.40                     |       |  |

|        |                     |                               |                                           | 150                | 42.2               | 49.26                     | 60.84                     | 73.41                     |       |  |

|        |                     | all<br>peripherals<br>enabled |                                           |                    | 144 <sup>(2)</sup> | 38.6                      | 45.37                     | 55.47                     | 66.96 |  |

|        |                     |                               |                                           | 120                | 29.3               | 35.70                     | 42.49                     | 51.46                     |       |  |

|        | Supply              |                               |                                           |                    | 90                 | 22.8                      | 29.17                     | 34.78                     | 43.12 |  |

| IDD    | current in<br>Sleep |                               |                                           | 60                 | 16.3               | 22.41                     | 27.12                     | 34.83                     | mA    |  |

|        | mode                |                               |                                           |                    | 30                 | 10.1                      | 16.03                     | 19.72                     | 26.86 |  |

|        |                     |                               |                                           | 25                 | 9.0                | 14.92                     | 18.41                     | 25.38                     |       |  |

|        |                     |                               |                                           | 16                 | 6.5                | 13.10                     | 15.1                      | 22.3                      |       |  |

|        |                     |                               | HSI, PLL                                  | 8                  | 5.2                | 12.31                     | 13.5                      | 20.4                      |       |  |

|        |                     |                               | off, Flash<br>on                          | 4                  | 4.5                | 11.63                     | 12.5                      | 19.3                      |       |  |

|        |                     |                               |                                           | 2                  | 4.1                | 11.23                     | 12.0                      | 18.8                      |       |  |

| Table 26. Typical and maximum current consumption in Sleep mode <sup>(1)</sup> |

|--------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------|

|                      |                                      |                                                                     |                                   | Typ <sup>(1)</sup>         |                            |                  | Max <sup>(2)</sup>        |                            |      |  |

|----------------------|--------------------------------------|---------------------------------------------------------------------|-----------------------------------|----------------------------|----------------------------|------------------|---------------------------|----------------------------|------|--|

| Symbol               | Parameter                            | Conditions                                                          | Conditions T <sub>A</sub> = 25 °C |                            |                            |                  | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

|                      |                                      |                                                                     | V <sub>DD</sub> =<br>1.7 V        | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | v                | , <sub>DD</sub> = 3.3     | v                          |      |  |

|                      |                                      | Backup SRAM ON, and LSE oscillator in low power mode                | 2.43                              | 3.44                       | 4.12                       | 7                | 20                        | 36                         |      |  |

| I <sub>DD_STBY</sub> | Supply<br>current in<br>Standby mode | Backup SRAM OFF, RTC ON<br>and LSE oscillator in low<br>power mode  | 1.81                              | 2.81                       | 3.33                       | 6                | 17                        | 31                         |      |  |

|                      |                                      | Backup SRAM ON, RTC ON<br>and LSE oscillator in high<br>drive mode  | 3.32                              | 4.33                       | 4.95                       | 8                | 21                        | 37                         | μA   |  |

|                      |                                      | Backup SRAM OFF, RTC ON<br>and LSE oscillator in high<br>drive mode | 2.57                              | 3.59                       | 4.16                       | 7                | 18                        | 32                         |      |  |

|                      |                                      | Backup SRAM ON, RTC and LSE OFF                                     | 2.03                              | 2.73                       | 3.5                        | 6 <sup>(3)</sup> | 19                        | 35 <sup>(3)</sup>          |      |  |

|                      |                                      | Backup SRAM OFF, RTC<br>and LSE OFF                                 | 1.28                              | 1.97                       | 2.03                       | 5 <sup>(3)</sup> | 16                        | 30 <sup>(3)</sup>          |      |  |

| Table 28. Typical and maximum current consumptions in Standby mode |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

1. When the PDR is OFF (internal reset is OFF), the typical current consumption is reduced by 1.2  $\mu$ A.

2. Guaranteed based on test during characterization unless otherwise specified.

3. Tested in production.

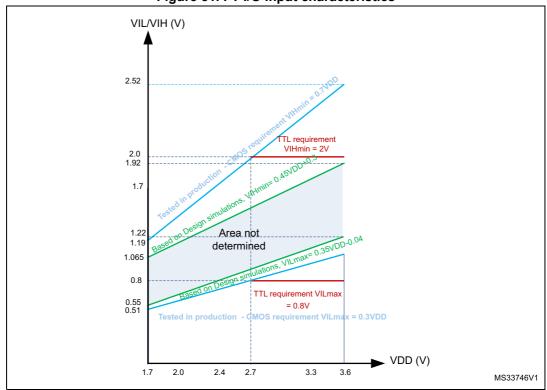

Figure 31. FT I/O input characteristics

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 14*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 14*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*. All I/Os are CMOS and TTL compliant.

|                       |                        | · · · · · ·                               |     |     |      |  |  |  |

|-----------------------|------------------------|-------------------------------------------|-----|-----|------|--|--|--|

| Symbol                | Parameter              | Conditions                                | Min | Max | Unit |  |  |  |

| t <sub>v(WS)</sub>    | WS valid time          | Master mode                               | -   | 5.5 |      |  |  |  |

| t <sub>h(WS)</sub>    | WS hold time           | Master mode                               | 1   | -   |      |  |  |  |

| t <sub>su(WS)</sub>   | WS actus time          | Slave mode                                | 1   | -   |      |  |  |  |

| -                     | WS setup time          | PCM short pulse Slave mode <sup>(3)</sup> | 2   | -   |      |  |  |  |

| t <sub>h(WS)</sub>    | WS hold time           | Slave mode                                | 3   | -   |      |  |  |  |

| -                     |                        | PCM short pulse Slave mode <sup>(3)</sup> | 1.5 | -   |      |  |  |  |

| $t_{su(SD_MR)}$       | Data input setup time  | Master receiver                           | 3   | -   | 20   |  |  |  |

| $t_{su(SD\_SR)}$      | Data input setup time  | Slave receiver                            | 2.5 | -   | ns   |  |  |  |

| t <sub>h(SD_MR)</sub> | Data input hold time   | Master receiver                           | 4   | -   |      |  |  |  |

| t <sub>h(SD_SR)</sub> |                        | Slave receiver                            | 1   | -   |      |  |  |  |

| $t_{v(SD\_ST)}$       | Data output valid time | Slave transmitter (after enable edge)     | -   | 16  |      |  |  |  |

| t <sub>v(SD_MT)</sub> | Data output valid time | Master transmitter (after enable edge)    | -   | 4.5 |      |  |  |  |

| t <sub>h(SD_ST)</sub> | Data output hold time  | Slave transmitter (after enable edge)     | 5   | -   |      |  |  |  |

| t <sub>h(SD_MT)</sub> | Data output hold time  | Master transmitter (after enable edge)    | 1   | -   |      |  |  |  |

| Table 66. I <sup>2</sup> S dynamic characteristics <sup>(1)</sup> (c | continued) |

|----------------------------------------------------------------------|------------|

|----------------------------------------------------------------------|------------|

1. Guaranteed based on test during characterization.

2. The maximum value of 256xFs is 45 MHz (APB1 maximum frequency).

3. Measurement done with respect to I2S\_CK rising edge.

Note: Refer to the I2S section of RM0390 reference manual for more details on the sampling frequency ( $F_S$ ).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

| Syn             | nbol                                                                                                                                                                                                | Parameter                                                 | Conditions                                                            | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|---------------------|------|---------------------|------|

| Input<br>levels | V <sub>DDUSB</sub>                                                                                                                                                                                  | USB OTG full speed<br>transceiver operating<br>voltage    | -                                                                     | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |

|                 | V <sub>DI</sub> <sup>(3)</sup> Differential input<br>sensitivity I(USB_FS_DP/DM,<br>USB_HS_DP/DM)   V <sub>CM</sub> <sup>(3)</sup> Differential common mode<br>range Includes V <sub>DI</sub> range |                                                           | 0.2                                                                   | -                   | -    |                     |      |

|                 |                                                                                                                                                                                                     |                                                           | 0.8                                                                   | -                   | 2.5  | V                   |      |

|                 | $V_{SE}^{(3)}$                                                                                                                                                                                      | Single ended receiver threshold                           | -                                                                     | 1.3                 | -    | 2.0                 |      |

| Output          | V <sub>OL</sub>                                                                                                                                                                                     | Static output level low                                   | ${\sf R}_{\sf L}$ of 1.5 k\Omega to 3.6 ${\sf V}^{(4)}$               | -                   | -    | 0.3                 | V    |

| levels          | V <sub>OH</sub>                                                                                                                                                                                     | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 ${\sf k}\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |

| R <sub>PD</sub> |                                                                                                                                                                                                     | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DDUSB</sub>                                  | 17                  | 21   | 24                  |      |

|                 |                                                                                                                                                                                                     | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDDUSB                                                          | 0.65                | 1.1  | 2.0                 | kΩ   |

| R <sub>PU</sub> |                                                                                                                                                                                                     | PA12, PB15<br>(USB_FS_DP,<br>USB_HS_DP)                   | V <sub>IN</sub> = V <sub>SS</sub>                                     | 1.5                 | 1.8  | 2.1                 | N22  |

|                 |                                                                                                                                                                                                     | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                     | 0.25                | 0.37 | 0.55                |      |

1. All the voltages are measured from the local ground potential.

2. The USB OTG full speed transceiver functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design.

4. R<sub>L</sub> is the load connected on the USB OTG full speed drivers.

Note: When VBUS sensing feature is enabled, PA9 and PB13 should be left at their default state (floating input), not as alternate function. A typical 200 µA current consumption of the sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 and PB13 when the feature is enabled.

## 6.3.23 V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                            | Min | Тур | Мах | Unit |

|---------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                 | -   | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                                | -   | 4   | -   | -    |

| Er <sup>(1)</sup>                     | Error on Q                                                           | - 1 | -   | + 1 | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1 mV accuracy | 5   | -   | -   | μs   |

Table 82. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.24 Reference voltage

The parameters given in *Table 83* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*.

| Symbol                                | Parameter                                                     | Conditions                        | Min  | Тур  | Max  | Unit   |

|---------------------------------------|---------------------------------------------------------------|-----------------------------------|------|------|------|--------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                    | –40 °C < T <sub>A</sub> < +105 °C | 1.18 | 1.21 | 1.24 | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the internal reference voltage | -                                 | 10   | -    | -    | μs     |

| V <sub>RERINT_s</sub> <sup>(2)</sup>  | Internal reference voltage spread over the temperature range  | $V_{DD}$ = 3V $\pm$ 10mV          | -    | 3    | 5    | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                       | -                                 | -    | 30   | 50   | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                                  | -                                 | -    | 6    | 10   | μs     |

Table 83. internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

#### Table 84. Internal reference voltage calibration values

| Symbol                 | Parameter                                                                        | Memory address            |

|------------------------|----------------------------------------------------------------------------------|---------------------------|

| V <sub>REFIN_CAL</sub> | Raw data acquired at temperature of 30 $^\circ\text{C}$ $_{\text{VDDA}}$ = 3.3 V | 0x1FFF 7A2A - 0x1FFF 7A2B |

## 6.3.25 DAC electrical characteristics

| Table | 85. | DAC | characteristics |

|-------|-----|-----|-----------------|

|-------|-----|-----|-----------------|

| Symbol            | Parameter                | Conditions | Min                | Тур | Мах | Unit | Comments                            |

|-------------------|--------------------------|------------|--------------------|-----|-----|------|-------------------------------------|

| V <sub>DDA</sub>  | Analog supply voltage    | -          | 1.7 <sup>(1)</sup> | -   | 3.6 | V    | -                                   |

| V <sub>REF+</sub> | Reference supply voltage | -          | 1.7 <sup>(1)</sup> | -   | 3.6 | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub> |

| Symbol                    | Parameter                             | Min                    | Мах                       | Unit |

|---------------------------|---------------------------------------|------------------------|---------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                       | 2T <sub>HCLK</sub> – 2 | 2 T <sub>HCLK</sub> + 0.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low            | 0                      | 1                         |      |

| t <sub>w(NOE)</sub>       | FMC_NOE low time                      | 2T <sub>HCLK</sub> - 1 | 2T <sub>HCLK</sub> + 0.5  |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time | 0                      | -                         |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid            | -                      | 0.5                       |      |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high  | 0                      | -                         |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid           | -                      | 2                         |      |

| t <sub>h(BL_NOE)</sub>    | FMC_BL hold time after FMC_NOE high   | 0                      | -                         | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time       | T <sub>HCLK</sub> - 2  | -                         |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOEx high setup time      | T <sub>HCLK</sub> - 2  | -                         |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high     | 0                      | -                         |      |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high     | 0                      | -                         |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low           | -                      | 0                         |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                     | -                      | T <sub>HCLK</sub> +1      |      |

Table 86. Asynchronous non-multiplexed SRAM/PSRAM/NOR - read timings  $^{(1)(2)}$

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

| Table 87. Asynchronous non-multiplexed SRAM/PSRAM/NOR read - |

|--------------------------------------------------------------|

| NWAIT timings <sup>(1)(2)</sup>                              |

| Symbol                    | Parameter                                 | Min                      | Мах                    | Unit |

|---------------------------|-------------------------------------------|--------------------------|------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 7T <sub>HCLK</sub> + 1   | 7T <sub>HCLK</sub>     |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> – 1   | 5T <sub>HCLK</sub> + 1 |      |

| t <sub>w(NWAIT)</sub>     | FMC_NWAIT low time                        | T <sub>HCLK</sub> – 0.5  | -                      | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> + 1.5 | -                      |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> + 1   | -                      |      |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

| Symbol                    | Parameter                                               | Min                      | Max                     | Unit |

|---------------------------|---------------------------------------------------------|--------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                         | 3T <sub>HCLK</sub> – 2   | 3T <sub>HCLK</sub> +0.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low                              | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub>      |      |

| t <sub>tw(NOE)</sub>      | FMC_NOE low time                                        | T <sub>HCLK</sub> – 1    | T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time                   | 0                        | -                       |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                              | -                        | 2                       |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                             | 0                        | 2                       |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                       | T <sub>HCLK</sub> – 0.5  | T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(address) valid hold time after<br>FMC_NADV high) | 0                        | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high                    | T <sub>HCLK</sub> – 0.5  | -                       |      |

| t <sub>h(BL_NOE)</sub>    | FMC_BL time after FMC_NOE high                          | 0                        | -                       |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                             | -                        | 2                       |      |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time                         | T <sub>HCLK</sub> + 1.5  | -                       |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOE high setup time                         | T <sub>HCLK</sub> + 1    | -                       |      |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high                       | 0                        | -                       |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high                       | 0                        | -                       |      |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

| Symbol                    | Parameter                                 | Min                      | Мах                    | Unit |

|---------------------------|-------------------------------------------|--------------------------|------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> - 1   | 8T <sub>HCLK</sub> + 2 |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> – 1   | 5T <sub>HCLK</sub> + 1 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> + 1.5 | -                      |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> + 1   | -                      |      |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed based on test during characterization.

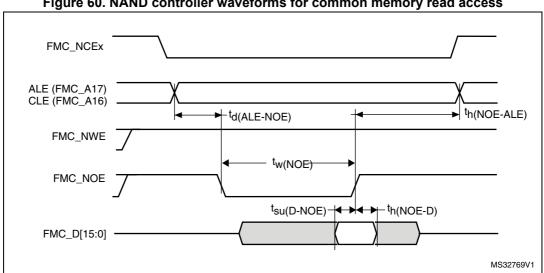

Figure 60. NAND controller waveforms for common memory read access

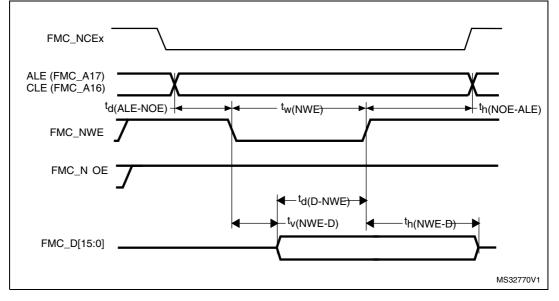

Figure 61. NAND controller waveforms for common memory write access

Table 98. Switching characteristics for NAND Flash read cycles<sup>(1)</sup>

| Symbol                  | Parameter                                  | Min                      | Max                      | Unit |

|-------------------------|--------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(N0E)</sub>     | FMC_NOE low width                          | 4T <sub>HCLK</sub> – 0.5 | 4T <sub>HCLK</sub> + 0.5 |      |

| t <sub>su(D-NOE)</sub>  | FMC_D[15-0] valid data before FMC_NOE high | 9                        | -                        |      |

| t <sub>h(NOE-D)</sub>   | FMC_D[15-0] valid data after FMC_NOE high  | 2.5                      | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> | FMC_ALE valid before FMC_NOE low           | -                        | 3T <sub>HCLK</sub> - 0.5 |      |

| t <sub>h(NOE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid            | 3T <sub>HCLK</sub> – 2   | -                        |      |

1. C<sub>L</sub> = 30 pF.

| Symbol                                         | Parameter                             | Conditions | Min | Тур  | Мах  | Unit       |  |

|------------------------------------------------|---------------------------------------|------------|-----|------|------|------------|--|

| f <sub>PP</sub>                                | Clock frequency in data transfer mode | -          | 0   | -    | 50   | MHz        |  |

| -                                              | SDIO_CK/fPCLK2 frequency ratio        | -          | -   | -    | 8/3  | -          |  |

| t <sub>W(CKL)</sub>                            | Clock low time                        | fpp =50MHz | 9.5 | 10.5 | -    | 20         |  |

| t <sub>W(CKH)</sub>                            | Clock high time                       | fpp =50MHz | 8.5 | 9.5  | -    | ns         |  |

| CMD, D inputs (referenced to CK) in eMMC mode  |                                       |            |     |      |      |            |  |

| t <sub>ISU</sub>                               | Input setup time HS                   | fpp =50MHz | 0.5 | -    | -    |            |  |

| t <sub>IH</sub>                                | Input hold time HS                    | fpp =50MHz | 7.5 | -    | -    | ns         |  |

| CMD, D outputs (referenced to CK) in eMMC mode |                                       |            |     |      |      |            |  |

| t <sub>OV</sub>                                | Output valid time HS                  | fpp =50MHz | -   | 13.5 | 14.5 | <b>D</b> C |  |

| t <sub>OH</sub>                                | Output hold time HS                   | fpp =50MHz | 12  | -    | -    | ns         |  |

## Table 106. Dynamic characteristics: eMMC characteristics $V_{DD}$ = 1.7 V to 1.9 V<sup>(1)(2)</sup>

1. Guaranteed based on test during characterization.

2.  $V_{DD}$  = 2.7 to 3.6 V.

## 6.3.29 RTC characteristics

#### Table 107. RTC characteristics

| Symbol | Parameter                                  | Conditions                                          | Min | Max |

|--------|--------------------------------------------|-----------------------------------------------------|-----|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4   | -   |

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|--|

|        | Min         | Тур    | Max    | Min                   | Тур    | Мах    |  |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |  |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |  |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |  |  |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |  |  |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |  |

# Table 109. LQPF100, 14 x 14 mm 100-pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

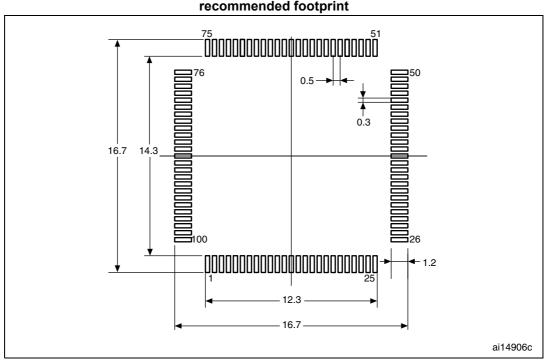

Figure 71. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

# 8 Part numbering

| Table 118. Ordering informa                      | ation sch | eme |       |   |   |   |     |

|--------------------------------------------------|-----------|-----|-------|---|---|---|-----|

| Example:                                         | STM32     | F   | 446 V | С | т | 6 | ххх |

|                                                  |           |     |       |   |   |   |     |

| Device family                                    |           |     |       |   |   |   |     |

| STM32 = ARM-based 32-bit microcontroller         |           |     |       |   |   |   |     |

|                                                  |           |     |       |   |   |   |     |

| Product type                                     |           |     |       |   |   |   |     |

| F = general-purpose                              |           |     |       |   |   |   |     |

|                                                  |           |     |       |   |   |   |     |

| Device subfamily                                 |           |     |       |   |   |   |     |

| 446= STM32F446xC/E,                              |           |     |       |   |   |   |     |

|                                                  |           |     |       |   |   |   |     |

| Pin count                                        |           |     |       |   |   |   |     |

| M = 81 pins                                      |           |     |       |   |   |   |     |

| R = 64 pins                                      |           |     |       |   |   |   |     |

| V = 100 pins                                     |           |     |       |   |   |   |     |

| Z = 144 pins                                     |           |     |       |   |   |   |     |

| Flash memory size                                |           |     |       |   |   |   |     |

| C=256 Kbytes of Flash memory                     |           |     |       |   |   |   |     |

| E=512 Kbytes of Flash memory                     |           |     |       |   |   |   |     |

| Package                                          |           |     |       |   |   |   |     |

| H = UFBGA (7 x 7 mm)                             |           |     |       |   |   |   |     |

| J = UFBGA (10 x 10 mm)                           |           |     |       |   |   |   |     |

| T = LQFP                                         |           |     |       |   |   |   |     |

| Y = WLCSP                                        |           |     |       |   |   |   |     |

| Temperature range                                |           |     |       |   |   |   |     |

| 6 = Industrial temperature range, -40 to 85 °C.  |           |     |       |   |   |   |     |

| 7 = Industrial temperature range, -40 to 105 °C. |           |     |       |   |   |   |     |

|                                                  |           |     |       |   |   |   |     |

| Options                                          |           |     |       |   |   |   |     |

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

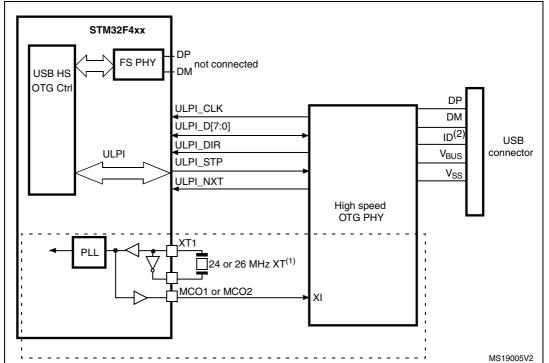

## A.2 USB OTG high speed (HS) interface solutions

Figure 88. USB controller configured as peripheral, host, or dual-mode and used in high speed mode

It is possible to use MCO1 or MCO2 to save a crystal. It is however not mandatory to clock the STM32F446xx with a 24 or 26 MHz crystal when using USB HS. The above figure only shows an example of a possible connection.

2. The ID pin is required in dual role only.