Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 53                                                                      |

| Program Memory Size        | 64KB (32K x 16)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 64-QFN (9x9)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega64l-8mu |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Features

- High-performance, Low-power Atmel AVR® 8-bit Microcontroller

- Advanced RISC Architecture

- 130 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers + Peripheral Control Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory segments

- 64 Kbytes of In-System Reprogrammable Flash program memory

- 2 Kbytes EEPROM

- 4 Kbytes Internal SRAM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C<sup>(1)</sup>

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program True Read-While-Write Operation

- Up to 64 Kbytes Optional External Memory Space

- Programming Lock for Software Security

- SPI Interface for In-System Programming

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

- Two Expanded 16-bit Timer/Counters with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Two 8-bit PWM Channels

- 6 PWM Channels with Programmable Resolution from 1 to 16 Bits

- 8-channel, 10-bit ADC

- 8 Single-ended Channels

- 7 Differential Channels

- 2 Differential Channels with Programmable Gain (1x, 10x, 200x)

- Byte-oriented Two-wire Serial Interface

- Dual Programmable Serial USARTs

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

Atmel

- Software Selectable Clock Frequency

- ATmega103 Compatibility Mode Selected by a Fuse

- Global Pull-up Disable

- I/O and Packages

- 53 Programmable I/O Lines

- 64-lead TQFP and 64-pad QFN/MLF

- Operating Voltages

- 2.7V 5.5V for Atmel ATmega64L

- 4.5V 5.5V for Atmel ATmega64

- Speed Grades

- 0 8 MHz for ATmega64L

- 0 16 MHz for ATmega64

# Atmel

8-bit Atmel Microcontroller with 64K Bytes In-System Programmable Flash

# ATmega64 ATmega64L

2490R-AVR-02/2013

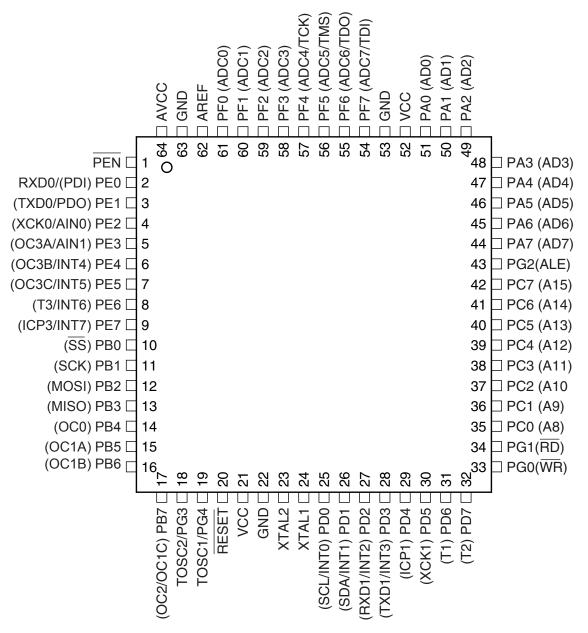

## Pin Configuration

Figure 1. Pinout ATmega64

TQFP/MLF

Note: The bottom pad under the QFN/MLF package should be soldered to ground.

**Disclaimer** Typical values contained in this data sheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

## **Overview**

The ATmega64 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega64 achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed.

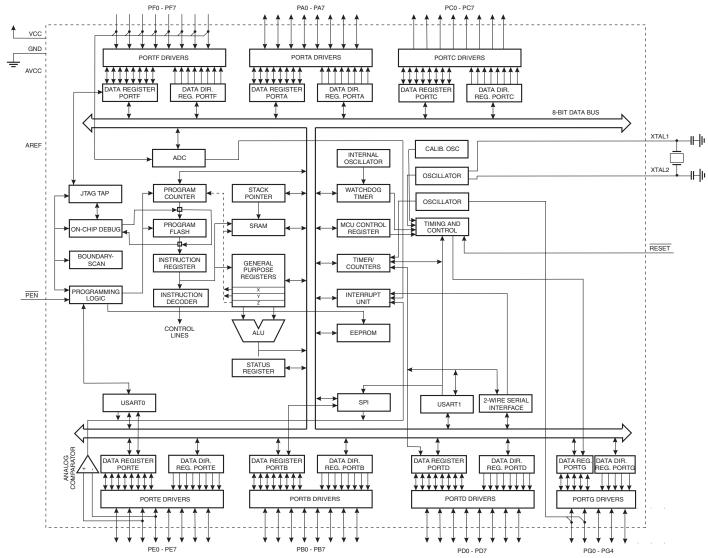

## **Block Diagram**

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega64 provides the following features: 64 Kbytes of In-System Programmable Flash with Read-While-Write capabilities, 2 Kbytes EEPROM, 4 Kbytes SRAM, 53 general purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), four flexible Timer/Counters with compare modes and PWM, two USARTs, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with internal Oscillator, an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption. In Extended Standby mode, both the main Oscillator and the asynchronous timer continue to run.

The device is manufactured using Atmel's high-density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip Boot program running on the AVR core. The Boot Program can use any interface to download the Application Program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega64 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega64 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

## ATmega103 and ATmega64 Compatibility

The ATmega64 is a highly complex microcontroller where the number of I/O locations supersedes the 64 I/O location reserved in the AVR instruction set. To ensure backward compatibility with the ATmega103, all I/O locations present in ATmega103 have the same location in ATmega64. Most additional I/O locations are added in an Extended I/O space starting from 0x60 to 0xFF (that is, in the ATmega103 internal RAM space). These location can be reached by using LD/LDS/LDD and ST/STS/STD instructions only, not by using IN and OUT instructions. The relocation of the internal RAM space may still be a problem for ATmega103 users. Also, the increased number of Interrupt Vectors might be a problem if the code uses absolute addresses. To solve these problems, an ATmega103 compatibility mode can be selected by programming the fuse M103C. In this mode, none of the functions in the Extended I/O space are in use, so the internal RAM is located as in ATmega103. Also, the extended Interrupt Vectors are removed.

The ATmega64 is 100% pin compatible with ATmega103, and can replace the ATmega103 on current printed circuit boards. The application notes "Replacing ATmega103 by ATmega128" and "Migration between ATmega64 and ATmega128" describes what the user should be aware of replacing the ATmega103 by an ATmega128 or ATmega64.

Atmel

#### ATmega103 Compatibility Mode

By programming the M103C Fuse, the ATmega64 will be compatible with the ATmega103 regards to RAM, I/O pins and Interrupt Vectors as described above. However, some new features in ATmega64 are not available in this compatibility mode, these features are listed below:

- One USART instead of two, asynchronous mode only. Only the eight least significant bits of the Baud Rate Register is available.

- One 16 bits Timer/Counter with two compare registers instead of two 16 bits Timer/Counters with three compare registers.

- Two-wire serial interface is not supported.

- Port G serves alternate functions only (not a general I/O port).

- Port F serves as digital input only in addition to analog input to the ADC.

- Boot Loader capabilities is not supported.

- It is not possible to adjust the frequency of the internal calibrated RC Oscillator.

- The External Memory Interface can not release any Address pins for general I/O, neither configure different wait states to different External Memory Address sections.

- Only EXTRF and PORF exist in the MCUCSR Register.

- No timed sequence is required for Watchdog Timeout change.

- Only low-level external interrupts can be used on four of the eight External Interrupt sources.

- Port C is output only.

- USART has no FIFO buffer, so Data OverRun comes earlier.

- The user must have set unused I/O bits to 0 in ATmega103 programs.

## **Pin Descriptions**

| VCC | Digital supply voltage. |

|-----|-------------------------|

|     |                         |

GND Ground.

**Port A (PA7..PA0)** Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the ATmega64 as listed on page 73.

**Port B (PB7..PB0)** Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega64 as listed on page 74.

| Port C (PC7PC0) | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                           |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Port C also serves the functions of special features of the ATmega64 as listed on page 77. In ATmega103 compatibility mode, Port C is output only, and the port C pins are <b>not</b> tri-stated when a reset condition becomes active.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Port D (PD7PD0) | Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                           |

|                 | Port D also serves the functions of various special features of the ATmega64 as listed on page 78.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port E (PE7PE0) | Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                           |

|                 | Port E also serves the functions of various special features of the ATmega64 as listed on page 81.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port F (PF7PF0) | Port F serves as the analog inputs to the A/D Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 | Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS) and PF4(TCK) will be activated even if a reset occurs. |

|                 | The TDO pin is tri-stated unless TAP states that shift out data are entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | Port F also serves the functions of the JTAG interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | In ATmega103 compatibility mode, Port F is an input port only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Port G (PG4PG0) | Port G is a 5-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                            |

|                 | Port G also serves the functions of various special features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | In ATmega103 compatibility mode, these pins only serves as strobes signals to the external memory as well as input to the 32 kHz Oscillator, and the pins are initialized to $PG0 = 1$ , $PG1 = 1$ , and $PG2 = 0$ asynchronously when a reset condition becomes active, even if the clock is not running. PG3 and PG4 are Oscillator pins.                                                                                                                                                                                                                                                                                                         |

**Atmel**

| RESET | Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 19 on page 52. Shorter pulses are not guaranteed to generate a reset. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1 | Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                          |

| XTAL2 | Output from the inverting Oscillator amplifier.                                                                                                                                                                                                         |

| AVCC  | AVCC is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to $V_{CC}$ through a low-pass filter.                         |

| AREF  | AREF is the analog reference pin for the A/D Converter.                                                                                                                                                                                                 |

| PEN   | This is a programming enable pin for the SPI Serial Programming mode. By holding this pin low                                                                                                                                                           |

**PEN** This is a programming enable pin for the SPI Serial Programming mode. By holding this pin low during a Power-on Reset, the device will enter the SPI Serial Programming mode. PEN is internally pulled high. The pullup is shown in Figure 22 on page 52 and its value is given in Section "DC Characteristics" on page 325. PEN has no function during normal operation.

**Resources** A comprehensive set of development tools, application notes and datasheetsare available for download on http://www.atmel.com/avr.

**Data Retention** Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

## About Code Examples

This datasheet contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

## **Ordering Information**

| Speed (MHz) | Power Supply (V) | Ordering Code <sup>(2)</sup>                                                                     | Package <sup>(1)</sup>     | Operation Range                               |

|-------------|------------------|--------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------|

| 8           | 2.7 - 5.5        | ATmega64L-8AU<br>ATmega64L-8AUR <sup>(3)</sup><br>ATmega64L-8MU<br>ATmega64L-8MUR <sup>(3)</sup> | 64A<br>64A<br>64M1<br>64M1 | Industrial<br>(-40°C to 85°C)                 |

| 16          | 4.5 - 5.5        | ATmega64-16AU<br>ATmega64-16AUR <sup>(3)</sup><br>ATmega64-16MU<br>ATmega64-16MUR <sup>(3)</sup> | 64A<br>64A<br>64M1<br>64M1 |                                               |

| 8           | 2.7 - 5.5        | ATmega64L-8AN<br>ATmega64L-8ANR <sup>(3)</sup><br>ATmega64L-8MN<br>ATmega64L-8MNR <sup>(3)</sup> | 64A<br>64A<br>64M1<br>64M1 | Industrial<br>(-40°C to 105°C) <sup>(4)</sup> |

| 16          | 4.5 - 5.5        | ATmega64-16AN<br>ATmega64-16ANR <sup>(3)</sup><br>ATmega64-16MN<br>ATmega64-16MNR <sup>(3)</sup> | 64A<br>64A<br>64M1<br>64M1 |                                               |

Note: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

2. Pb-free packaging complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. Tape & Reel.

4. See characterization specification at  $105^{\circ}C$

| Package Type |                                                                                                                   |

|--------------|-------------------------------------------------------------------------------------------------------------------|

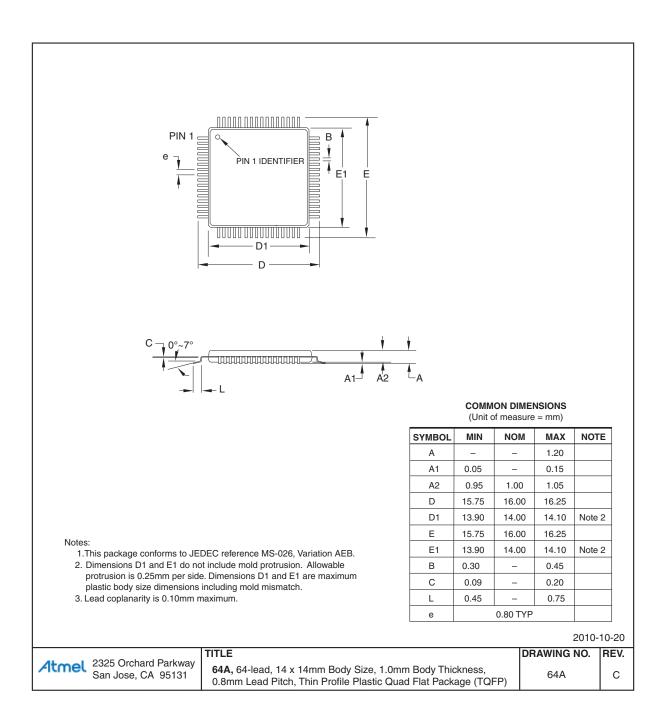

| 64A          | 64-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP)                                                 |

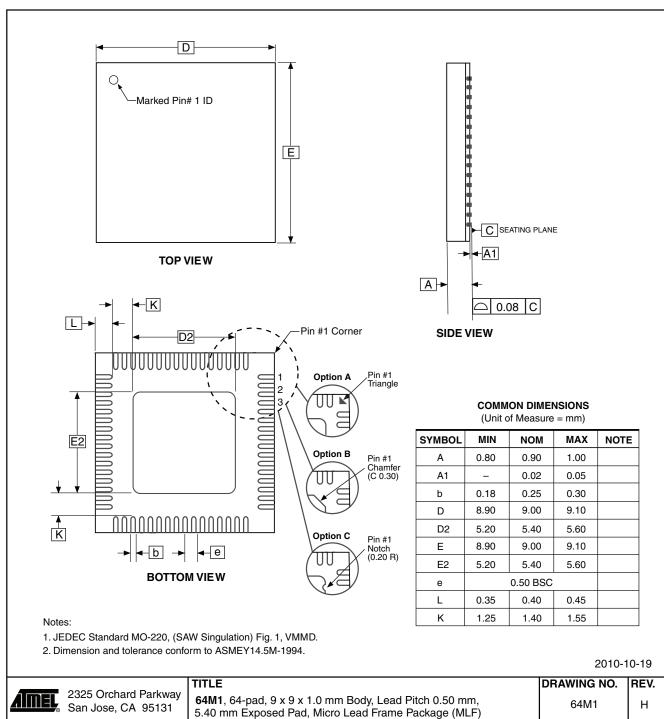

| 64M1         | 64-pad, $9 \times 9 \times 1.0$ mm body, lead pitch 0.50 mm, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF) |

## **Packaging Information**

64A

**Atmel**

## Errata

The revision letter in this section refers to the revision of the ATmega64 device.

# ATmega64, rev. A to C, E

- First Analog Comparator conversion may be delayed

- Interrupts may be lost when writing the timer registers in the asynchronous timer

- Stabilizing time needed when changing XDIV Register

- Stabilizing time needed when changing OSCCAL Register

- IDCODE masks data from TDI input

- Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request

## 1. First Analog Comparator conversion may be delayed

If the device is powered by a slow rising  $V_{CC}$ , the first Analog Comparator conversion will take longer than expected on some devices.

## **Problem Fix/Workaround**

When the device has been powered or reset, disable then enable theAnalog Comparator before the first conversion.

2. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

## **Problem Fix/Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

## 3. Stabilizing time needed when changing XDIV Register

After increasing the source clock frequency more than 2% with settings in the XDIV register, the device may execute some of the subsequent instructions incorrectly.

## Problem Fix / Workaround

The NOP instruction will always be executed correctly also right after a frequency change. Thus, the next 8 instructions after the change should be NOP instructions. To ensure this, follow this procedure:

1.Clear the I bit in the SREG Register.

2.Set the new pre-scaling factor in XDIV register.

3.Execute 8 NOP instructions

4.Set the I bit in SREG

This will ensure that all subsequent instructions will execute correctly.

Assembly Code Example:

| CLI            | ; clear global interrupt enable |

|----------------|---------------------------------|

| OUT XDIV, temp | ; set new prescale value        |

| NOP            | ; no operation                  |

| SEI            | ; clear global interrupt enable |

|                |                                 |

Atmel

#### 4. Stabilizing time needed when changing OSCCAL Register

After increasing the source clock frequency more than 2% with settings in the OSCCAL register, the device may execute some of the subsequent instructions incorrectly.

#### Problem Fix / Workaround

The behavior follows errata number 3., and the same Fix / Workaround is applicable on this errata.

#### 5. IDCODE masks data from TDI input

The JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.

#### Problem Fix / Workaround

- If ATmega64 is the only device in the scan chain, the problem is not visible.

- Select the Device ID Register of the ATmega64 by issuing the IDCODE instruction or by entering the Test-Logic-Reset state of the TAP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYPASS instruction to the ATmega64 while reading the Device ID Registers of preceding devices of the boundary scan chain.

- If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the ATmega64 must be the first device in the chain.

# 6. Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request.

Reading EEPROM by using the ST or STS command to set the EERE bit in the EECR register triggers an unexpected EEPROM interrupt request.

#### Problem Fix / Workaround

Always use OUT or SBI to set EERE in EECR.

Atmel

# Atmel Enabling Unlimited Possibilities®

Atmel Corporation 1600 Technology Drive San Jose, CA 95110 USA Tel: (+1) (408) 441-0311 Fax: (+1) (408) 487-2600 www.atmel.com Atmel Asia Limited Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Roa Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621 Atmel Japan G.K. 16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku Tokyo 141-0032 JAPAN Tel: (+81) (3) 6417-0300 Fax: (+81) (3) 6417-0370

© 2013 Atmel Corporation. All rights reserved. / Rev.: 2490R–AVR–02/2013

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.