Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 56480                                                      |

| Number of Logic Elements/Cells | 149500                                                     |

| Total RAM Bits                 | 7880704                                                    |

| Number of I/O                  | 336                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 672-BGA                                                    |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5cgxbc7d6f27c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| Cyclone | V Device Overview                                      | . 3 |

|---------|--------------------------------------------------------|-----|

| Ke      | ey Advantages of Cyclone V Devices                     | . 3 |

| Su      | ummary of Cyclone V Features                           | .4  |

|         | vclone V Device Variants and Packages                  |     |

| •       | Cyclone V E                                            |     |

|         | Cyclone V GX                                           | . 7 |

|         | Cyclone V GT                                           |     |

|         | Cyclone V SE                                           |     |

|         | Cyclone V SX                                           |     |

|         | Cyclone V ST                                           |     |

| I/0     | O Vertical Migration for Cyclone V Devices             |     |

| -       | daptive Logic Module                                   |     |

|         | riable-Precision DSP Block                             |     |

| En      | nbedded Memory Blocks                                  | 21  |

|         | Types of Embedded Memory                               |     |

|         | Embedded Memory Capacity in Cyclone V Devices          |     |

|         | Embedded Memory Configurations                         | 22  |

| Cle     | ock Networks and PLL Clock Sources                     | 22  |

| FP      | PGA General Purpose I/O                                | 23  |

| PC      | CIe Gen1 and Gen2 Hard IP                              | 24  |

| Ex      | ternal Memory Interface                                | 24  |

|         | Hard and Soft Memory Controllers                       |     |

|         | External Memory Performance                            |     |

|         | HPS External Memory Performance                        |     |

| Lo      | w-Power Serial Transceivers                            |     |

|         | Transceiver Channels                                   |     |

|         | PMA Features                                           |     |

|         | PCS Features                                           |     |

| Sc      | oC with HPS                                            |     |

|         | HPS Features                                           |     |

|         | FPGA Configuration and Processor Booting               |     |

|         | Hardware and Software Development                      |     |

| Dy      | namic and Partial Reconfiguration                      |     |

|         | Dynamic Reconfiguration                                |     |

|         | Partial Reconfiguration                                |     |

|         | hanced Configuration and Configuration via Protocol    |     |

|         | wer Management                                         |     |

| Do      | ocument Revision History for Cyclone V Device Overview | 33  |

## **Cyclone V Device Overview**

The Cyclone® V devices are designed to simultaneously accommodate the shrinking power consumption, cost, and time-to-market requirements; and the increasing bandwidth requirements for high-volume and cost-sensitive applications.

Enhanced with integrated transceivers and hard memory controllers, the Cyclone V devices are suitable for applications in the industrial, wireless and wireline, military, and automotive markets.

#### **Related Information**

Cyclone V Device Handbook: Known Issues

Lists the planned updates to the Cyclone V Device Handbook chapters.

### **Key Advantages of Cyclone V Devices**

Table 1. Key Advantages of the Cyclone V Device Family

| Advantage                                                                           | Supporting Feature                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lower power consumption                                                             | Built on TSMC's 28 nm low-power (28LP) process technology and includes an abundance of hard intellectual property (IP) blocks     Up to 40% lower power consumption than the previous generation device                                                                        |

| Improved logic integration and differentiation capabilities                         | 8-input adaptive logic module (ALM)     Up to 13.59 megabits (Mb) of embedded memory     Variable-precision digital signal processing (DSP) blocks                                                                                                                             |

| Increased bandwidth capacity                                                        | 3.125 gigabits per second (Gbps) and 6.144 Gbps transceivers     Hard memory controllers                                                                                                                                                                                       |

| Hard processor system (HPS)<br>with integrated Arm* Cortex*-A9<br>MPCore* processor | <ul> <li>Tight integration of a dual-core Arm Cortex-A9 MPCore processor, hard IP, and an FPGA in a single Cyclone V system-on-a-chip (SoC)</li> <li>Supports over 128 Gbps peak bandwidth with integrated data coherency between the processor and the FPGA fabric</li> </ul> |

| Lowest system cost                                                                  | Requires only two core voltages to operate  Available in low-cost wirebond packaging  Includes innovative features such as Configuration via Protocol (CvP) and partial reconfiguration                                                                                        |

# **Summary of Cyclone V Features**

**Summary of Features for Cyclone V Devices** Table 2.

| Feature                                           |                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Technology                                        | TSMC's 28-nm low-p 1.1 V core voltage                                                                                                   | ower (28LP) process technology                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Packaging                                         | Multiple device densi<br>different device densi                                                                                         | Multiple device densities with compatible package footprints for seamless migration between different device densities                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| High-performance<br>FPGA fabric                   | Enhanced 8-input ALM v                                                                                                                  | vith four registers                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Internal memory<br>blocks                         | •                                                                                                                                       | (b) memory blocks with soft error correction code (ECC) block (MLAB)—640-bit distributed LUTRAM where you can use up to 25% memory                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Embedded Hard IP<br>blocks                        | Variable-precision DSP                                                                                                                  | <ul> <li>Native support for up to three signal processing precision levels (three 9 x 9, two 18 x 18, or one 27 x 27 multiplier) in the same variable-precision DSP block</li> <li>64-bit accumulator and cascade</li> <li>Embedded internal coefficient memory</li> <li>Preadder/subtractor for improved efficiency</li> </ul>                                                                     |  |  |  |  |  |

|                                                   | Memory controller                                                                                                                       | DDR3, DDR2, and LPDDR2 with 16 and 32 bit ECC support                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                                                   | Embedded transceiver I/O PCI Express* (PCIe*) Gen2 and Gen1 (x1, x2, or x4) hard IP with multifunction support, endpoint, and root port |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Clock networks                                    |                                                                                                                                         | ol clock network<br>d peripheral clock networks<br>are not used can be powered down to reduce dynamic power                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Phase-locked loops<br>(PLLs)                      | Precision clock synth     Integer mode and from                                                                                         | esis, clock delay compensation, and zero delay buffering (ZDB) actional mode                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| FPGA General-purpose<br>I/Os (GPIOs)              | 400 MHz/800 Mbps 6     On-chip termination                                                                                              | cond (Mbps) LVDS receiver and 840 Mbps LVDS transmitter<br>external memory interface<br>(OCT)<br>p to 16 mA drive strength                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Low-power high-speed serial interface             | Transmit pre-emphase                                                                                                                    | Sbps integrated transceiver speed sis and receiver equalization infiguration of individual channels                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| HPS<br>(Cyclone V SE, SX,<br>and ST devices only) | support for symmetr  Interface peripherals On-The-GO (OTG) co flash controller, Secunetwork (CAN), seria interfaces                     | Arm Cortex-A9 MPCore processor-up to 925 MHz maximum frequency with ic and asymmetric multiprocessing s—10/100/1000 Ethernet media access control (EMAC), USB 2.0 ontroller, quad serial peripheral interface (QSPI) flash controller, NAND are Digital/MultiMediaCard (SD/MMC) controller, UART, controller area all peripheral interface (SPI), I <sup>2</sup> C interface, and up to 85 HPS GPIO |  |  |  |  |  |

|                                                   |                                                                                                                                         | -general-purpose timers, watchdog timers, direct memory access (DMA)<br>iguration manager, and clock and reset managers<br>ot ROM                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                                   | ·                                                                                                                                       | continued                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

<sup>(1)</sup> Contact Intel for availability.

### **Available Options**

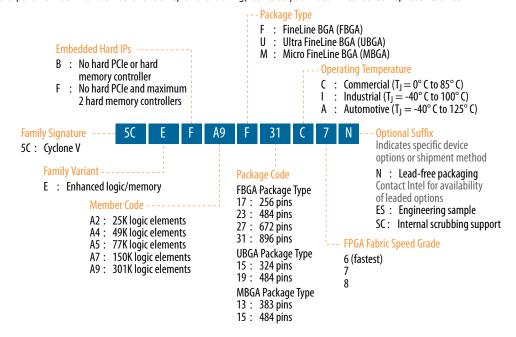

#### Figure 1. Sample Ordering Code and Available Options for Cyclone V E Devices

The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

### **Maximum Resources**

**Table 4.** Maximum Resource Counts for Cyclone V E Devices

| Resource               |              |        | Member Code |         |         |         |  |  |  |

|------------------------|--------------|--------|-------------|---------|---------|---------|--|--|--|

|                        |              | A2     | A4          | A5      | A7      | А9      |  |  |  |

| Logic Elements         | (LE) (K)     | 25     | 49          | 77      | 150     | 301     |  |  |  |

| ALM                    |              | 9,430  | 18,480      | 29,080  | 56,480  | 113,560 |  |  |  |

| Register               |              | 37,736 | 73,920      | 116,320 | 225,920 | 454,240 |  |  |  |

| Memory (Kb)            | M10K         | 1,760  | 3,080       | 4,460   | 6,860   | 12,200  |  |  |  |

|                        | MLAB         | 196    | 303         | 424     | 836     | 1,717   |  |  |  |

| Variable-precision     | on DSP Block | 25     | 66          | 150     | 156     | 342     |  |  |  |

| 18 x 18 Multipli       | er           | 50     | 132         | 300     | 312     | 684     |  |  |  |

| PLL                    |              | 4      | 4           | 6       | 7       | 8       |  |  |  |

| GPIO                   |              | 224    | 224         | 240     | 480     | 480     |  |  |  |

| LVDS                   | Transmitter  | 56     | 56          | 60      | 120     | 120     |  |  |  |

|                        | Receiver     | 56     | 56          | 60      | 120     | 120     |  |  |  |

| Hard Memory Controller |              | 1      | 1           | 2       | 2       | 2       |  |  |  |

### **Available Options**

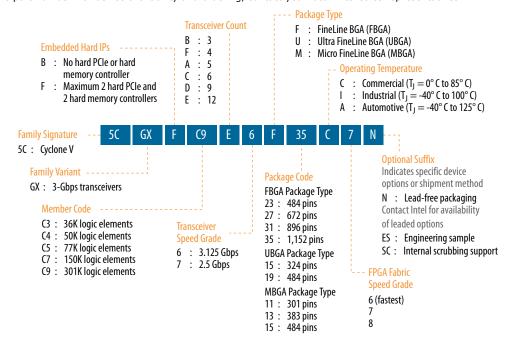

#### Figure 2. Sample Ordering Code and Available Options for Cyclone V GX Devices

The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

### **Maximum Resources**

**Table 6.** Maximum Resource Counts for Cyclone V GX Devices

| Resource            |             |        | Member Code |           |           |           |  |  |  |

|---------------------|-------------|--------|-------------|-----------|-----------|-----------|--|--|--|

|                     |             | С3     | C4          | <b>C5</b> | <b>C7</b> | С9        |  |  |  |

| Logic Elements (    | (LE) (K)    | 36     | 50          | 77        | 150       | 301       |  |  |  |

| ALM                 |             | 13,460 | 18,860      | 29,080    | 56,480    | 113,560   |  |  |  |

| Register            |             | 53,840 | 75,440      | 116,320   | 225,920   | 454,240   |  |  |  |

| Memory (Kb)         | M10K        | 1,350  | 2,500       | 4,460     | 6,860     | 12,200    |  |  |  |

|                     | MLAB        | 182    | 424         | 424       | 836       | 1,717     |  |  |  |

| Variable-precision  | n DSP Block | 57     | 70          | 150       | 156       | 342       |  |  |  |

| 18 x 18 Multiplie   | er          | 114    | 140         | 300       | 312       | 684       |  |  |  |

| PLL                 |             | 4      | 6           | 6         | 7         | 8         |  |  |  |

| 3 Gbps Transceiver  |             | 3      | 6           | 6         | 9         | 12        |  |  |  |

| GPIO <sup>(4)</sup> |             | 208    | 336         | 336       | 480       | 560       |  |  |  |

|                     |             |        |             |           |           | continued |  |  |  |

<sup>(4)</sup> The number of GPIOs does not include transceiver I/Os. In the Intel Quartus® Prime software, the number of user I/Os includes transceiver I/Os.

| Resource               |             | Member Code |    |           |     |           |  |  |

|------------------------|-------------|-------------|----|-----------|-----|-----------|--|--|

|                        |             | С3          | C4 | <b>C5</b> | С7  | <b>C9</b> |  |  |

| LVDS                   | Transmitter | 52          | 84 | 84        | 120 | 140       |  |  |

|                        | Receiver    | 52          | 84 | 84        | 120 | 140       |  |  |

| PCIe Hard IP Block     |             | 1           | 2  | 2         | 2   | 2         |  |  |

| Hard Memory Controller |             | 1           | 2  | 2         | 2   | 2         |  |  |

#### **Related Information**

True LVDS Buffers in Devices, I/O Features in Cyclone V Devices

Provides the number of LVDS channels in each device package.

### **Package Plan**

**Table 7.** Package Plan for Cyclone V GX Devices

| Member<br>Code |      |      | M383<br>(13 mm) |      | M484<br>(15 mm) |      | U324<br>(15 mm) |      | U484<br>(19 mm) |      |

|----------------|------|------|-----------------|------|-----------------|------|-----------------|------|-----------------|------|

|                | GPIO | XCVR | GPIO            | XCVR | GPIO            | XCVR | GPIO            | XCVR | GPIO            | XCVR |

| C3             | _    | _    | _               | _    | _               | _    | 144             | 3    | 208             | 3    |

| C4             | 129  | 4    | 175             | 6    | _               | _    | _               | _    | 224             | 6    |

| C5             | 129  | 4    | 175             | 6    | _               | _    | _               | _    | 224             | 6    |

| C7             | _    | _    | _               | _    | 240             | 3    | _               | _    | 240             | 6    |

| C9             | _    | _    | _               | _    | _               | _    | _               | _    | 240             | 5    |

| Member<br>Code | F4<br>(23 i |      | F672<br>(27 mm) |      | F896<br>(31 mm) |      | F1152<br>(35 mm) |      |

|----------------|-------------|------|-----------------|------|-----------------|------|------------------|------|

|                | GPIO        | XCVR | GPIO            | XCVR | GPIO            | XCVR | GPIO             | XCVR |

| C3             | 208         | 3    | _               | _    | _               | _    | _                | _    |

| C4             | 240         | 6    | 336             | 6    | _               | _    | _                | _    |

| C5             | 240         | 6    | 336             | 6    | _               | _    | _                | _    |

| C7             | 240         | 6    | 336             | 9    | 480             | 9    | _                | _    |

| С9             | 224         | 6    | 336             | 9    | 480             | 12   | 560              | 12   |

### **Cyclone V GT**

This section provides the available options, maximum resource counts, and package plan for the Cyclone V GT devices.

The information in this section is correct at the time of publication. For the latest information and to get more details, refer to the *Product Selector Guide*.

#### **Related Information**

Product Selector Guide

Provides the latest information about Intel products.

### **Available Options**

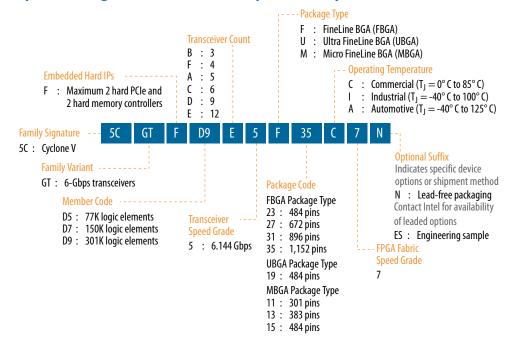

Figure 3. Sample Ordering Code and Available Options for Cyclone V GT Devices

#### **Maximum Resources**

**Table 8.** Maximum Resource Counts for Cyclone V GT Devices

| Resource              |             |         | Member Code |           |  |  |  |  |

|-----------------------|-------------|---------|-------------|-----------|--|--|--|--|

|                       |             | D5      | D7          | D9        |  |  |  |  |

| Logic Elements (LE) ( | K)          | 77      | 150         | 301       |  |  |  |  |

| ALM                   |             | 29,080  | 56,480      | 113,560   |  |  |  |  |

| Register              |             | 116,320 | 225,920     | 454,240   |  |  |  |  |

| Memory (Kb)           | M10K        | 4,460   | 6,860       | 12,200    |  |  |  |  |

|                       | MLAB        | 424     | 836         | 1,717     |  |  |  |  |

| Variable-precision DS | P Block     | 150     | 156         | 342       |  |  |  |  |

| 18 x 18 Multiplier    |             | 300     | 312         | 684       |  |  |  |  |

| PLL                   |             | 6       | 7           | 8         |  |  |  |  |

| 6 Gbps Transceiver    |             | 6       | 9           | 12        |  |  |  |  |

| GPIO <sup>(5)</sup>   |             | 336     | 480         | 560       |  |  |  |  |

| LVDS                  | Transmitter | 84      | 120         | 140       |  |  |  |  |

|                       | ,           | •       |             | continued |  |  |  |  |

<sup>(5)</sup> The number of GPIOs does not include transceiver I/Os. In the Intel Quartus Prime software, the number of user I/Os includes transceiver I/Os.

| Resource               |          | Member Code |     |     |  |  |  |

|------------------------|----------|-------------|-----|-----|--|--|--|

|                        |          | D5 D7       |     | D9  |  |  |  |

|                        | Receiver | 84          | 120 | 140 |  |  |  |

| PCIe Hard IP Block     |          | 2           | 2   | 2   |  |  |  |

| Hard Memory Controller |          | 2           | 2   | 2   |  |  |  |

#### **Related Information**

True LVDS Buffers in Devices, I/O Features in Cyclone V Devices

Provides the number of LVDS channels in each device package.

### **Package Plan**

#### **Table 9.** Package Plan for Cyclone V GT Devices

Transceiver counts shown are for transceiver  $\leq 5$  Gbps . 6 Gbps transceiver channel count support depends on the package and channel usage. For more information about the 6 Gbps transceiver channel count, refer to the Cyclone V Device Handbook Volume 2: Transceivers.

| Member<br>Code | M3<br>(11 i |      | M383<br>(13 mm) |      | M484<br>(15 mm) |      | U484<br>(19 mm) |      |

|----------------|-------------|------|-----------------|------|-----------------|------|-----------------|------|

|                | GPIO        | XCVR | GPIO            | XCVR | GPIO            | XCVR | GPIO            | XCVR |

| D5             | 129         | 4    | 175             | 6    | _               | _    | 224             | 6    |

| D7             | _           | _    | _               | _    | 240             | 3    | 240             | 6    |

| D9             | _           | _    | _               | _    | _               | _    | 240             | 5    |

| Member<br>Code | F48<br>(23 I |      | F672<br>(27 mm) |       | F896<br>(31 mm) |                   | F1152<br>(35 mm) |                   |

|----------------|--------------|------|-----------------|-------|-----------------|-------------------|------------------|-------------------|

|                | GPIO         | XCVR | GPIO            | XCVR  | GPIO            | XCVR              | GPIO             | XCVR              |

| D5             | 240          | 6    | 336             | 6     | _               | _                 | _                | _                 |

| D7             | 240          | 6    | 336             | 9 (6) | 480             | 9 (6)             | _                | _                 |

| D9             | 224          | 6    | 336             | 9 (6) | 480             | 12 <sup>(7)</sup> | 560              | 12 <sup>(7)</sup> |

#### **Related Information**

6.144-Gbps Support Capability in Cyclone V GT Devices, Cyclone V Device Handbook Volume 2: Transceivers

Provides more information about 6 Gbps transceiver channel count.

<sup>(6)</sup> If you require CPRI (at 6.144 Gbps) and PCIe Gen2 transmit jitter compliance, Intel recommends that you use only up to three full-duplex transceiver channels for CPRI, and up to six full-duplex channels for PCIe Gen2. The CMU channels are not considered full-duplex channels.

<sup>&</sup>lt;sup>(7)</sup> If you require CPRI (at 6.144 Gbps) and PCIe Gen2 transmit jitter compliance, Intel recommends that you use only up to three full-duplex transceiver channels for CPRI, and up to eight full-duplex channels for PCIe Gen2. The CMU channels are not considered full-duplex channels.

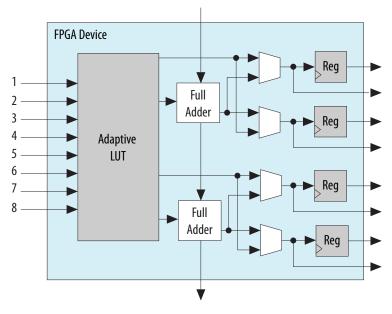

Figure 8. ALM for Cyclone V Devices

You can configure up to 25% of the ALMs in the Cyclone V devices as distributed memory using MLABs.

#### **Related Information**

Embedded Memory Capacity in Cyclone V Devices on page 21 Lists the embedded memory capacity for each device.

### **Variable-Precision DSP Block**

Cyclone V devices feature a variable-precision DSP block that supports these features:

- Configurable to support signal processing precisions ranging from 9 x 9, 18 x 18 and 27 x 27 bits natively

- A 64-bit accumulator

- A hard preadder that is available in both 18- and 27-bit modes

- Cascaded output adders for efficient systolic finite impulse response (FIR) filters

- Internal coefficient register banks, 8 deep, for each multiplier in 18- or 27-bit mode

- Fully independent multiplier operation

- A second accumulator feedback register to accommodate complex multiplyaccumulate functions

- Fully independent Efficient support for single-precision floating point arithmetic

- The inferability of all modes by the Intel Quartus Prime design software

Table 16. Variable-Precision DSP Block Configurations for Cyclone V Devices

| Usage Example                                           | Multiplier Size (Bit)       | DSP Block Resource |

|---------------------------------------------------------|-----------------------------|--------------------|

| Low precision fixed point for video applications        | Three 9 x 9                 | 1                  |

| Medium precision fixed point in FIR filters             | Two 18 x 18                 | 1                  |

| FIR filters and general DSP usage                       | Two 18 x 18 with accumulate | 1                  |

| High precision fixed- or floating-point implementations | One 27 x 27 with accumulate | 1                  |

You can configure each DSP block during compilation as independent three 9  $\times$  9, two 18  $\times$  18, or one 27  $\times$  27 multipliers. With a dedicated 64 bit cascade bus, you can cascade multiple variable-precision DSP blocks to implement even higher precision DSP functions efficiently.

**Table 17.** Number of Multipliers in Cyclone V Devices

The table lists the variable-precision DSP resources by bit precision for each Cyclone V device.

| Variant      | Member<br>Code | Variable-<br>precision<br>DSP Block |                     | Independent Input and Output<br>Multiplications Operator |                       |            | 18 x 18<br>Multiplier<br>Adder |

|--------------|----------------|-------------------------------------|---------------------|----------------------------------------------------------|-----------------------|------------|--------------------------------|

|              |                | DSP Block                           | 9 x 9<br>Multiplier | 18 x 18<br>Multiplier                                    | 27 x 27<br>Multiplier | Adder Mode | Summed<br>with 36 bit<br>Input |

| Cyclone V E  | A2             | 25                                  | 75                  | 50                                                       | 25                    | 25         | 25                             |

|              | A4             | 66                                  | 198                 | 132                                                      | 66                    | 66         | 66                             |

|              | A5             | 150                                 | 450                 | 300                                                      | 150                   | 150        | 150                            |

|              | A7             | 156                                 | 468                 | 312                                                      | 156                   | 156        | 156                            |

|              | A9             | 342                                 | 1,026               | 684                                                      | 342                   | 342        | 342                            |

| Cyclone V    | C3             | 57                                  | 171                 | 114                                                      | 57                    | 57         | 57                             |

| GX           | C4             | 70                                  | 210                 | 140                                                      | 70                    | 70         | 70                             |

|              | C5             | 150                                 | 450                 | 300                                                      | 150                   | 150        | 150                            |

|              | C7             | 156                                 | 468                 | 312                                                      | 156                   | 156        | 156                            |

|              | C9             | 342                                 | 1,026               | 684                                                      | 342                   | 342        | 342                            |

| Cyclone V GT | D5             | 150                                 | 450                 | 300                                                      | 150                   | 150        | 150                            |

|              | D7             | 156                                 | 468                 | 312                                                      | 156                   | 156        | 156                            |

|              | D9             | 342                                 | 1,026               | 684                                                      | 342                   | 342        | 342                            |

| Cyclone V SE | A2             | 36                                  | 108                 | 72                                                       | 36                    | 36         | 36                             |

|              | A4             | 84                                  | 252                 | 168                                                      | 84                    | 84         | 84                             |

|              | A5             | 87                                  | 261                 | 174                                                      | 87                    | 87         | 87                             |

|              | A6             | 112                                 | 336                 | 224                                                      | 112                   | 112        | 112                            |

| Cyclone V SX | C2             | 36                                  | 108                 | 72                                                       | 36                    | 36         | 36                             |

|              | C4             | 84                                  | 252                 | 168                                                      | 84                    | 84         | 84                             |

|              | C5             | 87                                  | 261                 | 174                                                      | 87                    | 87         | 87                             |

|              |                |                                     |                     |                                                          |                       |            | continued                      |

| Variant      | Member | M10K  |              | ML    | Total RAM Bit |        |

|--------------|--------|-------|--------------|-------|---------------|--------|

|              | Code   | Block | RAM Bit (Kb) | Block | RAM Bit (Kb)  | (Kb)   |

| Cyclone V GT | D5     | 446   | 4,460        | 679   | 424           | 4,884  |

|              | D7     | 686   | 6,860        | 1338  | 836           | 7,696  |

|              | D9     | 1,220 | 12,200       | 2748  | 1,717         | 13,917 |

| Cyclone V SE | A2     | 140   | 1,400        | 221   | 138           | 1,538  |

|              | A4     | 270   | 2,700        | 370   | 231           | 2,460  |

|              | A5     | 397   | 3,970        | 768   | 480           | 4,450  |

|              | A6     | 553   | 5,530        | 994   | 621           | 6,151  |

| Cyclone V SX | C2     | 140   | 1,400        | 221   | 138           | 1,538  |

|              | C4     | 270   | 2,700        | 370   | 231           | 2,460  |

|              | C5     | 397   | 3,970        | 768   | 480           | 4,450  |

|              | C6     | 553   | 5,530        | 994   | 621           | 6,151  |

| Cyclone V ST | D5     | 397   | 3,970        | 768   | 480           | 4,450  |

|              | D6     | 553   | 5,530        | 994   | 621           | 6,151  |

### **Embedded Memory Configurations**

#### Table 19. Supported Embedded Memory Block Configurations for Cyclone V Devices

This table lists the maximum configurations supported for the embedded memory blocks. The information is applicable only to the single-port RAM and ROM modes.

| Memory Block | Depth (bits) | Programmable Width |

|--------------|--------------|--------------------|

| MLAB         | 32           | x16, x18, or x20   |

| M10K         | 256          | x40 or x32         |

|              | 512          | x20 or x16         |

|              | 1K           | x10 or x8          |

|              | 2K           | x5 or x4           |

|              | 4K           | x2                 |

|              | 8K           | ×1                 |

### **Clock Networks and PLL Clock Sources**

550 MHz Cyclone V devices have 16 global clock networks capable of up to operation. The clock network architecture is based on Intel's global, quadrant, and peripheral clock structure. This clock structure is supported by dedicated clock input pins and fractional PLLs.

Note:

To reduce power consumption, the Intel Quartus Prime software identifies all unused sections of the clock network and powers them down.

#### **PLL Features**

The PLLs in the Cyclone V devices support the following features:

- Frequency synthesis

- On-chip clock deskew

- Jitter attenuation

- Programmable output clock duty cycles

- PLL cascading

- Reference clock switchover

- Programmable bandwidth

- User-mode reconfiguration of PLLs

- Low power mode for each fractional PLL

- Dynamic phase shift

- Direct, source synchronous, zero delay buffer, external feedback, and LVDS compensation modes

#### **Fractional PLL**

In addition to integer PLLs, the Cyclone V devices use a fractional PLL architecture. The devices have up to eight PLLs, each with nine output counters. You can use the output counters to reduce PLL usage in two ways:

- Reduce the number of oscillators that are required on your board by using fractional PLLs

- Reduce the number of clock pins that are used in the device by synthesizing multiple clock frequencies from a single reference clock source

If you use the fractional PLL mode, you can use the PLLs for precision fractional-N frequency synthesis—removing the need for off-chip reference clock sources in your design.

The transceiver fractional PLLs that are not used by the transceiver I/Os can be used as general purpose fractional PLLs by the FPGA fabric.

### FPGA General Purpose I/O

Cyclone V devices offer highly configurable GPIOs. The following list describes the features of the GPIOs:

- Programmable bus hold and weak pull-up

- $\bullet$  LVDS output buffer with programmable differential output voltage (V $_{\text{OD}}$  ) and programmable pre-emphasis

- ullet On-chip parallel termination (R<sub>T</sub> OCT) for all I/O banks with OCT calibration to limit the termination impedance variation

- On-chip dynamic termination that has the ability to swap between series and parallel termination, depending on whether there is read or write on a common bus for signal integrity

- Easy timing closure support using the hard read FIFO in the input register path, and delay-locked loop (DLL) delay chain with fine and coarse architecture

#### **PCS Features**

The Cyclone V core logic connects to the PCS through an 8, 10, 16, 20, 32, or 40 bit interface, depending on the transceiver data rate and protocol. Cyclone V devices contain PCS hard IP to support PCIe Gen1 and Gen2, Gbps Ethernet (GbE), Serial RapidIO<sup>®</sup> (SRIO), and Common Public Radio Interface (CPRI).

Most of the standard and proprietary protocols from 614 Mbps to 6.144 Gbps are supported.

**Table 23.** Transceiver PCS Features for Cyclone V Devices

| PCS Support                                | Data Rates<br>(Gbps)                      | Transmitter Data Path Feature                                                                                              | Receiver Data Path Feature                                                                                                                                                                         |

|--------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-Gbps and 6-Gbps Basic                    | 0.614 to 6.144                            | <ul> <li>Phase compensation FIFO</li> <li>Byte serializer</li> <li>8B/10B encoder</li> <li>Transmitter bit-slip</li> </ul> | <ul> <li>Word aligner</li> <li>Deskew FIFO</li> <li>Rate-match FIFO</li> <li>8B/10B decoder</li> <li>Byte deserializer</li> <li>Byte ordering</li> <li>Receiver phase compensation FIFO</li> </ul> |

| PCIe Gen1<br>(x1, x2, x4)                  | 2.5 and 5.0                               | Dedicated PCIe PHY IP core     PIPE 2.0 interface to the core logic                                                        | Dedicated PCIe PHY IP core     PIPE 2.0 interface to the core logic                                                                                                                                |

| PCIe Gen2<br>( x1, x2, x4) <sup>(12)</sup> |                                           | logic                                                                                                                      | logic                                                                                                                                                                                              |

| GbE                                        | 1.25                                      | Custom PHY IP core with preset feature     GbE transmitter synchronization state machine                                   | Custom PHY IP core with preset feature     GbE receiver synchronization state machine                                                                                                              |

| XAUI (13)                                  | 3.125                                     | Dedicated XAUI PHY IP core                                                                                                 | Dedicated XAUI PHY IP core                                                                                                                                                                         |

| HiGig                                      | 3.75                                      | XAUI synchronization state<br>machine for bonding four<br>channels                                                         | XAUI synchronization state<br>machine for realigning four<br>channels                                                                                                                              |

| SRIO 1.3 and 2.1                           | 1.25 to 3.125                             | Custom PHY IP core with preset feature     SRIO version 2.1-compliant x2 and x4 channel bonding                            | Custom PHY IP core with preset feature     SRIO version 2.1-compliant x2 and x4 deskew state machine                                                                                               |

| SDI, SD/HD, and 3G-SDI                     | 0.27 <sup>(14)</sup> , 1.485,<br>and 2.97 | Custom PHY IP core with preset feature                                                                                     | Custom PHY IP core with preset feature                                                                                                                                                             |

| JESD204A                                   | 0.3125 <sup>(15)</sup> to<br>3.125        |                                                                                                                            |                                                                                                                                                                                                    |

|                                            | ,                                         |                                                                                                                            | continued                                                                                                                                                                                          |

<sup>(12)</sup> PCIe Gen2 is supported for Cyclone V GT and ST devices. The PCIe Gen2 x4 support is PCIe-compatible.

<sup>(13)</sup> XAUI is supported through the soft PCS.

$<sup>^{(14)}</sup>$  The 0.27-Gbps data rate is supported using oversampling user logic that you must implement in the FPGA fabric.

<sup>(15)</sup> The 0.3125-Gbps data rate is supported using oversampling user logic that you must implement in the FPGA fabric.

| PCS Support                     | Data Rates<br>(Gbps) | Transmitter Data Path Feature                              | Receiver Data Path Feature                                                                    |

|---------------------------------|----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Serial ATA Gen1 and Gen2        | 1.5 and 3.0          | Custom PHY IP core with preset feature     Electrical idle | Custom PHY IP core with preset feature     Signal detect     Wider spread of asynchronous SSC |

| CPRI 4.1 <sup>(16)</sup>        | 0.6144 to 6.144      | Dedicated deterministic latency     PHY IP core            | Dedicated deterministic latency     PHY IP core                                               |

| OBSAI RP3                       | 0.768 to 3.072       | Transmitter (TX) manual bit-slip<br>mode                   | Receiver (RX) deterministic latency state machine                                             |

| V-by-One HS                     | Up to 3.75           | Custom PHY IP core                                         | Custom PHY IP core                                                                            |

| DisplayPort 1.2 <sup>(17)</sup> | 1.62 and 2.7         |                                                            | Wider spread of asynchronous     SSC                                                          |

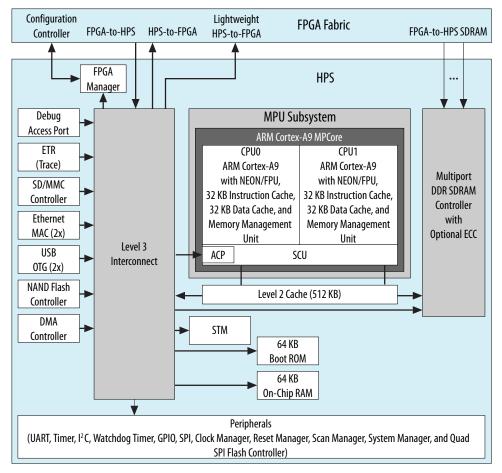

### **SoC with HPS**

Each SoC combines an FPGA fabric and an HPS in a single device. This combination delivers the flexibility of programmable logic with the power and cost savings of hard IP in these ways:

- Reduces board space, system power, and bill of materials cost by eliminating a discrete embedded processor

- Allows you to differentiate the end product in both hardware and software, and to support virtually any interface standard

- Extends the product life and revenue through in-field hardware and software updates

### **HPS Features**

The HPS consists of a dual-core Arm Cortex-A9 MPCore processor, a rich set of peripherals, and a shared multiport SDRAM memory controller, as shown in the following figure.

<sup>(16)</sup> High-voltage output mode (1000-BASE-CX) is not supported.

<sup>(17)</sup> Pending characterization.

Figure 11. HPS with Dual-Core Arm Cortex-A9 MPCore Processor

#### **System Peripherals and Debug Access Port**

Each Ethernet MAC, USB OTG, NAND flash controller, and SD/MMC controller module has an integrated DMA controller. For modules without an integrated DMA controller, an additional DMA controller module provides up to eight channels of high-bandwidth data transfers. Peripherals that communicate off-chip are multiplexed with other peripherals at the HPS pin level. This allows you to choose which peripherals to interface with other devices on your PCB.

The debug access port provides interfaces to industry standard JTAG debug probes and supports Arm CoreSight debug and core traces to facilitate software development.

Note:

Although the FPGA fabric and HPS are on separate power domains, the HPS must remain powered up during operation while the FPGA fabric can be powered up or down as required.

#### **Related Information**

Cyclone V Device Family Pin Connection Guidelines

Provides detailed information about power supply pin connection guidelines and power regulator sharing.

### **Hardware and Software Development**

For hardware development, you can configure the HPS and connect your soft logic in the FPGA fabric to the HPS interfaces using the Platform Designer (Standard) system integration tool in the Intel Quartus Prime software.

For software development, the Arm-based SoC devices inherit the rich software development ecosystem available for the Arm Cortex-A9 MPCore processor. The software development process for Intel SoCs follows the same steps as those for other SoC devices from other manufacturers. Support for Linux, VxWorks<sup>®</sup>, and other operating systems is available for the SoCs. For more information on the operating systems support availability, contact the Intel sales team.

You can begin device-specific firmware and software development on the Intel SoC Virtual Target. The Virtual Target is a fast PC-based functional simulation of a target development system—a model of a complete development board that runs on a PC. The Virtual Target enables the development of device-specific production software that can run unmodified on actual hardware.

#### **Related Information**

International Altera Sales Support Offices

### **Dynamic and Partial Reconfiguration**

The Cyclone V devices support dynamic reconfiguration and partial reconfiguration.

#### **Dynamic Reconfiguration**

The dynamic reconfiguration feature allows you to dynamically change the transceiver data rates, PMA settings, or protocols of a channel, without affecting data transfer on adjacent channels. This feature is ideal for applications that require on-the-fly multiprotocol or multirate support. You can reconfigure the PMA and PCS blocks with dynamic reconfiguration.

### **Partial Reconfiguration**

Note:

The partial reconfiguration feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

Partial reconfiguration allows you to reconfigure part of the device while other sections of the device remain operational. This capability is important in systems with critical uptime requirements because it allows you to make updates or adjust functionality without disrupting services.

### **Power Management**

Leveraging the FPGA architectural features, process technology advancements, and transceivers that are designed for power efficiency, the Cyclone V devices consume less power than previous generation Cyclone FPGAs:

- Total device core power consumption—less by up to 40%.

- Transceiver channel power consumption—less by up to 50%.

Additionally, Cyclone V devices contain several hard IP blocks that reduce logic resources and deliver substantial power savings of up to 25% less power than equivalent soft implementations.

# **Document Revision History for Cyclone V Device Overview**

| Document<br>Version | Changes                                                                                                                                                                                        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2018.05.07          | <ul> <li>Added the low power option ("L" suffix) for Cyclone V SE and Cyclone V SX devices in the Sample Ordering Code and Available Options diagrams.</li> <li>Rebranded as Intel.</li> </ul> |

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2017 | 2017.12.18 | Updated ALM resources for Cyclone V E, Cyclone V SE, Cyclone V SX, and Cyclone V ST devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| June 2016     | 2016.06.10 | Updated Cyclone V GT speed grade to -7 in Sample Ordering Code and Available Options for Cyclone V GT Devices diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| December 2015 | 2015.12.21 | <ul> <li>Added descriptions to package plan tables for Cyclone V GT and ST devices.</li> <li>Changed instances of <i>Quartus II</i> to <i>Quartus Prime</i>.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| June 2015     | 2015.06.12 | <ul> <li>Replaced a note to partial reconfiguration feature. Note: The partial reconfiguration feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Altera sales representatives.</li> <li>Updated logic elements (LE) (K) for the following devices:         <ul> <li>Cyclone V E A7: Updated from 149.5 to 150</li> <li>Cyclone V GX C3: Updated from 35.5 to 36</li> <li>Cyclone V GX C7: Updated from 149.7 to 150</li> <li>Cyclone V GT D7: Updated from 149.5 to 150</li> </ul> </li> <li>Updated MLAB (Kb) in Maximum Resource Counts for Cyclone V GX Devices table as follows:         <ul> <li>Cyclone V GX C3: Updated from 291 to 182</li> <li>Cyclone V GX C4: Updated from 678 to 424</li> <li>Cyclone V GX C5: Updated from 1,338 to 836</li> <li>Cyclone V GX C9: Updated from 2,748 to 1,717</li> </ul> </li> </ul> |

|               |            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Date         | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |            | <ul> <li>Updated MLAB RAM Bit (Kb) in Embedded Memory Capacity and Distribution in Cyclone V Devices table as follows:         <ul> <li>Cyclone V GX C3: Updated from 181 to 182</li> <li>Cyclone V GX C4: Updated from 295 to 424</li> </ul> </li> <li>Updated Total RAM Bit (Kb) in Embedded Memory Capacity and Distribution in Cyclone V Devices table as follows:         <ul> <li>Cyclone V GX C3: Updated from 1,531 to 1,532</li> <li>Cyclone V GX C4: Updated from 2,795 to 2,924</li> </ul> </li> <li>Updated MLAB Block count in Embedded Memory Capacity and Distribution in Cyclone V Devices table as follows:         <ul> <li>Cyclone V GX C4: Updated from 472 to 678</li> <li>Cyclone V GX C5: Updated from 679 to 678</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| March 2015   | 2015.03.31 | Added internal scrubbing feature under configuration in Summary of Features for Cyclone V Devices table.     Added optional suffix "SC: Internal scrubbing support" to the following diagrams:     — Sample Ordering Code and Available Options for Cyclone V E Devices     — Sample Ordering Code and Available Options for Cyclone V GX Devices     — Sample Ordering Code and Available Options for Cyclone V SE Devices     — Sample Ordering Code and Available Options for Cyclone V SX Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| January 2015 | 2015.01.23 | <ul> <li>Updated Sample Ordering Code and Available Options for Cyclone V ST Devices figure because Cyclone V ST devices are only available in I temperature grade and -7 speed grade.</li> <li>Operating Temperature: Removed C and A temperature grades</li> <li>FPGA Fabric Speed Grade: Removed -6 and -8 speed grades</li> <li>Updated the transceiver specification for Cyclone V ST from 5 Gbps to 6.144 Gbps:</li> <li>Device Variants for the Cyclone V Device Family table</li> <li>Sample Ordering Code and Available Options for Cyclone V ST Devices figure</li> <li>Maximum Resource Counts for Cyclone V ST Devices</li> <li>Updated Maximum Resource Counts for Cyclone V GX Devices table for Cyclone V GX G3 devices.</li> <li>Logic elements (LE) (K): Updated from 35.7 to 35.5</li> <li>Variable-precision DSP block: Updated from 51 to 57</li> <li>18 x 18 multiplier: Updated from 102 to 114</li> <li>Updated Number of Multipliers in Cyclone V Devices table for Cyclone V GX G3 devices.</li> <li>Variableprecision DSP Block: Updated from 51 to 57</li> <li>9 x 9 Multiplier: Updated from 153 to 171</li> <li>18 x 18 Multiplier: Updated from 102 to 114</li> <li>27 x 27 Multiplier: Updated from 51 to 57</li> <li>18 x 18 Multiplier Adder Mode: Updated from 51 to 57</li> <li>18 x 18 Multiplier Adder Summed with 36 bit Input: Updated from 51 to 57</li> <li>Updated Embedded Memory Capacity and Distribution in Cyclone V Devices table for Cyclone V GX G3 devices.</li> <li>M10K Block: Updated from 119 to 135</li> <li>M10K RAM bit (Kb): Updated from 1,190 to 1,350</li> <li>MLAB BRAM bit (Kb): Updated from 1,349 to 1,531</li> </ul> |

| October 2014 | 2014.10.06 | Added a footnote to the "Transceiver PCS Features for Cyclone V Devices" table to show that PCIe Gen2 is supported for Cyclone V GT and ST devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|