Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 11900                                                      |

| Number of Logic Elements/Cells | 31500                                                      |

| Total RAM Bits                 | 1381376                                                    |

| Number of I/O                  | 208                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 125°C (TJ)                                         |

| Package / Case                 | 484-FBGA                                                   |

| Supplier Device Package        | 484-UBGA (19x19)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5cgxfc3b6u19a7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| Cyclone | V Device Overview                                      | . 3 |

|---------|--------------------------------------------------------|-----|

| Ke      | ey Advantages of Cyclone V Devices                     | . 3 |

| Su      | ummary of Cyclone V Features                           | .4  |

|         | vclone V Device Variants and Packages                  |     |

| •       | Cyclone V E                                            |     |

|         | Cyclone V GX                                           | . 7 |

|         | Cyclone V GT                                           |     |

|         | Cyclone V SE                                           |     |

|         | Cyclone V SX                                           |     |

|         | Cyclone V ST                                           |     |

| I/0     | O Vertical Migration for Cyclone V Devices             |     |

| -       | daptive Logic Module                                   |     |

|         | riable-Precision DSP Block                             |     |

| En      | nbedded Memory Blocks                                  | 21  |

|         | Types of Embedded Memory                               |     |

|         | Embedded Memory Capacity in Cyclone V Devices          |     |

|         | Embedded Memory Configurations                         | 22  |

| Cle     | ock Networks and PLL Clock Sources                     | 22  |

| FP      | PGA General Purpose I/O                                | 23  |

| PC      | CIe Gen1 and Gen2 Hard IP                              | 24  |

| Ex      | ternal Memory Interface                                | 24  |

|         | Hard and Soft Memory Controllers                       |     |

|         | External Memory Performance                            |     |

|         | HPS External Memory Performance                        |     |

| Lo      | w-Power Serial Transceivers                            |     |

|         | Transceiver Channels                                   |     |

|         | PMA Features                                           |     |

|         | PCS Features                                           |     |

| Sc      | oC with HPS                                            |     |

|         | HPS Features                                           |     |

|         | FPGA Configuration and Processor Booting               |     |

|         | Hardware and Software Development                      |     |

| Dy      | namic and Partial Reconfiguration                      |     |

|         | Dynamic Reconfiguration                                |     |

|         | Partial Reconfiguration                                |     |

|         | hanced Configuration and Configuration via Protocol    |     |

|         | wer Management                                         |     |

| Do      | ocument Revision History for Cyclone V Device Overview | 33  |

# **Cyclone V Device Overview**

The Cyclone® V devices are designed to simultaneously accommodate the shrinking power consumption, cost, and time-to-market requirements; and the increasing bandwidth requirements for high-volume and cost-sensitive applications.

Enhanced with integrated transceivers and hard memory controllers, the Cyclone V devices are suitable for applications in the industrial, wireless and wireline, military, and automotive markets.

#### **Related Information**

Cyclone V Device Handbook: Known Issues

Lists the planned updates to the Cyclone V Device Handbook chapters.

# **Key Advantages of Cyclone V Devices**

Table 1. Key Advantages of the Cyclone V Device Family

| Advantage                                                                           | Supporting Feature                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lower power consumption                                                             | Built on TSMC's 28 nm low-power (28LP) process technology and includes an abundance of hard intellectual property (IP) blocks     Up to 40% lower power consumption than the previous generation device                                                                        |

| Improved logic integration and differentiation capabilities                         | 8-input adaptive logic module (ALM)     Up to 13.59 megabits (Mb) of embedded memory     Variable-precision digital signal processing (DSP) blocks                                                                                                                             |

| Increased bandwidth capacity                                                        | 3.125 gigabits per second (Gbps) and 6.144 Gbps transceivers     Hard memory controllers                                                                                                                                                                                       |

| Hard processor system (HPS)<br>with integrated Arm* Cortex*-A9<br>MPCore* processor | <ul> <li>Tight integration of a dual-core Arm Cortex-A9 MPCore processor, hard IP, and an FPGA in a single Cyclone V system-on-a-chip (SoC)</li> <li>Supports over 128 Gbps peak bandwidth with integrated data coherency between the processor and the FPGA fabric</li> </ul> |

| Lowest system cost                                                                  | Requires only two core voltages to operate  Available in low-cost wirebond packaging  Includes innovative features such as Configuration via Protocol (CvP) and partial reconfiguration                                                                                        |

# **Summary of Cyclone V Features**

**Summary of Features for Cyclone V Devices** Table 2.

| Feature                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                    |  |  |  |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Technology                                        | TSMC's 28-nm low-p 1.1 V core voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | , , , , , , , , , , , , , , , , , , , ,                                                                                            |  |  |  |  |  |

| Packaging                                         | Multiple device densi<br>different device densi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Multiple device densities with compatible package footprints for seamless migration between different device densities             |  |  |  |  |  |

| High-performance<br>FPGA fabric                   | Enhanced 8-input ALM v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vith four registers                                                                                                                |  |  |  |  |  |

| Internal memory<br>blocks                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (b) memory blocks with soft error correction code (ECC) block (MLAB)—640-bit distributed LUTRAM where you can use up to 25% memory |  |  |  |  |  |

| Embedded Hard IP<br>blocks                        | Variable-precision DSP  • Native support for up to three signal processing precision levels (three 9 x 9, two 18 x 18, or one 27 x 27 multiplier) in the sam variable-precision DSP block  • 64-bit accumulator and cascade  • Embedded internal coefficient memory  • Preadder/subtractor for improved efficiency                                                                                                                                                                                                                                |                                                                                                                                    |  |  |  |  |  |

|                                                   | Memory controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DDR3, DDR2, and LPDDR2 with 16 and 32 bit ECC support                                                                              |  |  |  |  |  |

|                                                   | Embedded transceiver I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PCI Express* (PCIe*) Gen2 and Gen1 (x1, x2, or x4) hard IP with multifunction support, endpoint, and root port                     |  |  |  |  |  |

| Clock networks                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ol clock network<br>d peripheral clock networks<br>are not used can be powered down to reduce dynamic power                        |  |  |  |  |  |

| Phase-locked loops<br>(PLLs)                      | Precision clock synth     Integer mode and from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | esis, clock delay compensation, and zero delay buffering (ZDB) actional mode                                                       |  |  |  |  |  |

| FPGA General-purpose<br>I/Os (GPIOs)              | 400 MHz/800 Mbps 6     On-chip termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cond (Mbps) LVDS receiver and 840 Mbps LVDS transmitter<br>external memory interface<br>(OCT)<br>p to 16 mA drive strength         |  |  |  |  |  |

| Low-power high-speed serial interface             | Transmit pre-emphase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Sbps integrated transceiver speed sis and receiver equalization infiguration of individual channels                                |  |  |  |  |  |

| HPS<br>(Cyclone V SE, SX,<br>and ST devices only) | <ul> <li>Single or dual-core Arm Cortex-A9 MPCore processor-up to 925 MHz maximum frequency with support for symmetric and asymmetric multiprocessing</li> <li>Interface peripherals—10/100/1000 Ethernet media access control (EMAC), USB 2.0 On-The-GO (OTG) controller, quad serial peripheral interface (QSPI) flash controller, NAND flash controller, Secure Digital/MultiMediaCard (SD/MMC) controller, UART, controller area network (CAN), serial peripheral interface (SPI), I²C interface, and up to 85 HPS GPIO interfaces</li> </ul> |                                                                                                                                    |  |  |  |  |  |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -general-purpose timers, watchdog timers, direct memory access (DMA)<br>iguration manager, and clock and reset managers<br>ot ROM  |  |  |  |  |  |

|                                                   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | continued                                                                                                                          |  |  |  |  |  |

<sup>(1)</sup> Contact Intel for availability.

### **Available Options**

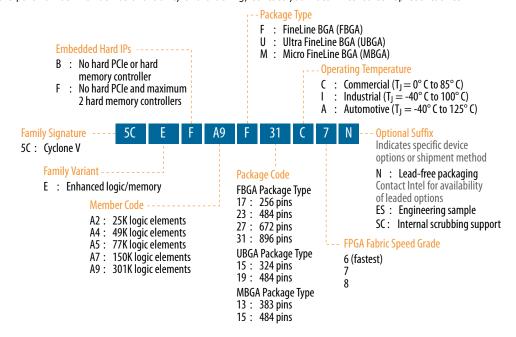

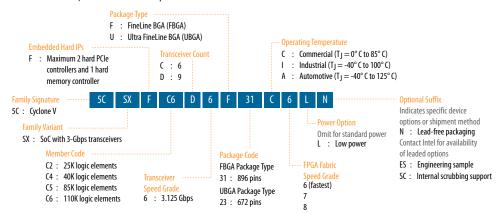

#### Figure 1. Sample Ordering Code and Available Options for Cyclone V E Devices

The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

**Table 4.** Maximum Resource Counts for Cyclone V E Devices

| Resource               |              |        | Member Code |         |         |         |  |  |  |

|------------------------|--------------|--------|-------------|---------|---------|---------|--|--|--|

|                        |              | A2     | A4          | A5      | A7      | А9      |  |  |  |

| Logic Elements         | (LE) (K)     | 25     | 49          | 77      | 150     | 301     |  |  |  |

| ALM                    |              | 9,430  | 18,480      | 29,080  | 56,480  | 113,560 |  |  |  |

| Register               |              | 37,736 | 73,920      | 116,320 | 225,920 | 454,240 |  |  |  |

| Memory (Kb)            | M10K         | 1,760  | 3,080       | 4,460   | 6,860   | 12,200  |  |  |  |

|                        | MLAB         | 196    | 303         | 424     | 836     | 1,717   |  |  |  |

| Variable-precision     | on DSP Block | 25     | 66          | 150     | 156     | 342     |  |  |  |

| 18 x 18 Multipli       | er           | 50     | 132         | 300     | 312     | 684     |  |  |  |

| PLL                    |              | 4      | 4           | 6       | 7       | 8       |  |  |  |

| GPIO                   |              | 224    | 224         | 240     | 480     | 480     |  |  |  |

| LVDS                   | Transmitter  | 56     | 56          | 60      | 120     | 120     |  |  |  |

|                        | Receiver     | 56     | 56          | 60      | 120     | 120     |  |  |  |

| Hard Memory Controller |              | 1      | 1           | 2       | 2       | 2       |  |  |  |

#### **Related Information**

True LVDS Buffers in Devices, I/O Features in Cyclone V Devices

Provides the number of LVDS channels in each device package.

### **Package Plan**

**Table 5.** Package Plan for Cyclone V E Devices

| Member<br>Code | M383<br>(13 mm) | M484<br>(15 mm) | U324<br>(15 mm) | F256<br>(17 mm) | U484<br>(19 mm) | F484<br>(23 mm) | F672<br>(27 mm) | F896<br>(31 mm) |

|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|                | GPIO            |

| A2             | 223             | _               | 176             | 128             | 224             | 224             | _               | _               |

| A4             | 223             | _               | 176             | 128             | 224             | 224             | _               | _               |

| A5             | 175             | _               | _               | _               | 224             | 240             | _               | _               |

| A7             | _               | 240             | _               | _               | 240             | 240             | 336             | 480             |

| A9             | _               | _               | _               | _               | 240             | 224             | 336             | 480             |

# **Cyclone V GX**

This section provides the available options, maximum resource counts, and package plan for the Cyclone V GX devices.

The information in this section is correct at the time of publication. For the latest information and to get more details, refer to the *Product Selector Guide*.

### **Related Information**

**Product Selector Guide**

Provides the latest information about Intel products.

### **Available Options**

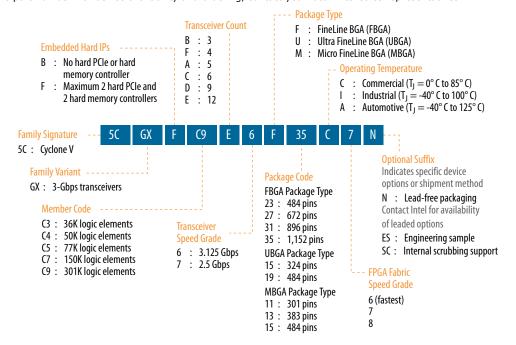

### Figure 2. Sample Ordering Code and Available Options for Cyclone V GX Devices

The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

**Table 6.** Maximum Resource Counts for Cyclone V GX Devices

| Resource            |             |        | Member Code |           |           |           |  |  |  |

|---------------------|-------------|--------|-------------|-----------|-----------|-----------|--|--|--|

|                     |             | С3     | C4          | <b>C5</b> | <b>C7</b> | С9        |  |  |  |

| Logic Elements (    | (LE) (K)    | 36     | 50          | 77        | 150       | 301       |  |  |  |

| ALM                 |             | 13,460 | 18,860      | 29,080    | 56,480    | 113,560   |  |  |  |

| Register            |             | 53,840 | 75,440      | 116,320   | 225,920   | 454,240   |  |  |  |

| Memory (Kb)         | M10K        | 1,350  | 2,500       | 4,460     | 6,860     | 12,200    |  |  |  |

|                     | MLAB        | 182    | 424         | 424       | 836       | 1,717     |  |  |  |

| Variable-precision  | n DSP Block | 57     | 70          | 150       | 156       | 342       |  |  |  |

| 18 x 18 Multiplie   | er          | 114    | 140         | 300       | 312       | 684       |  |  |  |

| PLL                 | PLL         |        | 6           | 6         | 7         | 8         |  |  |  |

| 3 Gbps Transceiver  |             | 3      | 6           | 6         | 9         | 12        |  |  |  |

| GPIO <sup>(4)</sup> |             | 208    | 336         | 336       | 480       | 560       |  |  |  |

|                     |             |        |             |           |           | continued |  |  |  |

<sup>(4)</sup> The number of GPIOs does not include transceiver I/Os. In the Intel Quartus® Prime software, the number of user I/Os includes transceiver I/Os.

### **Available Options**

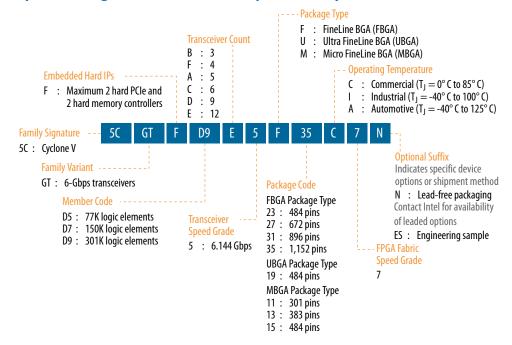

Figure 3. Sample Ordering Code and Available Options for Cyclone V GT Devices

**Table 8.** Maximum Resource Counts for Cyclone V GT Devices

| Resource              |             | Member Code |         |           |  |  |  |

|-----------------------|-------------|-------------|---------|-----------|--|--|--|

|                       |             | D5          | D7      | D9        |  |  |  |

| Logic Elements (LE) ( | K)          | 77          | 150     | 301       |  |  |  |

| ALM                   |             | 29,080      | 56,480  | 113,560   |  |  |  |

| Register              |             | 116,320     | 225,920 | 454,240   |  |  |  |

| Memory (Kb)           | M10K        | 4,460       | 6,860   | 12,200    |  |  |  |

|                       | MLAB        | 424         | 836     | 1,717     |  |  |  |

| Variable-precision DS | P Block     | 150         | 156     | 342       |  |  |  |

| 18 x 18 Multiplier    |             | 300         | 312     | 684       |  |  |  |

| PLL                   |             |             | 7       | 8         |  |  |  |

| 6 Gbps Transceiver    |             | 6           | 9       | 12        |  |  |  |

| GPIO <sup>(5)</sup>   |             | 336         | 480     | 560       |  |  |  |

| LVDS                  | Transmitter | 84          | 120     | 140       |  |  |  |

|                       | ,           | •           |         | continued |  |  |  |

<sup>(5)</sup> The number of GPIOs does not include transceiver I/Os. In the Intel Quartus Prime software, the number of user I/Os includes transceiver I/Os.

#### CV-51001 | 2018.05.07

| Resource               |          | Member Code |     |     |  |  |

|------------------------|----------|-------------|-----|-----|--|--|

|                        |          | D5          | D7  | D9  |  |  |

|                        | Receiver | 84          | 120 | 140 |  |  |

| PCIe Hard IP Block     |          | 2           | 2   | 2   |  |  |

| Hard Memory Controller |          | 2           | 2   | 2   |  |  |

#### **Related Information**

True LVDS Buffers in Devices, I/O Features in Cyclone V Devices

Provides the number of LVDS channels in each device package.

## **Package Plan**

### **Table 9.** Package Plan for Cyclone V GT Devices

Transceiver counts shown are for transceiver  $\leq 5$  Gbps . 6 Gbps transceiver channel count support depends on the package and channel usage. For more information about the 6 Gbps transceiver channel count, refer to the Cyclone V Device Handbook Volume 2: Transceivers.

| Member<br>Code | M301<br>(11 mm) |      | M383<br>(13 mm) |      | M484<br>(15 mm) |      | U484<br>(19 mm) |      |

|----------------|-----------------|------|-----------------|------|-----------------|------|-----------------|------|

|                | GPIO            | XCVR | GPIO            | XCVR | GPIO            | XCVR | GPIO            | XCVR |

| D5             | 129             | 4    | 175             | 6    | _               | _    | 224             | 6    |

| D7             | _               | _    | _               | _    | 240             | 3    | 240             | 6    |

| D9             | _               | _    | _               | _    | _               | _    | 240             | 5    |

| Member<br>Code | F484<br>(23 mm) |      | F672<br>(27 mm) |       | F896<br>(31 mm) |                   | F1152<br>(35 mm) |                   |

|----------------|-----------------|------|-----------------|-------|-----------------|-------------------|------------------|-------------------|

|                | GPIO            | XCVR | GPIO            | XCVR  | GPIO            | XCVR              | GPIO             | XCVR              |

| D5             | 240             | 6    | 336             | 6     | _               | _                 | _                | _                 |

| D7             | 240             | 6    | 336             | 9 (6) | 480             | 9 (6)             | _                | _                 |

| D9             | 224             | 6    | 336             | 9 (6) | 480             | 12 <sup>(7)</sup> | 560              | 12 <sup>(7)</sup> |

#### **Related Information**

6.144-Gbps Support Capability in Cyclone V GT Devices, Cyclone V Device Handbook Volume 2: Transceivers

Provides more information about 6 Gbps transceiver channel count.

<sup>(6)</sup> If you require CPRI (at 6.144 Gbps) and PCIe Gen2 transmit jitter compliance, Intel recommends that you use only up to three full-duplex transceiver channels for CPRI, and up to six full-duplex channels for PCIe Gen2. The CMU channels are not considered full-duplex channels.

<sup>&</sup>lt;sup>(7)</sup> If you require CPRI (at 6.144 Gbps) and PCIe Gen2 transmit jitter compliance, Intel recommends that you use only up to three full-duplex transceiver channels for CPRI, and up to eight full-duplex channels for PCIe Gen2. The CMU channels are not considered full-duplex channels.

### **Cyclone V SE**

This section provides the available options, maximum resource counts, and package plan for the Cyclone V SE devices.

The information in this section is correct at the time of publication. For the latest information and to get more details, refer to the *Product Selector Guide*.

#### **Related Information**

**Product Selector Guide**

Provides the latest information about Intel products.

#### **Available Options**

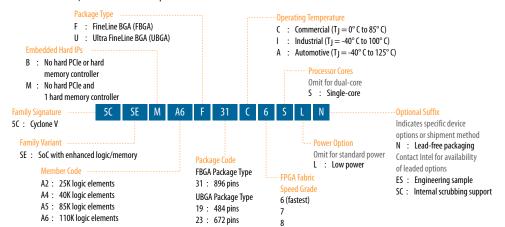

### Figure 4. Sample Ordering Code and Available Options for Cyclone V SE Devices

The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

Cyclone V SE and SX low-power devices (L power option) offer 30% static power reduction for devices with 25K LE and 40K LE, and 20% static power reduction for devices with 85K LE and 110K LE.

# **Maximum Resources**

Table 10. **Maximum Resource Counts for Cyclone V SE Devices**

| Res                            | ource              |                          | Member Code              |                      |                      |  |  |  |  |

|--------------------------------|--------------------|--------------------------|--------------------------|----------------------|----------------------|--|--|--|--|

|                                |                    | A2                       | A4                       | A5                   | A6                   |  |  |  |  |

| Logic Elements (               | LE) (K)            | 25                       | 40                       | 85                   | 110                  |  |  |  |  |

| ALM                            |                    | 9,430                    | 15,880                   | 32,070               | 41,910               |  |  |  |  |

| Register                       |                    | 37,736                   | 60,376                   | 128,300              | 166,036              |  |  |  |  |

| Memory (Kb)                    | M10K               | 1,400                    | 2,700                    | 3,970                | 5,570                |  |  |  |  |

|                                | MLAB               | 138                      | 231                      | 480                  | 621                  |  |  |  |  |

| Variable-precisio              | n DSP Block        | 36                       | 84                       | 87                   | 112                  |  |  |  |  |

| 18 x 18 Multiplie              | 18 x 18 Multiplier |                          | 168                      | 174                  | 224                  |  |  |  |  |

| FPGA PLL                       |                    | 5                        | 5                        | 6                    | 6                    |  |  |  |  |

| HPS PLL                        |                    | 3                        | 3                        | 3                    | 3                    |  |  |  |  |

| FPGA GPIO                      |                    | 145                      | 145                      | 288                  | 288                  |  |  |  |  |

| HPS I/O                        |                    | 181                      | 181                      | 181                  | 181                  |  |  |  |  |

| LVDS                           | Transmitter        | 32                       | 32                       | 72                   | 72                   |  |  |  |  |

|                                | Receiver           | 37                       | 37                       | 72                   | 72                   |  |  |  |  |

| FPGA Hard Memo                 | ory Controller     | 1                        | 1                        | 1                    | 1                    |  |  |  |  |

| HPS Hard Memory Controller     |                    | 1                        | 1                        | 1                    | 1                    |  |  |  |  |

| Arm Cortex-A9 MPCore Processor |                    | Single- or dual-<br>core | Single- or dual-<br>core | Single- or dual-core | Single- or dual-core |  |  |  |  |

#### **Related Information**

True LVDS Buffers in Devices, I/O Features in Cyclone V Devices Provides the number of LVDS channels in each device package.

# **Package Plan**

#### **Package Plan for Cyclone V SE Devices** Table 11.

The HPS I/O counts are the number of I/Os in the HPS and does not correlate with the number of HPS-specific I/O pins in the FPGA. Each HPS-specific pin in the FPGA may be mapped to several HPS I/Os.

| Member Code | U484<br>(19 mm) |         | U672<br>(23 mm) |         | F896<br>(31 mm) |         |

|-------------|-----------------|---------|-----------------|---------|-----------------|---------|

|             | FPGA GPIO       | HPS I/O | FPGA GPIO       | HPS I/O | FPGA GPIO       | HPS I/O |

| A2          | 66              | 151     | 145             | 181     | _               | _       |

| A4          | 66              | 151     | 145             | 181     | _               | _       |

| A5          | 66              | 151     | 145             | 181     | 288             | 181     |

| A6          | 66              | 151     | 145             | 181     | 288             | 181     |

### **Cyclone V SX**

This section provides the available options, maximum resource counts, and package plan for the Cyclone V SX devices.

The information in this section is correct at the time of publication. For the latest information and to get more details, refer to the *Product Selector Guide*.

#### **Related Information**

#### **Product Selector Guide**

Provides the latest information about Intel products.

#### **Available Options**

### Figure 5. Sample Ordering Code and Available Options for Cyclone V SX Devices

The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

Cyclone V SE and SX low-power devices (L power option) offer 30% static power reduction for devices with 25K LE and 40K LE, and 20% static power reduction for devices with 85K LE and 110K LE.

**Table 12.** Maximum Resource Counts for Cyclone V SX Devices

| Resource                     |      | Member Code |        |         |           |  |

|------------------------------|------|-------------|--------|---------|-----------|--|

|                              |      | C2          | C4     | C5      | C6        |  |

| Logic Elements (LE) (K)      |      | 25          | 40     | 85      | 110       |  |

| ALM                          |      | 9,430       | 15,880 | 32,070  | 41,910    |  |

| Register                     |      | 37,736      | 60,376 | 128,300 | 166,036   |  |

| Memory (Kb)                  | M10K | 1,400       | 2,700  | 3,970   | 5,570     |  |

|                              | MLAB | 138         | 231    | 480     | 621       |  |

| Variable-precision DSP Block |      | 36          | 84     | 87      | 112       |  |

| 18 x 18 Multiplier           |      | 72          | 168    | 174     | 224       |  |

| FPGA PLL                     |      | 5           | 5      | 6       | 6         |  |

|                              |      |             |        |         | continued |  |

#### CV-51001 | 2018.05.07

| Reso                        | urce | Member Code |           |  |

|-----------------------------|------|-------------|-----------|--|

|                             |      | D5          | D6        |  |

| Receiver                    |      | 72          | 72        |  |

| PCIe Hard IP Block          |      | 2           | 2         |  |

| FPGA Hard Memory Controller |      | 1           | 1         |  |

| HPS Hard Memory Controller  |      | 1           | 1         |  |

| Arm Cortex-A9 MPCore Proces | sor  | Dual-core   | Dual-core |  |

#### **Related Information**

True LVDS Buffers in Devices, I/O Features in Cyclone V Devices

Provides the number of LVDS channels in each device package.

### **Package Plan**

#### **Table 15.** Package Plan for Cyclone V ST Devices

- The HPS I/O counts are the number of I/Os in the HPS and does not correlate with the number of HPS-specific I/O pins in the FPGA. Each HPS-specific pin in the FPGA may be mapped to several HPS I/Os.

- Transceiver counts shown are for transceiver ≤5 Gbps . 6 Gbps transceiver channel count support depends on the package and channel usage. For more information about the 6 Gbps transceiver channel count, refer to the Cyclone V Device Handbook Volume 2: Transceivers.

| Member Code | F896<br>(31 mm) |         |        |  |

|-------------|-----------------|---------|--------|--|

|             | FPGA GPIO       | HPS I/O | XCVR   |  |

| D5          | 288             | 181     | 9 (11) |  |

| D6          | 288             | 181     | 9 (11) |  |

#### **Related Information**

6.144-Gbps Support Capability in Cyclone V GT Devices, Cyclone V Device Handbook Volume 2: Transceivers

Provides more information about 6 Gbps transceiver channel count.

<sup>(11)</sup> If you require CPRI (at 4.9152 Gbps) and PCIe Gen2 transmit jitter compliance, Intel recommends that you use only up to seven full-duplex transceiver channels for CPRI, and up to six full-duplex channels for PCIe Gen2. The CMU channels are not considered full-duplex channels.

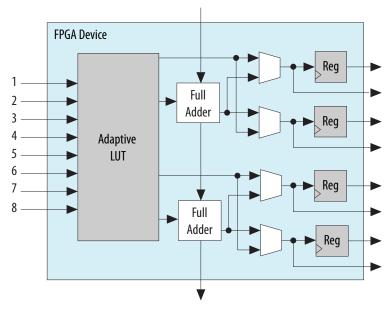

Figure 8. ALM for Cyclone V Devices

You can configure up to 25% of the ALMs in the Cyclone V devices as distributed memory using MLABs.

#### **Related Information**

Embedded Memory Capacity in Cyclone V Devices on page 21 Lists the embedded memory capacity for each device.

# **Variable-Precision DSP Block**

Cyclone V devices feature a variable-precision DSP block that supports these features:

- Configurable to support signal processing precisions ranging from 9 x 9, 18 x 18 and 27 x 27 bits natively

- A 64-bit accumulator

- A hard preadder that is available in both 18- and 27-bit modes

- Cascaded output adders for efficient systolic finite impulse response (FIR) filters

- Internal coefficient register banks, 8 deep, for each multiplier in 18- or 27-bit mode

- Fully independent multiplier operation

- A second accumulator feedback register to accommodate complex multiplyaccumulate functions

- Fully independent Efficient support for single-precision floating point arithmetic

- The inferability of all modes by the Intel Quartus Prime design software

Table 16. Variable-Precision DSP Block Configurations for Cyclone V Devices

| Usage Example                                           | Multiplier Size (Bit)       | DSP Block Resource |

|---------------------------------------------------------|-----------------------------|--------------------|

| Low precision fixed point for video applications        | Three 9 x 9                 | 1                  |

| Medium precision fixed point in FIR filters             | Two 18 x 18                 | 1                  |

| FIR filters and general DSP usage                       | Two 18 x 18 with accumulate | 1                  |

| High precision fixed- or floating-point implementations | One 27 x 27 with accumulate | 1                  |

You can configure each DSP block during compilation as independent three 9  $\times$  9, two 18  $\times$  18, or one 27  $\times$  27 multipliers. With a dedicated 64 bit cascade bus, you can cascade multiple variable-precision DSP blocks to implement even higher precision DSP functions efficiently.

**Table 17.** Number of Multipliers in Cyclone V Devices

The table lists the variable-precision DSP resources by bit precision for each Cyclone V device.

| Variant      | Code precis | Variable-<br>precision<br>DSP Block | Traitiphications operator |                       |                       | 18 x 18<br>Multiplier<br>Adder Mode | 18 x 18<br>Multiplier<br>Adder |

|--------------|-------------|-------------------------------------|---------------------------|-----------------------|-----------------------|-------------------------------------|--------------------------------|

|              |             | DSP Block                           | 9 x 9<br>Multiplier       | 18 x 18<br>Multiplier | 27 x 27<br>Multiplier | Adder Mode                          | Summed<br>with 36 bit<br>Input |

| Cyclone V E  | A2          | 25                                  | 75                        | 50                    | 25                    | 25                                  | 25                             |

|              | A4          | 66                                  | 198                       | 132                   | 66                    | 66                                  | 66                             |

|              | A5          | 150                                 | 450                       | 300                   | 150                   | 150                                 | 150                            |

|              | A7          | 156                                 | 468                       | 312                   | 156                   | 156                                 | 156                            |

|              | A9          | 342                                 | 1,026                     | 684                   | 342                   | 342                                 | 342                            |

| Cyclone V    | C3          | 57                                  | 171                       | 114                   | 57                    | 57                                  | 57                             |

| GX           | C4          | 70                                  | 210                       | 140                   | 70                    | 70                                  | 70                             |

|              | C5          | 150                                 | 450                       | 300                   | 150                   | 150                                 | 150                            |

|              | C7          | 156                                 | 468                       | 312                   | 156                   | 156                                 | 156                            |

|              | C9          | 342                                 | 1,026                     | 684                   | 342                   | 342                                 | 342                            |

| Cyclone V GT | D5          | 150                                 | 450                       | 300                   | 150                   | 150                                 | 150                            |

|              | D7          | 156                                 | 468                       | 312                   | 156                   | 156                                 | 156                            |

|              | D9          | 342                                 | 1,026                     | 684                   | 342                   | 342                                 | 342                            |

| Cyclone V SE | A2          | 36                                  | 108                       | 72                    | 36                    | 36                                  | 36                             |

|              | A4          | 84                                  | 252                       | 168                   | 84                    | 84                                  | 84                             |

|              | A5          | 87                                  | 261                       | 174                   | 87                    | 87                                  | 87                             |

|              | A6          | 112                                 | 336                       | 224                   | 112                   | 112                                 | 112                            |

| Cyclone V SX | C2          | 36                                  | 108                       | 72                    | 36                    | 36                                  | 36                             |

|              | C4          | 84                                  | 252                       | 168                   | 84                    | 84                                  | 84                             |

|              | C5          | 87                                  | 261                       | 174                   | 87                    | 87                                  | 87                             |

|              |             |                                     |                           |                       |                       |                                     | continued                      |

#### **PLL Features**

The PLLs in the Cyclone V devices support the following features:

- Frequency synthesis

- On-chip clock deskew

- Jitter attenuation

- Programmable output clock duty cycles

- PLL cascading

- Reference clock switchover

- Programmable bandwidth

- User-mode reconfiguration of PLLs

- Low power mode for each fractional PLL

- Dynamic phase shift

- Direct, source synchronous, zero delay buffer, external feedback, and LVDS compensation modes

#### **Fractional PLL**

In addition to integer PLLs, the Cyclone V devices use a fractional PLL architecture. The devices have up to eight PLLs, each with nine output counters. You can use the output counters to reduce PLL usage in two ways:

- Reduce the number of oscillators that are required on your board by using fractional PLLs

- Reduce the number of clock pins that are used in the device by synthesizing multiple clock frequencies from a single reference clock source

If you use the fractional PLL mode, you can use the PLLs for precision fractional-N frequency synthesis—removing the need for off-chip reference clock sources in your design.

The transceiver fractional PLLs that are not used by the transceiver I/Os can be used as general purpose fractional PLLs by the FPGA fabric.

# FPGA General Purpose I/O

Cyclone V devices offer highly configurable GPIOs. The following list describes the features of the GPIOs:

- Programmable bus hold and weak pull-up

- $\bullet$  LVDS output buffer with programmable differential output voltage (V $_{\text{OD}}$  ) and programmable pre-emphasis

- ullet On-chip parallel termination (R<sub>T</sub> OCT) for all I/O banks with OCT calibration to limit the termination impedance variation

- On-chip dynamic termination that has the ability to swap between series and parallel termination, depending on whether there is read or write on a common bus for signal integrity

- Easy timing closure support using the hard read FIFO in the input register path, and delay-locked loop (DLL) delay chain with fine and coarse architecture

| PCS Support                     | Data Rates<br>(Gbps) | Transmitter Data Path Feature                              | Receiver Data Path Feature                                                                    |

|---------------------------------|----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Serial ATA Gen1 and Gen2        | 1.5 and 3.0          | Custom PHY IP core with preset feature     Electrical idle | Custom PHY IP core with preset feature     Signal detect     Wider spread of asynchronous SSC |

| CPRI 4.1 <sup>(16)</sup>        | 0.6144 to 6.144      | Dedicated deterministic latency     PHY IP core            | Dedicated deterministic latency     PHY IP core                                               |

| OBSAI RP3                       | 0.768 to 3.072       | Transmitter (TX) manual bit-slip<br>mode                   | Receiver (RX) deterministic latency state machine                                             |

| V-by-One HS                     | Up to 3.75           | Custom PHY IP core                                         | Custom PHY IP core                                                                            |

| DisplayPort 1.2 <sup>(17)</sup> | 1.62 and 2.7         |                                                            | Wider spread of asynchronous     SSC                                                          |

## **SoC with HPS**

Each SoC combines an FPGA fabric and an HPS in a single device. This combination delivers the flexibility of programmable logic with the power and cost savings of hard IP in these ways:

- Reduces board space, system power, and bill of materials cost by eliminating a discrete embedded processor

- Allows you to differentiate the end product in both hardware and software, and to support virtually any interface standard

- Extends the product life and revenue through in-field hardware and software updates

## **HPS Features**

The HPS consists of a dual-core Arm Cortex-A9 MPCore processor, a rich set of peripherals, and a shared multiport SDRAM memory controller, as shown in the following figure.

<sup>(16)</sup> High-voltage output mode (1000-BASE-CX) is not supported.

<sup>(17)</sup> Pending characterization.

# **Power Management**

Leveraging the FPGA architectural features, process technology advancements, and transceivers that are designed for power efficiency, the Cyclone V devices consume less power than previous generation Cyclone FPGAs:

- Total device core power consumption—less by up to 40%.

- Transceiver channel power consumption—less by up to 50%.

Additionally, Cyclone V devices contain several hard IP blocks that reduce logic resources and deliver substantial power savings of up to 25% less power than equivalent soft implementations.

# **Document Revision History for Cyclone V Device Overview**

| Document<br>Version | Changes                                                                                                                                                                                        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2018.05.07          | <ul> <li>Added the low power option ("L" suffix) for Cyclone V SE and Cyclone V SX devices in the Sample Ordering Code and Available Options diagrams.</li> <li>Rebranded as Intel.</li> </ul> |

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2017 | 2017.12.18 | Updated ALM resources for Cyclone V E, Cyclone V SE, Cyclone V SX, and Cyclone V ST devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| June 2016     | 2016.06.10 | Updated Cyclone V GT speed grade to -7 in Sample Ordering Code and Available Options for Cyclone V GT Devices diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| December 2015 | 2015.12.21 | <ul> <li>Added descriptions to package plan tables for Cyclone V GT and ST devices.</li> <li>Changed instances of <i>Quartus II</i> to <i>Quartus Prime</i>.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| June 2015     | 2015.06.12 | <ul> <li>Replaced a note to partial reconfiguration feature. Note: The partial reconfiguration feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Altera sales representatives.</li> <li>Updated logic elements (LE) (K) for the following devices:         <ul> <li>Cyclone V E A7: Updated from 149.5 to 150</li> <li>Cyclone V GX C3: Updated from 35.5 to 36</li> <li>Cyclone V GX C7: Updated from 149.7 to 150</li> <li>Cyclone V GT D7: Updated from 149.5 to 150</li> </ul> </li> <li>Updated MLAB (Kb) in Maximum Resource Counts for Cyclone V GX Devices table as follows:         <ul> <li>Cyclone V GX C3: Updated from 291 to 182</li> <li>Cyclone V GX C4: Updated from 678 to 424</li> <li>Cyclone V GX C5: Updated from 1,338 to 836</li> <li>Cyclone V GX C9: Updated from 2,748 to 1,717</li> </ul> </li> </ul> |

|               |            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Date         | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |            | <ul> <li>Updated MLAB RAM Bit (Kb) in Embedded Memory Capacity and Distribution in Cyclone V Devices table as follows:         <ul> <li>Cyclone V GX C3: Updated from 181 to 182</li> <li>Cyclone V GX C4: Updated from 295 to 424</li> </ul> </li> <li>Updated Total RAM Bit (Kb) in Embedded Memory Capacity and Distribution in Cyclone V Devices table as follows:         <ul> <li>Cyclone V GX C3: Updated from 1,531 to 1,532</li> <li>Cyclone V GX C4: Updated from 2,795 to 2,924</li> </ul> </li> <li>Updated MLAB Block count in Embedded Memory Capacity and Distribution in Cyclone V Devices table as follows:         <ul> <li>Cyclone V GX C4: Updated from 472 to 678</li> <li>Cyclone V GX C5: Updated from 679 to 678</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| March 2015   | 2015.03.31 | Added internal scrubbing feature under configuration in Summary of Features for Cyclone V Devices table.     Added optional suffix "SC: Internal scrubbing support" to the following diagrams:     — Sample Ordering Code and Available Options for Cyclone V E Devices     — Sample Ordering Code and Available Options for Cyclone V GX Devices     — Sample Ordering Code and Available Options for Cyclone V SE Devices     — Sample Ordering Code and Available Options for Cyclone V SX Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| January 2015 | 2015.01.23 | <ul> <li>Updated Sample Ordering Code and Available Options for Cyclone V ST Devices figure because Cyclone V ST devices are only available in I temperature grade and -7 speed grade.</li> <li>Operating Temperature: Removed C and A temperature grades</li> <li>FPGA Fabric Speed Grade: Removed -6 and -8 speed grades</li> <li>Updated the transceiver specification for Cyclone V ST from 5 Gbps to 6.144 Gbps:         <ul> <li>Device Variants for the Cyclone V Device Family table</li> <li>Sample Ordering Code and Available Options for Cyclone V ST Devices figure</li> <li>Maximum Resource Counts for Cyclone V ST Devices</li> </ul> </li> <li>Updated Maximum Resource Counts for Cyclone V GX Devices table for Cyclone V GX G3 devices.         <ul> <li>Logic elements (LE) (K): Updated from 35.7 to 35.5</li> <li>Variable-precision DSP block: Updated from 51 to 57</li> <li>18 x 18 multiplier: Updated from 102 to 114</li> </ul> </li> <li>Updated Number of Multipliers in Cyclone V Devices table for Cyclone V GX G3 devices.         <ul> <li>Variableprecision DSP Block: Updated from 51 to 57</li> <li>9 x 9 Multiplier: Updated from 153 to 171</li> <li>18 x 18 Multiplier: Updated from 153 to 171</li> <li>18 x 18 Multiplier: Updated from 51 to 57</li> <li>18 x 18 Multiplier Adder Mode: Updated from 51 to 57</li> <li>18 x 18 Multiplier Adder Summed with 36 bit Input: Updated from 51 to 57</li> <li>18 x 18 Multiplier Adder Summed with 36 bit Input: Updated from 51 to 57</li> </ul> </li> <li>Updated Embedded Memory Capacity and Distribution in Cyclone V Devices table for Cyclone V GX G3 devices.         <ul> <li>M10K Block: Updated from 119 to 135</li> <li>M10K RAM bit (Kb): Updated from 1,190 to 1,350</li> <li>MLAB RAM bit (Kb): Updated from 1,349 to 1,531</li> </ul> </li></ul> |

| October 2014 | 2014.10.06 | Added a footnote to the "Transceiver PCS Features for Cyclone V Devices" table to show that PCIe Gen2 is supported for Cyclone V GT and ST devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|