Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1784-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

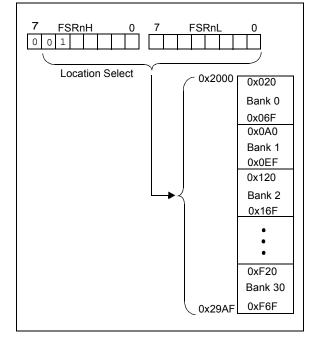

### 3.6.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

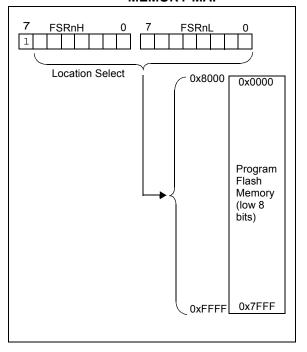

#### 3.6.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower 8 bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

DS40001637C-page 52

| Name   | Bit 7  | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|------------|-------|-------|-------|--------|--------|---------------------|

| BORCON | SBOREN | BORFS  | _          |       | _     |       |        | BORRDY | 61                  |

| PCON   | STKOVF | STKUNF | _          | RWDT  | RMCLR | RI    | POR    | BOR    | 65                  |

| STATUS |        |        | _          | TO    | PD    | Z     | DC     | С      | 27                  |

| WDTCON | —      | —      | WDTPS<4:0> |       |       |       | SWDTEN | 110    |                     |

#### TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| U-0                                     | U-0                               | U-0                              | R/W-0/0                                               | U-0                                | U-0 | U-0 | U-0   |  |

|-----------------------------------------|-----------------------------------|----------------------------------|-------------------------------------------------------|------------------------------------|-----|-----|-------|--|

| —                                       | —                                 | —                                | CCP3IE                                                | —                                  | —   | —   | —     |  |

| bit 7                                   |                                   |                                  |                                                       |                                    |     |     | bit 0 |  |

|                                         |                                   |                                  |                                                       |                                    |     |     |       |  |

| Legend:                                 |                                   |                                  |                                                       |                                    |     |     |       |  |

| R = Readable bit W = Writable bit       |                                   |                                  |                                                       | U = Unimplemented bit, read as '0' |     |     |       |  |

| u = Bit is unchanged x = Bit is unknown |                                   |                                  | -n/n = Value at POR and BOR/Value at all other Resets |                                    |     |     |       |  |

| '1' = Bit is set                        | = Bit is set '0' = Bit is cleared |                                  |                                                       |                                    |     |     |       |  |

| bit 7-5                                 | Unimplemen                        | ted: Read as '                   | )'                                                    |                                    |     |     |       |  |

| bit 4                                   | •                                 | P3 Interrupt Ena                 |                                                       |                                    |     |     |       |  |

|                                         | 1 = Enables                       | the CCP3 inter<br>the CCP3 inter | rupt                                                  |                                    |     |     |       |  |

| bit 3-0                                 | Unimplemen                        | ted: Read as '                   | )'                                                    |                                    |     |     |       |  |

## REGISTER 8-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

## 12.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- · EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EEDATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Words, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

### 12.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 12.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

| REGISTER 12-0: EECONZ: EEPROW CONTROL 2 REGISTER | REGISTER 12-6: | EECON2: EEPROM CONTROL 2 REGISTER |

|--------------------------------------------------|----------------|-----------------------------------|

|--------------------------------------------------|----------------|-----------------------------------|

| W-0/0                     | W-0/0    | W-0/0                | W-0/0 | W-0/0                                  | W-0/0            | W-0/0            | W-0/0        |

|---------------------------|----------|----------------------|-------|----------------------------------------|------------------|------------------|--------------|

| EEPROM Control Register 2 |          |                      |       |                                        |                  |                  |              |

| bit 7                     |          |                      |       |                                        |                  |                  | bit 0        |

|                           |          |                      |       |                                        |                  |                  |              |

| Legend:                   |          |                      |       |                                        |                  |                  |              |

| R = Readable              | bit      | W = Writable bit     |       | U = Unimpler                           | nented bit, read | l as '0'         |              |

| S = Bit can onl           | y be set | x = Bit is unknown   |       | -n/n = Value at POR and BOR/Value at a |                  | R/Value at all o | other Resets |

| '1' = Bit is set          |          | '0' = Bit is cleared |       |                                        |                  |                  |              |

#### bit 7-0 Data EEPROM Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the EECON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes. Refer to **Section 12.2.2** "Writing to the Data EEPROM Memory" for more information.

#### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7                                               | Bit 6 | Bit 5       | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0  | Register on<br>Page |

|--------|-----------------------------------------------------|-------|-------------|-------|--------|--------|-------|--------|---------------------|

| EECON1 | EEPGD                                               | CFGS  | LWLO        | FREE  | WRERR  | WREN   | WR    | RD     | 123                 |

| EECON2 | EEPROM Control Register 2 (not a physical register) |       |             |       |        |        | 124*  |        |                     |

| EEADRL | EEADRL<7:0>                                         |       |             |       |        |        | 122   |        |                     |

| EEADRH | _(1)                                                |       | EEADRH<6:0> |       |        |        |       | 122    |                     |

| EEDATL |                                                     |       | EEDATL<7:0> |       |        |        |       | 122    |                     |

| EEDATH | —                                                   | _     |             |       | EEDAT  | H<5:0> |       |        | 122                 |

| INTCON | GIE                                                 | PEIE  | TMR0IE      | INTE  | IOCIE  | TMR0IF | INTF  | IOCIF  | 93                  |

| PIE2   | OSFIE                                               | C2IE  | C1IE        | EEIE  | BCL1IE | C4IE   | C3IE  | CCP2IE | 95                  |

| PIR2   | OSFIF                                               | C2IF  | C1IF        | EEIF  | BCL1IF | C4IF   | C3IF  | CCP2IF | 99                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by data EEPROM module.

\* Page provides register information.

2: Unimplemented, read as '1'.

## 13.2 Register Definitions: Alternate Pin Function Control

#### REGISTER 13-1: APFCON1: ALTERNATE PIN FUNCTION CONTROL 1 REGISTER

| R/W-0/0          | R/W-0/0                                                | R/W-0/0                            | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|------------------|--------------------------------------------------------|------------------------------------|-----------------|-----------------|------------------|------------------|--------------|--|

| C2OUTSEL         | CCP1SEL SDOSEL SCKSEL SDISEL TXSEL RXSEL CCP2SE        |                                    |                 |                 |                  |                  |              |  |

| bit 7            |                                                        |                                    | •               | ·               |                  |                  | bit 0        |  |

|                  |                                                        |                                    |                 |                 |                  |                  |              |  |

| Legend:          |                                                        |                                    | L:4             |                 | nonted bit rece  |                  |              |  |

| R = Readable     |                                                        | W = Writable                       |                 | •               | nented bit, read |                  |              |  |

| u = bit is uncha | inged                                                  | x = Bit is unkr                    |                 | -n/n = value a  | at POR and BO    | R/value at all o | other Resets |  |

| '1' = Bit is set |                                                        | '0' = Bit is clea                  | ared            |                 |                  |                  |              |  |

| bit 7            | C2OUTSEL ·                                             | C2OUT Pin Se                       | lection bit     |                 |                  |                  |              |  |

|                  |                                                        |                                    |                 |                 |                  |                  |              |  |

|                  | 1 = C2OUT is on pin RA6<br>0 = C2OUT is on pin RA5     |                                    |                 |                 |                  |                  |              |  |

| bit 6            | CCP1SEL: CCP1 Input/Output Pin Selection bit           |                                    |                 |                 |                  |                  |              |  |

|                  | 1 = CCP1 is on pin RB0                                 |                                    |                 |                 |                  |                  |              |  |

|                  | 0 = CCP1 is                                            | •                                  |                 |                 |                  |                  |              |  |

| bit 5            |                                                        | SSP SDO Pin S                      | election bit    |                 |                  |                  |              |  |

|                  | 1 = SDO is c                                           | •                                  |                 |                 |                  |                  |              |  |

|                  | 0 = SDO is c                                           | •                                  |                 |                 |                  |                  |              |  |

| bit 4            |                                                        | SSP Serial Cloc                    | ,               | Pin Selection t | Dit              |                  |              |  |

|                  |                                                        | K is on pin RB7<br>K is on pin RC3 |                 |                 |                  |                  |              |  |

| bit 3            |                                                        | SP Serial Data                     |                 | Itout Din Soloo | tion hit         |                  |              |  |

| bit 5            |                                                        |                                    | (30A/301) 00    |                 |                  |                  |              |  |

|                  | 1 = SDA/SDI is on pin RB6<br>0 = SDA/SDI is on pin RC4 |                                    |                 |                 |                  |                  |              |  |

| bit 2            |                                                        | in Selection bit                   |                 |                 |                  |                  |              |  |

|                  | 1 = TX is on pin RB6                                   |                                    |                 |                 |                  |                  |              |  |

|                  | 0 = TX is on                                           | •                                  |                 |                 |                  |                  |              |  |

| bit 1            | RXSEL: RX F                                            | Pin Selection bi                   | t               |                 |                  |                  |              |  |

|                  | 1 = RX is on pin RB7                                   |                                    |                 |                 |                  |                  |              |  |

|                  | 0 = RX is on pin RC7                                   |                                    |                 |                 |                  |                  |              |  |

| bit 0            | CCP2SEL: C                                             | CP2 Input/Outp                     | out Pin Selecti | on bit          |                  |                  |              |  |

|                  | 1 = CCP2 is                                            |                                    |                 |                 |                  |                  |              |  |

|                  | 0 = CCP2 is                                            | on pin RC1                         |                 |                 |                  |                  |              |  |

| TABLE 16-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | —     |       | ADFVF | R<1:0> | 161                 |

Legend: Shaded cells are unused by the temperature indicator module.

## 23.1 Timer2 Operation

The clock input to the Timer2 modules is the system instruction clock (Fosc/4).

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 23.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- · Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMR2 is not cleared when T2CON is written.

## 23.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2-to-PR2 match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE, of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

### 23.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 26.0 "Master Synchronous Serial Port (MSSP) Module"

## 23.4 Timer2 Operation During Sleep

The Timer2 timers cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

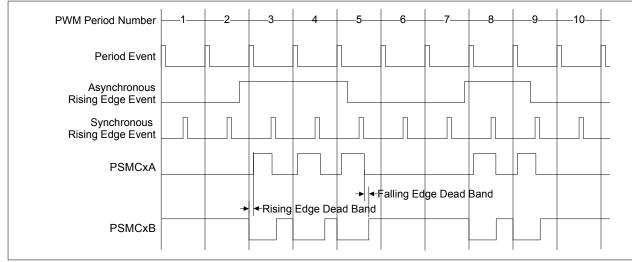

#### 24.3.8 PULSE-SKIPPING PWM WITH COMPLEMENTARY OUTPUTS

The pulse-skipping PWM is used to generate a series of fixed-length pulses that may or not be triggered at each period event. If any of the sources enabled to generate a rising edge event are high when a period event occurs, a pulse will be generated. If the rising edge sources are low at the period event, no pulse will be generated.

The rising edge occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

#### 24.3.8.1 Mode Features

- · Dead-band control is available

- · No steering control available

- · Primary PWM is output on only PSMCxA.

- · Complementary PWM is output on only PSMCxB.

## 24.3.8.2 Waveform Generation

#### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

- · Complementary output is set inactive

- Dead-band rising is activated (if enabled)

- · Primary output is set active

#### Falling Edge Event

- · Primary output is set inactive

- Dead-band falling is activated (if enabled)

- · Complementary output is set active

Note: To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

#### FIGURE 24-11: PULSE-SKIPPING WITH COMPLEMENTARY OUTPUT PWM WAVEFORM

© 2012-2014 Microchip Technology Inc.

### 27.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |  |  |  |

|-------|-------------------------------------------|--|--|--|

|       | FIFO have framing errors, repeated reads  |  |  |  |

|       | of the RCREG will not clear the FERR bit. |  |  |  |

#### 27.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 27.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9 bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 27.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

### 27.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 6.2.2** "Internal Clock Sources" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 27.4.1** "**Auto-Baud Detect**"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

| ADDLW            | Add literal and W                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | $(W) + k \to (W)$                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                               |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ANDLW            | AND literal with W                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                             |

| Operands:        | $0 \le k \le 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                      |

| Status Affected: | Z                                                                                                                    |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                               |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ADDWFC           | ADD W and CARRY bit to f                                                                                                                                                   |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                             |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                         |  |  |  |  |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                         |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                   |  |  |  |  |  |

| Description:     | Add W, the Carry flag and data<br>memory location 'f'. If 'd' is '0', the<br>result is placed in W. If 'd' is '1',<br>the result is placed in data<br>memory location 'f'. |  |  |  |  |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                              |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ]ASRF f{,d}                                                                                                                                                                                                          |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                  |  |  |  |  |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                                             |  |  |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                                |  |  |  |  |

| Description:     | The contents of register 'f' are<br>shifted one bit to the right through<br>the Carry flag. The MSb remains<br>unchanged. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |

|                  |                                                                                                                                                                                                                                     |  |  |  |  |

| ▶ register f → X |

|------------------|

|------------------|

| Param<br>No. | Sym.   | Characteristic                                                      | Min.   | Тур† | Max.   | Units | Conditions                                    |

|--------------|--------|---------------------------------------------------------------------|--------|------|--------|-------|-----------------------------------------------|

|              |        | Program Memory<br>Programming Specifications                        |        |      |        |       |                                               |

| D110         | VIHH   | Voltage on MCLR/VPP/RE3 pin                                         | 8.0    | _    | 9.0    | V     | (Note 3)                                      |

| D111         | IDDP   | Supply Current during<br>Programming                                | —      | —    | 10     | mA    |                                               |

| D112         |        | VDD for Bulk Erase                                                  | 2.7    | —    | VDDMAX | V     |                                               |

| D113         | VPEW   | VDD for Write or Row Erase                                          | VDDMIN | —    | VDDMAX | V     |                                               |

| D114         | IPPPGM | Current on MCLR/VPP during<br>Erase/Write                           | —      | —    | 1.0    | mA    |                                               |

| D115         | IDDPGM | Current on VDD during Erase/Write                                   | —      |      | 5.0    | mA    |                                               |

|              |        | Data EEPROM Memory                                                  |        |      |        |       |                                               |

| D116         | ED     | Byte Endurance                                                      | 100K   | —    | _      | E/W   | -40°C to +85°C                                |

| D117         | VDRW   | VDD for Read/Write                                                  | VDDMIN | —    | VDDMAX | V     |                                               |

| D118         | TDEW   | Erase/Write Cycle Time                                              | —      | 4.0  | 5.0    | ms    |                                               |

| D119         | TRETD  | Characteristic Retention                                            | —      | 40   | _      | Year  | Provided no other specifications are violated |

| D120         | TREF   | Number of Total Erase/Write<br>Cycles before Refresh <sup>(2)</sup> | 100k   | —    | _      | E/W   | -40°C to +85°C                                |

|              |        | Program Flash Memory                                                |        |      |        |       |                                               |

| D121         | Eр     | Cell Endurance                                                      | 10K    | —    | _      | E/W   | -40°C to +85°C ( <b>Note 1</b> )              |

| D122         | Vpr    | VDD for Read                                                        | VDDMIN | —    | VDDMAX | V     |                                               |

| D123         | Tiw    | Self-timed Write Cycle Time                                         | —      | 2    | 2.5    | ms    |                                               |

| D124         | TRETD  | Characteristic Retention                                            | —      | 40   | _      | Year  | Provided no other specifications are violated |

## Standard Operating Conditions (unless otherwise stated)

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Self-write and Block Erase.

2: Refer to Section 12.2 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

3: Required only if single-supply programming is disabled.

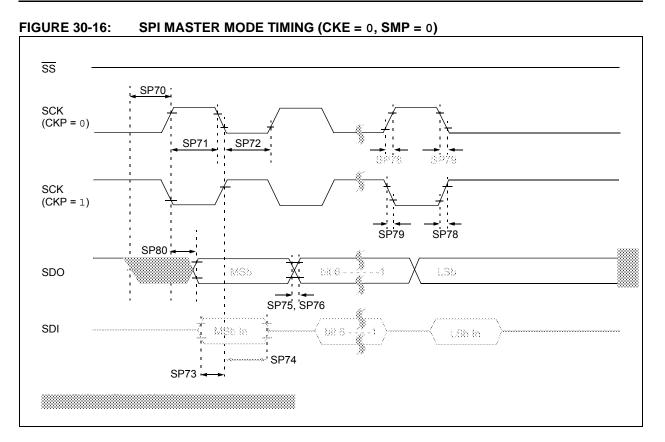

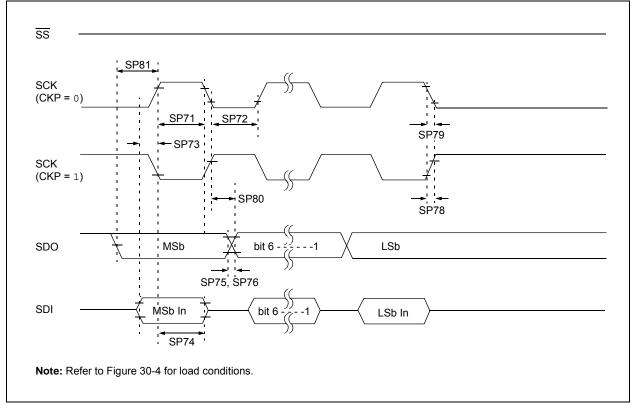

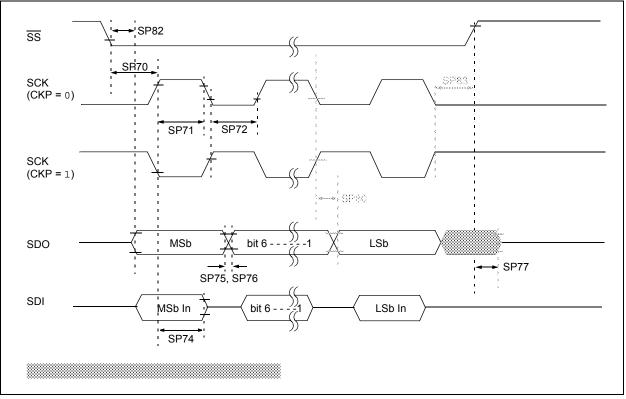

FIGURE 30-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

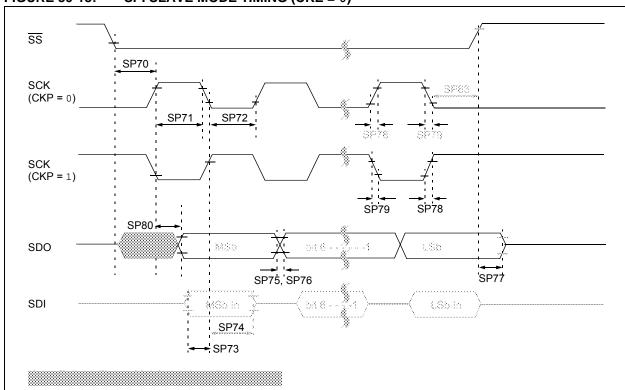

#### FIGURE 30-18: SPI SLAVE MODE TIMING (CKE = 0)

| Standard Operating Conditions (unless otherwise stated) |                                 |                            |              |            |      |                                            |                                             |  |

|---------------------------------------------------------|---------------------------------|----------------------------|--------------|------------|------|--------------------------------------------|---------------------------------------------|--|

| Param.<br>No.                                           | Symbol                          | Characteristic             |              | Min.       | Max. | Units                                      | Conditions                                  |  |

| SP100*                                                  | Тнідн                           | Clock high time            | 100 kHz mode | 4.0        |      | μS                                         | Device must operate at a minimum of 1.5 MHz |  |

|                                                         |                                 |                            | 400 kHz mode | 0.6        | _    | μS                                         | Device must operate at a minimum of 10 MHz  |  |

|                                                         |                                 |                            | SSP module   | 1.5TCY     | _    |                                            |                                             |  |

| SP101*                                                  | P101* TLOW Clock low time       | Clock low time             | 100 kHz mode | 4.7        | _    | μS                                         | Device must operate at a minimum of 1.5 MHz |  |

|                                                         |                                 | 400 kHz mode               | 1.3          | _          | μS   | Device must operate at a minimum of 10 MHz |                                             |  |

|                                                         |                                 |                            | SSP module   | 1.5TCY     | _    |                                            |                                             |  |

| SP102*                                                  | SP102* TR SDA and SCL rise time | SDA and SCL rise           | 100 kHz mode | —          | 1000 | ns                                         |                                             |  |

|                                                         |                                 | 400 kHz mode               | 20 + 0.1Св   | 300        | ns   | CB is specified to be from 10-400 pF       |                                             |  |

| SP103*                                                  | 3* TF SDA and SCL fall          | SDA and SCL fall           | 100 kHz mode | —          | 250  | ns                                         |                                             |  |

|                                                         |                                 | time                       | 400 kHz mode | 20 + 0.1Св | 250  | ns                                         | CB is specified to be from 10-400 pF        |  |

| SP106*                                                  | THD:DAT                         | Data input hold time       | 100 kHz mode | 0          | _    | ns                                         |                                             |  |

|                                                         |                                 |                            | 400 kHz mode | 0          | 0.9  | μs                                         |                                             |  |

| SP107*                                                  | TSU:DAT                         | Data input setup<br>time   | 100 kHz mode | 250        | _    | ns                                         | (Note 2)                                    |  |

|                                                         |                                 |                            | 400 kHz mode | 100        | _    | ns                                         |                                             |  |

| SP109*                                                  | ΤΑΑ                             | Output valid from<br>clock | 100 kHz mode | _          | 3500 | ns                                         | (Note 1)                                    |  |

|                                                         |                                 |                            | 400 kHz mode |            | _    | ns                                         |                                             |  |

| SP110*                                                  | TBUF                            | Bus free time              | 100 kHz mode | 4.7        | _    | μs                                         | Time the bus must be free                   |  |

|                                                         |                                 |                            | 400 kHz mode | 1.3        | _    | μS                                         | before a new transmission<br>can start      |  |

| SP111                                                   | Св                              | Bus capacitive loadir      | ng           |            | 400  | pF                                         |                                             |  |

## TABLE 30-22: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS

These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

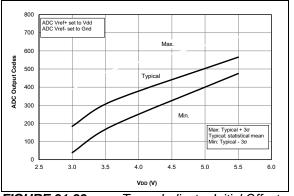

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

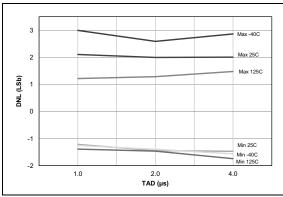

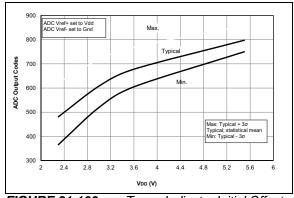

FIGURE 31-97: ADC 12-bit Mode, Single-Ended DNL, VDD = 5.5V, VREF = 5.5V.

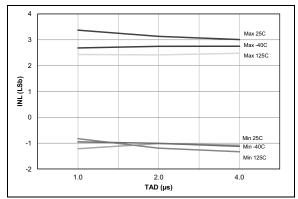

FIGURE 31-98: ADC 12-bit Mode, Single-Ended INL, VDD = 5.5V, VREF = 5.5V.

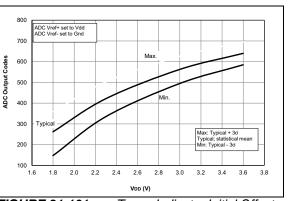

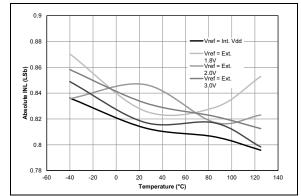

**FIGURE 31-99:** Temp. Indicator Initial Offset, High Range, Temp. = 20°C, PIC16F1784/6/7 Only.

FIGURE 31-100: Temp. Indicator Initial Offset, Low Range, Temp. = 20°C, PIC16F1784/6/7 Only.

**FIGURE 31-101:** Temp. Indicator Initial Offset, Low Range, Temp. = 20°C, PIC16LF1784/6/7 Only.

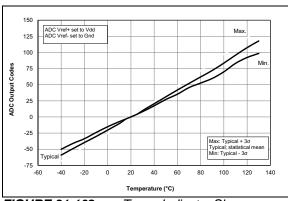

**FIGURE 31-102:** Temp. Indicator Slope Normalized to 20°C, High Range, VDD = 5.5V, PIC16F1784/6/7 Only.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

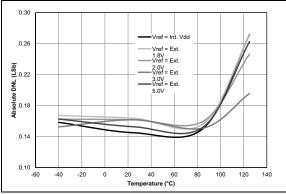

FIGURE 31-132: Absolute Value of DAC DNL Error, VDD = 5.0V, PIC16F1784/6/7 Only.

**FIGURE 31-133:** Absolute Value of DAC INL Error, VDD = 5.0V, PIC16F1784/6/7 Only.

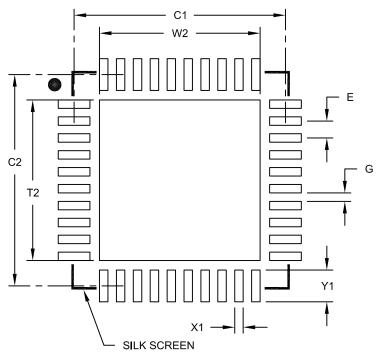

## 40-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 5x5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |  |

|----------------------------|-------------|----------|------|------|--|--|

| Dimension Limits           |             | MIN      | NOM  | MAX  |  |  |

| Contact Pitch              | E           | 0.40 BSC |      |      |  |  |

| Optional Center Pad Width  | W2          |          |      | 3.80 |  |  |

| Optional Center Pad Length | T2          |          |      | 3.80 |  |  |

| Contact Pad Spacing        | C1          |          | 5.00 |      |  |  |

| Contact Pad Spacing        | C2          |          | 5.00 |      |  |  |

| Contact Pad Width (X40)    | X1          |          |      | 0.20 |  |  |

| Contact Pad Length (X40)   | Y1          |          |      | 0.75 |  |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2156B