Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

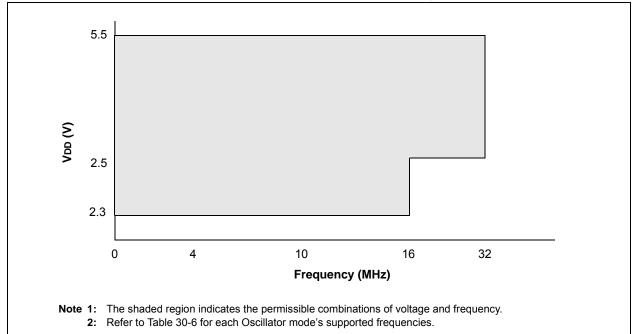

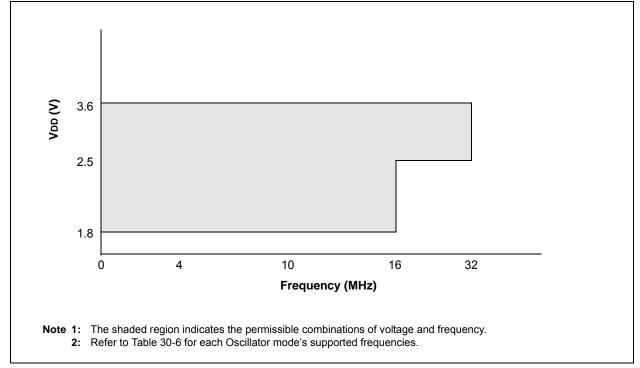

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1784-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Pin Diagram – 40-Pin PDIP

Note:

| Vpp/MCLR/RE3<br>RA0<br>RA1<br>RA2<br>RA3<br>RA4<br>RA5<br>RE0<br>RE1<br>RE2<br>VDD<br>VSS<br>RA7<br>RA6<br>RC0<br>RC1<br>RC2<br>RC3<br>RD0<br>RD1 | 1         2         3         4         5         6         7         8         9         10         11         12         13         14         15         16         17         18         19         20 | PIC16(L)F1784<br>PIC16(L)F1787 | 39         38         37         36         35         34         33         32         31         30         29         28         27         26         25         24         23         22 | RB7ICSPDAT<br>RB6/ICSPCLK<br>RB5<br>RB4<br>RB3<br>RB2<br>RB1<br>RB0<br>VDD<br>VSS<br>RD7<br>RD6<br>RD5<br>RD4<br>RC7<br>RC6<br>RC5<br>RC4<br>RC3<br>RC4<br>RD3<br>RD2 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                   |                                                                                                                                                                                                            |                                |                                                                                                                                                                                               |                                                                                                                                                                       |

See Table 2 for the location of all peripheral functions.

### TABLE 1-2: PIC16(L)F1784/6/7 PINOUT DESCRIPTION

| Name                                                                                                                      | Function  | Input<br>Type | Output<br>Type | Description                                     |

|---------------------------------------------------------------------------------------------------------------------------|-----------|---------------|----------------|-------------------------------------------------|

| RA0/AN0/C1IN0-/C2IN0-/                                                                                                    | RA0       | TTL/ST        | CMOS           | General purpose I/O.                            |

| C3IN0-/C4IN0-                                                                                                             | AN0       | AN            |                | ADC Channel 0 input.                            |

|                                                                                                                           | C1IN0-    | AN            |                | Comparator C1 negative input.                   |

|                                                                                                                           | C2IN0-    | AN            |                | Comparator C2 negative input.                   |

|                                                                                                                           | C3IN0-    | AN            | _              | Comparator C3 negative input.                   |

|                                                                                                                           | C4IN0-    | AN            |                | Comparator C4 negative input.                   |

| RA1/AN1/C1IN1-/C2IN1-/                                                                                                    | RA1       | TTL/ST        | CMOS           | General purpose I/O.                            |

| C3IN1-/C4IN1-/OPA1OUT                                                                                                     | AN1       | AN            | _              | ADC Channel 1 input.                            |

|                                                                                                                           | C1IN1-    | AN            |                | Comparator C1 negative input.                   |

|                                                                                                                           | C2IN1-    | AN            |                | Comparator C2 negative input.                   |

| 3IN1-/C4IN1-/OPA1OUT<br>A2/AN2/C1IN0+/C2IN0+/<br>3IN0+/C4IN0+/DAC1OUT1/<br>REF-/DAC1VREF-/OPA1IN-<br>A3/AN3/VREF+/C1IN1+/ | C3IN1-    | AN            |                | Comparator C3 negative input.                   |

|                                                                                                                           | C4IN1-    | AN            |                | Comparator C4 negative input.                   |

|                                                                                                                           | OPA10UT   |               | AN             | Operational Amplifier 1 output.                 |

| RA2/AN2/C1IN0+/C2IN0+/                                                                                                    | RA2       | TTL/ST        | CMOS           | General purpose I/O.                            |

| C3IN0+/C4IN0+/DAC1OUT1/<br>VREF-/DAC1VREF-/OPA1IN-                                                                        | AN2       | AN            | _              | ADC Channel 2 input.                            |

|                                                                                                                           | C1IN0+    | AN            | —              | Comparator C1 positive input.                   |

|                                                                                                                           | C2IN0+    | AN            | —              | Comparator C2 positive input.                   |

|                                                                                                                           | C3IN0+    | AN            | —              | Comparator C3 positive input.                   |

|                                                                                                                           | C4IN0+    | AN            | —              | Comparator C4 positive input.                   |

|                                                                                                                           | DAC1OUT1  | —             | AN             | Digital-to-Analog Converter output.             |

|                                                                                                                           | VREF-     | AN            | _              | ADC Negative Voltage Reference input.           |

|                                                                                                                           | DAC1VREF- | AN            | _              | Digital-to-Analog Converter negative reference. |

| RA3/AN3/VREF+/C1IN1+/                                                                                                     | RA3       | TTL/ST        | CMOS           | General purpose I/O.                            |

| DAC1VREF+                                                                                                                 | AN3       | AN            | —              | ADC Channel 3 input.                            |

|                                                                                                                           | VREF+     | AN            | _              | ADC Voltage Reference input.                    |

|                                                                                                                           | C1IN1+    | AN            | —              | Comparator C1 positive input.                   |

|                                                                                                                           | DAC1VREF+ | AN            | _              | Digital-to-Analog Converter positive reference. |

| RA4/C1OUT/OPA1IN+/T0CKI                                                                                                   | RA4       | TTL/ST        | CMOS           | General purpose I/O.                            |

|                                                                                                                           | C1OUT     |               | CMOS           | Comparator C1 output.                           |

|                                                                                                                           | OPA1IN+   | AN            |                | Operational Amplifier 1 non-inverting input.    |

|                                                                                                                           | TOCKI     | ST            | _              | Timer0 clock input.                             |

| RA5/AN4/C2OUT <sup>(1)</sup> /OPA1IN-/                                                                                    | RA5       | TTL/ST        | CMOS           | General purpose I/O.                            |

| SS                                                                                                                        | AN4       | AN            |                | ADC Channel 4 input.                            |

|                                                                                                                           | C2OUT     |               | CMOS           | Comparator C2 output.                           |

|                                                                                                                           | OPA1IN-   | AN            |                | Operational Amplifier 1 inverting input.        |

|                                                                                                                           | SS        | ST            |                | Slave Select input.                             |

Legend:AN= Analog input or outputCMOS = CMOS compatible input or outputOD= Open DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $l^2C^{TM}$ = Schmitt Trigger input with  $l^2C$ HV= High VoltageXTAL= Crystallevels

Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

2: All pins have interrupt-on-change functionality.

3: PIC16(L)F1784/7 only.

4: PIC16(L)F1786 only.

# PIC16(L)F1784/6/7

| IAD                | LE 3-12.             | SPECIAL                                             | FUNCTIC                                                                                                                                                | IN REGIS         | IER SUMM          |                 |                           |                       |                       |                      |                                 |

|--------------------|----------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-----------------|---------------------------|-----------------------|-----------------------|----------------------|---------------------------------|

| Addr               | Name                 | Bit 7                                               | Bit 6                                                                                                                                                  | Bit 5            | Bit 4             | Bit 3           | Bit 2                     | Bit 1                 | Bit 0                 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Banl               | k 0                  |                                                     |                                                                                                                                                        |                  |                   |                 |                           |                       |                       |                      | •                               |

| 00Ch               | PORTA                | PORTA Data L                                        | atch when wr                                                                                                                                           | itten: PORTA p   | ins when read     |                 |                           |                       |                       | xxxx xxxx            | uuuu uuuu                       |

| 00Dh               | PORTB                | PORTB Data Latch when written: PORTB pins when read |                                                                                                                                                        |                  |                   |                 |                           |                       |                       |                      | uuuu uuuu                       |

| 00Eh               | PORTC                | PORTC Data Latch when written: PORTC pins when read |                                                                                                                                                        |                  |                   |                 |                           |                       |                       | xxxx xxxx            | uuuu uuuu                       |

| 00Fh               | PORTD <sup>(3)</sup> | PORTD Data L                                        | _atch when w                                                                                                                                           | ritten: PORTD p  | oins when read    |                 |                           |                       |                       | xxxx xxxx            | uuuu uuuu                       |

| 010h               | PORTE                | _                                                   |                                                                                                                                                        | _                | _                 | RE3             | RE2 <sup>(3)</sup>        | RE1 <sup>(3)</sup>    | RE0 <sup>(3)</sup>    | xxxx                 | uuuu                            |

| 011h               | PIR1                 | TMR1GIF                                             | ADIF                                                                                                                                                   | RCIF             | TXIF              | SSP1IF          | CCP1IF                    | TMR2IF                | TMR1IF                | 0000 0000            | 0000 0000                       |

| 012h               | PIR2                 | OSFIF                                               | C2IF                                                                                                                                                   | C1IF             | EEIF              | BCL1IF          | C4IF                      | C3IF                  | CCP2IF                | 0000 0-00            | 0000 0-00                       |

| 13h                | PIR3                 | _                                                   | _                                                                                                                                                      | _                | CCP3IF            | _               | _                         | _                     | _                     | 0                    | 0000 0000                       |

| 014h               | PIR4                 |                                                     | PSMC3TIF                                                                                                                                               | PSMC2TIF         | PSMC1TIF          | _               | PSMC3SIF                  | PSMC2SIF              | PSMC1SIF              | -000 -000            | -000 -000                       |

| 015h               | TMR0                 | Timer0 Module                                       |                                                                                                                                                        |                  |                   |                 |                           |                       |                       | xxxx xxxx            | uuuu uuuu                       |

| 016h               | TMR1L                |                                                     |                                                                                                                                                        | st Significant B | yte of the 16-bi  | t TMR1 Regist   | er                        |                       |                       | xxxx xxxx            | uuuu uuuu                       |

| 017h               | TMR1H                |                                                     |                                                                                                                                                        | •                | yte of the 16-bit | •               |                           |                       |                       | XXXX XXXX            | uuuu uuuu                       |

| 018h               | T1CON                | TMR1CS1                                             | TMR1CS0                                                                                                                                                | T1CKPS1          | T1CKPS0           | T10SCEN         | TISYNC                    | _                     | TMR10N                | 0000 00-0            | uuuu uu-u                       |

| 019h               | T1GCON               | TMR1GE                                              | T1GPOL                                                                                                                                                 | T1GTM            | T1GSPM            | T <u>1GGO</u> / | T1GVAL                    | T1GS                  | S<1:0>                | 0000 0x00            | uuuu uxuu                       |

| 016h               | TMR2                 | DONE                                                |                                                                                                                                                        |                  |                   |                 |                           |                       |                       |                      |                                 |

|                    |                      |                                                     | Holding Register for the Least Significant Byte of the 16-bit TMR2 Register Holding Register for the Most Significant Byte of the 16-bit TMR2 Register |                  |                   |                 |                           |                       |                       | XXXX XXXX            | uuuu uuuu                       |

| 017h               | PR2                  | Holding Regist                                      | ter for the ivios                                                                                                                                      | · ·              |                   | TIVIRZ Registe  | 1                         | TOOLO                 | 0.10                  | XXXX XXXX            | uuuu uuuu                       |

| 018h               | T2CON                |                                                     |                                                                                                                                                        | 12001            | PS<3:0>           |                 | TMR2ON                    | T2CKP                 | PS<1:0>               | -000 0000            | -000 0000                       |

| 01Dh<br>to<br>01Fh | _                    | Unimplemented                                       |                                                                                                                                                        |                  |                   |                 |                           |                       |                       | -                    | -                               |

| Ban                | k 1                  |                                                     |                                                                                                                                                        |                  |                   |                 |                           |                       |                       |                      |                                 |

| 08Ch               | TRISA                | PORTA Data D                                        | Direction Regi                                                                                                                                         | ster             |                   |                 |                           |                       |                       | 1111 1111            | 1111 1111                       |

| 08Dh               | TRISB                | PORTB Data                                          | Direction Regi                                                                                                                                         | ster             |                   |                 |                           |                       |                       | 1111 1111            | 1111 1111                       |

| 08Eh               | TRISC                | PORTC Data                                          |                                                                                                                                                        |                  |                   |                 |                           |                       |                       | 1111 1111            | 1111 1111                       |

| 08Fh               | TRISD <sup>(3)</sup> | PORTD Data                                          |                                                                                                                                                        |                  |                   |                 |                           |                       |                       | 1111 1111            |                                 |

| 090h               | TRISE                | _                                                   | _                                                                                                                                                      | _                | _                 | (2)             | TRISE2 <sup>(3)</sup>     | TRISE1 <sup>(3)</sup> | TRISE0 <sup>(3)</sup> | 1111                 | 1111                            |

| 091h               | PIE1                 | TMR1GIE                                             | ADIE                                                                                                                                                   | RCIE             | TXIE              | SSP1IE          | CCP1IE                    | TMR2IE                | TMR1IE                | 0000 0000            |                                 |

| 092h               | PIE2                 | OSFIE                                               | C2IE                                                                                                                                                   | C1IE             | EEIE              | BCL1IE          | C4IE                      | C3IE                  | CCP2IE                | 0000 0-00            |                                 |

| 093h               | PIE3                 | _                                                   | _                                                                                                                                                      | _                | CCP3IE            | _               | _                         | _                     | _                     | 0                    | 0000 0000                       |

| 094h               | PIE4                 | _                                                   | PSMC3TIE                                                                                                                                               | PSMC2TIE         | PSMC1TIE          | _               | PSMC3SIE                  | PSMC2SIE              | PSMC1SIE              | -000 -000            | -000 -000                       |

| 095h               | OPTION_REG           | WPUEN                                               | INTEDG                                                                                                                                                 | TMR0CS           | TMR0SE            | PSA             |                           | PS<2:0>               |                       | 1111 1111            |                                 |

| 096h               | PCON                 | STKOVF                                              | STKUNF                                                                                                                                                 | _                | RWDT              | RMCLR           | RI                        | POR                   | BOR                   | 00-1 11qq            |                                 |

| 097h               | WDTCON               | _                                                   | _                                                                                                                                                      |                  |                   | NDTPS<4:0>      |                           |                       | SWDTEN                | 01 0110              |                                 |

| 098h               | OSCTUNE              |                                                     |                                                                                                                                                        |                  |                   | TUN<            | 5:0>                      |                       | ONDIEN                |                      | 00 0000                         |

| 099h               | OSCCON               | SPLLEN                                              |                                                                                                                                                        | IRCE             | -<3:0>            |                 |                           | SCS                   | <1:0>                 |                      | 0011 1-00                       |

| 09Ah               | OSCSTAT              | T10SCR                                              | PLLR                                                                                                                                                   | OSTS             | HFIOFR            | HFIOFL          | MFIOFR                    | LFIOFR                | HFIOFS                | 00q000               | -                               |

| 09An               | ADRESL               | A/D Result Re                                       |                                                                                                                                                        | 0010             |                   |                 |                           |                       | 1111010               | xxxx xxxx            | uuuu uuuu                       |

| 09Bh               | ADRESH               | A/D Result Re                                       | •                                                                                                                                                      |                  |                   |                 |                           |                       |                       |                      |                                 |

|                    | ADRESH<br>ADCON0     |                                                     | giater i Tigri                                                                                                                                         |                  | 040-4.0           |                 |                           |                       | ADON                  | XXXX XXXX            |                                 |

| 09Dh               |                      | ADRMD                                               |                                                                                                                                                        | 1000-00-0        | CHS<4:0>          |                 |                           | GO/DONE               |                       | 0000 0000            |                                 |

| 09Eh               | ADCON1               | ADFM                                                | TDIOO                                                                                                                                                  | ADCS<2:0>        |                   | _               | ADNREF                    |                       | EF<1:0>               | 0000 -000            |                                 |

| 09Fh               | ADCON2               |                                                     | TRIGS                                                                                                                                                  | EL<3:0>          |                   |                 | CHSN<br>d, read as '0', r | 153:02                |                       | 000000               | 000000                          |

### **TABLE 3-12**: SPECIAL FUNCTION REGISTER SUMMARY

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16(L)F1784/7 only. Note 1:

2:

3:

PIC16F1784/6/7 only. 4:

## 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

### 6.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

# $INTOSC \longrightarrow for the second seco$

### FIGURE 6-8: TWO-SPEED START-UP

### 6.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

### 11.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 30.0 "Electrical Specifications**" for the LFINTOSC tolerances.

### 11.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 11-1.

### 11.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

### 11.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### 11.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 11-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | х      | Х              | Active      |

| 10        |        | Awake          | Active      |

| 10        | х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ~              | Disabled    |

| 00        | х      | Х              | Disabled    |

### TABLE 11-2: WDT CLEARING CONDITIONS

### 11.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

### 11.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 11-2 for more information.

### 11.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0** "**Memory Organization**" and Status Register (Register 3-1) for more information.

| WDT                          |  |

|------------------------------|--|

|                              |  |

|                              |  |

| Cleared                      |  |

| - Cleared                    |  |

|                              |  |

|                              |  |

| Cleared until the end of OST |  |

| Unaffected                   |  |

|                              |  |

### REGISTER 13-40: SLRCONE: PORTE SLEW RATE CONTROL REGISTER<sup>(1)</sup>

| U-0                                   | U-0                                                                  | U-0               | U-0 | U-0                                                   | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------------------------------------|----------------------------------------------------------------------|-------------------|-----|-------------------------------------------------------|---------|---------|---------|

| _                                     | _                                                                    | _                 | _   | _                                                     | SLRE2   | SLRE1   | SLRE0   |

| bit 7                                 |                                                                      | ·                 |     | ·                                                     |         | •       | bit 0   |

|                                       |                                                                      |                   |     |                                                       |         |         |         |

| Legend:                               |                                                                      |                   |     |                                                       |         |         |         |

| R = Readable                          | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                   |     |                                                       |         |         |         |

| u = Bit is uncha                      | anged                                                                | x = Bit is unkno  | own | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |

| '1' = Bit is set '0' = Bit is cleared |                                                                      |                   | red |                                                       |         |         |         |

|                                       |                                                                      |                   |     |                                                       |         |         |         |

| bit 7-3                               | Unimpleme                                                            | nted: Read as '0' |     |                                                       |         |         |         |

| bit 2-0 | SLRE<2:0>: PORTE Slew Rate Enable bits |

|---------|----------------------------------------|

|         | For RE<2:0> pins, respectively         |

|         | 1 = Port pin slew rate is limited      |

|         | 0 = Port pin slews at maximum rate     |

Note 1: SLRE<2:0> are available on PIC16(L)F1784/7 only.

### REGISTER 13-41: INLVLE: PORTE INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1                | R/W-1/1                | R/W-1/1                |

|-------|-----|-----|-----|---------|------------------------|------------------------|------------------------|

| —     | _   | _   | _   | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> |

| bit 7 | •   |     |     |         |                        |                        | bit 0                  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| 0' |

|----|

|    |

bit 3-0 INLVLE<3:0>: PORTE Input Level Select bit<sup>(1)</sup>

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

**Note 1:** INLVLE<2:0> are available on PIC16(L)F1784/7 only.

|                        |       |       |       |          | •       | •••••                  | —                      |                        |                     |

|------------------------|-------|-------|-------|----------|---------|------------------------|------------------------|------------------------|---------------------|

| Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Register<br>on Page |

| ADCON0                 | ADRMD |       |       | CHS<4:0> | •       |                        | GO/DONE                | ADON                   | 172                 |

| ANSELE                 | _     | _     | _     |          |         | ANSE2                  | ANSE1                  | ANSE0                  | 153                 |

| INLVLE                 | —     | _     | —     | _        | INLVLE3 | INLVLE2 <sup>(2)</sup> | INLVLE1 <sup>(2)</sup> | INLVLE0 <sup>(2)</sup> | 155                 |

| LATE <sup>(2)</sup>    | _     | _     | _     |          |         | LATE2                  | LATE1                  | LATE0                  | 153                 |

| ODCONE <sup>(2)</sup>  | _     | _     | _     |          |         | ODE2                   | ODE1                   | ODE0                   | 154                 |

| PORTE                  | —     | _     | —     | _        | RE3     | RE2 <sup>(2)</sup>     | RE1 <sup>(2)</sup>     | RE0 <sup>(2)</sup>     | 152                 |

| SLRCONE <sup>(2)</sup> | _     | _     | _     |          |         | SLRE2                  | SLRE1                  | SLRE0                  | 155                 |

| TRISE                  | _     | _     | _     | _        | (1)     | TRISE2 <sup>(2)</sup>  | TRISE1 <sup>(2)</sup>  | TRISE0 <sup>(2)</sup>  | 152                 |

| WPUE                   | _     | _     | _     | _        | WPUE3   | WPUE2 <sup>(2)</sup>   | WPUE1 <sup>(2)</sup>   | WPUE0 <sup>(2)</sup>   | 154                 |

### TABLE 13-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Unimplemented, read as '1'.

2: PIC16(L)F1784/7 only

### 15.4 Register Definitions: FVR Control

### REGISTER 15-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0         | R-q/q                                                   | R/W-0/0                                                        | R/W-0/0                                                        | R/W-0/0                                                                                     | R/W-0/0                                                                                             | R/W-0/0                                                                     | R/W-0/0      |

|-----------------|---------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------|

| FVREN           | FVRRDY <sup>(1)</sup>                                   | TSEN                                                           | TSRNG                                                          | CDAF                                                                                        | /R<1:0>                                                                                             | ADFV                                                                        | R<1:0>       |

| bit 7           |                                                         |                                                                |                                                                |                                                                                             |                                                                                                     |                                                                             | bit (        |

|                 |                                                         |                                                                |                                                                |                                                                                             |                                                                                                     |                                                                             |              |

| Legend:         |                                                         |                                                                |                                                                |                                                                                             |                                                                                                     |                                                                             |              |

| R = Readabl     | e bit                                                   | W = Writable                                                   | bit                                                            | U = Unimpler                                                                                | nented bit, read                                                                                    | as '0'                                                                      |              |

| u = Bit is unc  | hanged                                                  | x = Bit is unki                                                | nown                                                           | -n/n = Value a                                                                              | at POR and BO                                                                                       | R/Value at all c                                                            | other Resets |

| '1' = Bit is se | t                                                       | '0' = Bit is cle                                               | ared                                                           | q = Value dep                                                                               | pends on condit                                                                                     | ion                                                                         |              |

| bit 7           | 1 = Fixed Vo                                            | d Voltage Refe<br>Itage Referenc<br>Itage Referenc             | e is enabled                                                   | bit                                                                                         |                                                                                                     |                                                                             |              |

| bit 6           | 1 = Fixed Vo                                            | ed Voltage Re<br>Itage Referenc<br>Itage Referenc              | e output is rea                                                |                                                                                             | enabled                                                                                             |                                                                             |              |

| bit 5           | 1 = Tempera                                             | erature Indicato<br>ture Indicator is<br>ture Indicator is     | s enabled                                                      | 3)                                                                                          |                                                                                                     |                                                                             |              |

| bit 4           | 1 = VOUT = V                                            | perature Indica<br>′DD - 4V⊤ (High<br>′DD - 2V⊤ (Low           | Range)                                                         | election bit <sup>(3)</sup>                                                                 |                                                                                                     |                                                                             |              |

| bit 3-2         | CDAFVR<1:0<br>11 = Compar<br>10 = Compar<br>01 = Compar | )>: Comparator<br>ator and DAC<br>ator and DAC<br>ator and DAC | and DAC Fix<br>Fixed Voltage<br>Fixed Voltage<br>Fixed Voltage | Reference Per<br>Reference Per<br>Reference Per                                             | erence Selectio<br>ipheral output is<br>ipheral output is<br>ipheral output is<br>ipheral output is | s 4x (4.096V) <sup>(2</sup><br>s 2x (2.048V) <sup>(2</sup><br>s 1x (1.024V) |              |

| bit 1-0         | 11 = ADC Fix<br>10 = ADC Fix<br>01 = ADC Fix            | ed Voltage Re<br>ed Voltage Re<br>ed Voltage Re                | ference Perip<br>ference Perip<br>ference Perip                | nce Selection t<br>heral output is<br>heral output is<br>heral output is<br>heral output is | 4x (4.096V) <sup>(2)</sup><br>2x (2.048V) <sup>(2)</sup><br>1x (1.024V)                             |                                                                             |              |

|                 | VRRDY is always                                         |                                                                | •                                                              | ם סע                                                                                        |                                                                                                     |                                                                             |              |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 16.0 "Temperature Indicator Module" for additional information.

### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|---------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0> | ADFVF | R<1:0> | 162                 |

Legend: Shaded cells are not used with the Fixed Voltage Reference.

### 17.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 17.4 "ADC Acquisition Requirements".

### EXAMPLE 17-1: A/D CONVERSION

;This code block configures the ADC ; for polling, Vdd and Vss references, Frc ;clock and ANO input. ;Conversion start & polling for completion ; are included. BANKSEL ADCON1 ; B'11110000' ;2's complement, Frc MOVLW ;clock MOVWF ADCON1 ;Vdd and Vss Vref B'00001111' ;set negative input MOVLW MOVWF ADCON2 ;to negative ;reference BANKSEL TRISA BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ANSEL.0 BSF ;Set RA0 to analog BANKSEL ADCON0 ; B'00000001' ;Select channel AN0 MOVLW MOVWF ADCON0 ;Turn ADC On CALL SampleTime ; Acquisiton delay BSF ADCON0, ADGO ;Start conversion ADCON0, ADGO ; Is conversion done? BTFSC GOTO \$-1 ;No, test again BANKSEL ADRESH ; MOVF ADRESH,W ;Read upper 2 bits MOVWF RESULTHI ;store in GPR space

### 19.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

### 19.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DAC10UT pin.

- The DAC1R<7:0> range select bits are cleared.

### 24.3.7 PULSE-SKIPPING PWM

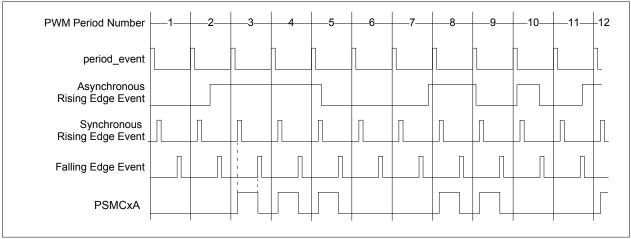

The pulse-skipping PWM is used to generate a series of fixed-length pulses that can be triggered at each period event. A rising edge event will be generated when any enabled asynchronous rising edge input is active when the period event occurs, otherwise no event will be generated.

The rising edge event occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

### 24.3.7.1 Mode Features

- · No dead-band control available

- No steering control available

- PWM is output to only one pin:

- PSMCxA

### 24.3.7.2 Waveform Generation

### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

PSMCxA is set active

Falling Edge Event

PSMCxA is set inactive

**Note:** To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

### FIGURE 24-10: PULSE-SKIPPING PWM WAVEFORM

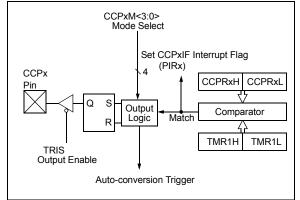

### 25.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- · Set the CCPx output

- · Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 25-2 shows a simplified diagram of the compare operation.

### FIGURE 25-2: COMPARE MODE OPERATION BLOCK DIAGRAM

### 25.2.1 CCPX PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

The CCP2 pin function can be moved to alternate pins using the APFCON register (Register 13-1). Refer to **Section 13.1 "Alternate Pin Function"** for more details.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

### 25.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode. See **Section 22.0 "Timer1 Module with Gate Control"** for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

### 25.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

### 25.2.4 AUTO-CONVERSION TRIGGER

When Auto-conversion Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- · Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Auto-conversion Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Auto-conversion Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Refer to **Section 17.2.5 "Auto-Conversion Trigger"** for more information.

- **Note 1:** The Auto-conversion Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Auto-conversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

### 25.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

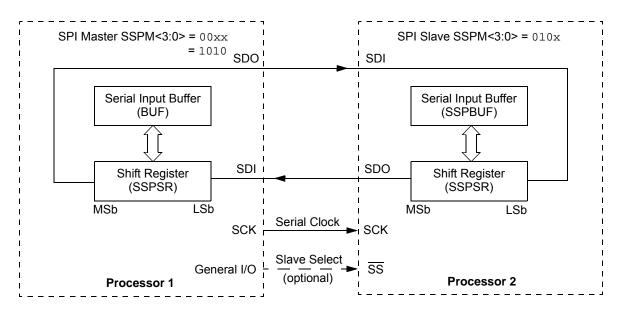

### 26.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- · Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCONx registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI must have corresponding TRIS bit set

- · SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding TRIS bit cleared

- SCK (Slave mode) must have corresponding

TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Detect bit, BF of the SSPSTAT register, and the interrupt flag bit, SSP1IF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF of the SSPSTAT register, indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can

### FIGURE 26-5: SPI MASTER/SLAVE CONNECTION

### 27.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 27-3 contains the formulas for determining the baud rate. Example 27-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 27-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

### EXAMPLE 27-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: Fosc Desired Baud Rate =  $\frac{1}{64([SPBRGH:SPBRGL] + 1)}$ Solving for SPBRGH:SPBRGL: Fosc  $X = \frac{Desired Baud Rate}{-1}$ 64 16000000  $\frac{9600}{64} - 1$ = [25.042] = 25 Calculated Baud Rate =  $\frac{16000000}{64(25+1)}$ = 9615Error = Calc. Baud Rate – Desired Baud Rate Desired Baud Rate  $= \frac{(9615 - 9600)}{9600} = 0.16\%$

|        |                |                  |                             |                | SYNC             | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>616 =</b> 0    |                             |                |                  |                             |  |

|--------|----------------|------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos            | Fosc = 8.000 MHz |                             |                | Fosc = 4.000 MHz |                             |                | Fosc = 3.6864 MHz |                             |                | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | —              | _                | _                           |                | _                | _                           |                | _                 | _                           | 300            | 0.16             | 207                         |  |

| 1200   | —              | —                | —                           | 1202           | 0.16             | 207                         | 1200           | 0.00              | 191                         | 1202           | 0.16             | 51                          |  |

| 2400   | 2404           | 0.16             | 207                         | 2404           | 0.16             | 103                         | 2400           | 0.00              | 95                          | 2404           | 0.16             | 25                          |  |

| 9600   | 9615           | 0.16             | 51                          | 9615           | 0.16             | 25                          | 9600           | 0.00              | 23                          | _              | _                | _                           |  |

| 10417  | 10417          | 0.00             | 47                          | 10417          | 0.00             | 23                          | 10473          | 0.53              | 21                          | 10417          | 0.00             | 5                           |  |

| 19.2k  | 19231          | 0.16             | 25                          | 19.23k         | 0.16             | 12                          | 19.2k          | 0.00              | 11                          | _              | _                | _                           |  |

| 57.6k  | 55556          | -3.55            | 8                           | —              | _                | _                           | 57.60k         | 0.00              | 3                           | —              | _                | _                           |  |

| 115.2k | —              | _                | —                           |                | _                | —                           | 115.2k         | 0.00              | 1                           |                | _                | —                           |  |

## TABLE 27-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0             | 0.00                          | 6666                        | 300.0             | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.0              | 0.00       | 2303                        |

| 1200   | 1200              | -0.02                         | 3332                        | 1200              | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200               | 0.00       | 575                         |

| 2400   | 2401              | -0.04                         | 832                         | 2399              | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2400               | 0.00       | 287                         |

| 9600   | 9615              | 0.16                          | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |

| 10417  | 10417             | 0.00                          | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k            | 0.16                          | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 57.14k            | -0.79                         | 34                          | 56.818            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 117.6k            | 2.12                          | 16                          | 113.636           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |

|        |                  |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRG        | <b>616 =</b> 1 |                             |                  |            |                             |

|--------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|-------------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            |                             | Fos            | c = 4.000  | ) MHz                       | Fosc = 3.6864 MHz |                |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9            | -0.02      | 1666                        | 300.1          | 0.04       | 832                         | 300.0             | 0.00           | 767                         | 300.5            | 0.16       | 207                         |

| 1200   | 1199             | -0.08      | 416                         | 1202           | 0.16       | 207                         | 1200              | 0.00           | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404             | 0.16       | 207                         | 2404           | 0.16       | 103                         | 2400              | 0.00           | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615             | 0.16       | 51                          | 9615           | 0.16       | 25                          | 9600              | 0.00           | 23                          | _                | _          | _                           |

| 10417  | 10417            | 0.00       | 47                          | 10417          | 0.00       | 23                          | 10473             | 0.53           | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19.23k           | 0.16       | 25                          | 19.23k         | 0.16       | 12                          | 19.20k            | 0.00           | 11                          | _                | _          | _                           |

| 57.6k  | 55556            | -3.55      | 8                           | —              | —          | _                           | 57.60k            | 0.00           | 3                           | —                | _          | _                           |

| 115.2k | —                | _          | _                           | _              | _          | _                           | 115.2k            | 0.00           | 1                           | _                | _          | _                           |

# 27.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 27.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- · Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 27.5.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.