Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-W-                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1784-i-mv |

| TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC16(L)F1784/7) |

|-------------------------------------------------------|

|-------------------------------------------------------|

|     |             |             |             |            |      |                    | (                                    | • • (=) | • ., . ,  |                |                                  |                     |                                        |                                          |           |         |                        |

|-----|-------------|-------------|-------------|------------|------|--------------------|--------------------------------------|---------|-----------|----------------|----------------------------------|---------------------|----------------------------------------|------------------------------------------|-----------|---------|------------------------|

| 0/1 | 40-Pin PDIP | 40-Pin UQFN | 44-Pin TQFP | 44-Pin QFN | ADC  | Reference          | Comparator                           | Op Amps | 8-bit DAC | Timers         | PSMC                             | doo                 | EUSART                                 | MSSP                                     | Interrupt | dn-IInd | Basic                  |

| RA0 | 2           | 17          | 19          | 19         | AN0  | 1                  | C1IN0-<br>C2IN0-<br>C3IN0-<br>C4IN0- | _       | _         | _              | 1                                | ı                   | ı                                      | _                                        | IOC       | Y       | _                      |

| RA1 | 3           | 18          | 20          | 20         | AN1  | I                  | C1IN1-<br>C2IN1-<br>C3IN1-<br>C4IN1- | OPA1OUT | _         | _              | I                                | 1                   |                                        | _                                        | IOC       | Υ       | _                      |

| RA2 | 4           | 19          | 21          | 21         | AN2  | DAC1VREF-<br>VREF- | C1IN0+<br>C2IN0+<br>C3IN0+<br>C4IN0+ |         | DAC1OUT1  | _              | I                                | 1                   | I                                      | _                                        | IOC       | Υ       | _                      |

| RA3 | 5           | 20          | 22          | 22         | AN3  | DAC1VREF+<br>VREF+ | C1IN1+                               | _       | _         | _              |                                  | ı                   | ı                                      | _                                        | IOC       | Υ       | _                      |

| RA4 | 6           | 21          | 23          | 23         | _    | 1                  | C1OUT                                | OPA1IN+ | _         | T0CKI          | -                                | -                   | _                                      | _                                        | IOC       | Υ       | _                      |

| RA5 | 7           | 22          | 24          | 24         | AN4  | _                  | C2OUT                                | OPA1IN- | _         | _              | _                                | _                   | _                                      | SS                                       | IOC       | Υ       | _                      |

| RA6 | 14          | 29          | 31          | 33         | _    |                    | C2OUT <sup>(1)</sup>                 | _       | _         | _              | I                                |                     | _                                      | _                                        | IOC       | Υ       | VCAP<br>CLKOUT<br>OSC2 |

| RA7 | 13          | 28          | 30          | 32         | _    |                    | _                                    | _       | _         | _              | PSMC1CLK<br>PSMC2CLK<br>PSMC3CLK | _                   | _                                      | _                                        | IOC       | Υ       | CLKIN<br>OSC1          |

| RB0 | 33          | 8           | 8           | 9          | AN12 | 1                  | C2IN1+                               | _       | _         | _              | PSMC1IN<br>PSMC2IN<br>PSMC3IN    | CCP1 <sup>(1)</sup> | _                                      | _                                        | INT       | Υ       | _                      |

| RB1 | 34          | 9           | 9           | 10         | AN10 |                    | C1IN3-<br>C2IN3-<br>C3IN3-<br>C4IN3- | OPA2OUT |           | _              | I                                | 1                   | 1                                      | _                                        | IOC       | Υ       | _                      |

| RB2 | 35          | 10          | 10          | 11         | AN8  | 1                  | I                                    | OPA2IN- | _         | _              | 1                                |                     |                                        | _                                        | IOC       | Υ       | CLKR                   |

| RB3 | 36          | 11          | 11          | 12         | AN9  | _                  | C1IN2-<br>C2IN2-<br>C3IN2-           | OPA2IN+ | _         | _              | _                                | CCP2 <sup>(1)</sup> | _                                      | _                                        | IOC       | Υ       | _                      |

| RB4 | 37          | 12          | 14          | 14         | AN11 | 1                  | C3IN1+                               | _       | _         | _              | _                                | _                   | _                                      | _                                        | IOC       | Υ       | _                      |

| RB5 | 38          | 13          | 15          | 15         | AN13 |                    | C4IN2-                               | _       | _         | T1G            |                                  | CCP3 <sup>(1)</sup> | _                                      | SDO <sup>(1)</sup>                       | IOC       | Υ       | _                      |

| RB6 | 39          | 14          | 16          | 16         | _    |                    | C4IN1+                               | _       | _         | _              | _                                | _                   | TX <sup>(1)</sup><br>CK <sup>(1)</sup> | SDA <sup>(1)</sup><br>SDI <sup>(1)</sup> | IOC       | Υ       | ICSPCLK                |

| RB7 | 40          | 15          | 17          | 17         | _    | _                  | _                                    | _       | DAC1OUT2  | _              | _                                | _                   | RX <sup>(1)</sup><br>DT <sup>(1)</sup> | SCL <sup>(1)</sup><br>SCK <sup>(1)</sup> | IOC       | Υ       | ICSPDAT                |

| RC0 | 15          | 30          | 32          | 34         | _    | _                  | 1                                    | _       | _         | T1CKI<br>T1OSO | PSMC1A                           | _                   | _                                      | _                                        | IOC       | Υ       | _                      |

Note 1: Alternate pin function selected with the APFCON1 (Register 13-1) and APFCON2 (Register 13-2) registers.

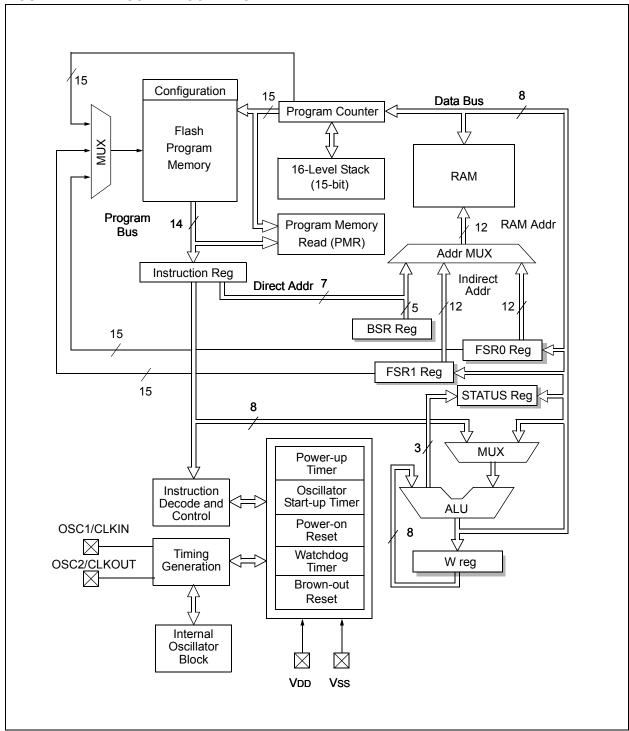

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and

Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- · File Select Registers

- · Instruction Set

FIGURE 2-1: CORE BLOCK DIAGRAM

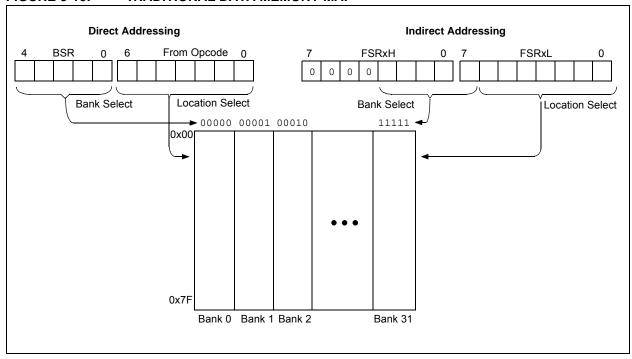

## 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

FIGURE 3-10: TRADITIONAL DATA MEMORY MAP

#### 5.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

## 5.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting" (DS00607).

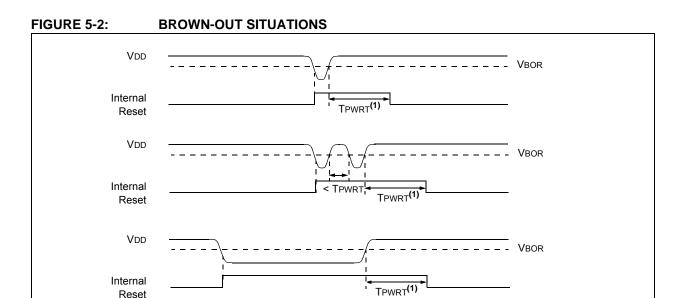

## 5.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 5-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 5-2 for more information.

TABLE 5-1: BOR OPERATING MODES

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |  |  |  |

|------------|--------|-------------|----------|---------------------------------------------------------------------|--|--|--|

| 11         | Х      | X           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |  |  |  |

| 1.0        | v      | Awake       | Active   | Weite for DOD roady (DODDDV = 1)                                    |  |  |  |

| 10         | X      | Sleep       | Disabled | Waits for BOR ready (BORRDY = 1)                                    |  |  |  |

| 0.1        | 1      | X           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |  |  |  |

| 01         | 0      | Х           | Disabled | Regine immediately (RODDDV =)                                       |  |  |  |

| 0.0        | Х      | Х           | Disabled | Begins immediately (BORRDY = x)                                     |  |  |  |

Note 1: In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 5.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 5.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

## 5.3 Register Definitions: BOR Control

Note 1: TPWRT delay only if PWRTE bit is programmed to '0'.

## REGISTER 5-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | _   | _   | _   | _   |     | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7 SBOREN: Software Brown-out Reset Enable bit

If BOREN <1:0> in Configuration Words ≠ 01:

SBOREN is read/write, but has no effect on the BOR.

If BOREN <1:0> in Configuration Words = 01:

1 = BOR Enabled

0 = BOR Disabled

bit 6 **BORFS:** Brown-out Reset Fast Start bit<sup>(1)</sup>

If BOREN<1:0> = 11 (Always on) or BOREN<1:0> = 00 (Always off)

BORFS is Read/Write, but has no effect.

If BOREN <1:0> = 10 (Disabled in Sleep) or BOREN<1:0> = 01 (Under software control):

1 = Band gap is forced on always (covers sleep/wake-up/operating cases)

0 = Band gap operates normally, and may turn off

bit 5-1 **Unimplemented:** Read as '0'

bit 0 BORRDY: Brown-out Reset Circuit Ready Status bit

1 = The Brown-out Reset circuit is active

0 = The Brown-out Reset circuit is inactive

Note 1: BOREN<1:0> bits are located in Configuration Words.

# 6.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 6.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 6-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources

The oscillator module can be configured in one of eight clock modes.

- ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- ECM External Clock Medium-Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. RC External Resistor-Capacitor (RC).

- 8. INTOSC Internal oscillator (31 kHz to 32 MHz).

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The EC clock mode relies on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The RC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces low, medium, and high-frequency clock sources, designated LFINTOSC, MFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 6-1). A wide selection of device clock frequencies may be derived from these three clock sources.

## 6.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

Note:

Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCSTAT register to remain clear.

# 6.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

TABLE 6-1: OSCILLATOR SWITCHING DELAYS

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay                 |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|

| Sleep/POR        | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (TWARM) |

| Sleep/POR        | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                         |

| LFINTOSC         | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each                  |

| Sleep/POR        | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                                | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST)          |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                   |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                  |

| Any clock source | Timer1 Oscillator                                                             | 32 kHz                                          | 1024 Clock Cycles (OST)          |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)                   |

Note 1: PLL inactive.

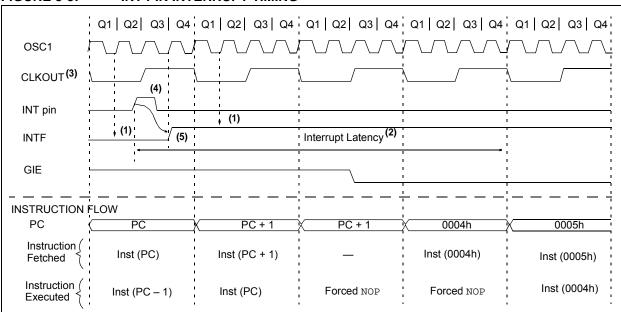

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-5 TcY. Synchronous latency = 3-4 TcY, where TcY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT not available in all oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 30.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

## 12.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- Load the starting address of the row to be modified.

- Read the existing data from the row into a RAM image.

- Modify the RAM image to contain the new data to be written into program memory.

- Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- 8. Repeat steps 6 and 7 as many times as required to reprogram the erased row.

# 12.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15>=1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 12-2.

When read access is initiated on an address outside the parameters listed in Table 12-2, the EEDATH:EEDATL register pair is cleared.

## TABLE 12-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### **EXAMPLE 12-6: CONFIGURATION WORD AND DEVICE ID ACCESS**

```

This code block will read 1 word of program memory at the memory address:

PROG_ADDR_LO (must be 00h-08h) data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL EEADRL

; Select correct Bank

PROG_ADDR_LO

W-TV/OM

MOVWF

EEADRL

; Store LSB of address

CLRF

EEADRH

; Clear MSB of address

BSF

EECON1,CFGS

; Select Configuration Space

INTCON,GIE

BCF

; Disable interrupts

EECON1,RD

; Initiate read

BSF

NOP

; Executed (See Figure 12-1)

NOP

; Ignored (See Figure 12-1)

INTCON, GIE

BSF

; Restore interrupts

MOVF

EEDATL,W

; Get LSB of word

; Store in user location

MOVWF

PROG_DATA_LO

MOVF

EEDATH,W

; Get MSB of word

MOVWF

PROG_DATA_HI

; Store in user location

```

# 13.11.7 PORTE FUNCTIONS AND OUTPUT PRIORITIES<sup>(1)</sup>

Each PORTE pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 13-11.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority. Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

**Note 1:** Applies to 40/44-pin devices only.

## TABLE 13-11: PORTE OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RE0      | CCP3<br>RE0                      |

| RE1      | PSMC3B<br>RE1                    |

| RE2      | PSMC3A<br>RE2                    |

**Note 1:** Priority listed from highest to lowest.

## TABLE 16-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1        | Bit 0 | Register on page |

|---------|--------|--------|-------|-------|-------|-------|--------------|-------|------------------|

| EV/DCON | EV/DEN |        | TOEN  | TODNO |       |       | ADEV/D 44.05 |       | 404              |

| FVRCON  | FVREN  | FVRRDY | TSEN  | TSRNG | _     | _     | ADFVR<1:0>   |       | 161              |

**Legend:** Shaded cells are unused by the temperature indicator module.

## 18.4 Register Definitions: Op Amp Control

## REGISTER 18-1: OPAXCON: OPERATIONAL AMPLIFIERS (OPAX) CONTROL REGISTERS

| R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|-----|-----|-----|---------|---------|

| OPAxEN  | OPAxSP  | _   | _   | _   | _   | OPAxC   | H<1:0>  |

| bit 7   |         |     |     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 **OPAXEN:** Op Amp Enable bit

1 = Op amp is enabled

0 = Op amp is disabled and consumes no active power

bit 6 **OPAxSP:** Op Amp Speed/Power Select bit

1 = Comparator operates in high GBWP mode

0 = Reserved. Do not use.

bit 5-2 **Unimplemented:** Read as '0'

bit 1-0 **OPAxCH<1:0>:** Non-inverting Channel Selection bits

11 = Non-inverting input connects to FVR Buffer 2 output

10 = Non-inverting input connects to DAC\_output

0x = Non-inverting input connects to OPAxIN+ pin

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

| Name     | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0   | Register<br>on Page |

|----------|--------|--------|---------|---------|---------|---------|--------|---------|---------------------|

| ANSELA   | ANSA7  | -      | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1  | ANSA0   | 132                 |

| ANSELB   | _      | ANSB6  | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1  | ANSB0   | 138                 |

| DAC1CON0 | DAC1EN | -      | DAC10E1 | DAC10E2 | DAC1PS  | SS<1:0> | _      | DAC1NSS | 186                 |

| DAC1CON1 |        |        |         | DAC1    | IR<7:0> |         |        |         | 186                 |

| OPA1CON  | OPA1EN | OPA1SP | _       | _       | _       | _       | OPA1P0 | CH<1:0> | 182                 |

| OPA2CON  | OPA2EN | OPA2SP | _       | _       | _       | _       | OPA2P0 | CH<1:0> | 182                 |

| TRISA    | TRISA7 | TRISA6 | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1 | TRISA0  | 131                 |

| TRISB    | TRISB7 | TRISB6 | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1 | TRISB0  | 137                 |

| TRISC    | TRISC7 | TRISC6 | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1 | TRISC0  | 142                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

Note 1: PIC16(L)F1784/7 only

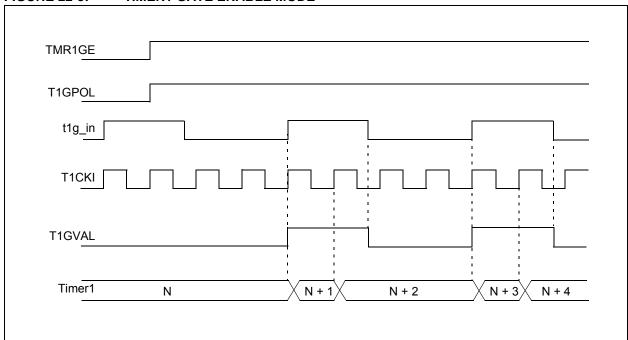

FIGURE 22-3: TIMER1 GATE ENABLE MODE

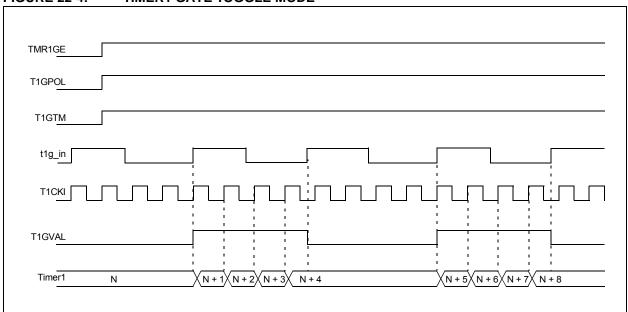

FIGURE 22-4: TIMER1 GATE TOGGLE MODE

# 24.0 PROGRAMMABLE SWITCH MODE CONTROL (PSMC)

The Programmable Switch Mode Controller (PSMC) is a high-performance Pulse Width Modulator (PWM) that can be configured to operate in one of several modes to support single or multiple phase applications.

A simplified block diagram indicating the relationship between inputs, outputs, and controls is shown in Figure 24-1.

This section begins with the fundamental aspects of the PSMC operation. A more detailed description of operation for each mode is located later in **Section 24.3** "**Modes of Operation**"

Modes of operation include:

- · Single-phase

- · Complementary Single-phase

- · Push-Pull

- · Push-Pull 4-Bridge

- · Complementary Push-Pull 4-Bridge

- · Pulse Skipping

- · Variable Frequency Fixed Duty Cycle

- Complementary Variable Frequency Fixed Duty Cycle

- · ECCP Compatible modes

- Full-Bridge

- Full-Bridge Reverse

- · 3-Phase 6-Step PWM

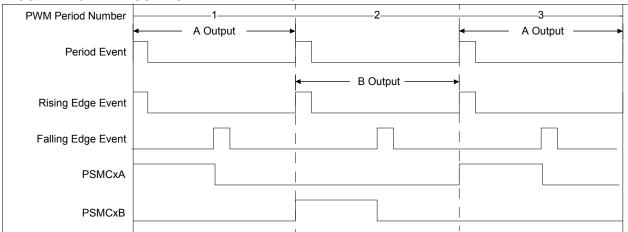

#### 24.3.3 PUSH-PULL PWM

The push-pull PWM is used to drive transistor bridge circuits. It uses at least two outputs and generates PWM signals that alternate between the two outputs in even and odd cycles.

Variations of the push-pull waveform include four outputs with two outputs being complementary or two sets of two identical outputs. Refer to Sections 24.3.4 through 24.3.6 for the other Push-Pull modes.

#### 24.3.3.1 Mode Features

- · No dead-band control available

- · No steering control available

- · Output is on the following two pins only:

- PSMCxA

- PSMCxB

Note: This is a subset of the 6-pin output of the push-pull PWM output, which is why pin functions are fixed in these positions, so they are compatible with that mode. See Section 24.3.6 "Push-Pull PWM with Four Full-Bridge and Complementary Outputs"

#### 24.3.3.2 Waveform Generation

Odd numbered period rising edge event:

· PSMCxA is set active

Odd numbered period falling edge event:

· PSMCxA is set inactive

Even numbered period rising edge event:

· PSMCxB is set active

Even numbered period falling edge event:

· PSMCxB is set inactive

Code for setting up the PSMC generate the complementary single-phase waveform shown in Figure 24-6, and given in Example 24-3.

#### **EXAMPLE 24-3: PUSH-PULL SETUP**

```

; Push-Pull PWM PSMC setup

; Fully synchronous operation

; Period = 10 us

; Duty cycle = 50% (25% each phase)

BANKSEL PSMC1CON

MOVLW

0x02

; set period

MOVWF

PSMC1PRH

MOVLW

0x7F

MOVWF

PSMC1PRL

MOVLW

0 \times 01

; set duty cycle

MOVWF

PSMC1DCH

MOVLW

0 \times 3 F

MOVWF

PSMC1DCL

CLRF

PSMC1PHH

; no phase offset

PSMC1PHL

CLRF

MOVLW

0x01

; PSMC clock=64 MHz

MOVWF

PSMC1CLK

; output on A and B, normal polarity

MOVLW

B'00000011'

MOVWF

PSMC10EN

CLRF

PSMC1POL

; set time base as source for all events

BSF

PSMC1PRS, P1PRST

BSF

PSMC1PHS, P1PHST

BSF

PSMC1DCS, P1DCST

; enable PSMC in Push-Pull Mode

; this also loads steering and time buffers

MOVLW

B'11000010'

MOVWF

PSMC1CON

BANKSEL TRISC

BCF

TRISC, 0

; enable pin drivers

BCF

TRISC, 1

```

#### FIGURE 24-6: PUSH-PULL PWM WAVEFORM

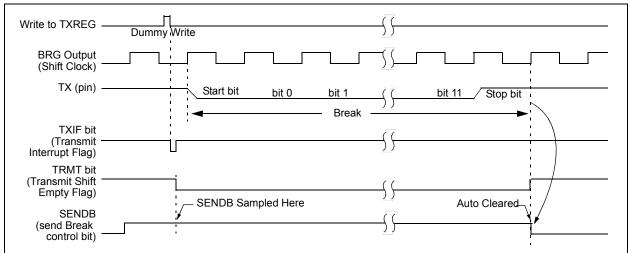

## 27.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 27-9 for the timing of the Break character sequence.

#### 27.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 27.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- · RCIF bit is set

- · FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 27.4.3** "Auto-Wake-up on **Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

#### 27.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 27.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPFN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 27.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 27.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock.

Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 27.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

**Note:** The TSR register is not mapped in data memory, so it is not available to the user.

# 27.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

**Note:** Unless otherwise noted, VIN = 5V, FOSC = 300 kHz, CIN = 0.1  $\mu F$ , TA = 25°C.

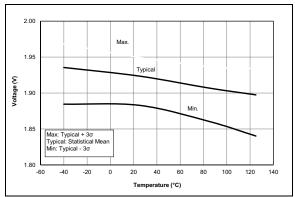

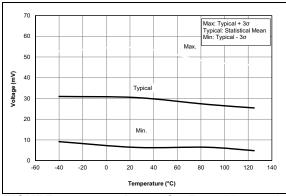

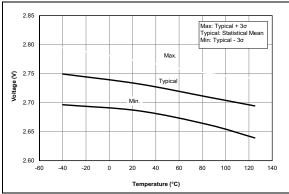

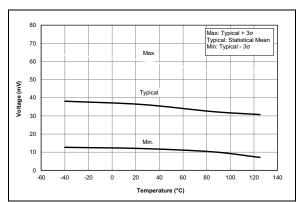

FIGURE 31-61: Brown-Out Reset Voltage, Low Trip Point (BORV = 1), PIC16LF1784/6/7 Only.

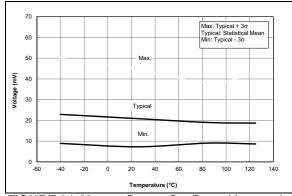

FIGURE 31-62: Brown-Out Reset Hysteresis, Low Trip Point (BORV = 1), PIC16LF1784/6/7 Only.

FIGURE 31-63: Brown-Out Reset Voltage, Low Trip Point (BORV = 1), PIC16F1784/6/7 Only.

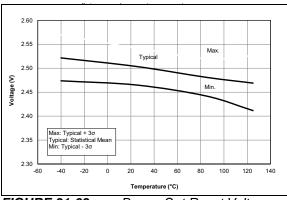

**FIGURE 31-64:** Brown-Out Reset Hysteresis, Low Trip Point (BORV = 1), PIC16F1784/6/7 Only.

**FIGURE 31-65:** Brown-Out Reset Voltage, High Trip Point (BORV = 0).

**FIGURE 31-66:** Brown-Out Reset Hysteresis, High Trip Point (BORV = 0).

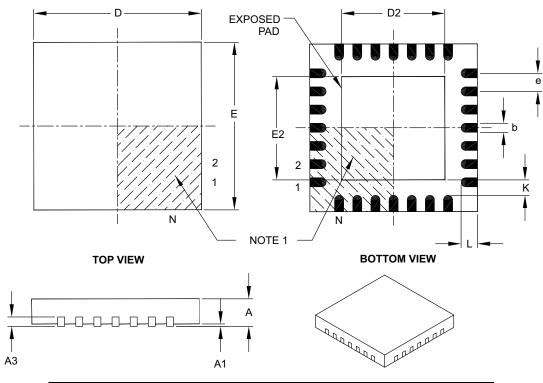

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |          | MILLIMETERS |      |  |

|------------------------|-------|----------|-------------|------|--|

| Dimension Limits       |       | MIN      | NOM         | MAX  |  |

| Number of Pins         | N     | 28       |             |      |  |

| Pitch                  | е     | 0.65 BSC |             |      |  |

| Overall Height         | Α     | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1    | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | А3    | 0.20 REF |             |      |  |

| Overall Width          | Е     | 6.00 BSC |             |      |  |

| Exposed Pad Width      | E2    | 3.65     | 3.70        | 4.20 |  |

| Overall Length         | D     | 6.00 BSC |             |      |  |

| Exposed Pad Length     | D2    | 3.65     | 3.70        | 4.20 |  |

| Contact Width          | b     | 0.23     | 0.30        | 0.35 |  |

| Contact Length         | L     | 0.50     | 0.55        | 0.70 |  |

| Contact-to-Exposed Pad | K     | 0.20     | -           | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

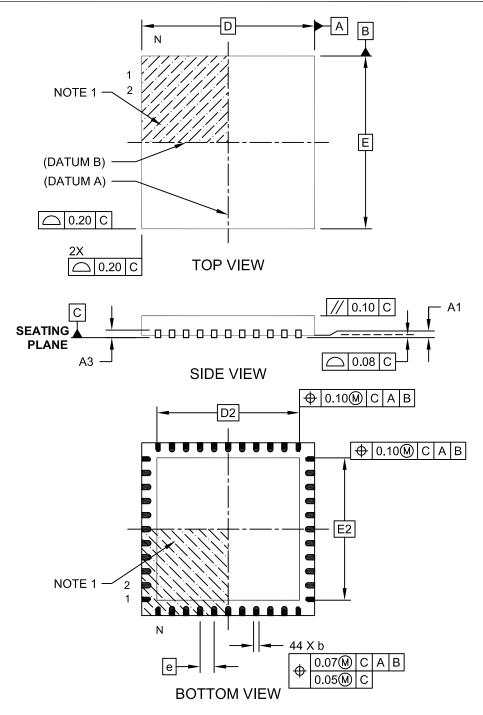

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-103C Sheet 1 of 2